Page 1

bq78350-R1

Technical Reference

Literature Number: SLUUBD3D

September 2015–Revised September 2018

Page 2

Contents

Preface ........................................................................................................................................ 9

1 Introduction....................................................................................................................... 10

2 Basic Measurement System................................................................................................. 11

2.1 Introduction.................................................................................................................. 11

2.2 Current and Coulomb Counting .......................................................................................... 11

2.3 Voltage....................................................................................................................... 11

2.4 Temperature ................................................................................................................ 12

2.4.1 FET Temperature Measurement ............................................................................... 12

2.4.2 Temperature Enable .............................................................................................. 12

2.4.3 Temperature Mode Configuration ............................................................................... 12

2.5 Temperature Ranges ...................................................................................................... 13

2.6 Basic Configuration Options .............................................................................................. 13

2.6.1 DA Configuration .................................................................................................. 13

2.6.2 FET Options........................................................................................................ 14

2.6.3 AFE Cell Map ...................................................................................................... 15

3 Protections........................................................................................................................ 17

3.1 Introduction.................................................................................................................. 17

3.1.1 General Protections Configuration .............................................................................. 17

3.1.2 Enabled Protections .............................................................................................. 18

3.1.3 Enabled Removal Recovery ..................................................................................... 20

3.1.4 FET Action Options for Current Protections ................................................................... 21

3.2 Cell Undervoltage Protection ............................................................................................. 21

3.3 Cell Overvoltage Protection............................................................................................... 22

3.4 Overcurrent in Charge Protection........................................................................................ 22

3.5 Overcurrent in Discharge Protection..................................................................................... 23

3.6 Hardware-Based Protection............................................................................................... 24

3.6.1 Overload in Discharge Protection............................................................................... 24

3.6.2 Short Circuit in Discharge Protection........................................................................... 26

3.6.3 AFE ALERT OVRD Protection .................................................................................. 27

3.7 Temperature Protections .................................................................................................. 28

3.7.1 Overtemperature in Charge Protection......................................................................... 28

3.7.2 Overtemperature in Discharge Protection...................................................................... 29

3.7.3 Undertemperature in Charge Protection ....................................................................... 29

3.7.4 Undertemperature in Discharge Protection.................................................................... 29

3.7.5 Overtemperature FET Protection................................................................................ 30

3.8 Precharge Timeout Protection............................................................................................ 30

3.9 Fast Charge Timeout Protection ......................................................................................... 31

3.10 Overcharge Protection..................................................................................................... 31

4 Permanent Fail................................................................................................................... 32

4.1 Introduction.................................................................................................................. 32

4.2 Permanent Failure Configuration......................................................................................... 32

4.3 Enabling Use of the SAFE Pin ........................................................................................... 34

4.4 Safety Cell Undervoltage Permanent Fail............................................................................... 36

4.5 Safety Cell Overvoltage Permanent Fail ................................................................................ 37

2

Contents

Copyright © 2015–2018, Texas Instruments Incorporated

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 3

www.ti.com

4.6 Safety Overcurrent in Charge Permanent Fail ......................................................................... 37

4.7 Safety Overcurrent in Discharge Permanent Fail ...................................................................... 38

4.8 Safety Overtemperature Cell Permanent Fail .......................................................................... 38

4.9 Safety Overtemperature FET (SOTF) Permanent Fail ................................................................ 38

4.10 Voltage Imbalance at Rest Permanent Fail............................................................................. 39

4.11 Charge FET Permanent Fail.............................................................................................. 39

4.12 Discharge FET Permanent Fail........................................................................................... 39

4.13 External Override Permanent Fail........................................................................................ 40

4.14 AFE Register Permanent Fail............................................................................................. 40

4.15 AFE Communication Permanent Fail.................................................................................... 41

4.16 AFE XREADY Permanent Fail ........................................................................................... 41

4.17 Instruction Flash (IF) Checksum Permanent Fail ...................................................................... 41

4.18 Data Flash (DF) Permanent Fail ......................................................................................... 41

4.19 Open Thermistor Permanent Fail (TS1, TS2, TS3).................................................................... 42

4.20 PF Status Snapshot Data Flash.......................................................................................... 42

4.20.1 Device Status Data .............................................................................................. 42

4.20.2 Device Voltage Data............................................................................................. 43

4.20.3 Device Current Data............................................................................................. 44

4.20.4 Device Temperature Data....................................................................................... 44

4.20.5 AFE Regs ......................................................................................................... 44

4.21 Black Box Recorder........................................................................................................ 44

4.21.1 Black Box Recorded Data....................................................................................... 45

5 Charge Algorithm ............................................................................................................... 47

5.1 Introduction.................................................................................................................. 47

5.2 Fast and Pre-Charging .................................................................................................... 47

5.3 Valid Charge Termination ................................................................................................. 48

5.4 Charge and Discharge Alarms ........................................................................................... 48

5.5 Charge Disable ............................................................................................................. 51

5.6 Charge Inhibit............................................................................................................... 51

5.7 Charge Suspend ........................................................................................................... 52

6 System Present.................................................................................................................. 53

6.1 Introduction.................................................................................................................. 53

6.2 System Present Detection and Action................................................................................... 53

7 Cell Balancing.................................................................................................................... 54

7.1 Introduction.................................................................................................................. 54

7.1.1 Cell Balancing Configuration..................................................................................... 55

8 Power Modes ..................................................................................................................... 56

8.1 Introduction.................................................................................................................. 56

8.2 NORMAL Mode............................................................................................................. 56

8.3 SLEEP Mode................................................................................................................ 56

8.3.1 Device Sleep....................................................................................................... 56

8.3.2 ManufacturerAccess() MAC Sleep.............................................................................. 57

8.3.3 IN SYSTEM SLEEP Mode....................................................................................... 57

8.4 SHUTDOWN Mode ........................................................................................................ 57

8.4.1 Voltage Based Shutdown ........................................................................................ 57

8.4.2 Time Based Shutdown............................................................................................ 58

8.4.3 ManufacturerAccess() MAC Shutdown......................................................................... 58

8.5 Power Mode Indication (PWRM)......................................................................................... 58

9 CEDV Gas Gauging ............................................................................................................ 59

9.1 Introduction.................................................................................................................. 59

9.1.1 Main Fuel Gauge Registers...................................................................................... 59

9.1.2 Fuel Gauge Operating Modes................................................................................... 60

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Contents

3

Page 4

www.ti.com

9.1.3 Full Charge Capacity ............................................................................................. 61

9.1.4 Initial Battery Capacity at Device Reset........................................................................ 62

9.1.5 Capacity Learning (FCC Update) ............................................................................... 62

9.1.6 Qualified Discharge ............................................................................................... 63

9.1.7 End-of-Discharge Thresholds and Capacity Correction...................................................... 64

9.1.8 Reserve Capacity ................................................................................................. 65

9.1.9 EDV Discharge Rate and Temperature Compensation...................................................... 65

9.1.10 EDV Age Factor.................................................................................................. 66

9.1.11 Self Discharge .................................................................................................... 67

9.1.12 Battery Electronic Load Compensation ....................................................................... 67

9.2 Gauging Configuration Options........................................................................................... 67

10 Lifetime Data Collection ...................................................................................................... 70

10.1 Description .................................................................................................................. 70

10.2 Lifetimes..................................................................................................................... 71

10.2.1 LifetimeDataBlock1() 0x0060 ................................................................................... 71

10.2.2 LifetimeDataBlock2() 0x0061 ................................................................................... 71

10.2.3 LifetimeDataBlock3() 0x0062 ................................................................................... 71

10.2.4 LifetimeDataBlock4() 0x0063 ................................................................................... 72

10.2.5 LifetimeDataBlock5() 0x0064 ................................................................................... 73

10.2.6 LifetimeDataBlock6() 0x0065 ................................................................................... 73

10.2.7 LifetimeDataBlock7() 0x0066 ................................................................................... 73

11 Device Security .................................................................................................................. 75

11.1 Description .................................................................................................................. 75

11.2 SHA-1 Description.......................................................................................................... 75

11.3 HMAC Description.......................................................................................................... 75

11.4 Authentication............................................................................................................... 75

11.5 Security Modes ............................................................................................................. 76

11.5.1 FULL ACCESS or UNSEALED to SEALED .................................................................. 76

11.5.2 SEALED to UNSEALED......................................................................................... 76

11.5.3 UNSEALED to FULL ACCESS................................................................................. 76

12 Manufacture Production...................................................................................................... 77

12.1 Manufacture Testing ....................................................................................................... 77

12.1.1 Manufacturing Status Configuration ........................................................................... 77

12.2 Calibration................................................................................................................... 78

12.2.1 Cell Voltage Calibration ......................................................................................... 79

12.2.2 External Average Voltage Calibration ......................................................................... 79

12.2.3 VAUX Voltage Calibration....................................................................................... 80

12.2.4 Voltage Calibration Data Flash ................................................................................. 80

12.2.5 Current Calibration ............................................................................................... 80

12.2.6 Deadbands........................................................................................................ 81

12.2.7 Current Calibration Data Flash ................................................................................. 82

12.2.8 Temperature Calibration......................................................................................... 82

12.2.9 Temperature Calibration Data Flash........................................................................... 82

12.2.10 External Temp Model .......................................................................................... 83

13 Display Port....................................................................................................................... 84

13.1 Introduction.................................................................................................................. 84

13.1.1 Light Emitting Diode (LED) Display Operation ............................................................... 84

13.1.2 Liquid Crystal Display (LCD) Operation....................................................................... 84

13.2 Display Activation .......................................................................................................... 84

13.2.1 LED Display Activation .......................................................................................... 84

13.2.2 LCD Display Activation.......................................................................................... 85

13.3 State-Of-Charge Display .................................................................................................. 85

4

Contents

Copyright © 2015–2018, Texas Instruments Incorporated

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 5

www.ti.com

13.4 LED and LCD Display Configuration .................................................................................... 85

13.5 LCD Specific Display Configuration...................................................................................... 86

13.6 LED Configuration Register............................................................................................... 86

14 Host Controlled GPIO ......................................................................................................... 88

14.1 Introduction.................................................................................................................. 88

14.2 Configuring the GPIO...................................................................................................... 88

14.3 Using the GPIO............................................................................................................. 91

15 Key Input........................................................................................................................... 92

15.1 Introduction.................................................................................................................. 92

15.2 Input Configuration......................................................................................................... 92

15.3 Operation.................................................................................................................... 92

16 Communications ................................................................................................................ 93

16.1 Introduction.................................................................................................................. 93

16.2 SMBus On and Off State.................................................................................................. 93

16.3 Packet Error Checking..................................................................................................... 93

16.4 Slave Address .............................................................................................................. 93

16.5 Broadcasts to Smart Charger and Smart Battery Host................................................................ 94

16.6 SMB Configuration Options ............................................................................................... 95

17 SBS Commands ................................................................................................................. 96

17.1 Summary .................................................................................................................... 96

17.2 0x00 ManufacturerAccess() and 0x44 ManufacturerBlockAccess()................................................. 98

17.2.1 ManufacturerAccess() 0x0000 ManufacturerBlockAccess() or ManufacturerData()................... 100

17.2.2 ManufacturerAccess() 0x0001 Device Type ................................................................ 100

17.2.3 ManufacturerAccess() 0x0002 Firmware Version .......................................................... 100

17.2.4 ManufacturerAccess() 0x0003 Hardware Version.......................................................... 100

17.2.5 ManufacturerAccess() 0x0004 Instruction Flash Signature............................................... 100

17.2.6 ManufacturerAccess() 0x0005 Static DF Signature........................................................ 100

17.2.7 ManufacturerAccess() 0x0006 Chemical ID................................................................. 100

17.2.8 ManufacturerAccess() 0x0008 Static Chem DF Signature................................................ 101

17.2.9 ManufacturerAccess() 0x0009 All DF Signature............................................................ 101

17.2.10 ManufacturerAccess() 0x0010 SHUTDOWN Mode ...................................................... 101

17.2.11 ManufacturerAccess() 0x0011 SLEEP Mode.............................................................. 101

17.2.12 ManufacturerAccess() 0x001B Cell Balance Toggle ..................................................... 102

17.2.13 ManufacturerAccess() 0x001C AFE Delay Disable....................................................... 102

17.2.14 ManufacturerAccess() 0x001D SAFE Toggle ............................................................. 102

17.2.15 ManufacturerAccess() 0x001E PRE-CHG FET ........................................................... 102

17.2.16 ManufacturerAccess() 0x001F CHG FET.................................................................. 102

17.2.17 ManufacturerAccess() 0x0020 DSG FET .................................................................. 102

17.2.18 ManufacturerAccess() 0x0022 FET Control ............................................................... 102

17.2.19 ManufacturerAccess() 0x0023 Lifetime Data Collection ................................................. 103

17.2.20 ManufacturerAccess() 0x0024 Permanent Failure........................................................ 103

17.2.21 ManufacturerAccess() 0x0025 Black Box Recorder...................................................... 103

17.2.22 ManufacturerAccess() 0x0026 SAFE....................................................................... 103

17.2.23 ManufacturerAccess() 0x0027 LED Display Enable...................................................... 103

17.2.24 ManufacturerAccess() 0x0028 Lifetime Data Reset...................................................... 103

17.2.25 ManufacturerAccess() 0x0029 Permanent Fail Data Reset ............................................. 103

17.2.26 ManufacturerAccess() 0x002A Black Box Recorder Reset.............................................. 104

17.2.27 ManufacturerAccess() 0x002B LED TOGGLE ............................................................ 104

17.2.28 ManufacturerAccess() 0x002C LED Display Press....................................................... 104

17.2.29 ManufacturerAccess() 0x002D CALIBRATION Mode ................................................... 104

17.2.30 ManufacturerAccess() 0x0030 Seal Device ............................................................... 104

17.2.31 ManufacturerAccess() 0x0035 Security Keys ............................................................. 104

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Contents

5

Page 6

www.ti.com

17.2.32 ManufacturerAccess() 0x0037 Authentication Key ....................................................... 104

17.2.33 ManufacturerAccess() 0x0041 Device Reset.............................................................. 105

17.2.34 ManufacturerAccess() 0x0050 SafetyAlert................................................................. 105

17.2.35 ManufacturerAccess() 0x0051 SafetyStatus............................................................... 106

17.2.36 ManufacturerAccess() 0x0052 PFAlert..................................................................... 108

17.2.37 ManufacturerAccess() 0x0053 PFStatus................................................................... 109

17.2.38 ManufacturerAccess() 0x0054 OperationStatus .......................................................... 111

17.2.39 ManufacturerAccess() 0x0055 ChargingStatus........................................................... 113

17.2.40 ManufacturerAccess() 0x0056 GaugingStatus............................................................ 114

17.2.41 ManufacturerAccess() 0x0057 ManufacturingStatus..................................................... 115

17.2.42 ManufacturerAccess() 0x0058 AFEStatus................................................................. 117

17.2.43 ManufacturerAccess() 0x0059 AFEConfig ................................................................ 117

17.2.44 ManufacturerAccess() 0x005A AFEVCx .................................................................. 117

17.2.45 ManufacturerAccess() 0x005B AFEData................................................................... 117

17.2.46 ManufacturerAccess() 0x0060 Lifetime Data Block 1 .................................................... 117

17.2.47 ManufacturerAccess() 0x0061 Lifetime Data Block 2 .................................................... 118

17.2.48 ManufacturerAccess() 0x0062 Lifetime Data Block 3 .................................................... 118

17.2.49 ManufacturerAccess() 0x0063 Lifetime Data Block 4 .................................................... 118

17.2.50 ManufacturerAccess() 0x0064 Lifetime Data Block 5 .................................................... 118

17.2.51 ManufacturerAccess() 0x0065 Lifetime Data Block 6 .................................................... 118

17.2.52 ManufacturerAccess() 0x0066 Lifetime Data Block 7 .................................................... 118

17.2.53 ManufacturerAccess() 0x0070 ManufacturerInfo ......................................................... 119

17.2.54 ManufacturerAccess() 0x0071 DAStatus1................................................................. 119

17.2.55 ManufacturerAccess() 0x0072 DAStatus2................................................................. 119

17.2.56 ManufacturerAccess() 0x0080 CUV Snapshot ............................................................ 119

17.2.57 ManufacturerAccess() 0x0081 COV Snapshot............................................................ 120

17.2.58 ManufacturerAccess() 0x0F00 ROM Mode................................................................ 120

17.2.59 Data Flash Access() 0x4000–0x5FFF...................................................................... 120

17.2.60 ManufacturerAccess() 0xF080 Exit Calibration Output Mode........................................... 121

17.2.61 ManufacturerAccess() 0xF081 OutputCellVoltageforCalibration........................................ 121

17.2.62 ManufacturerAccess() 0xF082 OutputCellVoltageCCandTempforCalibration ........................ 122

17.3 0x01 RemainingCapacityAlarm() ....................................................................................... 123

17.4 0x02 RemainingTimeAlarm()............................................................................................ 123

17.5 0x03 BatteryMode()....................................................................................................... 123

17.6 0x04 AtRate().............................................................................................................. 124

17.7 0x05 AtRateTimeToFull() ................................................................................................ 125

17.8 0x06 AtRateTimeToEmpty()............................................................................................. 125

17.9 0x07 AtRateOK().......................................................................................................... 125

17.10 0x08 Temperature() ...................................................................................................... 125

17.11 0x09 Voltage() ............................................................................................................ 126

17.12 0x0A Current() ............................................................................................................ 126

17.13 0x0B AverageCurrent() .................................................................................................. 126

17.14 0x0C MaxError().......................................................................................................... 126

17.15 0x0D RelativeStateOfCharge() ......................................................................................... 127

17.16 0x0E AbsoluteStateOfCharge()......................................................................................... 127

17.17 0x0F RemainingCapacity().............................................................................................. 127

17.18 0x10 FullChargeCapacity().............................................................................................. 127

17.19 0x11 RunTimeToEmpty()................................................................................................ 128

17.20 0x12 AverageTimeToEmpty()........................................................................................... 128

17.21 0x13 AverageTimeToFull().............................................................................................. 128

17.22 0x14 ChargingCurrent().................................................................................................. 128

17.23 0x15 ChargingVoltage() ................................................................................................. 128

17.24 0x16 BatteryStatus() ..................................................................................................... 129

6

Contents

Copyright © 2015–2018, Texas Instruments Incorporated

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 7

www.ti.com

17.25 0x17 CycleCount()........................................................................................................ 130

17.26 0x18 DesignCapacity()................................................................................................... 130

17.27 0x19 DesignVoltage().................................................................................................... 131

17.28 0x1A SpecificationInfo() ................................................................................................. 131

17.29 0x1B ManufacturerDate()................................................................................................ 132

17.30 0x1C SerialNumber()..................................................................................................... 132

17.31 0x20 ManufacturerName() .............................................................................................. 132

17.32 0x21 DeviceName() ...................................................................................................... 133

17.33 0x22 DeviceChemistry() ................................................................................................. 133

17.34 0x23 ManufacturerData()/CalibrationData()........................................................................... 133

17.35 0x2B HostFETControl.................................................................................................... 134

17.36 0x2C GPIOStatus ........................................................................................................ 134

17.37 0x2D GPIOControl ....................................................................................................... 135

17.38 0x2E VAUXVoltage()..................................................................................................... 136

17.39 0x2F Authenticate()/ManufacturerInput().............................................................................. 136

17.40 0x30..0x3E CellVoltage1..15() .......................................................................................... 136

17.41 0x4C DynamicPower() .................................................................................................. 137

17.42 0x4D ExtAveCellVoltage()............................................................................................... 137

17.43 0x4E PendingEDV()...................................................................................................... 137

17.44 0x4F StateOfHealth (SOH) ............................................................................................. 138

17.45 0x50 SafetyAlert .......................................................................................................... 138

17.46 0x51 SafetyStatus........................................................................................................ 138

17.47 0x52 PFAlert .............................................................................................................. 138

17.48 0x53 PFStatus ............................................................................................................ 138

17.49 0x54 OperationStatus.................................................................................................... 138

17.50 0x55 ChargingStatus..................................................................................................... 139

17.51 0x56 GaugingStatus ..................................................................................................... 139

17.52 0x57 ManufacturingStatus............................................................................................... 139

17.53 0x58 AFEStatus .......................................................................................................... 139

17.54 0x59 AFEConfig .......................................................................................................... 139

17.55 0x5A AFEVCx............................................................................................................. 139

17.56 0x5B AFEData ............................................................................................................ 140

17.57 0x60 Lifetime Data Block 1.............................................................................................. 140

17.58 0x61 Lifetime Data Block 2.............................................................................................. 140

17.59 0x62 Lifetime Data Block 3.............................................................................................. 140

17.60 0x63 Lifetime Data Block 4.............................................................................................. 140

17.61 0x64 Lifetime Data Block 5.............................................................................................. 140

17.62 0x65 Lifetime Data Block 6.............................................................................................. 141

17.63 0x66 Lifetime Data Block 7.............................................................................................. 141

17.64 0x70 ManufacturerInfo................................................................................................... 141

17.65 0x71 DAStatus1 .......................................................................................................... 141

17.66 0x72 DAStatus2 .......................................................................................................... 141

17.67 0x80 CUV Snapshot ..................................................................................................... 141

17.68 0x81 COV Snapshot ..................................................................................................... 142

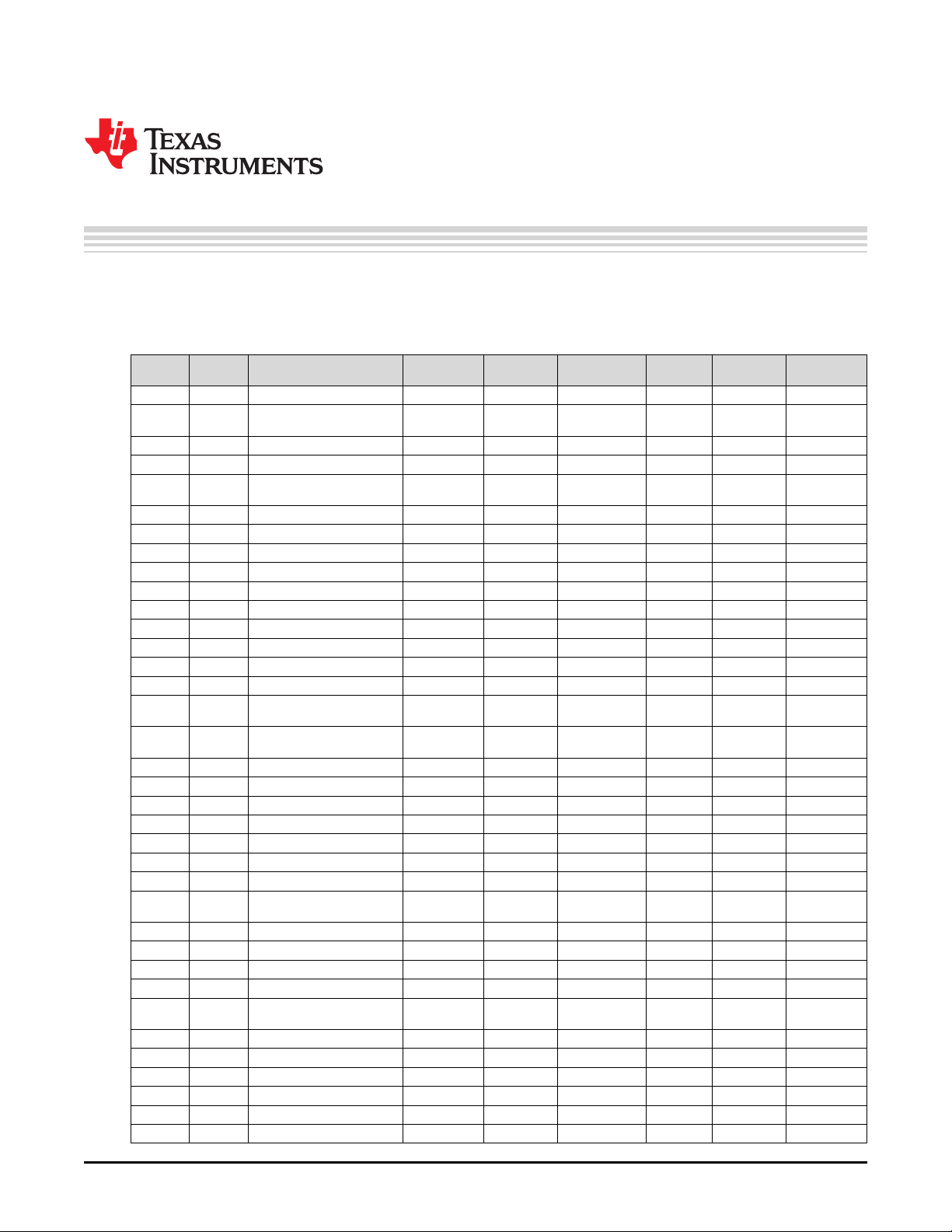

18 Data Flash Access and Format........................................................................................... 143

18.1 Data Flash Access........................................................................................................ 143

18.1.1 Minimum Voltage ............................................................................................... 143

18.2 Data Formats.............................................................................................................. 143

18.2.1 Unsigned Integer (U)........................................................................................... 143

18.2.2 Integer (I) ........................................................................................................ 143

18.2.3 Floating Point (F) ............................................................................................... 144

18.2.4 Hex (H)........................................................................................................... 144

18.2.5 String (S)......................................................................................................... 144

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Contents

7

Page 8

www.ti.com

19 Data Flash Summary......................................................................................................... 145

Revision History ........................................................................................................................ 158

8

Contents

Copyright © 2015–2018, Texas Instruments Incorporated

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 9

Read this First

This manual discusses the modules and peripherals of the bq78350-R1 device, and how each is used to

build a complete battery pack gas gauge and protection solution.

Notational Conventions

The following notational conventions are used if SBS commands and data flash values are mentioned

within a text block:

• SBS commands: italics with parentheses and no breaking spaces; for example, RemainingCapacity().

• Data flash: italics, bold, and breaking spaces; for example, Design Capacity.

• Register bits and flags: italics and brackets; for example, [TDA] Data

• Flash bits: italics and bold; for example, [LED1]

• Modes and states: ALL CAPITALS; for example, UNSEALED

The reference format for SBS commands is: SBS:Command Name(Command No.): Manufacturer

Access(MA No.)[Flag], for example:

SBS:Voltage(0x09), or SBS:ManufacturerAccess(0x00): Seal Device(0x0020)

Read This First

SLUUBD3D–September 2015–Revised September 2018

Preface

Trademarks

All trademarks are the property of their respective owners.

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Preface

9

Page 10

Chapter 1

SLUUBD3D–September 2015–Revised September 2018

Introduction

The bq78350-R1 device provides a feature-rich battery management solution for 3-series cell to 15-series

cell battery pack applications. The device has extended capabilities, including:

• Companion Protection Controller to the bq76920, bq76930, and bq76940 AFE Devices for Li-Ion or

LiFePO4 Battery Packs

• Compensated End-of-Discharge Voltage (CEDV) Gas Gauging Algorithm Accurately Measures

Available Charge and State-of-Health

• Voltage Based Cell Balancing Control

• Normal and Lower Power Modes

– NORMAL

– SLEEP

– SHUTDOWN

• Full Array of Programmable Protection Features

– Voltage

– Current

– Temperature

– Charge Timeout

– CHG/DSG FETs

• Precharge and Fast Charge Algorithm

• Diagnostic Lifetime Data Monitor

• Black Box Event Recorder

• Supports Two-Wire SMBus v1.1 Interface

• SHA-1 Authentication

• Package: 30-Lead TSSOP

The bq78350-R1 is intended to be used with the bq769x0 Battery Monitor with a 2.5-V REGOUT

configuration and I2C Address 0x08. However, the bq78350-R1 can use a bq769x0 with or without the

communications CRC enabled (the bq78350-R1 automatically detects if CRC is enabled).

10

Introduction

SLUUBD3D–September 2015–Revised September 2018

Copyright © 2015–2018, Texas Instruments Incorporated

Submit Documentation Feedback

Page 11

2.1 Introduction

NOTE: For this section, refer to the bq769x0 3-Series to 15-Series Cell Battery Monitor Family for Li-

Ion and Phosphate Applications Data Manual (SLUSBK2) for further details.

The bq78350-R1 reads the bq769x0 companion AFE registers that contain recent values from the

integrating analog-to-digital converter (ADC) for current measurement, and a second delta-sigma ADC for

individual cell and temperature measurements. The bq78350-R1 also has the capability to measure the

battery voltage through an externally translated voltage.

2.2 Current and Coulomb Counting

The integrating delta-sigma ADC in the companion bq769x0 AFE measures the charge/discharge flow of

the battery by measuring the voltage drop across a small-value sense resistor between the SRP and SRN

pins. The 15-bit integrating ADC measures bipolar signals from –0.20 V to 0.20 V with 15-µV resolution.

The AFE reports charge activity when VSR = V

V

– V

(SRP)

digital signal from the AFE over time using an internal counter.

To support large battery configurations, the current data can be scaled to ensure accurate reporting

through the SMBus. The data reported is scaled based on the setting of the SpecificationInfo() command.

The data reported through the Current() can also have a deadband applied to it. This removes any noise

or offset that has not been calibrated out from being reported as real current. This value is programmed in

Deadband with a default configured for mA scaling in SpecificationInfo(). If the SpecificationInfo()

IPSCALE is set to 10 mA or 100 mA, then it is strongly recommended to set Deadband to 1.

is negative. The bq78350-R1 continuously monitors the measured current and integrates the

(SRN)

Chapter 2

SLUUBD3D–September 2015–Revised September 2018

Basic Measurement System

(SRP)

– V

is positive, and discharge activity when VSR =

(SRN)

2.3 Voltage

The bq78350-R1 updates the individual series cell voltages through the bq769x0 at 250-ms intervals. The

bq78350-R1 configures the bq769x0 to connect to the selected cells in sequence and uses this

information for cell balancing and individual cell fault functions. The internal 14-bit ADC of the bq769x0

measures each cell voltage value, which is then communicated digitally to the bq78350-R1 where it is

scaled and translated into unit millivolts. The maximum supported input range of the ADC is 6.075 V.

The bq78350-R1 also separately measures the average cell voltage through an external translation circuit

at the BAT pin. This value is specifically used for the gas gauge algorithm. The external translation circuit

is controlled via the VEN pin so that the translation circuit is only enabled when required to reduce overall

power consumption. VEN requires an external pullup to VCC, typically 100 k, to operate correctly.

In addition to the voltage measurements used by the bq78350-R1 algorithms, there is an optional auxiliary

voltage measurement capability via the VAUX pin. This feature measures the input on a 250-ms update

rate and provides the programmable scaled value through the VAUXVoltage() SMBus command. The data

can be enabled to influence selected fault recovery features. See General Protections Configuration,

[VAUXR], for further details.

The VEN pin will go high 2 ms prior to the BAT being measured if DA Configuration [ExtAveEN] = 1,

and then return low unless DA Configuration [VAUXEN] = 1, which will cause VEN to remain high for a

further 2 ms prior to making the VAUX measurement. This results in VEN possibly being high for up to

40 ms per second in NORMAL mode.

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Basic Measurement System

11

Page 12

Temperature

To support large battery configurations where the battery voltage can exceed 32767 mV, the data should

be scaled as the gauge's internal data processing is done in a signed integer range (–32768 to 32767) to

ensure accurate reporting through the SMBus. The data reported is scaled based on the setting of the

SpecificationInfo() command. The cell voltages are not scaled.

2.4 Temperature

The bq78350-R1 receives temperature information from external or internal temperature sensors in the

bq769x0 AFE. Depending on the number of series cells supported, the AFE will provide one, two, or three

external thermistor measurements. The value of temperature is reported through Temperature() and can

be configured in DA Configuration.

2.4.1 FET Temperature Measurement

The bq78350-R1 can be configured to report FET temperature, which can be available through

DAStatus2(). If multiple temperature sensors are selected for FET temperature, then either the average or

highest is used based on the setting of [FTEMP] in [DA Configuration].

The selection of temperature sensor as cell temperature protection or FET temperature protection can be

made through the Temperature Mode register.

2.4.2 Temperature Enable

This register enables/disables the available temperature sensor options.

www.ti.com

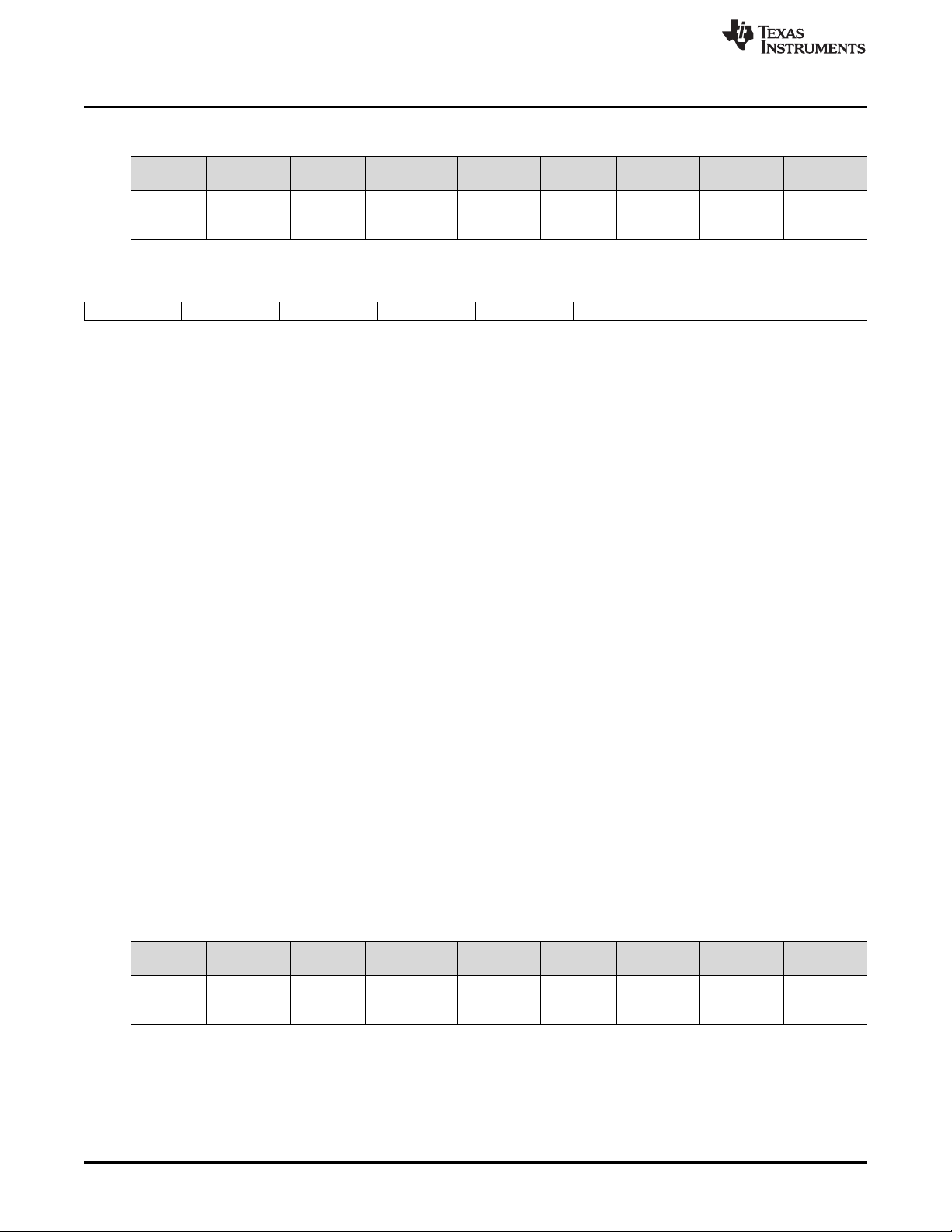

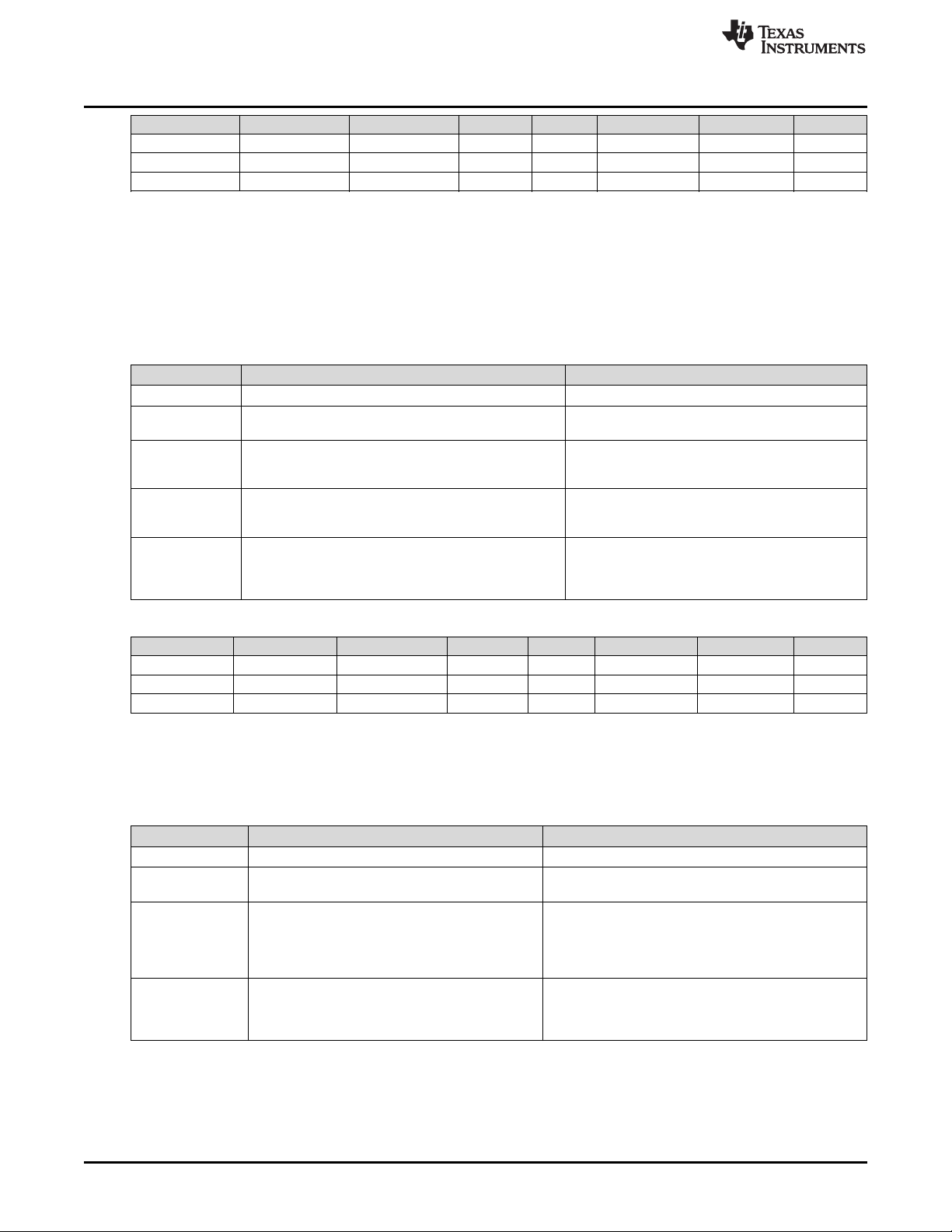

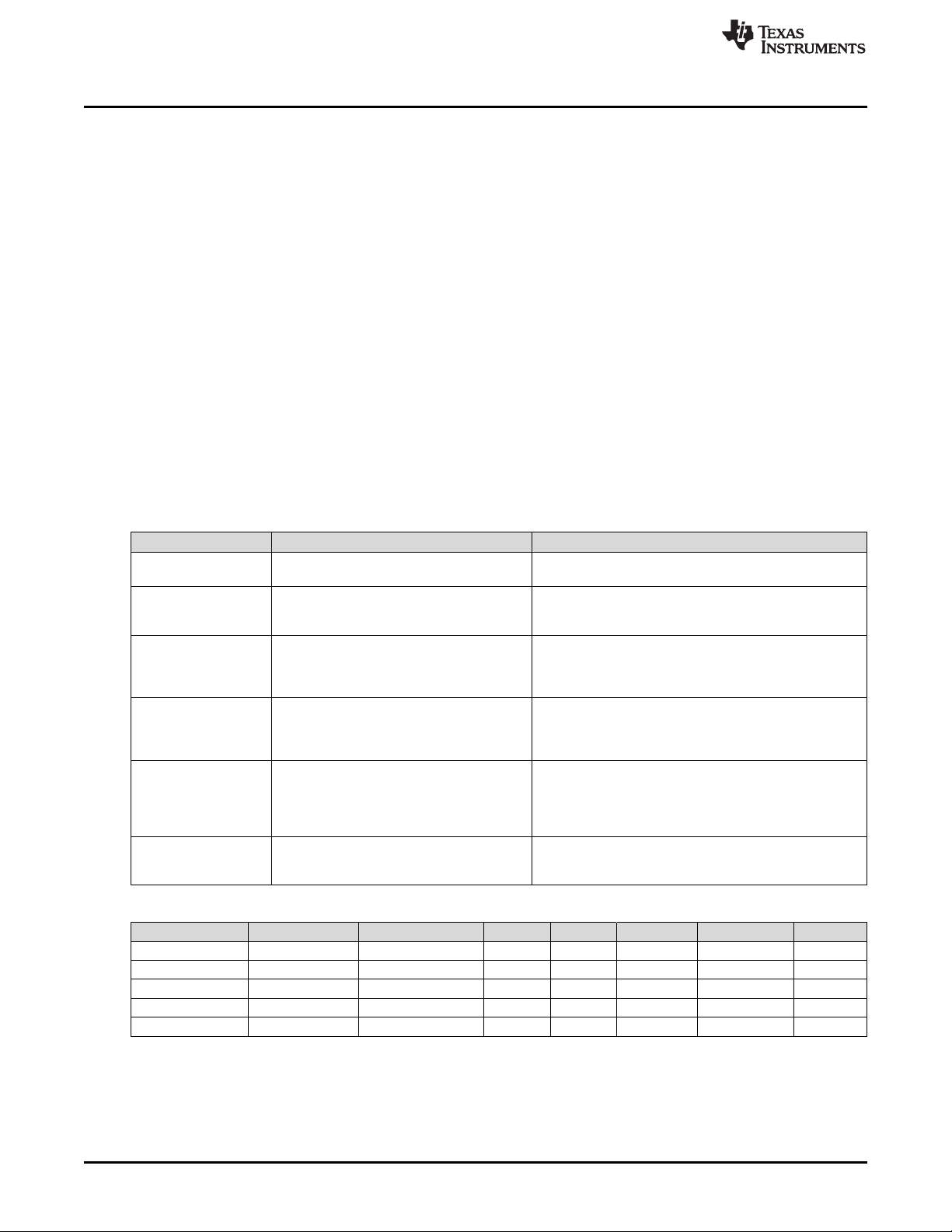

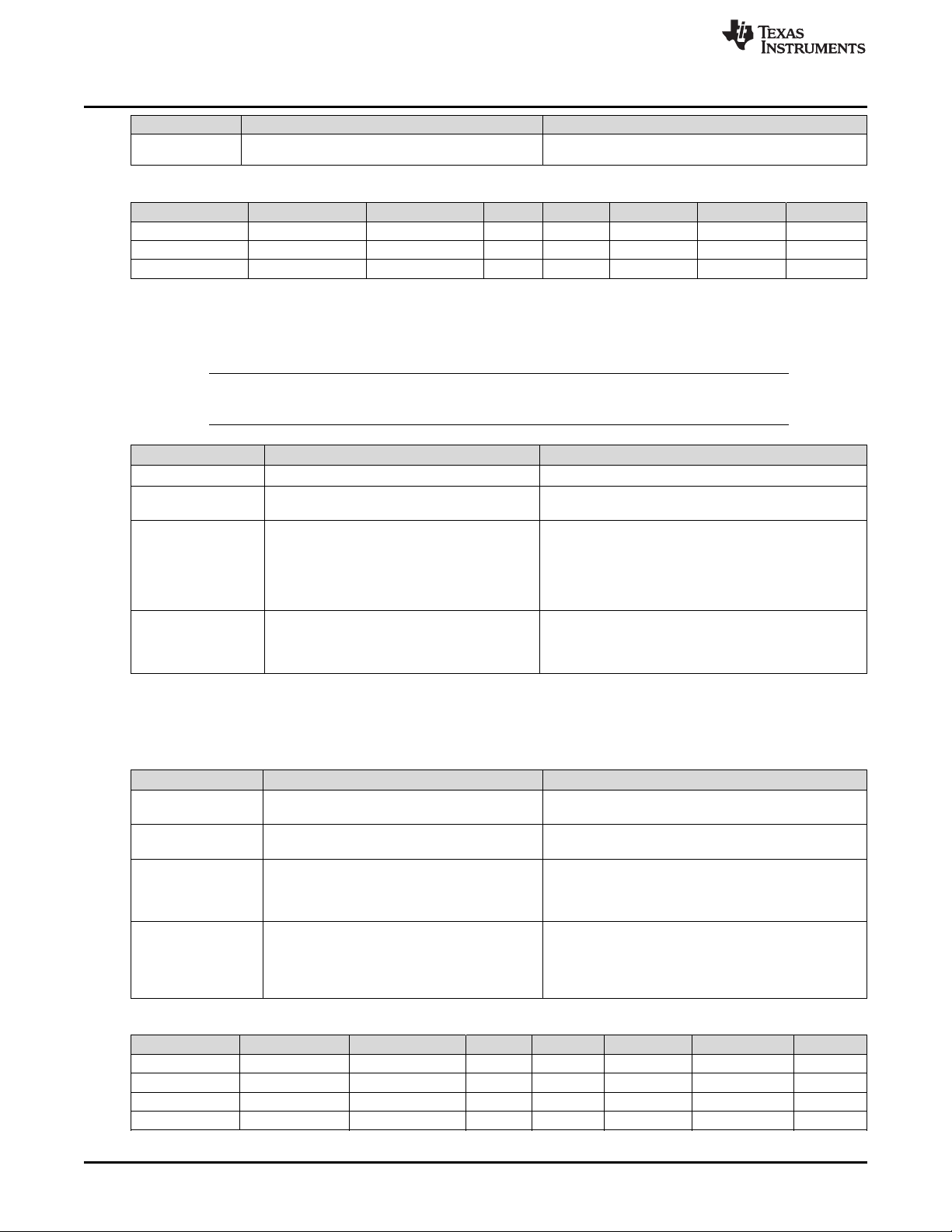

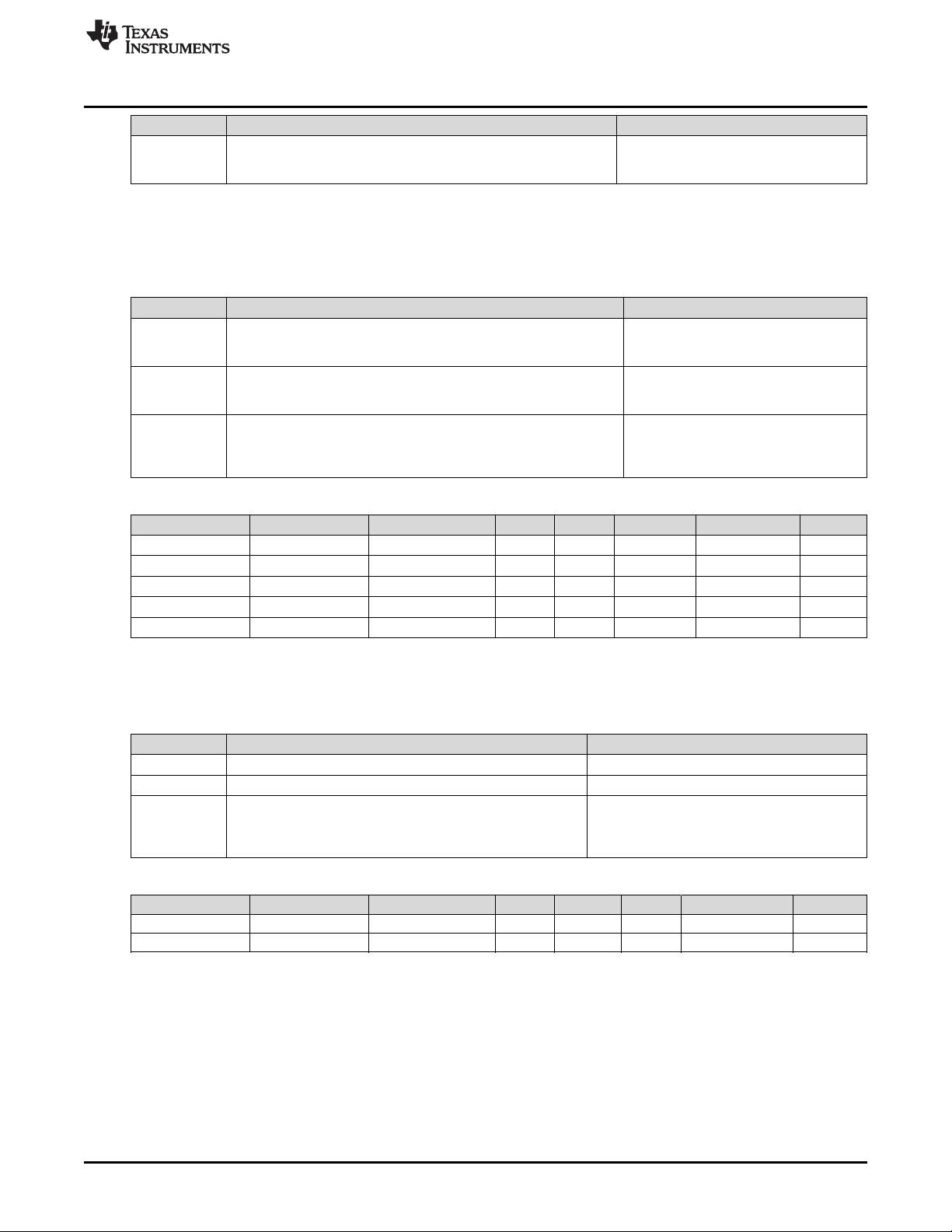

Class Subclass Name Format

Settings Configuration

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Low Byte RSVD RSVD RSVD RSVD SOURCE TS3 TS2 TS1

Temperature

Enable

hex 1 0x00 0xFF 0x09 —

Size in

Bytes

Min Max Default Unit

RSVD (Bits 7–4): Reserved

SOURCE (Bit 3): Configure the use of Internal or External temperature sensors for all AFE ports

0 = Use internal temperature sensor(s)

1 = Use external temperature sensor(s)

TS3 (Bit 2): Enable/disable companion AFE temperature sensor TS3, if available

0 = Disable TS3 temperature sensor

1 = Enable TS3 temperature sensor

TS2 (Bit 1): Enable/disable companion AFE temperature sensor TS2, if available

0 = Disable TS2 temperature sensor

1 = Enable TS2 temperature sensor

TS1 (Bit 0): Enable/disable companion AFE temperature sensor TS1

0 = Disable TS1 temperature sensor

1 = Enable TS1 temperature sensor

2.4.3 Temperature Mode Configuration

Each available external temperature sensor can be configured to be used for the cell temperature or FET

temperature features.

12

Basic Measurement System

Copyright © 2015–2018, Texas Instruments Incorporated

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 13

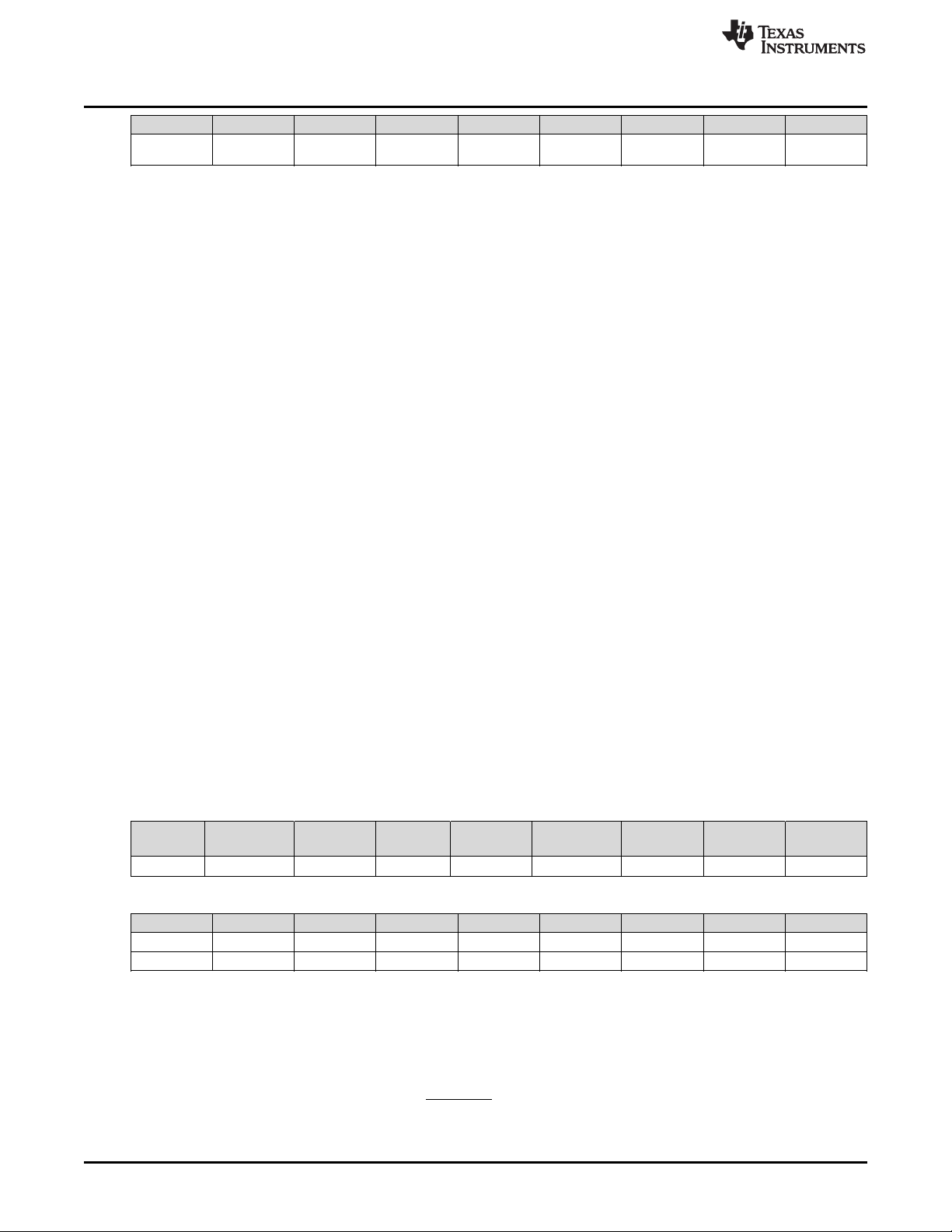

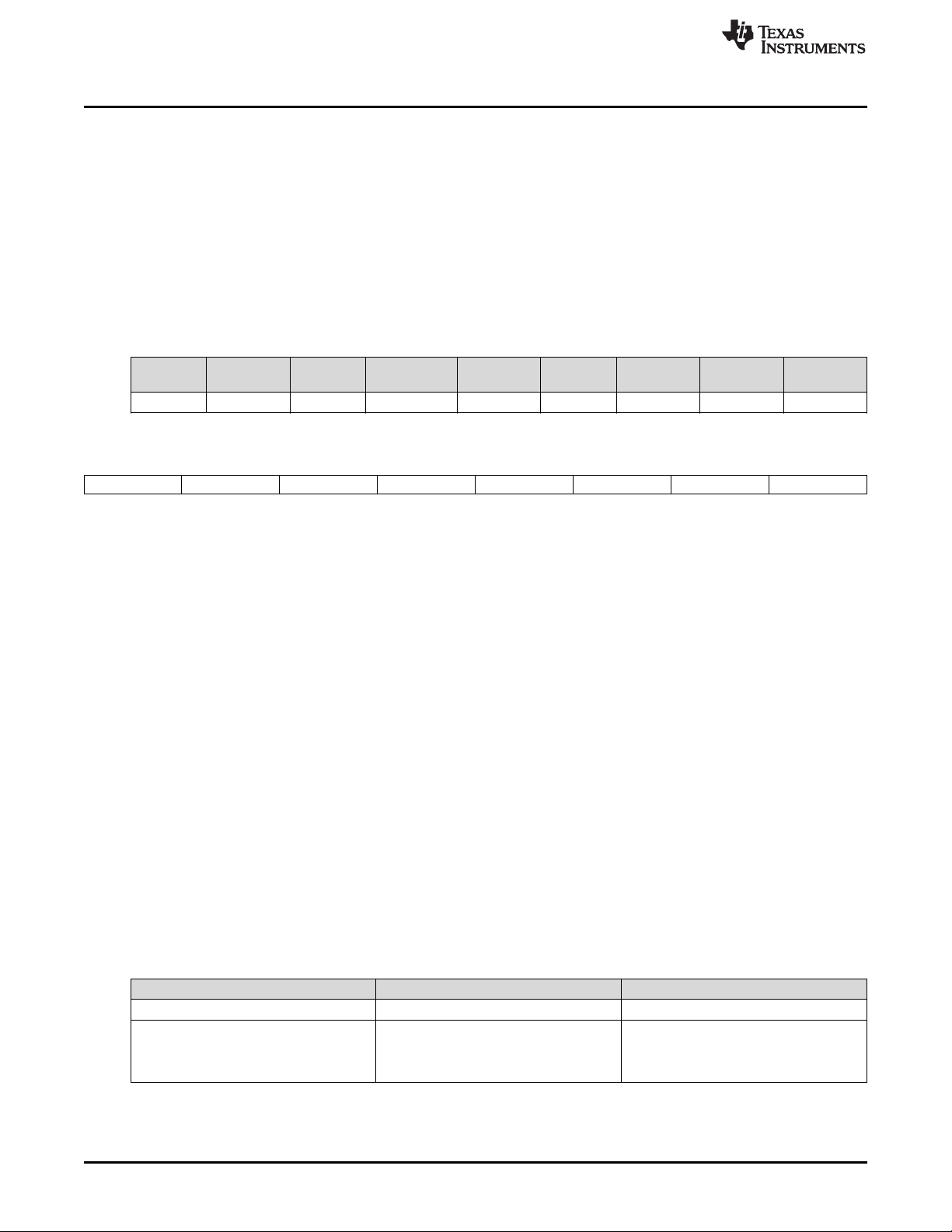

T1

Temperature()

Under Temp

TempRange() [UT]=1

Low Temp

TempRange() [LT]=1

Standard Temp

TempRange() [ST]=1

High Temp

TempRange() [HT]=1

Over Temp

TempRange() [OT]=1

T2

T3 T4

Temperature() > Charge

Inhibit / Suspend Low Temp

+ Hysteresis Temp

Temperature() < Charge

Inhibit / Suspend Low Temp

Temperature() > Pre Charge

Temp + Hysteresis Temp

Temperature() < Pre Charge

Temp

Temperature() > Charge

Inhibit High Temp+

Hysteresis Temp

Temperature() > Charge

Suspend High Temp+

Hysteresis Temp

Temperature() < Charge

Inhibit High Temp

Temperature() < Charge

Suspend High Temp

www.ti.com

Temperature Ranges

Figure 2-1. Temperature Mode

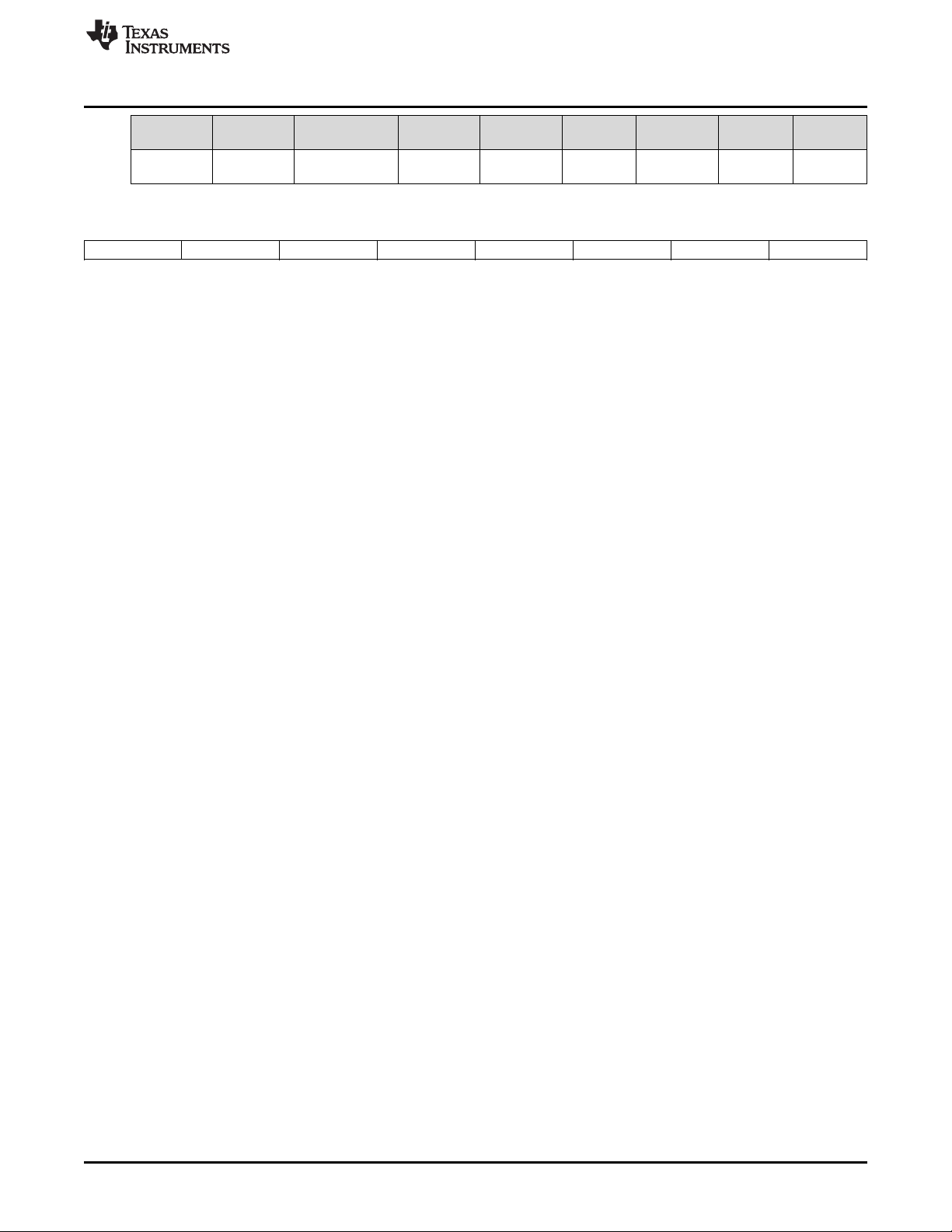

7 6 5 4 3 2 1 0

RSVD RSVD RSVD RSVD RSVD TSMode3 TSMode2 TSMode1

RSVD (Bits 7–3): Reserved

TSMode3 (Bit 2): Select TS3 sensor for Cell or FET Temperature Protection

0 = Use for Cell (default)

1 = Use for FETTemperature()

TSMode2 (Bit 1): Select TS2 sensor for Cell or FET Temperature Protection

0 = Use for Cell (default)

1 = Use for FETTemperature()

TSMode1 (Bit 0): Select TS1 sensor for Cell or FET Temperature Protection

0 = Use for Cell (default)

1 = Use for FETTemperature()

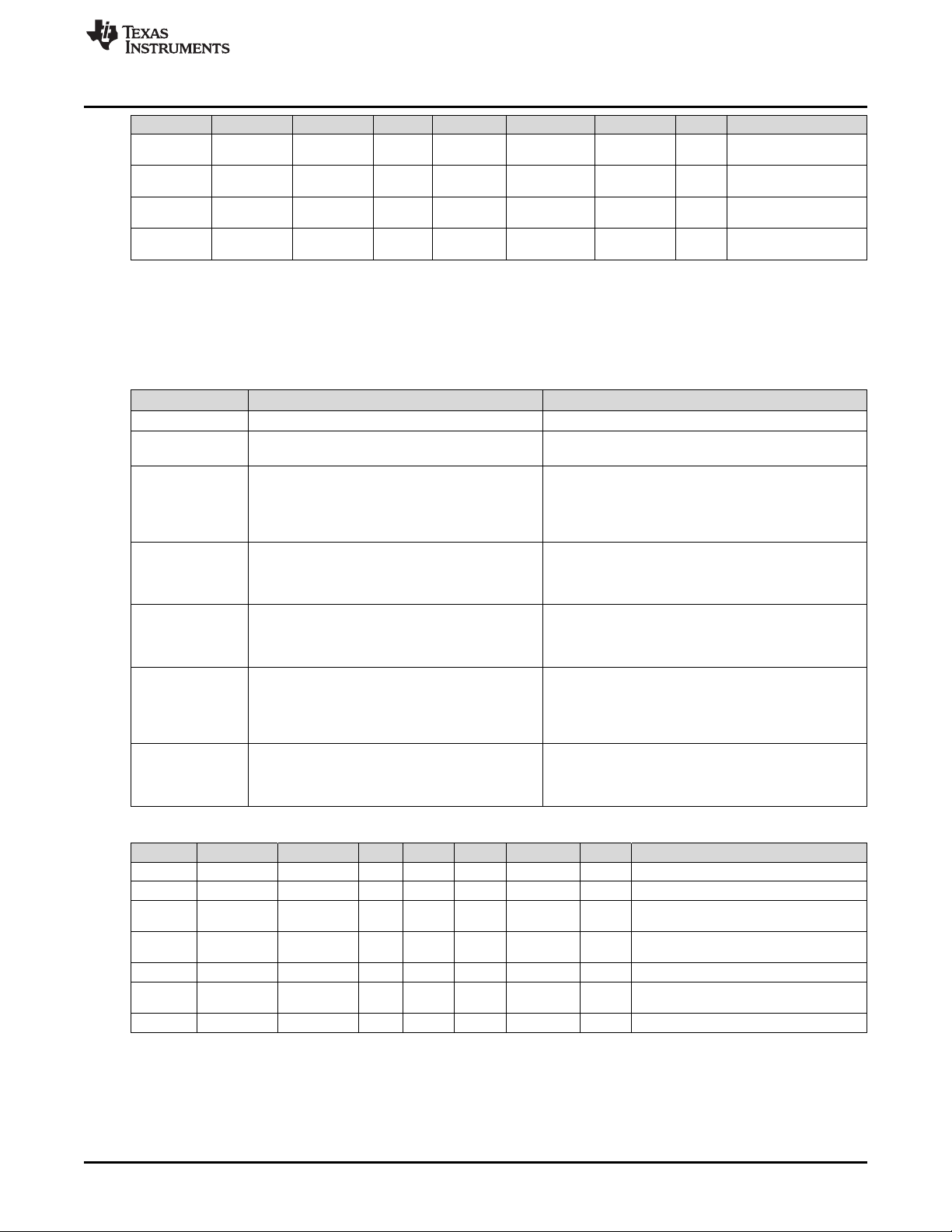

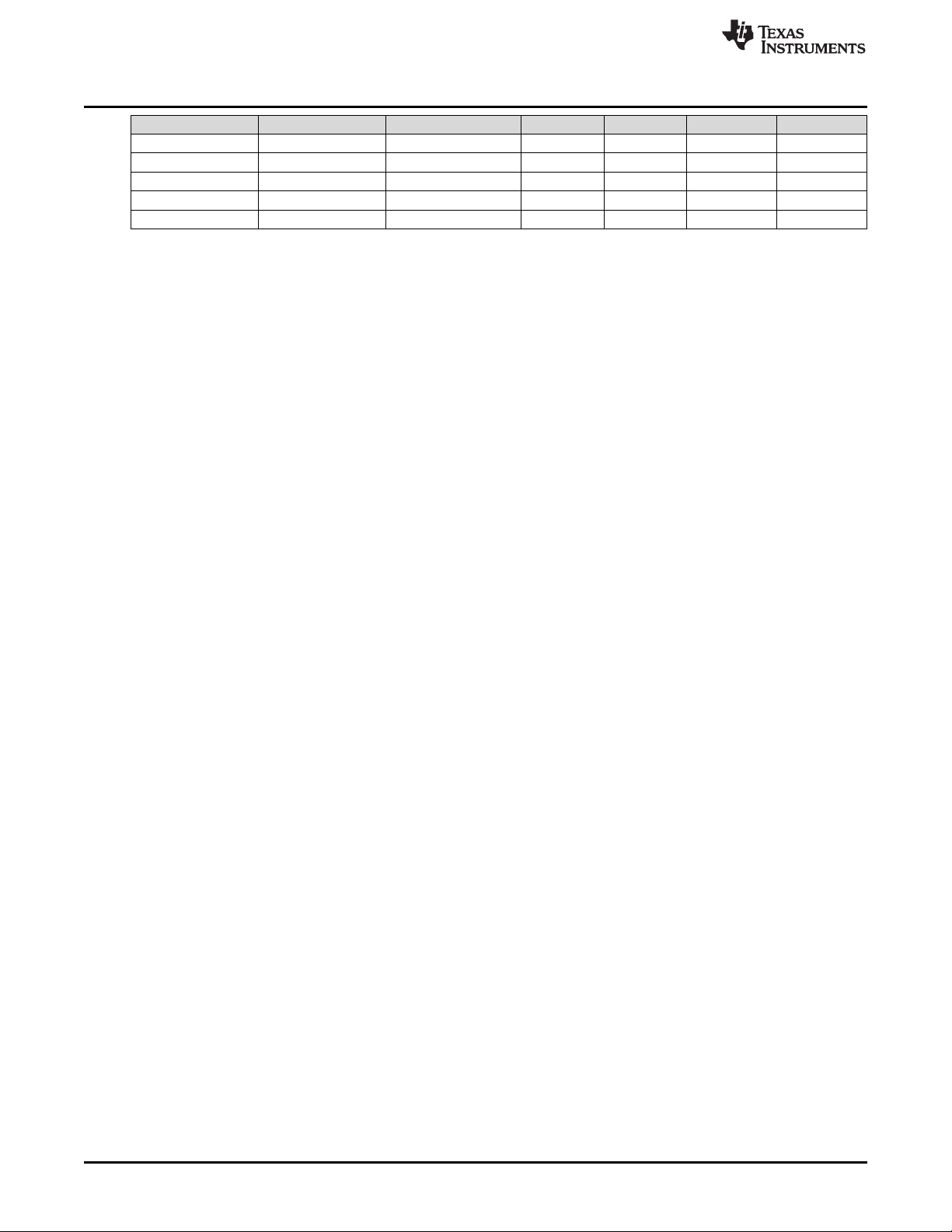

2.5 Temperature Ranges

The measured temperature is segmented into several temperature ranges. The bq78350-R1 uses these

as indication, and, for Lifetime Data Logging, the time spent in each range. The temperature ranges set in

data flash should adhere to the following format:

T1 ≤ T2 ≤ T3 ≤ T4

2.6 Basic Configuration Options

2.6.1 DA Configuration

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Figure 2-2. Data Flash Temperature Range Format

See the Temperature Ranges data flash subclass for details on the specific data flash variables.

There are a variety of options available in the bq78350-R1 and the companion AFE that influence the

startup conditions, system configuration, and the data measurement system.

This register is used to configure the setup of various measurement features of the bq78350-R1.

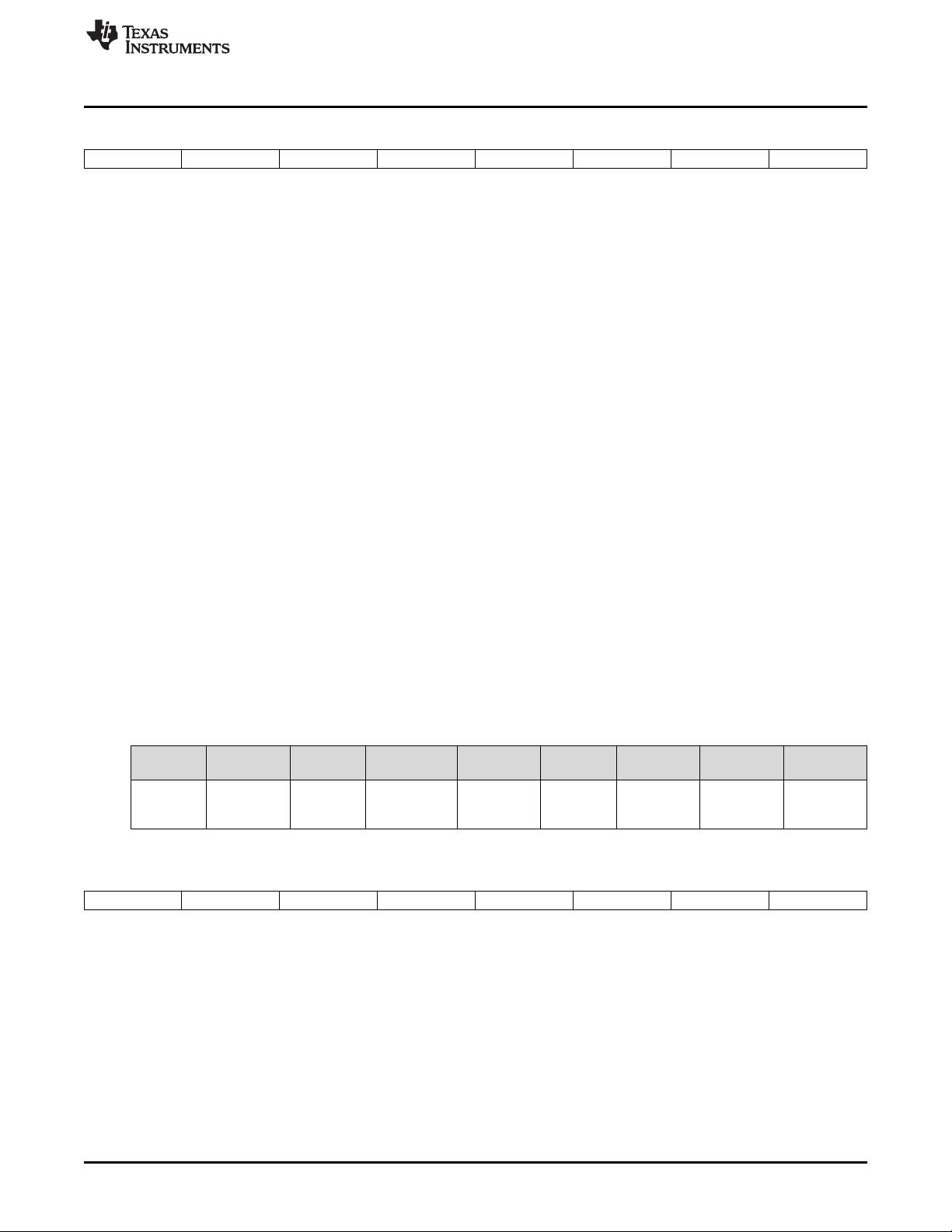

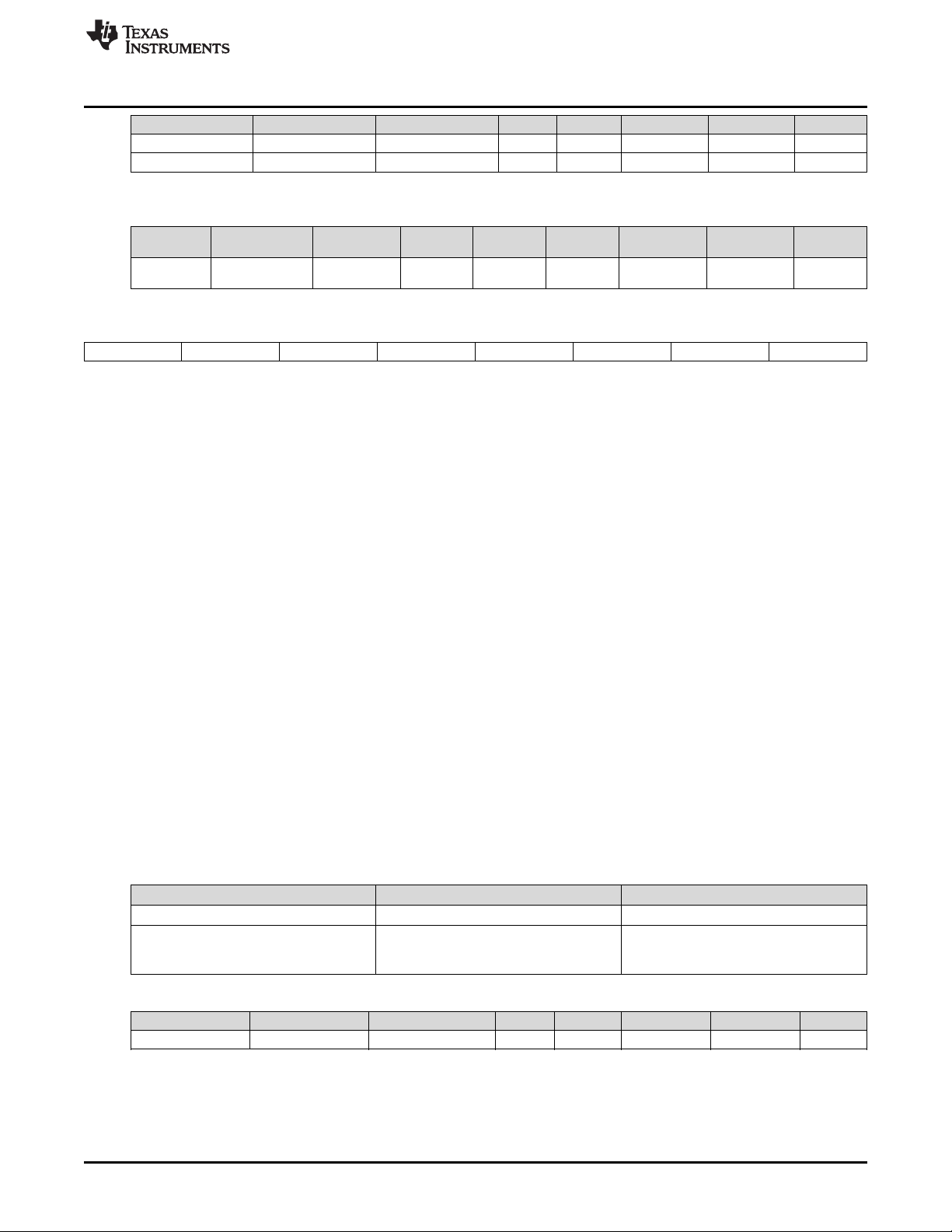

Class Subclass Name Format

Settings Configuration

Configuration

DA

Copyright © 2015–2018, Texas Instruments Incorporated

hex 1 0x00 0xFF 0x11 —

Size in

Bytes

Min Max Default Unit

Basic Measurement System

13

Page 14

Basic Configuration Options

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Low Byte FTEMP CTEMP RSVD ExtAveEN VAUXEN VAUX_SCALE

FTEMP (Bit 7): FET Temperature Protection Source

0 = Maximum of external available sources (default)

1 = Average of external available sources

CTEMP (Bit 6): Cell Temperature Protection Source

0 = Maximum of external available sources (default)

1 = Average of external available sources

RSVD (Bit 5): Reserved

ExtAveEN (Bit 4): Enables the bq78350-R1 to measure the BAT input

0 = BAT input is not measured.

1 = BAT input is measured and made available via ExtAveCellVoltage() (default).

VAUXEN (Bit 3): Enables the bq78350-R1 to measure the VAUX input

0 = VAUX input is not measured (default).

1 = VAUX input is measured and made available via VAUXVoltage().

VAUX_SCALE (Bit 2): Enables the bq78350-R1 to scale the VAUXVoltage() data by 10. For example:

Units are 10 mV rather than 1 mV.

0 = VAUXVoltage() is not scaled (resolution is 1 mV) (default).

1 = VAUXVoltage() is scaled (resolution is 10 mV).

IN_SYSTEM_SLEEP (Bit 1): IN SYSTEM SLEEP mode

1 = Enable

0 = Disable (default)

SLEEP (Bit 0): Enables the bq78350-R1 to enter SLEEP mode.

0 = The bq78350-R1 never enters SLEEP mode.

1 = The bq78350-R1 enters SLEEP mode under normal sleep entry criteria (default).

IN_SYSTEM_

SLEEP

www.ti.com

SLEEP

2.6.2 FET Options

This register configures the various FET control options.

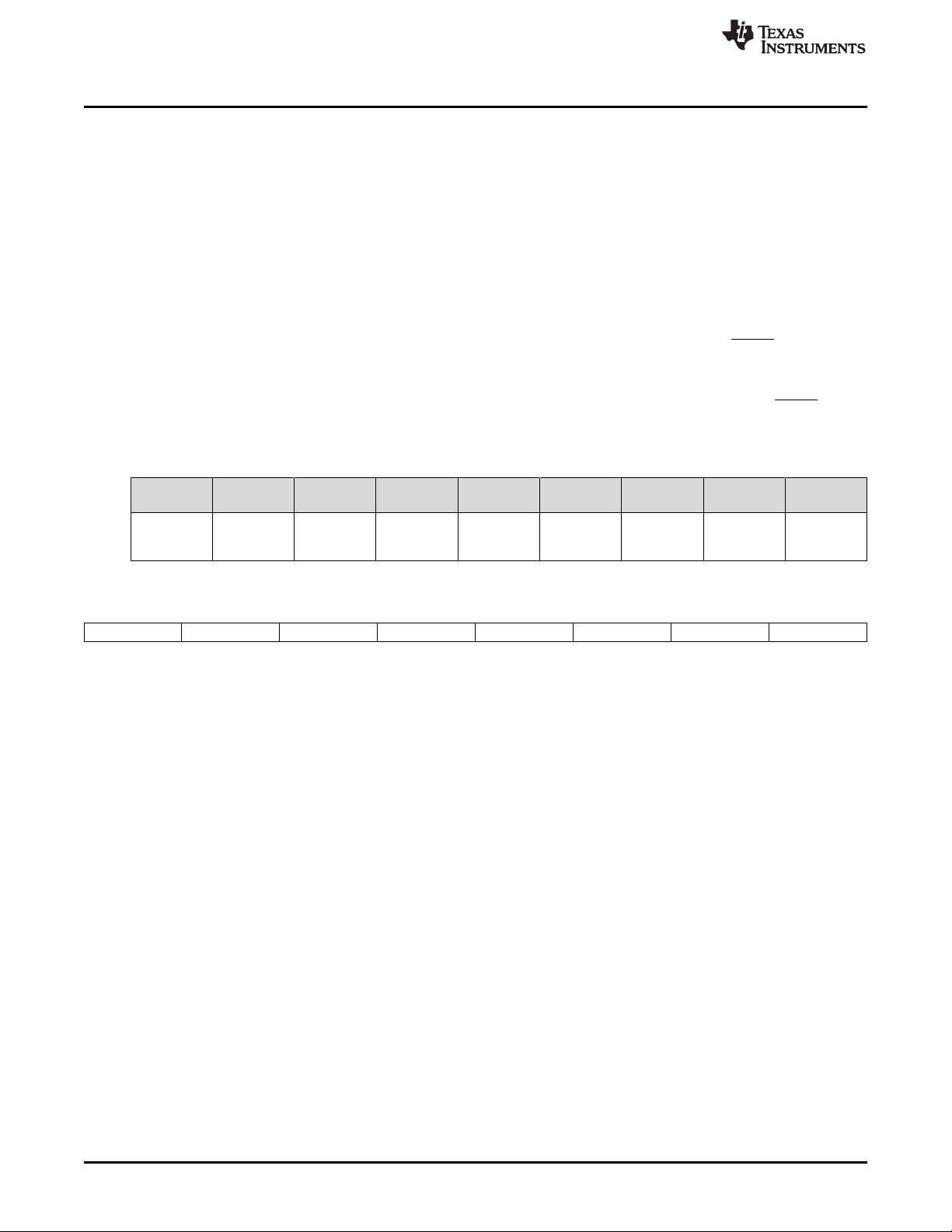

Class Subclass Name Format

Settings Configuration FET Options hex 2 0x0000 0xFFFF 0x0021 —

High Byte RSVD RSVD RSVD RSVD RSVD RSVD KEY_POL PCHG_POL

Low Byte RSVD SLEEPCHG CHGFET CHGIN CHGSU OTFET KEY_EN PCHG_EN

RSVD (Bits 7–2): Reserved

KEY_POL: This bit configures the KEYIN input detection polarity.

0 = KEYIN detection is active low (default).

1 = KEYIN detection is active high.

PCHG_POL: Configures the bq78350-R1 PRECHG pin output polarity. If PCHG_EN = 0, then this bit

has no influence.

14

Basic Measurement System

Size in

Bytes

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Copyright © 2015–2018, Texas Instruments Incorporated

Min Max Default Unit

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 15

www.ti.com

Basic Configuration Options

0 = The bq78350-R1 configures the PRECHG as active low (default).

1 = The bq78350-R1 configures the PRECHG as active high, requiring an external pullup.

SLEEPCHG: CHG FET is enabled during SLEEP.

0 = CHG FET off during SLEEP (default).

1 = CHG FET remains on during SLEEP.

CHGFET: FET action on valid charge termination

0 = FET active

1 = Charging and Precharging disabled, FET off (default)

CHGIN: FET action in CHARGE INHIBIT mode

0 = FET active (default)

1 = Charging and Precharging disabled, FETs off

CHGSU: FET action in CHARGE SUSPEND mode

0 = FET active (default)

1 = Charging and Precharging disabled, FETs off

OTFET: FET action in OVERTEMPERATURE mode

0 = No FET action for overtemperature condition (default)

1 = CHG and DSG FETs will be turned off for overtemperature conditions.

KEY_EN: Enables the bq78350-R1 to use the KEYIN pin function

0 = The bq78350-R1 never uses KEYIN (default).

1 = The bq78350-R1 KEYIN is used to control the DSG FET.

PCHG_EN: Enables the bq78350-R1 to use the PRECHG pin during PRECHARGE mode

0 = The bq78350-R1 never uses PRECHG.

1 = The bq78350-R1 controls PRECHG under normal charge control algorithm (default).

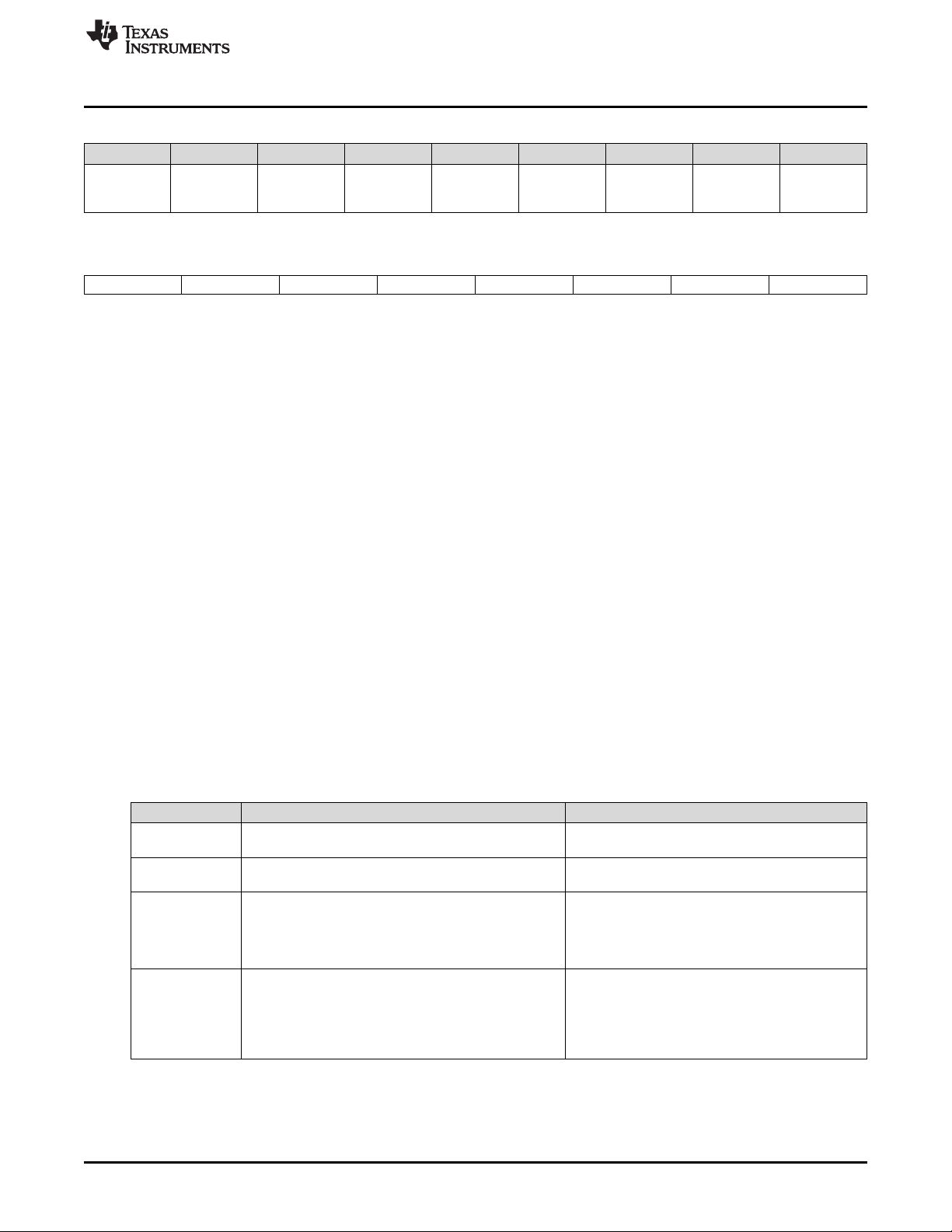

2.6.3 AFE Cell Map

This register maps the cells connected to the companion AFE so that the bq78350-R1 knows cells are

present at the indicated VCx channel.

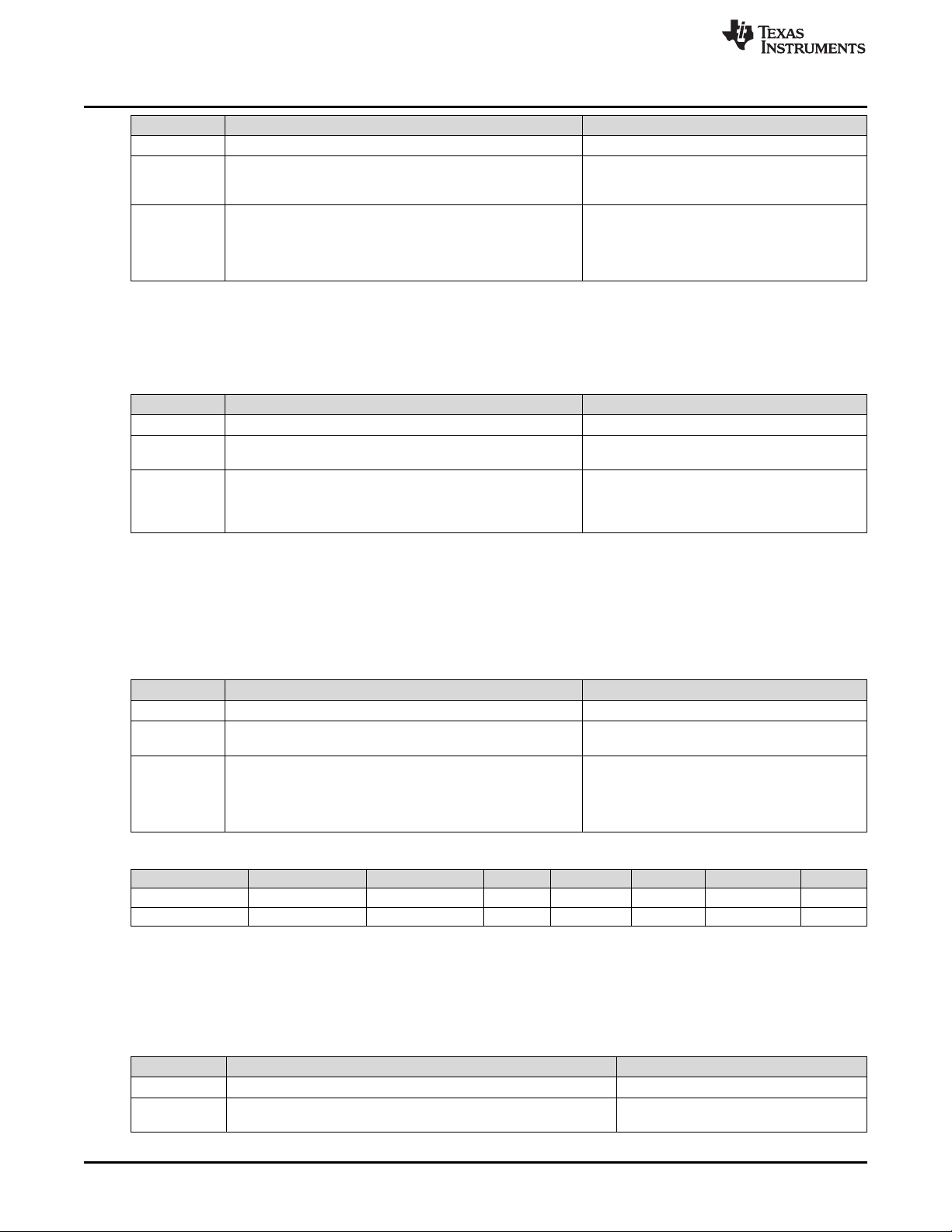

Class Subclass Name Format

Configuration AFE

High Byte RSVD VC15 VC14 VC13 VC12 VC11 VC10 VC9

Low Byte VC8 VC7 VC6 VC5 VC4 VC3 VC2 VC1

RSVD (Bit 7): Reserved

VCx: Cell connected to this node

1 = A cell is connected to this node and valid measurements are expected.

0 = A cell is NOT connected to this node.

Size in

Bytes

AFE Cell

Map

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

hex 2 0x0000 0xFFFF 0x0013 —

Min Max Default Unit

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Basic Measurement System

15

Page 16

Basic Configuration Options

The bq78350-R1 determines which companion AFE is connected by the total number of cells connected.

• When Series Cells = 3 to 5, the bq76920 companion AFE is used.

• When Series Cells = 6 to 10, the bq76930 companion AFE is used.

• When Series Cells = 9 to 15, the bq76940 companion AFE is used.

www.ti.com

16

Basic Measurement System

SLUUBD3D–September 2015–Revised September 2018

Copyright © 2015–2018, Texas Instruments Incorporated

Submit Documentation Feedback

Page 17

3.1 Introduction

The bq78350-R1 supports a wide range of battery and system protection features that are easily

configured or enabled via the integrated data flash. All of the protection items can be enabled or disabled

under Settings:Enable Protections A, Settings:Enable Protections B, and Settings:Enable

Protections C.

If the CHG FET is off and the gauge detects discharge current ≥ Dsg Current Threshold, then the CHG

FET is turned on to protect CHG FET body diode. The CHG FET is turned back off once discharge current

is removed. If the DSG FET is off and the gauge detects charge current ≥ Chg Current Threshold, then

the DSG FET is turned on to protect the DSG FET body diode. The DSG FET is turned back off once

charge current is removed. Body diode protection is always active.

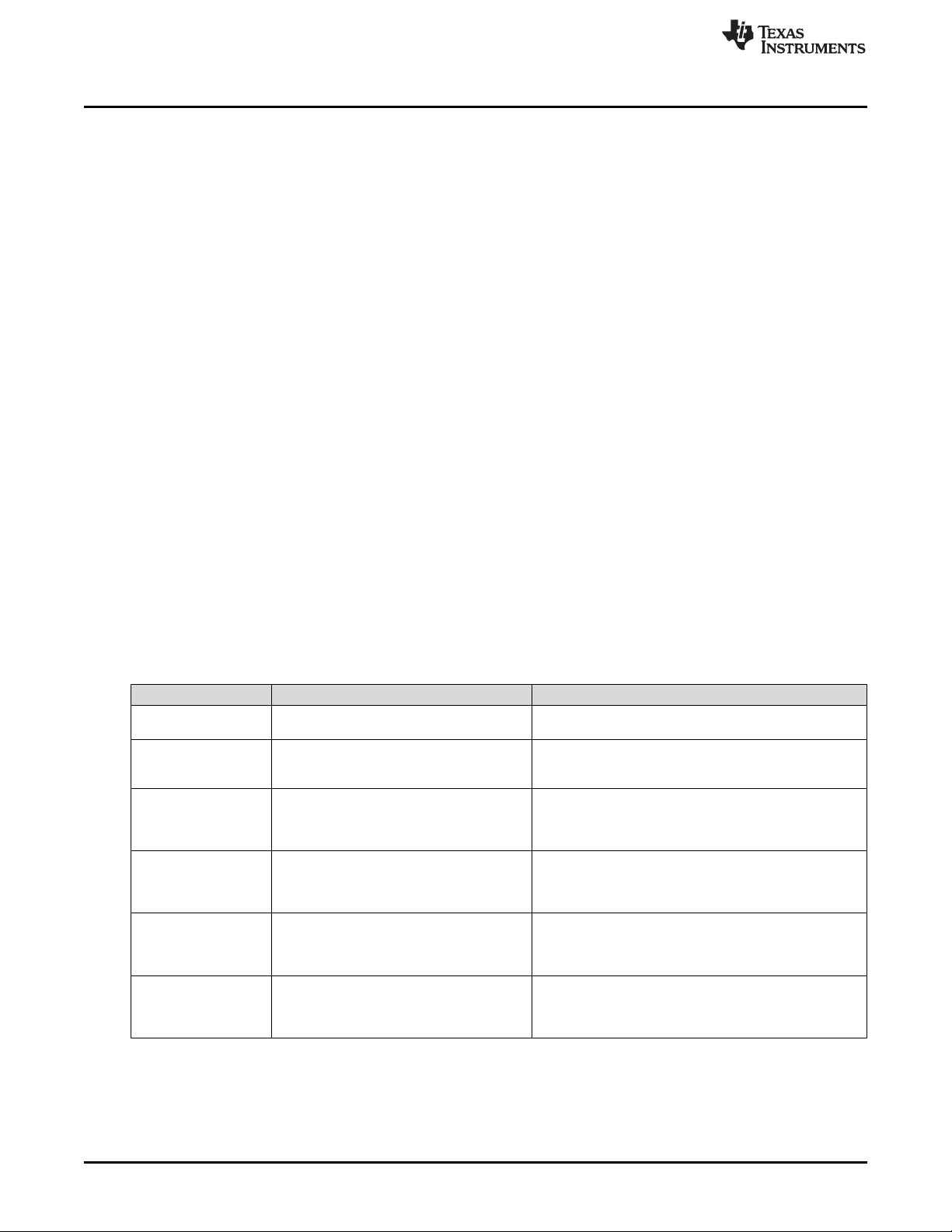

3.1.1 General Protections Configuration

Chapter 3

SLUUBD3D–September 2015–Revised September 2018

Protections

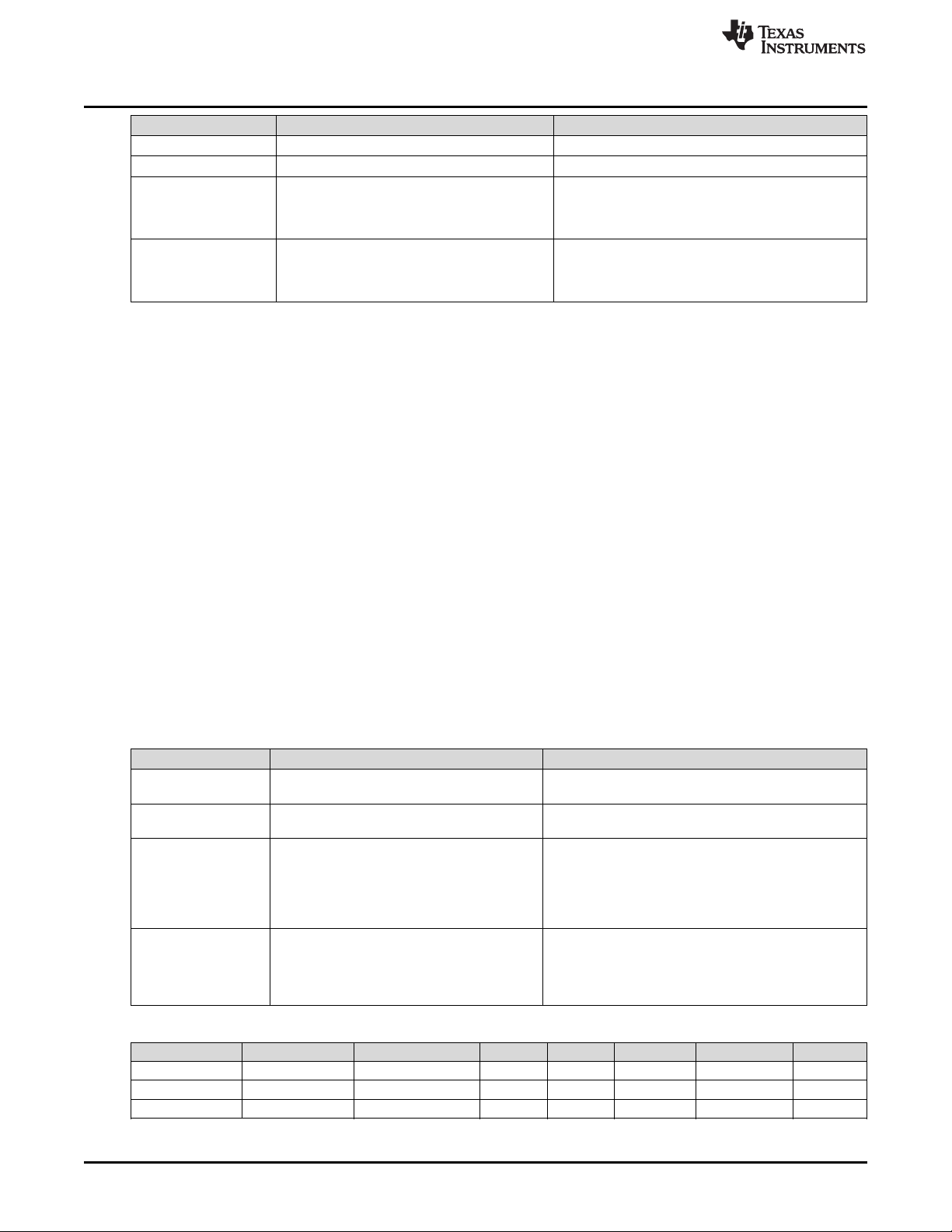

Class Subclass Name Format

Settings Protection

7 6 5 4 3 2 1 0

RSVD RSVD CC_DSG_OFF DC_CHG_OFF LPEN VAUXR

Protection

Configuration

Hex 1 0x00 0xFF 0x00 —

Size in

Bytes

Min Max Default Unit

CUV_RECOV_

CHG

RSVD (Bits 7–6): Reserved

CC_DSG_OFF (Bit 5): Turns DSG FET OFF in current-based charge faults

0 = Disabled (default)

1 = Enabled

DC_CHG_OFF (Bit 4): Turns CHG FET OFF in current-based discharge faults

0 = Disabled (default)

1 = Enabled

LPEN (Bit 3): Protection recovery uses the LOAD_PRESENT flag in the AFE to determine discharge

fault recovery. LOAD_PRESENT should only be used in a low-side protection FET configuration.

0 = Disabled (default)

1 = Enabled

VAUXR (Bit 2): Protection recovery uses the VAUX input as charger present detection.

0 = Disabled (default)

1 = Enabled

CUV_RECOV_CHG (Bit 1): Requires charge to recover SafetyStatus()[CUV]

0 = Disabled (default)

1 = Enabled

RSVD (Bit 0): Reserved

RSVD

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Protections

17

Page 18

Introduction

3.1.2 Enabled Protections

www.ti.com

Class Subclass Name Format

Settings Protection

7 6 5 4 3 2 1 0

ASCDL ASCD AOLDL AOLD OCD OCC COV CUV

Enabled

Protections

A

Hex 1 0x00 0xFF 0xFF —

Size in

Bytes

Min Max Default Unit

ASCDL (Bit 7): Short Circuit in Discharge Latch

0 = Disabled

1 = Enabled

ASCD (Bit 6): Short Circuit in Discharge recovery. Detection of an ASCD fault cannot be disabled.

0 = Bypassed, auto recovers within 250 ms

1 = Enabled

AOLDL (Bit 5): Overload in Discharge Latch

0 = Disabled

1 = Enabled

AOLD (Bit 4): Overload in Discharge recovery. Detection of an AOLD fault cannot be disabled.

0 = Bypassed, auto recovers within 250 ms

1 = Enabled

OCD (Bit 3): Overcurrent in Discharge

0 = Disabled

1 = Enabled

OCC (Bit 2): Overcurrent in Charge

0 = Disabled

1 = Enabled

COV (Bit 1): Cell Overvoltage

0 = Disabled

1 = Enabled

CUV (Bit 0): Cell Undervoltage

0 = Disabled

1 = Enabled

18

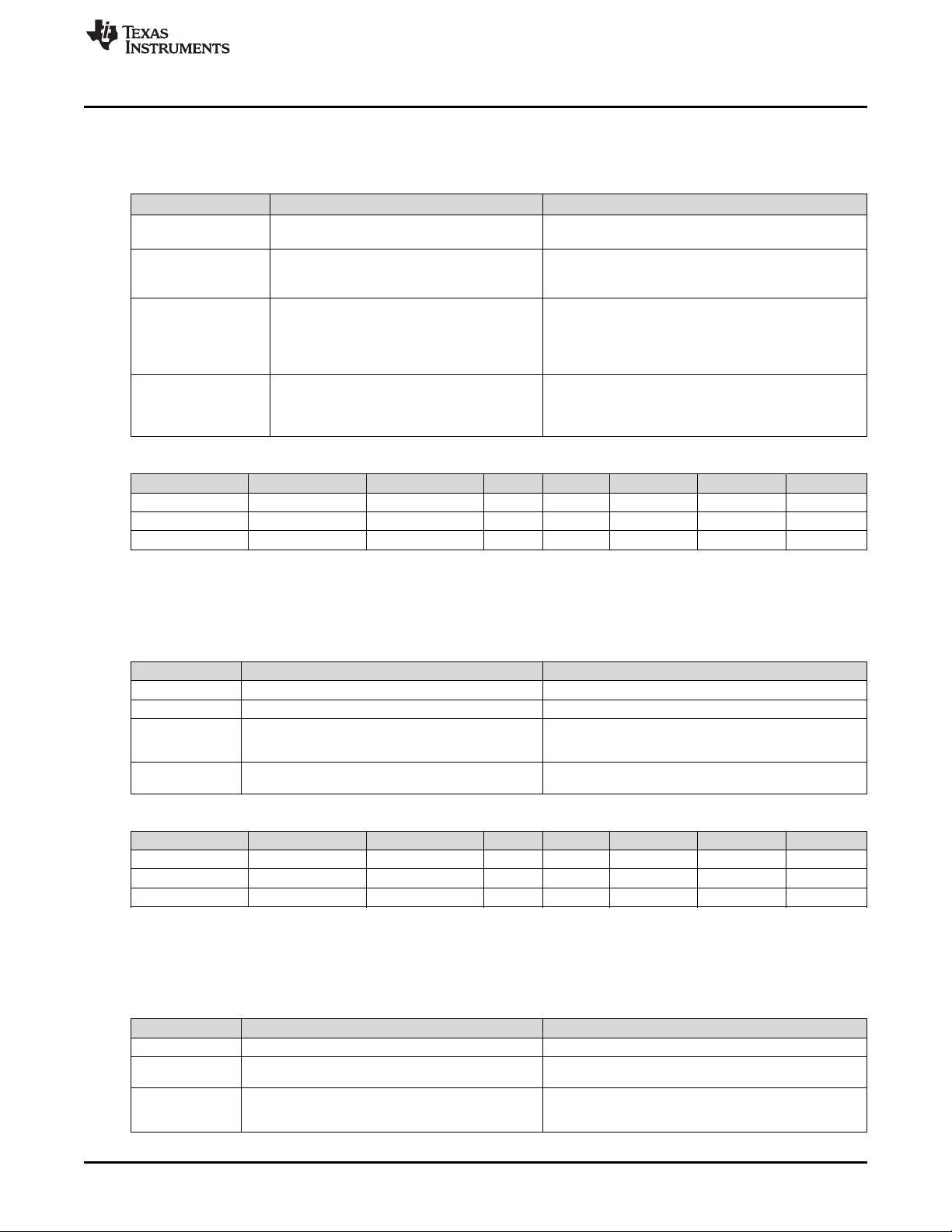

Class Subclass Name Format

Settings Protection

Protections

Enabled

Protections

B

Copyright © 2015–2018, Texas Instruments Incorporated

Size in

Bytes

Hex 1 0x00 0xFF 0x0F —

Min Max Default Unit

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Page 19

www.ti.com

7 6 5 4 3 2 1 0

RSVD OCDL OTF AFE_OVRD UTD UTC OTD OTC

RSVD (Bit 7): Reserved

OCDL (Bit 6): Overcurrent in Discharge Latch

0 = Disabled (default)

1 = Enabled

OTF (Bit 5): Overtemperature Fault

0 = Disabled (default)

1 = Enabled

AFE_OVRD (Bit 4): AFE ALERT

0 = Disabled (default)

1 = Enabled

UTD (Bit 3): Undertemperature in Discharge

0 = Disabled

1 = Enabled

UTC (Bit 2): Undertemperature in Charge

0 = Disabled

1 = Enabled

OTD (Bit 1): Overtemperature in Discharge

0 = Disabled

1 = Enabled

OTC (Bit 0): Overtemperature in Charge

0 = Disabled

1 = Enabled

Introduction

Class Subclass Name Format

Settings Protection

7 6 5 4 3 2 1 0

RSVD RSVD RSVD OC CTOS CTO PTOS PTO

Enabled

Protections

C

Hex 1 0x00 0xFF 0x15 —

Size in

Bytes

Min Max Default Unit

RSVD (Bits 7–5): Reserved. Do not use.

OC (Bit 4): Overcharge

0 = Disabled

1 = Enabled

CTOS (Bit 3): Charging Timeout Suspended

0 = Disabled

1 = Enabled

CTO (Bit 2): Charging Timeout

0 = Disabled

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Protections

19

Page 20

Introduction

1 = Enabled

PTOS (Bit 1): Precharging Timeout Suspend

0 = Disabled

1 = Enabled

PTO (Bit 0): Precharging Timeout

0 = Disabled

1 = Enabled

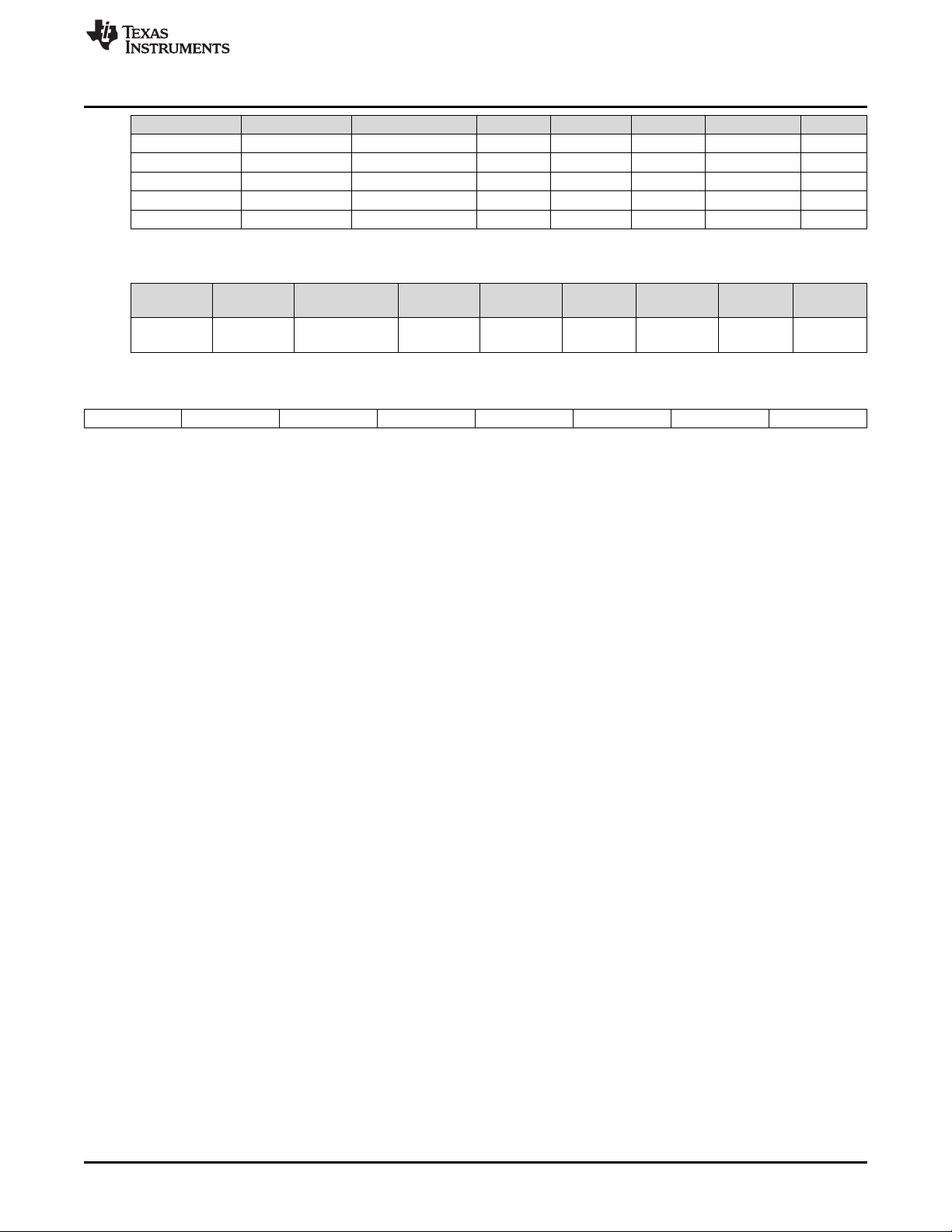

3.1.3 Enabled Removal Recovery

The bq78350-R1 offers the option to recover current-based protection by detecting the PRES pin transition

from high to low; for example, the pack is removed and re-inserted into the system.

To enable the replacement recovery, the appropriate bit in Enable Removable Recovery A and Enable

Removable Recovery B should be set. When the bit is set, then the high to low transition of PRES

becomes the only recovery method.

www.ti.com

Table 3-1. Enabled Removal Recovery A

Class Subclass Name Format

Settings Protection

7 6 5 4 3 2 1 0

ASCDL ASCD AOLDL AOLD OCD OCC RSVD RSVD

Enable

Removable

Recovery A

Hex 1 0x00 0xff 0x00 —

Size in

Bytes

Min Max Default Unit

ASCDL (Bit 7): ASCDL Protection Removal recovery

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

ASCD (Bit 6): ASCD Protection Removal recovery

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

AOLDL (Bit 5): AOLDL Protection Removal recovery

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

AOLD (Bit 4): AOLD Protection Removal recovery

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

OCD (Bit 3): Precharging Timeout

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

OCC (Bit 2): OCC Protection Removal recovery

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

RSVD (Bits 1–0): Reserved. Do not use.

20

Protections

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Page 21

www.ti.com

Table 3-2. Enabled Removal Recovery B

Class Subclass Name Format Size in Bytes Min Max Default Unit

Settings Protection

7 6 5 4 3 2 1 0

RSVD OCDL RSVD RSVD RSVD RSVD RSVD RSVD

Enable

Removable

Recovery B

Hex 1 0x00 0xff 0x00 —

RSVD (Bit 7): Reserved. Do not use.

OCDL (Bit 6): OCDL Protection Removal recovery

0 = Standard recovery only enabled (default)

1 = Removal recovery only enabled

RSVD (Bits 5–0): Reserved. Do not use.

3.1.4 FET Action Options for Current Protections

The bq78350-R1 offers the option to turn off the CHG FET during an overcurrent in discharge (OCD),

overcurrent in discharge latch (OCDL), overload (AOLD), overload latch (AOLDL) or short circuit in

discharge (ASCD), short circuit in discharge latch (ASCDL) faults, or the DSG FET in overcurrent in

charge (OCC) faults.

The CHG FET will turn off for the OCD, OCDL, AOLD, AOLDL, ASCD, and ASCDL faults when

[DC_CHG_OFF] in Protection Configuration is set.

The DSG FET will turn off for the OCC faults when [CC_DSG_OFF] in Protection Configuration is set.

Introduction

3.2 Cell Undervoltage Protection

The device can detect undervoltage in batteries and protect cells from damage by preventing further

discharge.

Upon CUV detection, a snapshot of the measured cell voltages are made available in CUVSnapshot().

This snapshot is available until the next instance of a CUV fault, as this causes the data to be updated to

the latest set of measurements.

Status Condition Action

Normal All Cell voltages in CellVoltage1..15() > CUV:Threshold

Alert

Trip

Recovery

Any Cell voltages in CellVoltage1..15() ≤

CUV:Threshold

Any Cell voltages in CellVoltage1..15() ≤

CUV:Threshold for CUV:Delay duration

SafetyStatus()[CUV] = 1 AND

All Cell voltages in CellVoltage1..15() ≥ CUV:Recovery

AND

Protection Configuration[CUV_RECOV_CHG] = 0 OR

[CUV_RECOV_CHG] = 1

AND Charging detected (that is, BatteryStatus[DSG] = 0)

SafetyAlert()[CUV] = 0

BatteryStatus()[TDA] = 0

SafetyAlert()[CUV] = 1

BatteryStatus()[TDA] = 1

SafetyAlert()[CUV] = 0

SafetyStatus()[CUV] = 1

BatteryStatus()[FD] = 1

OperationStatus()[XDSG] = 1

Discharging is not allowed.

SafetyStatus()[CUV] = 0

BatteryStatus()[FD] = 0, [TDA] = 0

OperationStatus()[XDSG] = 0

Discharging is allowed.

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Protections

21

Page 22

Cell Overvoltage Protection

Class Subclass Name Type Min Max Default Unit

Protections CUV Threshold I2 0 5000 2500 mV

Protections CUV Delay U1 0 255 2 s

Protections CUV Recovery I2 0 5000 3000 mV

3.3 Cell Overvoltage Protection

The device can detect cell overvoltage in batteries and protect cells from damage by preventing further

charging.

Upon COV detection, a snapshot of the measured cell voltages are made available in COVSnapshot().

This snapshot is available until the next instance of a COV fault, as this causes the data to be updated to

the latest set of measurements.

Status Condition Action

Normal All voltages in CellVoltage1..15() < COV:Threshold SafetyAlert()[COV] = 0

Alert Any voltage in CellVoltage1..15() ≥ COV:Threshold

Trip

Recovery

Recovery

Any voltage in CellVoltage1..15() ≥ COV:Threshold

continuous ≥ COV:Threshold for COV:Delay duration

SafetyStatus()[COV] = 1 AND Protection

Configuration:VAUXR = 0

all voltages in CellVoltage1..15() ≤ COV:Recovery

SafetyStatus()[COV] = 1 AND Protection

Configuration:VAUXR = 1

all voltages in CellVoltage1..15() ≤ COV:Recovery AND

VAUXVoltage() < Power:Charger Present Threshold

www.ti.com

SafetyAlert()[COV] = 1

BatteryStatus()[TCA] = 1

SafetyAlert()[COV] = 0

SafetyStatus()[COV] = 1

BatteryStatus()[TCA] = 0

SafetyStatus()[COV] = 0

BatteryStatus()[TCA] = 0

SafetyStatus()[COV] = 0

BatteryStatus()[TCA] = 0

Class Subclass Name Type Min Max Default Unit

Protections COV Threshold I2 0 32767 4300 mV

Protections COV Delay U1 0 255 2 s

Protections COV Recovery I2 0 32767 4100 mV

3.4 Overcurrent in Charge Protection

The device has overcurrent in charge protection that can be configured to specific current and delay

thresholds to accommodate charging behaviors. See Section 3.1.4 for additional FET action options.

Status Condition Action

Normal Current() < OCC:Threshold SafetyAlert()[OCC] = 0

Alert Current() ≥ OCC:Threshold

Trip

Recovery

Current() continuous ≥ OCC:Threshold for

OCC:Delay duration

[SafetyStatus()[OCC] = 1 AND

Current() continuous ≤ OCC:Recovery Threshold

for OCC:Recovery Delay time

SafetyAlert()[OCC] = 1

BatteryStatus()[TCA] = 1

SafetyAlert()[OCC] = 0

SafetyStatus()[OCC] = 1

BatteryStatus()[TCA] = 0

OperationStatus()[XCHG] = 1

Charging is not allowed.

SafetyStatus()[OCC] = 0

BatteryStatus()[TCA] = 0

OperationStatus()[XCHG] = 0

Charging is allowed.

22

Protections

SLUUBD3D–September 2015–Revised September 2018

Copyright © 2015–2018, Texas Instruments Incorporated

Submit Documentation Feedback

Page 23

www.ti.com

Class Subclass Name Type Min Max Default Unit Description

Protections OCC Threshold I2 –32768 32767 6000 mA

Protections OCC Delay U1 0 255 6 s

Protections OCC

Protections OCC

Recovery

Threshold

Recovery

Delay

I2 –32768 32767 –200 mA

U1 0 255 5 s

3.5 Overcurrent in Discharge Protection

The device has two independent overcurrent in discharge protections that can be set to different current

and delay thresholds to accommodate different load behaviors. See Section 3.1.4 for additional FET

action options.

Status Condition Action

Normal Current() > OCD:Threshold SafetyAlert()[OCDL] = 0, if OCDL counter = 0

Alert OCDL counter > 0

Trip

Latch OCDL counter ≥ OCD:Latch Limit

Recovery

Recovery

Latch Reset SafetyStatus()[OCDL] = 1 for OCD: Reset Time

Current() continuous ≤ OCD:Threshold for

OCD:Delay duration

[SafetyStatus()[OCD] = 1 AND Protection

Configuration:VAUXR = 0

Current() continuous ≥ OCD:Recovery Threshold

for OCD:Recovery Delay time

[SafetyStatus()[OCD] = 1 AND Protection

Configuration:VAUXR = 1

Current() continuous ≥ OCD:Recovery Threshold

for OCD:Recovery Delay time OR VAUXVoltage()

≥ Power:Charger Present Threshold

Overcurrent in Discharge Protection

Overcurrent in Charge trip

threshold

Overcurrent in Charge trip

delay

Overcurrent in Charge

recovery threshold

Overcurrent in Charge

recovery delay

SafetyAlert()[OCDL] = 1, Decrement OCDL counter by

one after each OCD:Counter Dec Delay period

SafetyAlert()[OCD] = 0

SafetyStatus()[OCD] = 1

OperationStatus()[XDSG] = 1

DSG FET is disabled.

Increment OCDL counter.

SafetyAlert()[OCDL] = 0

SafetyStatus()[OCDL] = 1

OperationStatus()[XDSG] = 1

DSG FET is disabled.

SafetyStatus()[OCD] = 0

OperationStatus()[XDSG] = 0

Discharging is allowed.

SafetyStatus()[OCD] = 0

OperationStatus()[XDSG] = 0

Discharging is allowed.

SafetyStatus()[OCDL] = 0

Reset OCDL counter

OperationStatus()[XDSG] = 0

DSG FET returns to normal if SafetyStatus()[OCD] = 0.

Class Subclass Name Type Min Max Default Unit Description

Protections OCD Threshold I2 –32768 32767 –6000 mA Overcurrent in Discharge trip threshold

Protections OCD Delay U1 0 255 6 s Overcurrent in Discharge trip delay

Protections OCD

Protections OCD

Protections OCDL Latch Limit U1 0 255 0 counts Overcurrent in Discharge latch limit

Protections OCDL

Protections OCDL Reset U1 0 255 15 s Overcurrent in Discharge latch reset delay

Recovery

Threshold

Recovery

Delay

Counter Dec

Delay

I2 –32768 32767 200 mA Overcurrent in Discharge recovery threshold

U1 0 255 5 s Overcurrent in Discharge recovery delay

U1 0 255 10 s

SLUUBD3D–September 2015–Revised September 2018

Submit Documentation Feedback

Copyright © 2015–2018, Texas Instruments Incorporated

Overcurrent in Discharge counter decrement

delay

Protections

23

Page 24

Hardware-Based Protection

3.6 Hardware-Based Protection

The bq78350-R1 device has two main hardware-based protections, AOLD and ASCD, with adjustable

current and delay time. Setting ASCD Threshold and Delay [RSNS] doubles the threshold value. It is

located in bit 8 of the ASCD Threshold Delay register. The Threshold settings are in mV; therefore, the

actual current that triggers the protection is based on the R

For details on how to configure the AFE hardware protection, refer to the tables in the companion data

manual, bq769x0 3-Series to 15-Series Cell Battery Monitor Family for Li-Ion and Phosphate Applications

(SLUSBK2).

All of the hardware-based protections provide a short term Trip/Alert/Recovery protection to account for a

current spike as well as a Trip/Alert/Latch protection for persistent faulty condition. The latch feature also

stops the FETs from toggling on and off continuously, preventing damage to the FETs.

In general, when a fault is detected after the Delay time, the DSG FET will be disabled. However, if

Protection Configuration [LPEN] is set, then both FETs are turned off (Trip stage), and an internal fault

counter will be incremented (Alert stage). As the DSG FET is turned off, the current will drop to 0 mA.

After Recovery time, the CHG and DSG FETs will be turned on again (Recovery stage) unless additional

recovery conditions are enabled.

If the alert is caused by a current spike, the fault count will be decremented after Counter Dec Delay

time. If this is a persistent faulty condition, the device will enter the Trip stage after Delay time, and repeat

the Trip/Alert/Recovery cycle. The internal fault counter is incremented every time the device goes through

the Trip/Alert/Recovery cycle. Once the internal fault counter hits the Latch Limit, the protection enters a

Latch stage and the fault will only be cleared through the Latch Reset condition. If Latch Limit is set to 0, it

will latch after the first detection.

The Trip/Alert/Recovery/Latch stages are documented in each of the following hardware-based protection

sections.

used in the schematic design.

SENSE

www.ti.com

3.6.1 Overload in Discharge Protection

The device has a hardware-based overload in discharge protection with adjustable current and delay. See

Section 3.1.4 for additional FET action options.

Status Condition Action

Normal

Alert AOLDL counter > 0

Trip

Latch AOLDL counter ≥ AOLD:Latch Limit

Recovery

Latch Reset

Current() > (AOLD Threshold and

Delay[3:0]/R

Current() continuous ≤ (AOLD Threshold

and Delay[3:0]/R

and Delay[6:4] duration

SafetyStatus()[AOLD] = 1 for

AOLD:Recovery time OR

If Protection Configuration [LPEN] = 1

AND AFEStatus()[LOAD_PRESENT]= 0

SafetyStatus()[AOLDL] = 1

for AOLD:Reset time

SENSE

)

SENSE

) for AOLD Threshold

SafetyAlert()[AOLDL] = 0, if AOLDL counter = 0

SafetyAlert()[AOLDL] = 1

Decrement AOLDL counter by one after each

AOLD:Counter Dec Delay period

SafetyStatus()[AOLD] = 1

OperationStatus()[XDSG] = 1

DSG FET is disabled.

Increment AOLDL counter

SafetyAlert()[AOLDL] = 0

SafetyStatus()[AOLDL] = 1

OperationStatus()[XDSG] = 1

DSG FET is disabled.

SafetyStatus()[AOLD] = 0

OperationStatus()[XDSG] = 0

DSG FET returns to normal if SafetyStatus[AOLDL] = 0.

SafetyStatus()[AOLDL] = 0

Reset AOLDL counter

OperationStatus()[XDSG] = 0

DSG FET returns to normal if SafetyStatus()[AOLD] = 0.

24

Protections

SLUUBD3D–September 2015–Revised September 2018

Copyright © 2015–2018, Texas Instruments Incorporated

Submit Documentation Feedback

Page 25

www.ti.com

This register is representative of the bq769x0 PROTECT 2 register.