Texas Instruments BQ4845YS-A4TR, BQ4845YS-A4NTR, BQ4845YS-A4N, BQ4845YS-A4, BQ4845YP-A4 Datasheet

...

bq4845/bq4845Y

Parallel RTC With CPU Supervisor

Features

➤ Real-Time Clock counts seconds

through years in BCD format

➤ On-chip battery-backup switchover

circuit with nonvolatile control for

external SRAM

➤ Less than 500nA of clock opera-

tion current in backup mode

➤ Microprocessor reset valid to

V

CC=VSS

➤ Independent watchdog timer

with a programmable time-out

period

➤ Power-failinterruptwarning

➤ Programmable clock alarm inter-

rupt active in battery-backup

mode

➤ Programmable periodic interrupt

➤ Battery-low warning

General Description

The bq4845 Real-Time Clock is a

low-power microprocessor peripheral that integrates a time-of-day

clock, a 100-year calendar, and a

CPU supervisor in a 28-pin SOIC or

DIP. The bq4845 is ideal for fax machines, copiers, industrial control

systems, point-of-sale terminals,

data loggers,andcomputers.

The bq4845 provides direct connections for a 32.768KHz quartz crystal

and a 3V backup battery. Through

the use of the conditional chip enable output (CE

voltage output (V

bq4845 can write-protect and make

nonvolatile external SRAMs. The

backup cell powers the real-time

clock and maintains SRAM information in the absence of system

voltage.

The bq4845 contains a temperaturecompensated reference and comparator

circuit that monitors the status of its

voltage supply . When the bq4845 de-

) and battery

OUT

) pins, the

OUT

tects an out-of-tolerance condition, it

generates an interrupt warning and

subsequently a microprocessor reset.

The reset stays active for 200ms after

V

rises within tolerance, to allow for

CC

power supply and processor stabilization.

The bq4845 also has a built-in

watchdog timer to monitor processor

operation. If the microprocessor does

not toggle the watchdog input (WDI)

within the programmed time-out period, the bq4845 asserts WDO

and

RST. WDI unconnected disables the

watchdogtimer.

The bq4845 can generate other interrupts based on a clock alarm condition or a periodic setting. The

alarm interrupt can be set to occur

from once per second to once per

month. The alarm can be made active

in the battery-backup mode to serve

as a system wake-up call. F or interrupts at a rate beyond once per second, the periodic interrupt can be programmed with periods of 30.5µsto

500ms.

Pin Connections

V

WDO

RST

DQ

Aug.1995

OUT

INT

DQ

DQ

V

X

1

X

2

A

3

A

2

A

1

A

0

0

1

2

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28-DIP or SOIC

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PN484501.eps

V

WE

CE

CE

BC

WDI

OE

CS

V

DQ

DQ

DQ

DQ

DQ

Pin Names

A0–A

CC

IN

OUT

DQ0–DQ7Data inputs/outputs

WE Write enable

OE Output enable

SS

7

8

5

4

3

CS Chip select input

CE

IN

CE

OUT

X1–X2 Crystal inputs

Clock/control address

3

inputs

External RAM chip

enable

Conditional RAM chip

enable

BC Backup battery input

V

OUT

Back-up battery output

INT Interrupt output

RST Microprocessor reset

WDI Watchdoginput

WDO Watchdogoutput

V

CC

V

SS

+5V supply

Ground

1

bq4845/bq4845Y

Functional Description

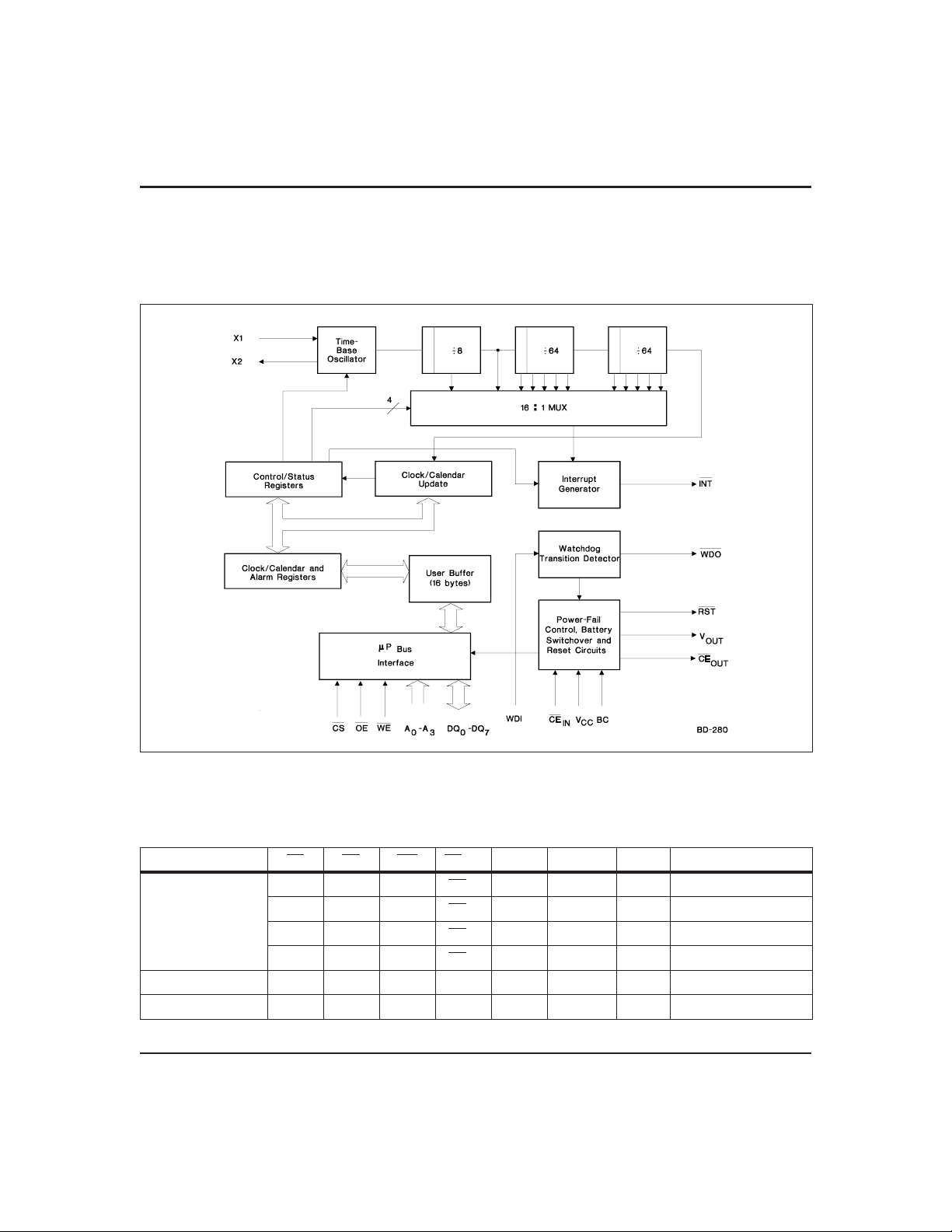

Figure 1 is a block diagram of the bq4845. The following sections describe the bq4845 functional operation

including clock interface, data-retention modes,

power-on reset timing, watchdog timer activation, and

interrupt generation.

Truth Table

V

CC

(max.) V

<V

CC

(min.) V

>V

CC

(min.) > V

<V

PFD

≤ V

SO

Figure 1. Block Diagram

CS OE WE CE

IH

V

IL

IL

V

IL

XXXVOHV

SO

XXXV

XXCEINV

XVILCE

V

V

V

IL

IH

IH

V

IH

V

OUT

V

IN

CE

CE

V

IN

V

IN

OHBVOUT2

2

OUT

OUT1

OUT1

OUT1

OUT1

OUT1

Mode DQ Power

Deselect High Z Standby

Write D

Read D

IN

OUT

Active

Active

Read High Z Active

Deselect High Z CMOS standby

Deselect High Z Battery-backup mode

Aug.1995

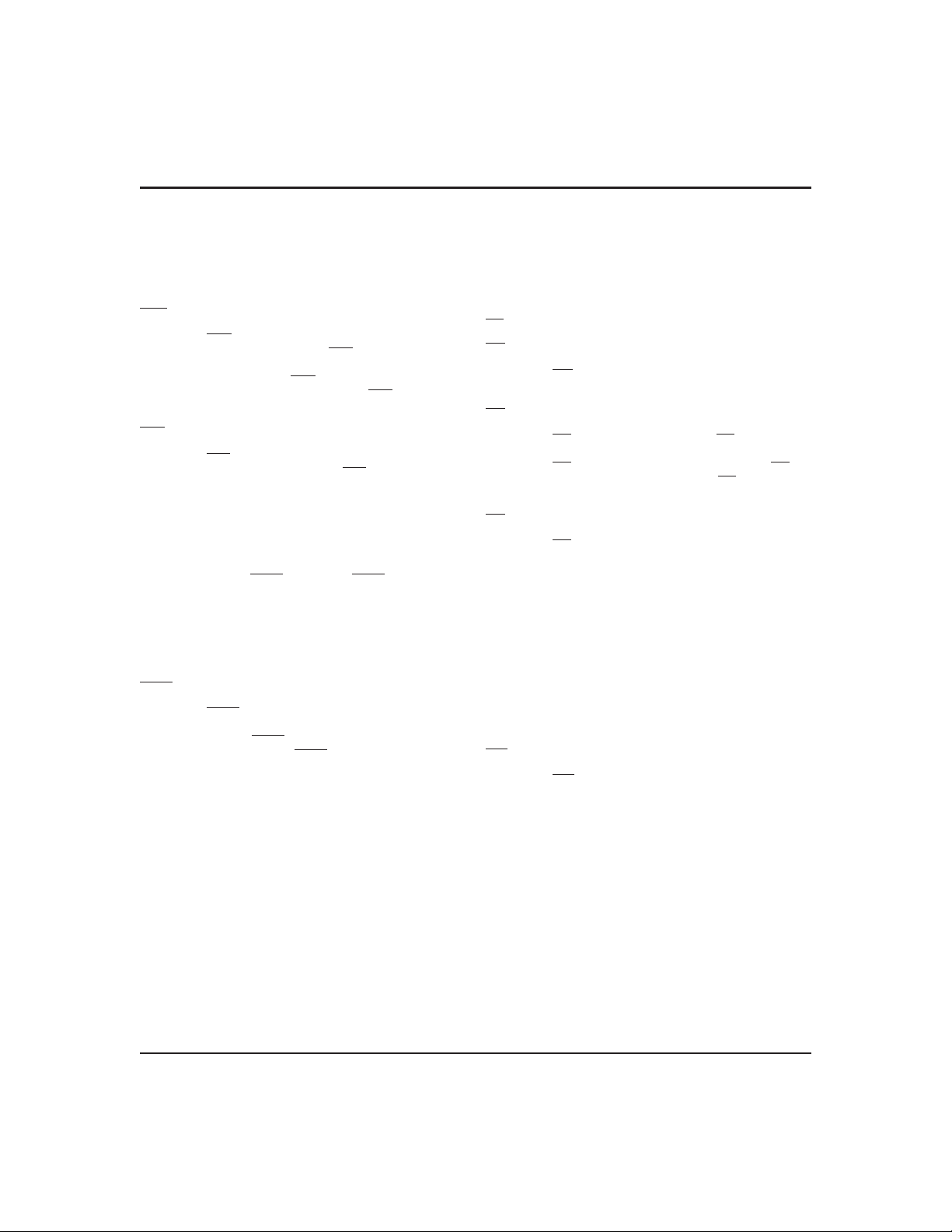

Pin Descriptions

X1–X2

RST

INT Interrupt output

WDI

WDO

A0–A

Crystal inputs

X1–X2 are a direct connection for a

32.768kHZ, 6pF crystal.

Reset output

RST goes low whenever VCCfalls below the

power fail threshold. RST will remain low for

200ms typical after VCCcrosses the threshold

on power-up. RST also goes low whenever a

watchdog timeout occurs. RST is an opendrain output.

INT goes low when a power fail, periodic, or

alarm condition occurs. INT is an open-drain

output.

Watchdog input

WDI is a three-level input. If WDI remains

either high or low for longer than the

watchdog time-out period (1.5 seconds default), WDO goes low. WDO remains low

until the next transition at WDI. Leaving

WDI unconnected disables the watchdog

function. WDI connects to an internal voltage divider between V

sets it to mid-supply when left unconnected.

Watchdog output

WDO goes low if WDI remains either high

or low longer than the watchdog time-out

period. WDO returns high on the next transition at WDI. WDO remains high if WDI is

unconnected.

Clock address inputs

3

A0–A3allow access to the 16 bytes of realtime clock and control registers.

and VSS, which

OUT

DQ

–DQ7Data input and output

0

DQ0–DQ7provide x8 data for real-time clock

information. These pins connect to the memory data bus.

V

CS

SS

Ground

Chip select

OE Outputenable

OE provides the read control for the RTC

memory locations.

CE

OUT

Chip enable output

CE

goes low only when CEINis low and

OUT

VCCis above the power fail threshold. If

CEINis low, and power fail occurs, CE

stays low for 100µs or until CEINgoes high,

whichever occurs first.

CE

IN

Chip enable input

CEINis the input to the chip-enable gating

circuit.

BC

Backup battery input

BC should be connected to a 3V backup

cell. A voltage within the VBCrange on the

BC pin should be present upon power up to

provide proper oscillator start-up.

V

OUT

Output supply voltage

V

provides the higher of VCCor VBC,

OUT

switched internally, to supply external

RAM.

WE

Write enable

WE provides the write control for the RTC

memory locations.

V

CC

Input supply voltage

+5V input

bq4845/bq4845Y

OUT

Aug.1995

3

bq4845/bq4845Y

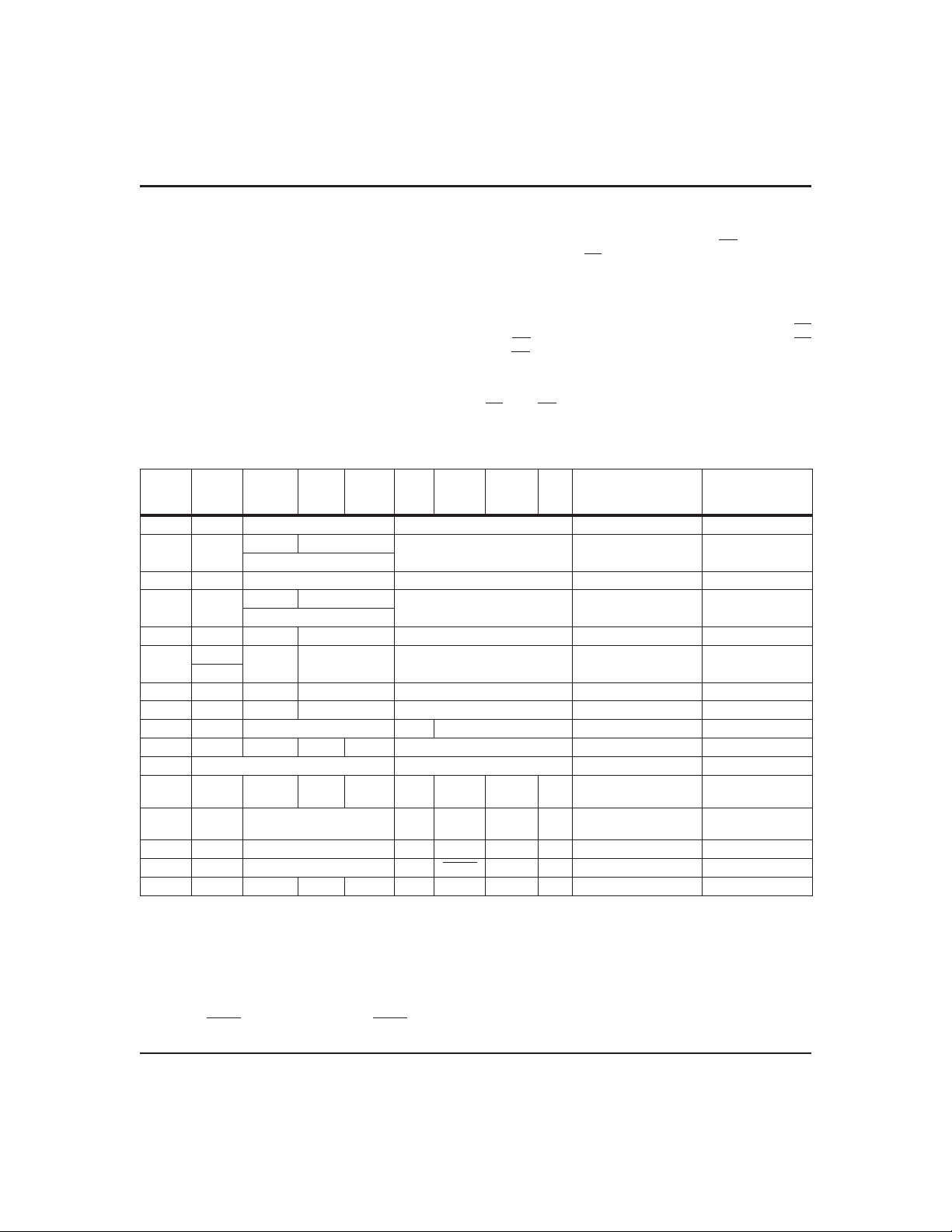

Address Map

The bq4845 provides 16 bytes of clock and control status

registers. Table 1 is a map of the bq4845 registers, and

Table2describestheregisterbits.

Clock Memory Interface

The bq4845 has the same interface for clock/calendar

and control information as standard SRAM. To read and

write to these locations, the user must put the bq4845 in

the proper mode and meet the timing requirements.

Read Mode

The bq4845 is in read mode whenever OE (Output enable) is low and CS (chip select) is low. The unique address, specified by the 4 address inputs, defines which

one of the 16 clock/calendar bytes is to be accessed. The

bq4845 makes valid data available at the data I/O pins

within tAA(address access time). This occurs after the

last address input signal is stable, and providing the CS

and OE (output enable) access times are met. If the CS

and OE access times are not met, valid data is available

after the latter of chip select access time (t

enable access time (tOE).

and OE control the state of the eight three-state

CS

data I/O signals. If the outputs are activated before tAA,

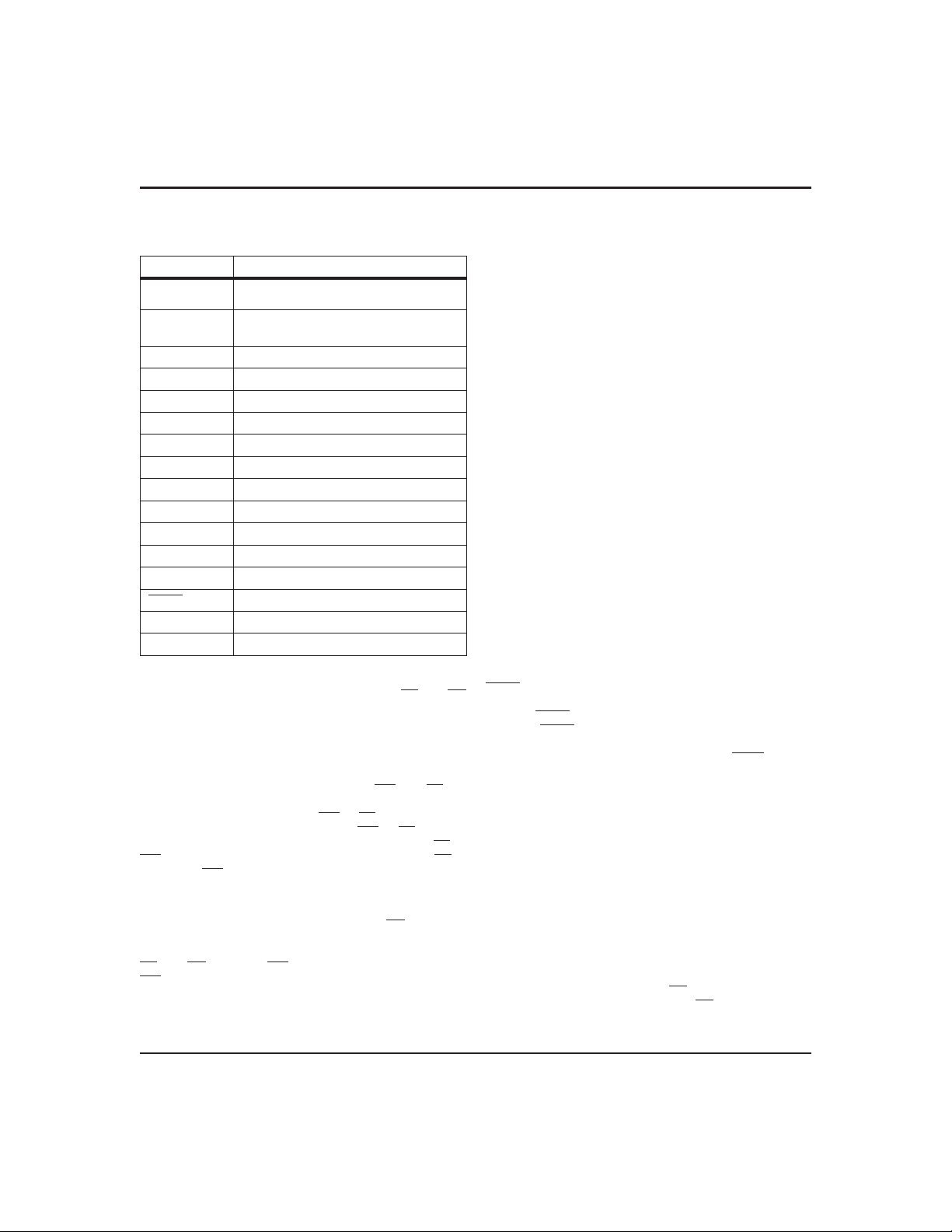

Table 1. bq4845 Clock and Control Register Map

Ad-

dress

(h) D7 D6 D5 D4 D3 D2 D1 D0

0 0 10-second digit 1-second digit 00–59 Seconds

1 ALM1

2 0 10-minute digit 1-minute digit 00–59 Minutes

3 ALM1

4 PM/AM 0 10-hour digit 1-hour digit 01–12AM/81– 92 PM Hours

ALM1

5

PM/AM

6 0 0 10-day digit 1-day digit 01–31 Day

7 ALM1 ALM0 10-day digit 1-day digit 01–31 Day alarm

8 0 0 0 Day-of-week digit 01–07 Day-of-week

9 0 0 0 10mo. 1-month digit 01–12 Month

A 10-year digit 1-year digit 00–99 Year

B * WD2 WD1 WD0 RS3 RS2 RS1 RS0

C * * AIE PIE PWRIE ABE Interrupt en-

D * * AF PF PWRF BVF Flags

E * * UTI STOP

F * * * * * * * * Unused

Notes: * = Unused bits; unwritable and read as 0.

ALM0

10-second digit

ALM0

10-minute digit

ALM0 10-hour digit 1-hourdigit 01–12AM/ 81–92 PM Hoursalarm

0 = should be set to 0 for valid time/calendar range.

Clock calendar data in BCD. Automatic leap year adjustment.

PM/AM = 1 for PM; PM/AM = 0 for AM.

DSE = 1 enables daylight savings adjustment.

24/12 = 1 enables 24-hour data representation; 24/12 = 0 enables 12-hour data representation.

Day-of-Weekcoded as Sunday = 1 through Saturday = 7.

BVF = 1 for valid battery.

STOP = 1 turns the RTC on; STOP = 0 stops the RTC in back-up mode.

1-second digit 00–59 Seconds alarm

1-minute digit 00–59 Minutes alarm

24/12 DSE Control

12-Hour

Range (h) Register

Programmable

rates

ables

) or output

ACS

Aug.1995

4

Table 2. Clock and Control Register Bits

Bits Description

24/12

24- or 12-hour representation

ABE Alarminterrupt enable in

battery-backup mode

AF Alarm interrupt flag

AIE Alarminterrupt enable

ALM0–ALM1 Alarm mask bits

BVF Battery-valid flag

DSE Daylight savings time enable

PF Periodic interrupt flag

PIE Periodic interrupt enable

PM/AM PM or AM indication

PWRF Power-fail interrupt flag

PWRIE Power-failinterrupt enable

RS0–RS3 Periodic interrupt rate

STOP

Oscillator stop and start

UTI Update transfer inhibit

WD0 - WD2 Watchdog time-out rate

the data lines are driven to an indeterminate state until

tAA. If the address inputs are changed while CS and OE

remain low, output data remains valid for tOH(output

data hold time), but goes indeterminate until the next

address access.

Write Mode

The bq4845 is in write mode whenever WE and CS are

active. The start of a write is referenced from the

latter-occurring falling edge of WE or CS. A write is terminated by the earlier rising edge of WE or CS. The addresses must be held valid throughout the cycle. CS or

WE must return high for a minimum of t

t

from WE prior to the initiation of another read or

WR1

write cycle.

Data-in must be valid t

remain valid for t

DH1

prior to the end of write and

DW

or t

afterward. OE should be

DH2

kept high during write cycles to avoid bus contention; although, if the output bus has been activated by a low on

CS and OE, a low on WE disables the outputs tWZafter

WE falls.

WR2

from CS or

bq4845/bq4845Y

Reading the Clock

Once every second, the user-accessible clock/calendar locations are updated simultaneously from the internal

real time counters. To prevent reading data in transition, updates to the bq4845 clock registers should be

halted. Updating is halted by setting the update transfer inhibit (UTI) bit D3 of the control register E. As long

as the UTI bit is 1, updates to user-accessible clock locations are inhibited. Once the frozen clock information is

retrieved by reading the appropriate clock memory locations, the UTI bit should be reset to 0 in order to allow

updates to occur from the internal counters. Because

the internal counters are not halted by setting the UTI

bit, reading the clock locations has no effect on clock accuracy. Once the UTI bit is reset to 0, the internal registers update within one second the user-accessible registers with the correct time. A halt command issued during a clock update allows the update to occur before

freezing the data.

Setting the Clock

The UTI bit must also be used to set the bq4845 clock.

Once set, the locations can be written with the desired

information in BCD format. Resetting the UTI bit to 0

causes the written values to be transferred to the internal clock counters and allows updates to the useraccessible registers to resume within one second.

Stopping and Starting the Clock Oscillator

The bq4845 clock can be programmed to turn off when

the part goes into battery back-up mode by setting

STOP to 0 prior to power down. If the board using the

bq4845 is to spend a significant period of time in storage, the STOP bit can be used to preserve some battery

capacity. STOP set to 1 keeps the clock running when

VCCdrops below VSO. With VCCgreater than VSO, the

bq4845 clockrunsregardlessofthestateofSTOP.

Power-Down/Power-Up Cycle

The bq4845 continuously monitors VCCfor out-oftolerance. During a power failure, when VCCfalls below

V

, the bq4845 write-protects the clock and storage

PFD

registers. When VCCis below VBC(3V typical), the

power source is switched to BC. RTC operation and

storage data are sustained by a valid backup energy

source. When VCCis above VBC, the power source is

VCC. Write-protection continues for t

rises above V

PFD

.

An external CMOS static RAM is battery-backed using

the V

and chip enable output pins from the bq4845.

OUT

As the voltage input VCCslews down during a power

failure, the chip enable output, CE

independent of the chip enable input CE

time after V

CSR

is forced inactive

OUT,

IN.

CC

Aug.1995

5

bq4845/bq4845Y

This activity unconditionally write-protects the external

SRAM as VCCfalls below V

. If a memory access is in

PFD

progress to the external SRAM during power-fail detection, that memory cycle continues to completion before

the memory is write-protected. If the memory cycle is

not terminated within time t

, the chip enable output

WPT

is unconditionally driven high, write-protecting the controlled SRAM.

As the supply continues to fall past V

switching device forces V

ergy source. CE

OUT

to the external backup en-

OUT

is held high by the V

, an internal

PFD

OUT

energy

source.

During power-up, V

is switched back to the 5V sup-

OUT

ply as VCCrises above the backup cell input voltage

sourcing V

ter the power supply has reached V

OUT

.CE

is held inactive for time t

OUT

PFD

af-

CER

, independent of

the CEINinput,toallowforprocessorstabilization.

During power-valid operation, the CE

through to the CE

output with a propagation delay of

OUT

input is passed

IN

less than 12ns.

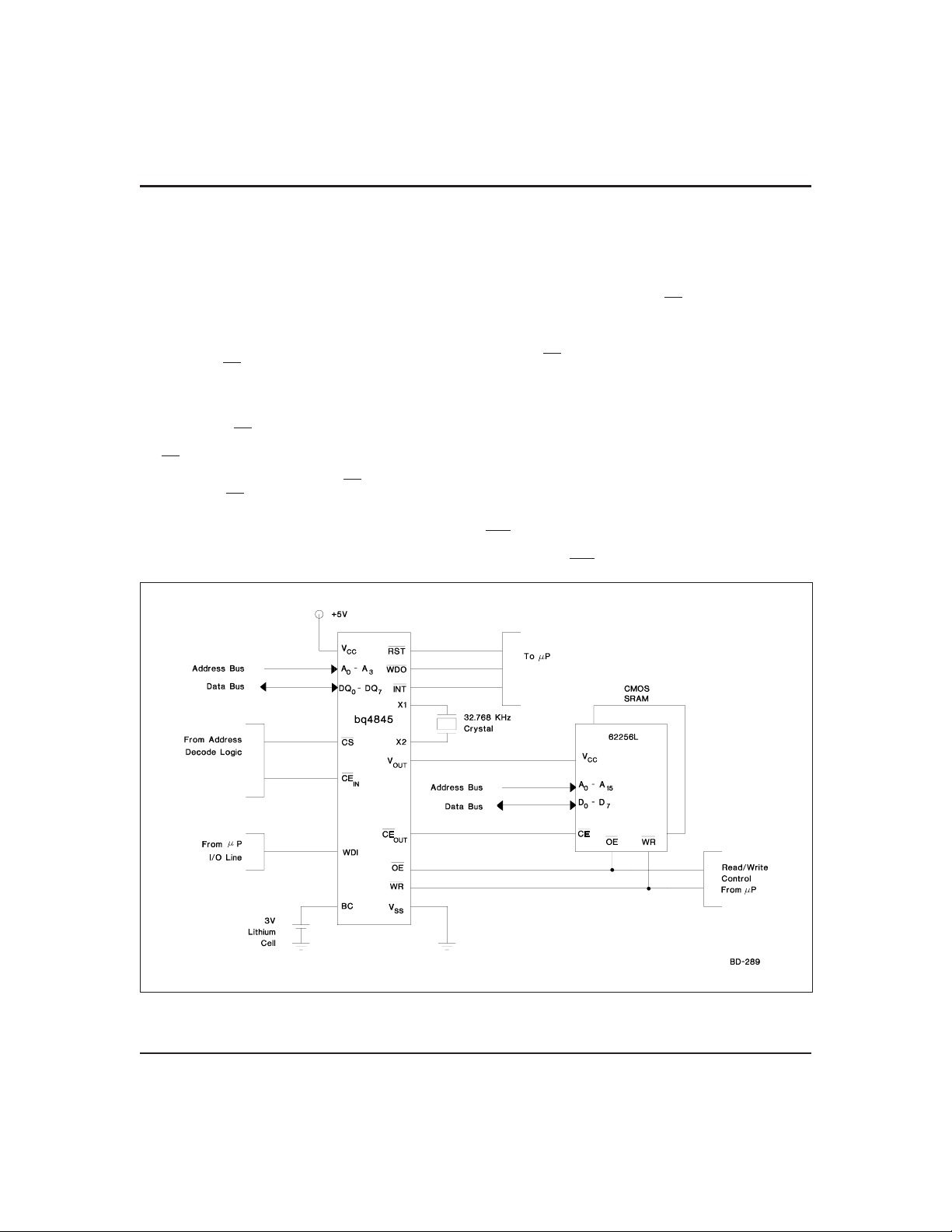

Figure 2 shows the hardware hookup for the external

RAM,battery,and crystal.

A primary backup energy source input is provided on

the bq4845. The BC input accepts a 3V primary battery,

typically some type of lithium chemistry. Since the

bq4845 provides for reverse battery charging protection,

no diode or current limiting resistor is needed in series

with the cell. To prevent battery drain when there is no

valid data to retain, V

OUT

and CE

are internally iso-

OUT

lated from BC by the initial connection of a battery. Following the first application of VCCabove V

, this iso-

PFD

lation is broken, and the backup cell provides power to

V

OUT

and CE

for the external SRAM.

OUT

The crystal should be located as close to X1 and X2 as

possible and meet the specifications in the Crystal

Specification Table. With the specified crystal, the

bq4845 RTC will be accurate to within one minute per

month at room temperature. In the absence of a crystal,

a 32.768 kHz waveform can be fed into X1 with X2

grounded.

Power-On Reset

The bq4845 provides a power-on reset, which pulls the

RST pin low on power-down and remains low on powerup for t

voltage on BC,RST remains valid for VCC=VSS.

after VCCpasses V

RST

With valid battery

PFD.

Figure 2. bq4845 Application Circuit

6

Aug.1995

Loading...

Loading...