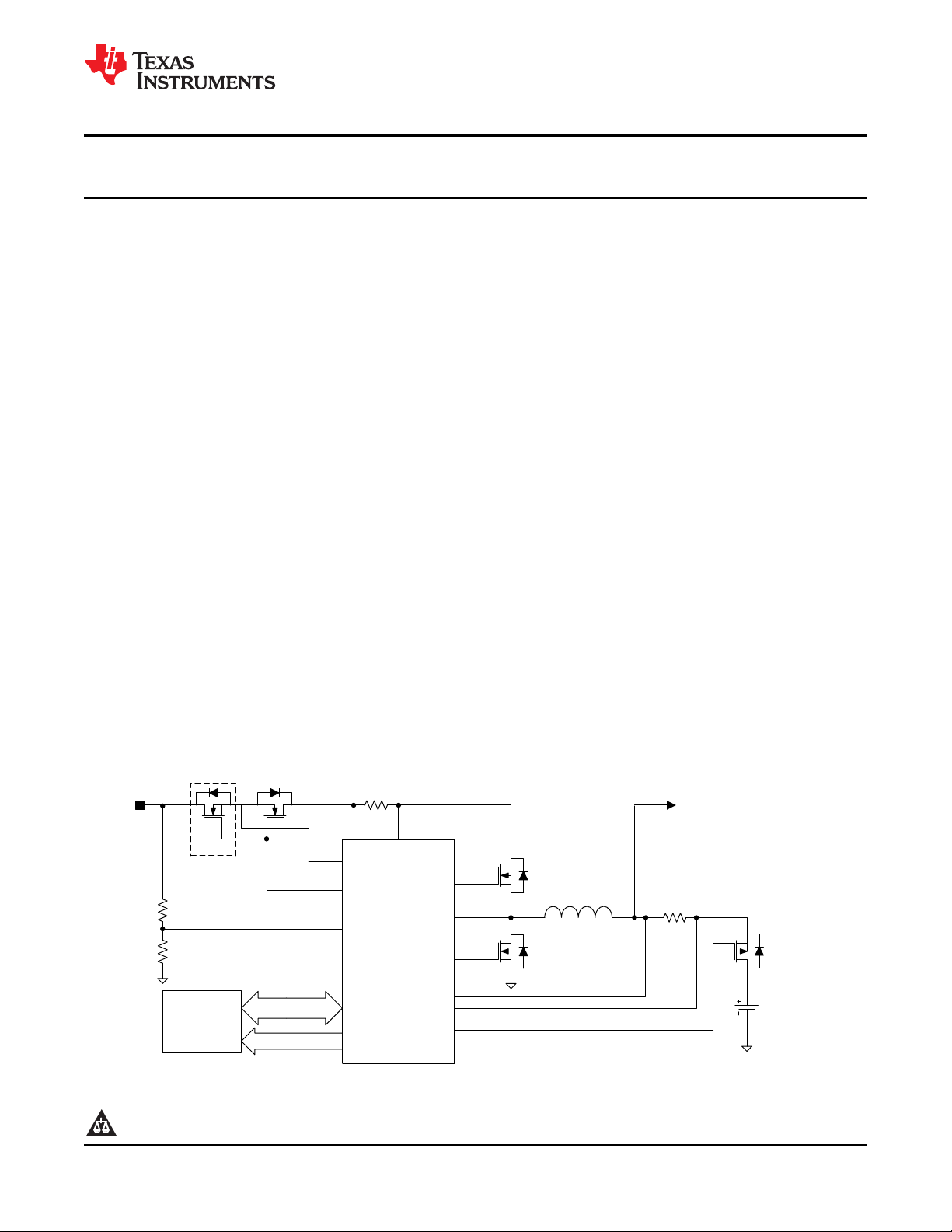

Texas Instruments BQ24715J Schematic [ru]

HOST

SMBus

To System

Adaptor

2S-3S

Ultra-Fast

DPM

Ultra-Low Quiescent

Current

N-FET

Driver

SMBus Controls V and I

with High Accuracy

6-24V

Iin, Idischarge

Support CPU Turbo Mode

PMOS BAT

FET Driver

Integrated Compensation Internal Soft Start

Iin

Ichg

Enhanced Safety

Features

OCP, OVP,

FET Short

Adaptor Detection

Optional

NVDC-1

Charger

Controller

bq24715J

Simplified Application Diagram

www.ti.com

SLUSBQ1 –AUGUST 2013

2-3 Cell NVDC-1 Battery Charger Controller

Check for Samples: bq24715J

1

FEATURES APPLICATIONS

• 6-24V Input SMBus NVDC-1 2-3S Battery • Ultrabook, Notebook, and Tablet PC

Charger Controller

• System Instant-on Operation with No Battery

or Deeply Discharged Battery

• Ultra-Fast Transient Response of 100 µs DESCRIPTION

• Ultra-Low Quiescent Current of 500 µA and

High PFM Light Load Efficiency 80% at 20mA

load to Meet Energy Star and ErP Lot6

• Switching Frequency: 600 kHz, 800 kHz, 1MHz

• Programmable System/Charge Voltage (16

mV/step), Input/Charge Current (64 mA/step)

with High Accuracy

– ±0.5% Charge Voltage Regulation

– ±3% Input/Charge Current Regulation

– ±2% 40x Input/16x Discharge Current

Monitor Output

• Support Battery LEARN Function

• Maximize CPU Performance with Deeply

Discharged Battery or No Battery

• Integrated NMOS ACFET and RBFET Driver

• 20-pin 3.5 x 3.5 mm2QFN Package

• Industrial and Medical Equipment

• Portable Equipment

The bq24715J is a NVDC-1 synchronous battery

charge controller with low quiescent current, high light

load efficiency for 2S or 3S Li-ion battery charging

applications, offering low component count.

The power path management allows the system to be

regulated at battery voltage but does not drop below

the programmable system minimum voltage.

The device provides N-channel ACFET and RBFET

drivers for the power path management. It also

provides driver of the external P-channel battery FET.

The loop compensation is fully integrated.

The device has programmable 11-bit charge voltage,

7-bit input/charge current and 6-bit minimal system

voltage with very high regulation accuracies through

the SMBus communication interface.

The device monitors adapter current or battery

discharge current through the IOUT pin allowing the

host to throttle down CPU speed when needed.

The device provides extensive safety features for

over current, over voltage and MOSFET short circuit.

bq24715J

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testingof all parameters.

Copyright © 2013, Texas Instruments Incorporated

bq24715J

SLUSBQ1 –AUGUST 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

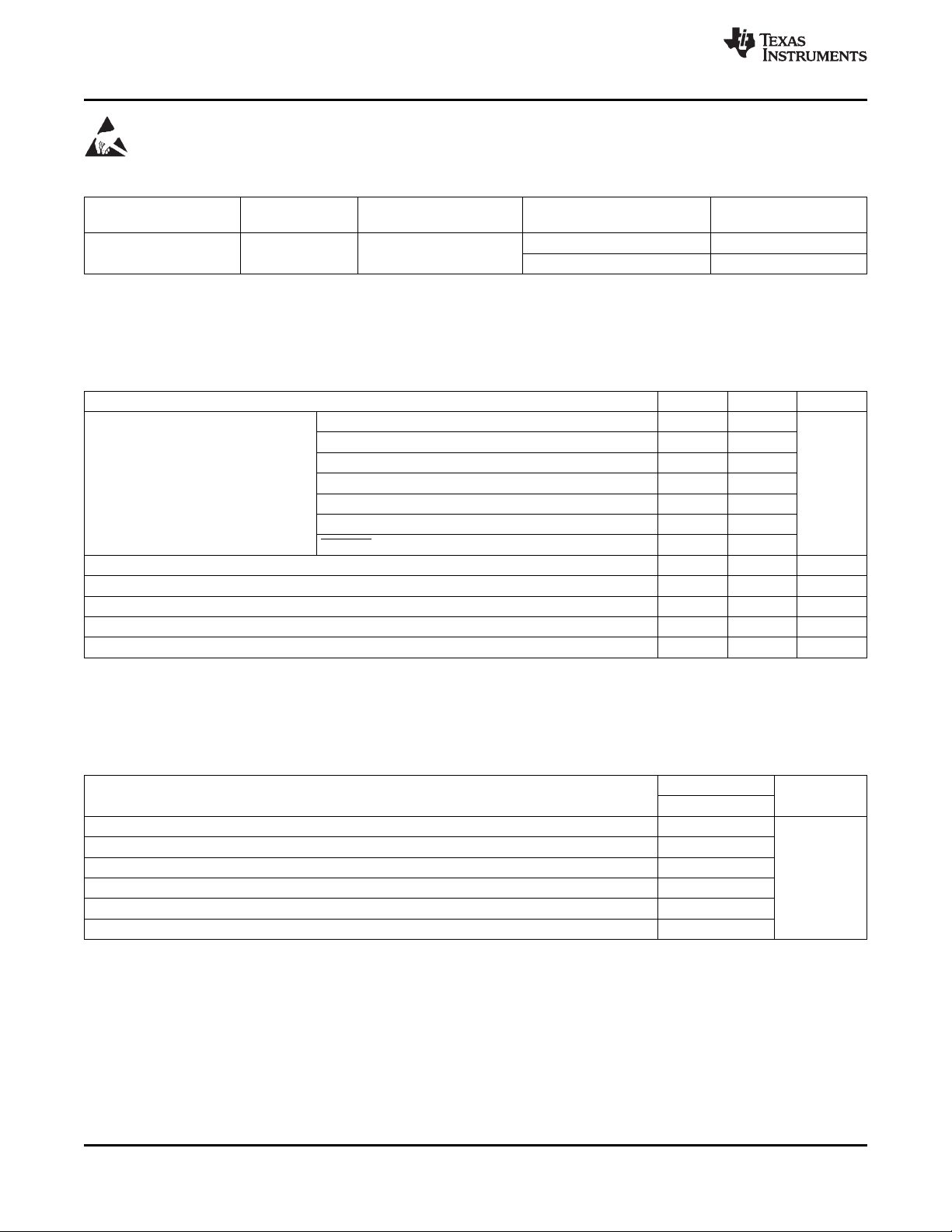

ORDERING INFORMATION

PART NUMBER IC MARKING PACKAGE QUANTITY

bq24715J BQ715 20-PIN 3.5 × 3.5 mm2QFN

(1)

ORDERING NUMBER

(Tape and Reel)

bq24715JRGRR 3000

bq24715JRGRT 250

(1) For the most current package and ordering information see Package Option Addendum at the end of this document; or see the TI

website at www.ti.com

ABSOLUTE MAXIMUM RATINGS

(1)(2)

over operating free-air temperature range (unless otherwise noted)

MIN MAX UNIT

SRN, SRP, ACN, ACP, CMSRC, VCC –0.3 30

PHASE –2.5 30

ACDET, SDA, SCL, LODRV, REGN, IOUT, ACOK, CELL –0.3 7

Voltage range LODRV (20ns) –2.5 7 V

BTST, HIDRV, ACDRV –0.3 36

HIDRV (20ns) –2.5 36

BATDRV –0.3 30

Maximum difference voltage SRP–SRN, ACP–ACN –0.5 0.5 V

T

J

T

STG

(1) Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

(2) All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified terminal. Consult Packaging

Junction temperature range –40 155 °C

Storage temperature range –55 155 °C

ESD Human Body Model (HBM) 2000 V

ESD Charged Device Model (CDM) 500 V

only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Section of the data book for thermal limitations and considerations of packages.

THERMAL INFORMATION

(1)

(2)

θ

θ

θ

ψ

ψ

θ

JA

JCtop

JB

JT

JB

JCbot

THERMAL METRIC

Junction-to-ambient thermal resistance 34.6

Junction-to-case (top) thermal resistance 49.3

Junction-to-board thermal resistance

Junction-to-top characterization parameter 0.5

Junction-to-board characterization parameter 12.7

Junction-to-case (bottom) thermal resistance 1

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

2 Copyright © 2013, Texas Instruments Incorporated

bq24715

QFN (20 PINS)

12.5

UNITS

°C/W

www.ti.com

RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

SRN, SRP, ACN, ACP, CMSRC, VCC 0 24 V

PHASE –2 24 V

Voltage range ACDET, SDA, SCL, LODRV, REGN, IOUT, ACOK, CELL 0 6.5 V

BTST, HIDRV, ACDRV 0 30 V

BATDRV –0.3 16 V

Maximum

difference range

T

T

Junction temperature range –20 125 °C

J

Operating free-air temperature range –20 85 °C

A

SRP–SRN, ACP–CAN –0.2 0.2 V

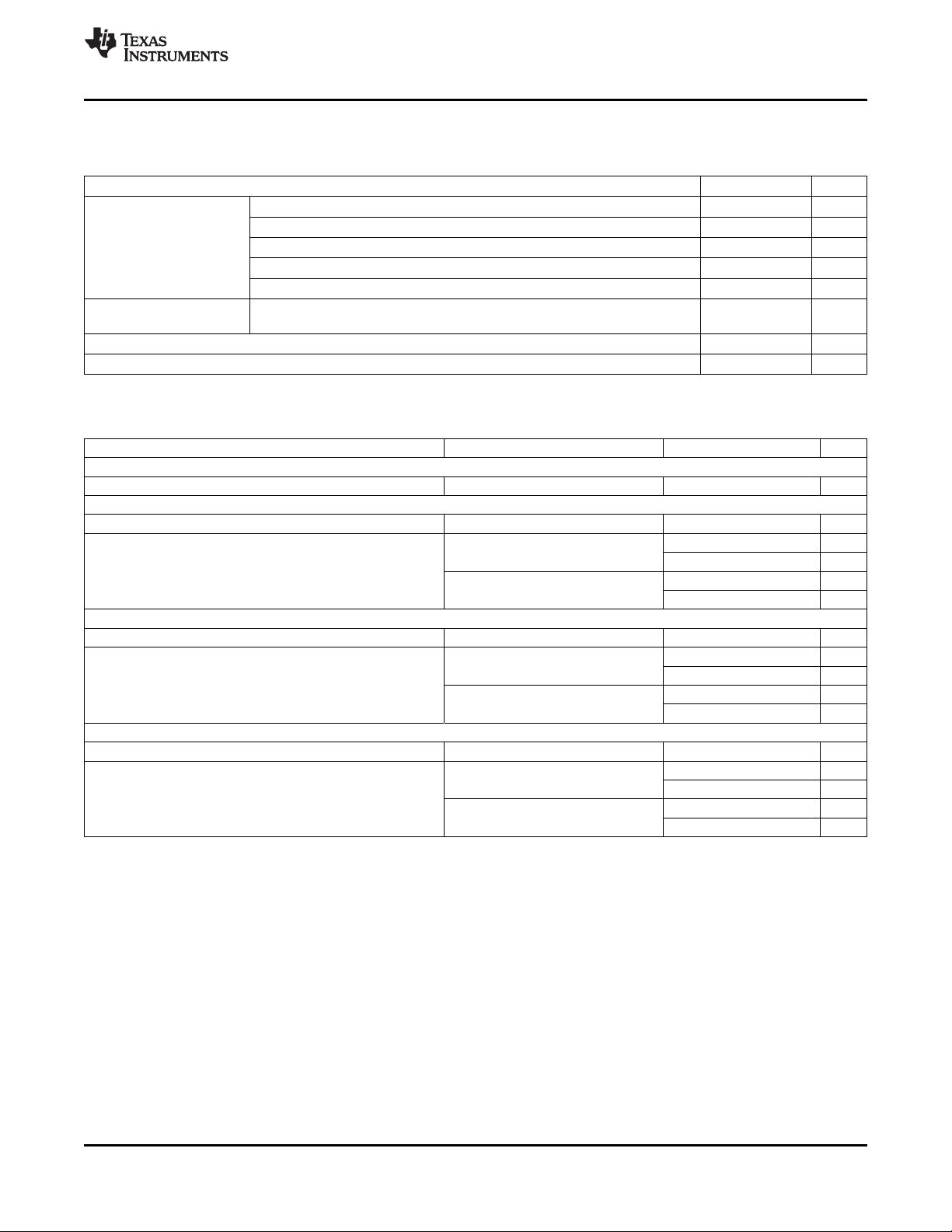

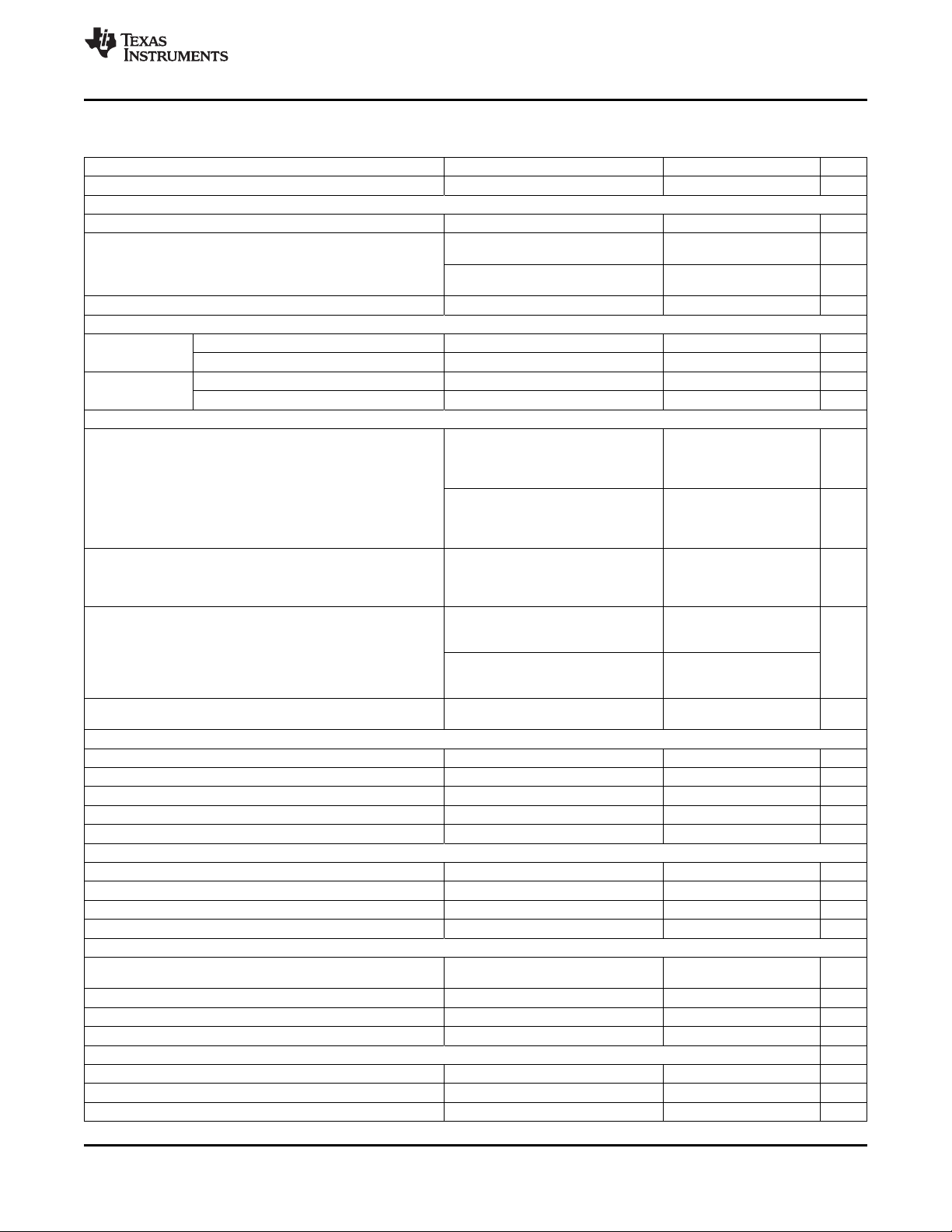

ELECTRICAL CHARACTERISTICS

6 V ≤ V

INPUT OPERATING CONDITIONS

V

VCC_OP

MIN SYSTEM VOLTAGE REGULATION (0x3E register)

V

SYSMIN_RNG

V

SYSMIN_REG

V

SYSMIN_REG_ACC

MAX SYSTEM VOLTAGE REGULATION (0x15 register charge disable)

V

SYSMAX_RNG

V

SYSMAX_REG

V

SYSMAX_REG_ACC

MAX CHARGE VOLTAGE REGULATION (0-85C; 0x15 register charge enable)

V

BAT_REG_RNG

V

BAT_REG_ACC

≤ 24V, –20°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITION MIN TYP MAX UNIT

VCC Input Voltage Operating Range 6 24 V

MinSystem Voltage Regulation Range 4.096 14.5 V

and

Default minimum system voltage and accuracy at

charge enable and battery voltage lower than

V

SYSMIN_REG

MaxSystem Voltage Regulation Range 4.096 14.5 V

and Default maximum system voltage and accuracy

at charge disable

Battery voltage range 4.096 14.5 V

Charge voltage regulation accuracy

MinsystemVoltage() = 0x2400H (3S)

MinsystemVoltage() = 0x1800H (2S)

MaxChargeVoltage() = 0x34C0H (3S)

MaxChargeVoltage() = 0x2330H (2S)

MaxChargeVoltage() = 0x3130H

MaxChargeVoltage() = 0x20D0H

bq24715J

SLUSBQ1 –AUGUST 2013

MIN MAX UNIT

9.216 V

–2% 1.2%

6.144 V

–3% 1.5%

13.504 V

–2% 1.2%

9.008 V

–3% 1.5%

12.529 12.592 12.655 V

–0.5% 0.5%

8.35 8.4 8.45 V

–0.6% 0.6%

Copyright © 2013, Texas Instruments Incorporated 3

bq24715J

SLUSBQ1 –AUGUST 2013

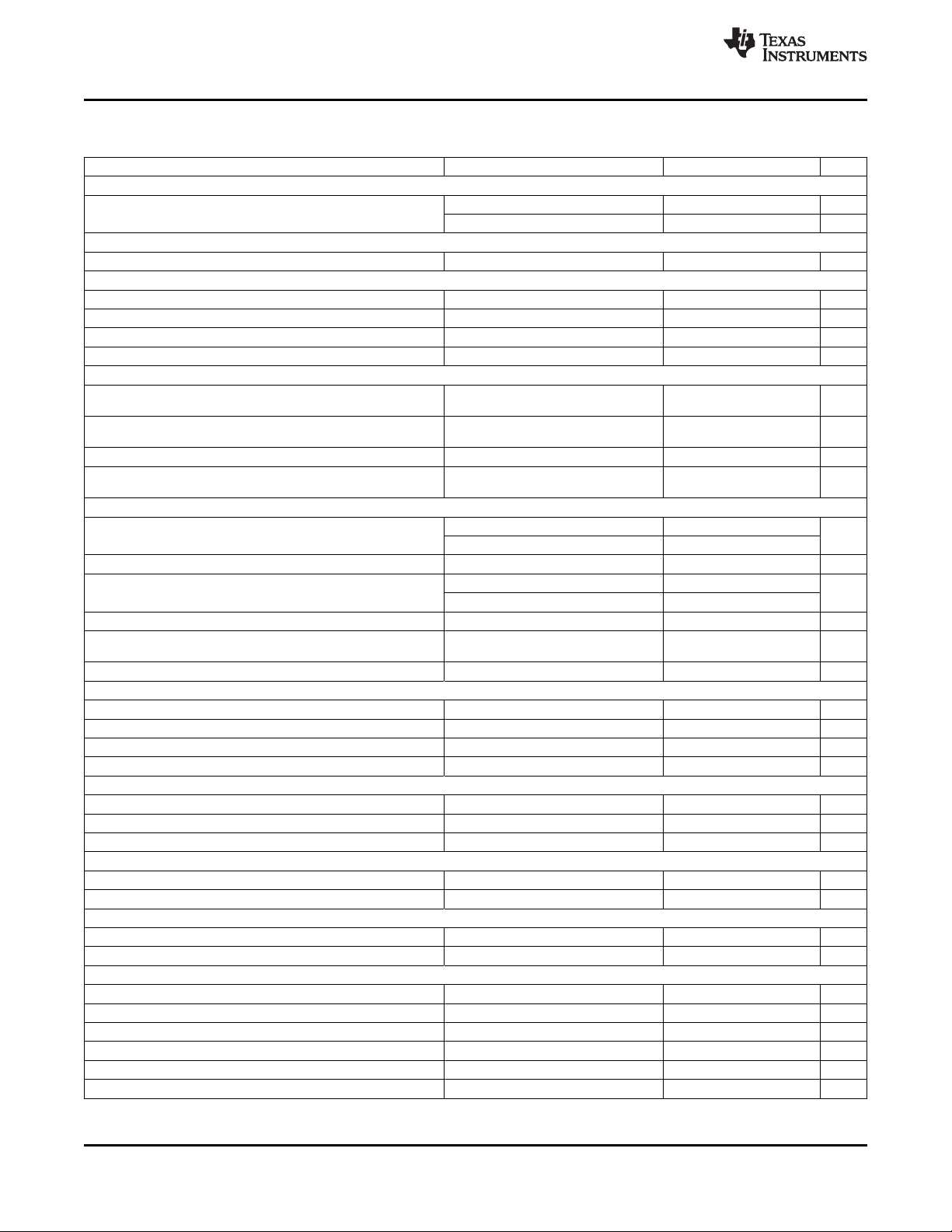

ELECTRICAL CHARACTERISTICS (continued)

6 V ≤ V

CHARGE CURRENT REGULATION (0-85°C)

V

IREG_CHG_RNG

I

CHRG_REG_ACC

PRECHARGE CURRENT REGULATION (0-85°C)

I

PRECHRG_REG_ACC

INPUT CURRENT REGULATION

V

DPM_REG_RNG

I

DPM_REG_ACC

INPUT CURRENT OR DISCHARGE CURRENT SENSE AMPLIFIER

V

ACP/N_OP

V

SRP/N_OP

I

IOUT

A

IOUT

V

SRN-SRP_OFF

V

IOUT_ACC

≤ 24V, –20°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITION MIN TYP MAX UNIT

Charge current regulation differential voltage

range R

SNS

= 10mΩ

Charge current regulation accuracy

10mΩ current sensing resistor, VBAT>VSYSMIN

Charge current regulation accuracy 10mΩ current

sensing resistor,

VBAT<VSYSMIN, chargeoption(2)=1

Input current regulation differential voltage range

RAC= 10mΩ

Input current regulation accuracy 10 mΩ current

sensing resistor

Input common mode range Voltage on ACP/ACN 4.5 24 V

Output common mode range Voltage on SRP/SRN 14.5 V

IOUT Output current 0 40 uA

Current sense amplifier gain

Input current amplifier offset voltage 1 mV

Current sense output accuracy V

www.ti.com

VIREG_CHG = VSRP - VSRN 0 81.28 mV

ChargeCurrent() = 0x1000H

ChargeCurrent() = 0x0800H

ChargeCurrent() = 0x0400H

ChargeCurrent() = 0x0200H

ChargeCurrent() = 0x0180H

ChargeCurrent() = 0x0100H

ChargeCurrent() = 0x00C0H

ChargeCurrent() = 0x0080H

ChargeCurrent() >= 0x0180H

ChargeCurrent() = 0x0100H

ChargeCurrent() = 0x00C0H

ChargeCurrent() = 0x0080H

V

IREG_DPM

= V

ACP

– V

ACN

InputCurrent() = 0x1000H

InputCurrent() = 0x0800H

InputCurrent() = 0x0400H

InputCurrent() = 0x0200H

V

(IOUT)/V(SRN-SRP)

= 1 and 0x12H[3] = 1

V

(IOUT)/V(ACP-ACN)

0x12H[3] = 1

(SRN-SRP)

V

(SRN-SRP)

V

(SRN-SRP)

V

(SRN-SRP)

, 0x12H[15] = 1, 0x12H[4]

, 0x12H[4] = 0 and

or V

or V

or V

or V

= 40.96 mV -2% 2%

(ACP-ACN)

= 20.48 mV -3% 3%

(ACP-ACN)

= 10.24 mV -10% 10%

(ACP-ACN)

) = 5.12 mV -25% 25%

(ACP-ACN

3937 4096 4219 mA

–3% 3%

1946 2048 2150 mA

–5% 5%

921 1024 1127 mA

–10% 10%

410 512 614 mA

–20% 20%

288 384 480

–25% 25%

172 256 340 mA

–33% 33%

115 192 269

–40% 40%

64 128 192 mA

–60% 60%

268.8 384 499.2

–30% 30%

153.6 256 358.4 mA

–40% 40%

96 192 288

–50% 50%

25.6 128 230.4 mA

–80% 80%

0 80.64 mV

3973 4096 4219 mA

–3% 3%

1946 2048 2150 mA

–5% 5%

870 1024 1178 mA

–15% 15%

358.4 512 665.6 mA

–30% 30%

16 V/V

40 V/V

4 Copyright © 2013, Texas Instruments Incorporated

bq24715J

www.ti.com

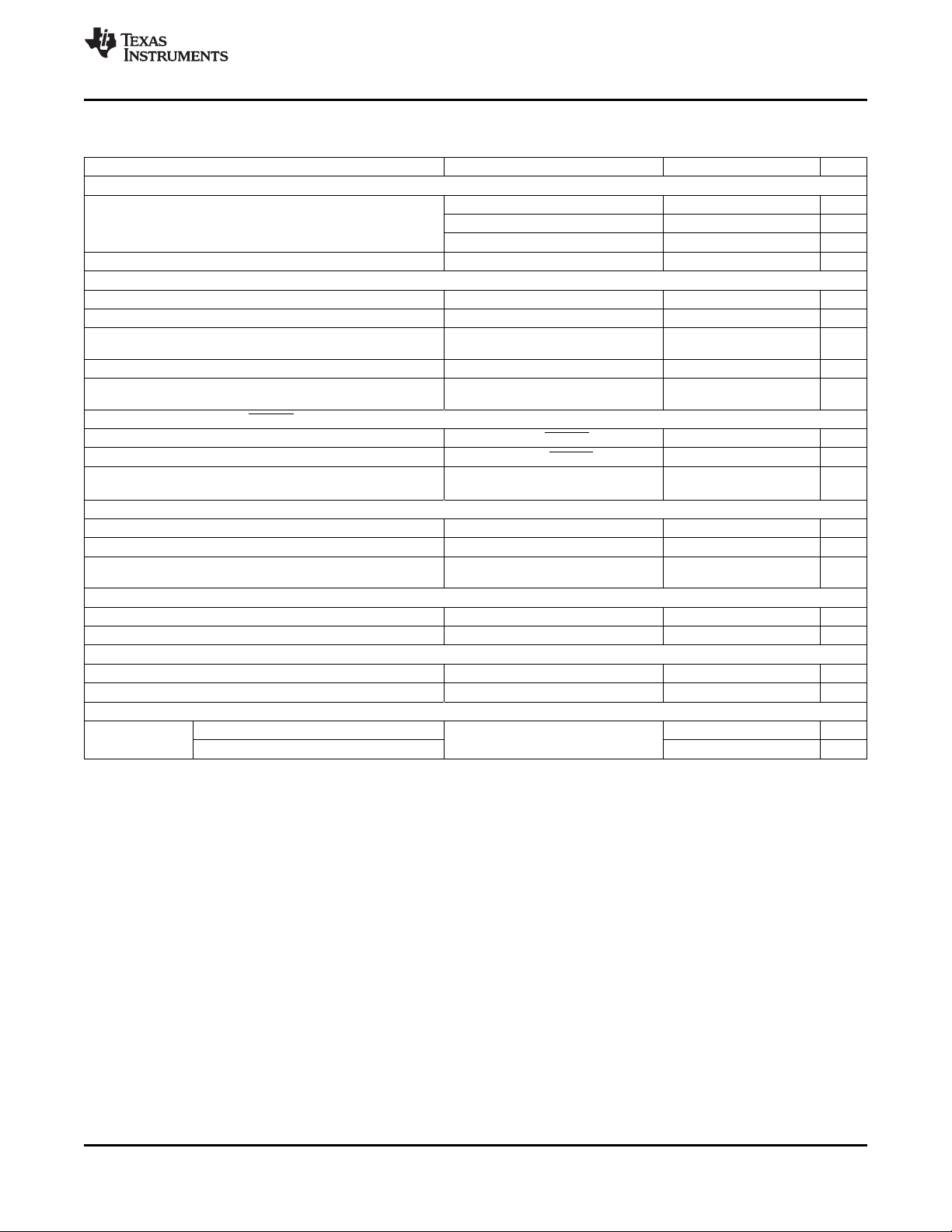

ELECTRICAL CHARACTERISTICS (continued)

6 V ≤ V

C

IOUT_MAX

REGN REGULATOR

V

REGN_REG

I

REGN_LIM

C

REGN

UNDER VOLTAGE LOCKOUT COMPARATOR (UVLO)

V

UVLO_VCC

V

UVLO_BAT

QUIESCENT CURRENT

I

BAT_BATFET_ON

I

STANDBY

I

AC_SWLIGHT

I

AC_SW

ACOK COMPARATOR

V

ACOK_RISE

V

ACOK_FALL_HYS

V

ACOK_RISE_DEG

V

WAKEUP_RISE

V

WAKEUP_FALL

VCC to SRN COMPARATOR (VCC_SRN), SLEEP

V

VCC-SRN_FALL

V

VCC-SRN _RHYS

INPUT OVER-CURRENT COMPARATOR

ACOC ChargeOption() bit [7] = 1 330% I

LIGHT LOAD COMPARATOR

≤ 24V, –20°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITION MIN TYP MAX UNIT

Maximum output load capacitance For stability with 0 to 1mA load 100 pF

REGN Regulator voltage V

REGN Current limit

REGN Output capacitor required for stability I

Under-voltage rising threshold V

Under-voltage hysteresis, falling V

Under-voltage rising threshold V

Under-voltage hysteresis, falling V

Standby mode. System powered by battery.

BATFET ON.

I

SRN+ISRP+IPHASE+IBTST+IACP+IACN+ICMSRC

> 6.5V, V

VCC

V

= 0V, V

REGN

enabled and not in T

V

= 0V, V

REGN

disabled or in T

= 100 µA to 50 mA 1 μF

LOAD

rising 3 3.2 3.4 V

VCC

falling 400 mV

VCC

rising 3 3.3 3.6 V

SRN

falling 400 mV

SRN

V

= 12.6V, V

BAT

turns on,

> 0.6V (0-50 mA load) 5.5 6 6.5 V

ACDET

> UVLO, Converter

VCC

SHUT

> UVLO, Converter

VCC

SHUT

> UVLO, BATFET

SRN

ACDET < 0.6 V, TJ= –20°C to 85°C,

0x12[15] = 1 (low power mode enabled)

V

= 12.6V, V

BAT

turns on,

> UVLO, BATFET

SRN

ACDET < 0.6 V, TJ= –20°C to 85°C,

0x12[15] = 0 (low power mode disabled)

ACN = ACP = CMSRC = VCC = 20 V,

Adapter standby quiescent current, V

I

VCC+IACP+IACN+ICMSRC

Adapter current, I

VCC

+ I

ACP

+ I

ACN

+ I

CMSRC

= 12.6V, V

BAT

CELL pull up, TJ= –20°C to 85°C. No

ACDET

> 2.4V,

switching.

I

plus supply current in PFM,

STANDBY

200 mW output; Reg0x12[10] = 0;

MOSFET Qg = 4 nC;

I

plus supply current in PFM,

STANDBY

200 mW output; Reg0x12[10] = 1;

MOSFET Qg = 4 nC;

Adapter current, I

VCC

+ I

ACP

+ I

ACN

+ I

CMSRC

ACOK Rising threshold V

ACOK Falling hysteresis V

ACOK Rising deglitch (Specified by design) V

WAKEUP Detect rising threshold V

WAKEUP Detect falling threshold V

VCC-SRN Falling threshold V

VCC-SRN Rising hysteresis V

VCC-SRN falling delay V

Resume time V

Charge enable, 800kHz switching

frequency MOSFET Qg = 4 nC

> UVLO, V

VCC

> UVLO, V

VCC

>UVLO, V

VCC

> UVLO, V

VCC

> UVLO, V

VCC

falling towards V

VCC

rising above V

VCC

falling towards V

VCC

rising above V

VCC

rising 2.376 2.4 2.424 V

ACDET

falling 35 55 75 mV

ACDET

rising above 2.4V 2 3 ms

ACDET

rising 0.52 0.6 V

ACDET

falling 0.35 0.46 V

ACDET

SRN

SRN

SRN

SRN

0.76 1.28 1.9 ms

ACP to ACN Rising Threshold, respect to input

current().

ACOC floor 50 mV

ACOC ceiling 180 mV

Relax time, No latch. 300 ms

ACP to ACN Falling Threshold, average Converter CCM-DCM, current decrease 1.25 mV

ACP to ACN Rising Threshold, average 2.5 mV

Deglitch time, both side 10 µs

SLUSBQ1 –AUGUST 2013

50 75 mA

7 14 mA

13.3 20 μA

50 70 μA

540 700 µA

1.5

5

10 mA

70 125 200 mV

150 mV

95 160 237 µs

mA

DPM

Copyright © 2013, Texas Instruments Incorporated 5

bq24715J

SLUSBQ1 –AUGUST 2013

ELECTRICAL CHARACTERISTICS (continued)

6 V ≤ V

CONVERTER OVER-CURRENT COMPARATOR (ILIM_HI), CYCLE-BY-CYCLE

ILIM_HI Converter over current limit, measure GND-PH

CONVERTER UNDER-CURRENT COMPARATOR (ILIM_LOW) , CYCLE-BY-CYCLE

INPUT OVER-VOLTAGE (ACOVP)

V

ACOVP

V

ACOV_HYS

BAT OVER-VOLTAGE COMPARATOR (BAT_OVP)

V

OVP_RISE

V

OVP_FALL

SYSTEM OVER-VOLTAGE COMPARATOR (SYS_OVP)

V

SYSOVP_RISE_3S

V

SYSOVP_FALL_3S

V

SYSOVP_RISE_2S

V

SYSOVP_FALL_2S

t

SYSOVP_DEG

THERMAL SHUTDOWN COMPARATOR (T

T

SHUT

T

SHUT_HYS

LOGIC INPUT (SDA, SCL)

VIN_ LO Input low threshold 0.8 V

VIN_ HI Input high threshold 2.1 V

IIN_ LEAK Input bias current V = 7 V –1 1 μA

LOGIC OUTPUT OPEN DRAIN (ACOK, SDA)

VOUT_ LO Output saturation voltage 5 mA drain current 500 mV

IOUT_ LEAK Leakage current V = 7 V –1 1 μA

ANALOG INPUT (ACDET)

IIN_ LEAK Input bias current V = 7 V –1 1 μA

ANALOG INPUT (CELL)

≤ 24V, –20°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITION MIN TYP MAX UNIT

Chargeoption() bit [6] =0 250 mV

Chargeoption() bit [6] =1 (default) 350 mV

Converter over current limit, measure GND-PH –2 0 6 mV

VCC Over-Voltage Rising Threshold VCC rising 24 26 28 V

VCC Over-Voltage Falling Hysteresis VCC falling 1 V

Rising deglitch VCC rising 0.1 ms

Falling deglitch VCC falling 1 ms

Over-voltage rising threshold as percentage of

VBAT_REG

Over-voltage falling threshold as percentage of

VBAT_REG

V

rising 102%

SRN

V

falling 101%

SRN

Discharge current during OVP, SRP pin Charge enable, BATFET ON 4 mA

Over voltage deglitch time to fully turn-off

BATFET

V

rising, chargeoption bit[12]=0 default 15.1

3S System over-voltage rising threshold V

3S System over-voltage falling threshold V

2S System over-voltage rising threshold V

2S System over-voltage falling threshold V

SRN

V

rising, chargeoption bit[12]=1 17.0

SRN

falling 13.2 V

SRN

V

rising, chargeoption bit[12]=0 default 10.1

SRN

V

rising, chargeoption bit[12]=1 11.3

SRN

falling 8.8 V

SRN

System over-voltage deglitch time to turn-off

ACDRV

Discharge current during OVP 4 mA

)

SHUT

Thermal shutdown rising temperature Temperature rising 155 °C

Thermal shutdown hysteresis, falling Temperature falling 20 °C

Rising deglitch 100 µs

Falling deglitch 10 ms

Offset –10 10 mV

GND 1.0 V

Float (2S setting) 1.2 1.8 V

High (3S setting) 2.5 V

Allowed max delay time to config CELL at POR 72 100 120 ms

Internal pull up resistor to REGN 405 kΩ

Internal pull down resistor to GND 141 kΩ

www.ti.com

1 ms

24 µs

6 Copyright © 2013, Texas Instruments Incorporated

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

6 V ≤ V

PWM OSCILLATOR

F

SW

F

SW_min

ACFET GATE DRIVER (ACDRV)

I

ACFET

V

ACFET

R

ACDRV_LOAD

R

ACDRV_OFF

V

ACFET_LOW

BATTERY FET GATE DRIVER (BATDRV)

R

DS_BAT_OFF

R

DS_BAT_ON

V

BATDRV_REG

PWM HIGH SIDE DRIVER (HIDRV)

R

DS_HI_ON

R

DS_HI_OFF

V

BTST_REFRESH

PWM LOW SIDE DRIVER (LODRV)

R

DS_LO_ON

R

DS_LO_OFF

PWM DRIVER TIMING

t

LOW_HIGH

t

HIGH_LOW

INTERNAL SOFT START

I

STEP

≤ 24V, –20°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITION MIN TYP MAX UNIT

PWM Switching frequency ChargeOption() bit [9:8] = 01 (Default) –10% 800 10% kHz

Audio frequency limit, PFM ChargeOption() bit [10] = 1 40 kHz

ACDRV Charge pump current limit 40 60 μA

Gate drive voltage on ACFET V

Minimum load resistance between ACDRV and

CMSRC

ACDRV Turn-off resistance I = 30 μA 5 6.2 7.4 kΩ

ACDRV Turn-off when Vgs voltage is lower than

V

(Specified by design)

ACFET

BATFET Turn-off resistance 100 µA current into BATDRV 2 kΩ

BATFET Turn-on resistance 100 µA current from BATDRV 5 kΩ

BATFET Drive voltage 4.2 8 V

High side driver turn-on resistance V

High side driver turn-off resistance V

Bootstrap refresh comparator threshold voltage 3.85 4.15 4.7 V

Low side driver turn-on resistance V

Low side driver turn-off resistance V

Driver dead time from low side to high side 20 ns

Driver dead time from high side to low side 20 ns

Soft start current step 64 mA

Soft start current step time 24 μs

bq24715J

SLUSBQ1 –AUGUST 2013

ChargeOption () bit [9:8] = 00 –10% 600 10% kHz

ChargeOption() bit [9:8] = 10 –10% 1000 10% kHz

– V

ACDRV

The voltage below V

V

BATDRV_REG=VSRN

when V

AVCC

– VPH = 5.5 V, I = 10 mA 4 5.5 Ω

BTST

– VPH= 5.5 V, I = 10 mA 0.65 1.3 Ω

BTST

V

– VPHwhen low side refresh pulse is

BTST

requested

= 6V, I = 10mA 4 6.2 Ω

REGN

= 6V, I = 10mA 0.9 1.4 Ω

REGN

In CCM mode 10 mΩ current sensing

resistor

when V

CMSRC

> 5 V and BATFET is on

> UVLO 5.5 6.1 6.7 V

VCC

ACFET

– V

BATDRV

500 kΩ

0.2 V

Copyright © 2013, Texas Instruments Incorporated 7

bq24715J

SLUSBQ1 –AUGUST 2013

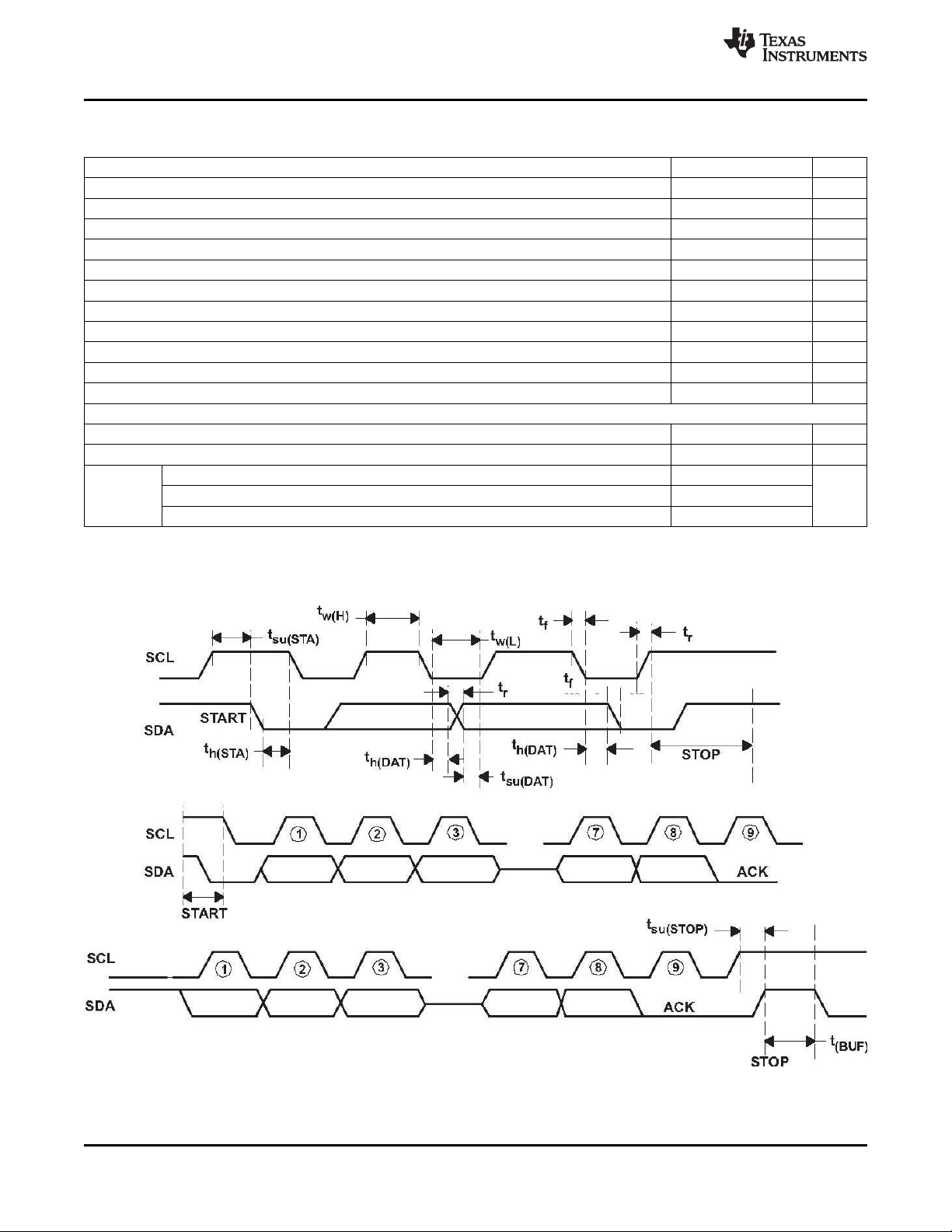

SMBus TIMING CHARACTERISTICS

4.5 V ≤ V

t

R

t

F

t

W(H)

t

W(L)

t

SU(STA)

t

H(STA)

t

SU(DAT)

t

H(DAT)

t

SU(STOP)

t

(BUF)

F

S(CL)

HOST COMMUNICATION FAILURE

t

timeout

t

BOOT

t

WDI

(1) Devices participating in a transfer will timeout when any clock low exceeds the 25ms minimum timeout period. Devices that have

detected a timeout condition must reset the communication no later than the 35ms maximum timeout period. Both a master and a slave

must adhere to the maximum value specified as it incorporates the cumulative stretch limit for both a master (10ms) and a slave (25ms).

(2) User can adjust threshold via SMBus ChargeOption() REG0x12.

≤ 24 V, 0°C ≤ TJ≤125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

MIN TYP MAX UNIT

SCLK/SDATA rise time 1 µs

SCLK/SDATA fall time 300 ns

SCLK pulse width high 4 50 µs

SCLK Pulse Width Low 4.7 µs

Setup time for START condition 4.7 µs

START condition hold time after which first clock pulse is generated 4 µs

Data setup time 250 ns

Data hold time 300 ns

Setup time for STOP condition 4 µs

Bus free time between START and STOP condition 4.7 µs

Clock Frequency 10 100 kHz

SMBus bus release timeout

(1)

25 35 ms

Deglitch for watchdog reset signal 10 ms

Watchdog timeout period, ChargeOption() bit [14:13] = 01

Watchdog timeout period, ChargeOption() bit [14:13] = 10

Watchdog timeout period, ChargeOption() bit [14:13] = 11

(2)

(2)

(2)

(Default) 140 175 210

35 44 53

70 88 105 s

www.ti.com

Figure 1. SMBus Communication Timing Waveforms

8 Copyright © 2013, Texas Instruments Incorporated

1

2

3

4

5

6 7 8 9 10

15

14

13

12

11

20 19 18 17 16

ACN

ACP

CMSRC

ACDRV

ACOK

ACDET

IOUT

SDA

SCL

CELL

BATDRV

SRN

SRP

GND

LODRV

REGN

BTST

HIDRV

PHASE

VCC

bq24715J

www.ti.com

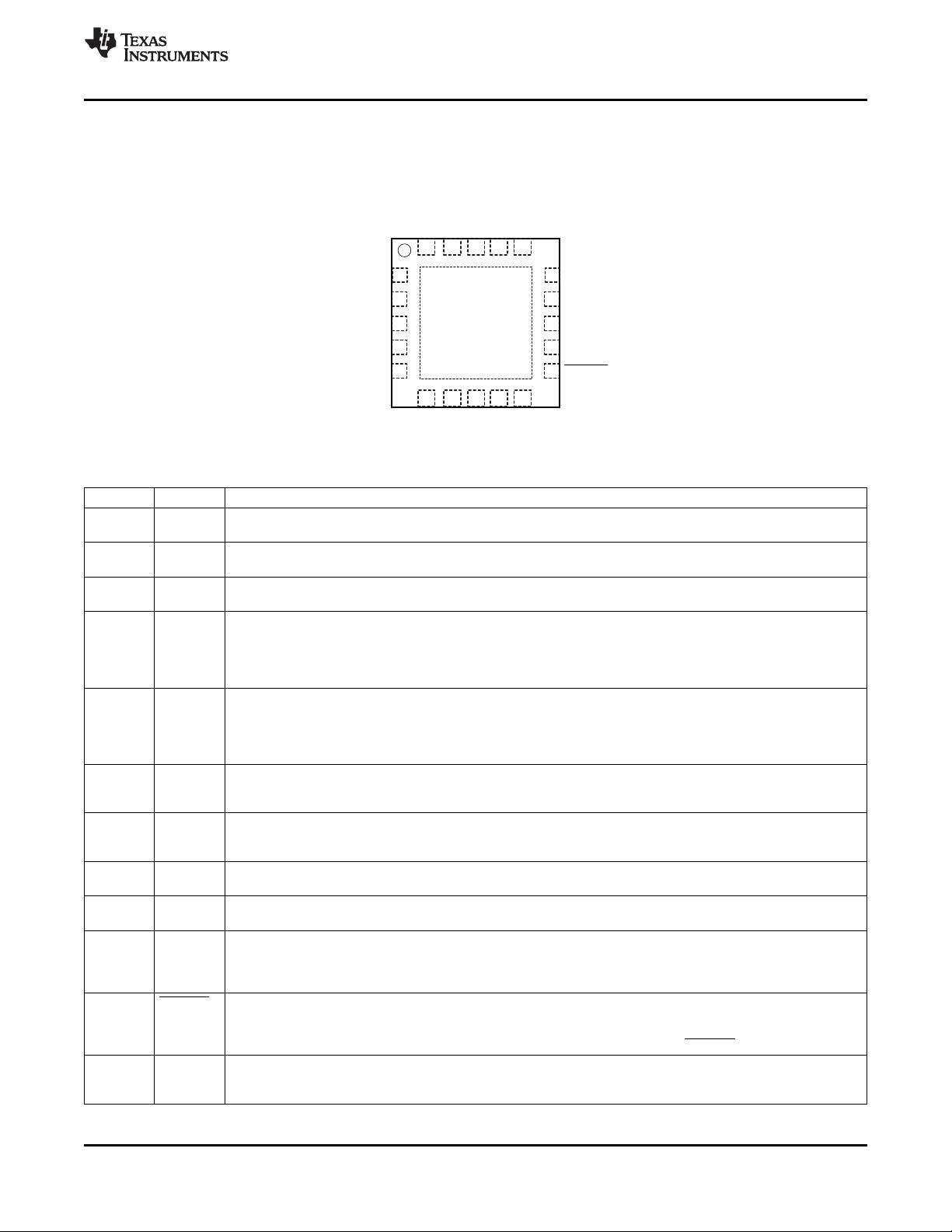

PIN CONFIGURATION

QFN PACKAGE

(TOP VIEW)

PIN DESCRIPTIONS

PIN NAME FUNCTION DESCRIPTION

1 ACN Input current sense resistor negative input. Place an optional 0.1µF ceramic capacitor from ACN to GND for

2 ACP Input current sense resistor positive input. Place a 1µF ceramic capacitor from ACP to GND for common-mode

3 CMSRC ACDRV charge pump source input. Place a 4kΩ resistor from CMSRC to the common source of ACFET (Q1) and

4 ACDRV Charge pump output to drive both adapter input n-channel MOSFET (ACFET) and reverse blocking n-channel

5 ACOK AC adapter detection open drain output. It is pulled HIGH to external pull-up supply rail by external pull-up resistor

6 ACDET Adapter detection input. Program adapter valid input threshold by connecting a resistor divider from adapter input

7 IOUT Buffered 40 times adapter or 16 times discharge current output - the differential voltage across sense resistor;

8 SDA SMBus open-drain data I/O. Connect to SMBus data line from the host controller or smart battery. Connect a

9 SCL SMBus open-drain clock input. Connect to SMBus clock line from the host controller or smart battery. Connect a

10 CELL Cell selection pin. For bq24715J, set CELL pin Float for 2-cell, and HIGH for 3-cell. Pulling CELL to GND will

11 BATDRV P-channel battery FET gate driver output. This pin can go high to turn off the battery FET, go low to turn on the

Copyright © 2013, Texas Instruments Incorporated 9

12 SRN Charge current sense resistor negative input. SRN pin is for battery voltage sensing as well. Connect SRN pin

common-mode filtering. Place a 0.1µF ceramic capacitor from ACN to ACP to provide differential mode filtering.

filtering. Place a 0.1µF ceramic capacitor from ACN to ACP to provide differential-mode filtering.

RBFET (Q2) limits the in-rush current on CMSRC pin.

MOSFET (RBFET). ACDRV voltage is 6.1V above CMSRC when voltage on ACDET pin is higher than 2.4V,

voltage on VCC pin is above UVLO but lower than 26V and voltage on VCC pin is 675mV above voltage on SRN

pin so that ACFET and RBFET can be turned on to power the system by AC adapter. Place a 4kΩ resistor from

ACDRV to the gate of ACFET and RBFET limits the in-rush current on ACDRV pin.

when voltage on ACDET pin is above 2.4V, VCC above UVLO but lower than 26V and voltage on VCC pin is

675mV above voltage on SRN pin, indicating a valid adapter is present to start charge. If any one of the above

conditions can not meet, it is pulled LOW to GND by internal MOSFET. Connect a 10kΩ pull up resistor from

ACOK to the pull-up supply rail.

to ACDET pin to GND pin. When ACDET pin is above 0.6V and VCC is above UVLO, REGN LDO is present,

ACOK comparator and IOUT are both active.

selectable with SMBus command ChargeOption(). Place a 100pF or less ceramic decoupling capacitor from IOUT

pin to GND.

10kΩ pull-up resistor according to SMBus specifications.

10kΩ pull-up resistor according to SMBus specifications.

provide a hardware exit function from LEARN mode, disable the input DPM function, reset the bit[5] and bit[1] in

chargeoption(), and reset Maxchargevoltage() to previous CELL pin default setting value and chargecurrent() to

zero. Release CELL from GND, charger will recheck CELL pin voltage and lock the new CELL pin selection.

battery FET, or operate battery FET in linear mode to regulate the minimum system voltage when battery is

depleted. Connect the source of the BATFET to the system load voltage node. Connect the drain of the BATFET

to the battery pack positive node. There is an internal pull-down resistor of 50k on BATDRV to ground.

with a 0.1µF ceramic capacitor to GND for common-mode filtering and connect to current sensing resistor.

Connect a 0.1µF ceramic capacitor between current sensing resistor to provide differential mode filtering.

SLUSBQ1 –AUGUST 2013

bq24715J

SLUSBQ1 –AUGUST 2013

PIN DESCRIPTIONS (continued)

PIN NAME FUNCTION DESCRIPTION

13 SRP Charge current sense resistor positive input. Connect a 0.1µF ceramic capacitor between current sensing resistor

to provide differential mode filtering.

14 GND IC ground. On PCB layout, connect to analog ground plane, and only connect to power ground plane through the

power pad underneath IC.

15 LODRV Low side power MOSFET driver output. Connect to low side n-channel MOSFET gate.

16 REGN Linear regulator output. REGN is the output of the 6V linear regulator supplied from VCC. The LDO is active when

voltage on ACDET pin is above 0.6V and voltage on VCC is above UVLO. Connect a 1µF ceramic capacitor from

REGN to GND.

17 BTST High side power MOSFET driver power supply. Connect a 0.047µF-0.1µF capacitor from BTST to PHASE.

Connect a bootstrap Schottky diode from REGN to BTST.

18 HIDRV High side power MOSFET driver output. Connect to the high side n-channel MOSFET gate.

19 PHASE High side power MOSFET driver source. Connect to the source of the high side n-channel MOSFET.

20 VCC Input supply. Use 10Ω resistor and 1µF capacitor to ground as low pass filter to limit inrush current.

PowerPad Exposed pad beneath the IC. Analog ground and power ground star-connected only at the PowerPad plane.

Always solder PowerPad to the board, and have vias on the PowerPad plane connecting to analog ground and

power ground planes. It also serves as a thermal pad to dissipate the heat.

www.ti.com

10 Copyright © 2013, Texas Instruments Incorporated

2ms Rising

Deglitch

40X

MUX

1X

16X

SELECTOR

LOGIC

ACDRV

CHARGE

PUMP

REGN

LDO

SMBUS Interface

ChargeOption()

ChargeCurrent()

ChargeV

oltage()

InputCurrent()

MinsysVoltage()

ManufactureID()

DeviceID()

UVLO

3.2V

WAKEUP

EN_REGN

ACOVP

0.6V

26V

2.4V

ACGOOD

VCC_SRN

ACOK_DRV

VREF_IAC

IOUT_SEL

VREF_ICHG

VFB

VREF_VREG

EN_CHRG

BATOVP or

SYSOVP

4mA

DAC_VALID

CHARGE_INHIBIT

EN_LEARN

VREF_VREG

VREF_ICHG

VREF_IAC

VREF_SYSMIN

IOUT_SEL

EN_DPM

10uA

FBO

PWM/PFM

ACOK_DRV

ACDRV

CMSRC+5.9V

ACDRV_CMSRC

SYSOVP

ACOC

ACGOOD

CHARGE_INHIBIT

DAC_VALID

EN_LEARN

WATCHDOG

TIMER 175s**

WD_TIMEOUT

EN_CHRG

Tj

155C

TSHUT

ILIM_HI

GND_PHASE

350mV**

ILIM_LOW

GND

PHASE

LIGHT_LOAD

1.25mV

ACP_ACN

ACOC

ACP_ACN

3.33xVREF_IAC**

REFRESH

4.15V

BTST_PH

BATOVP

SRN

104%VREF_VREG

VCC_SRN

VCC

SRN+375mV

TRI-STAT

BUFFER

CELL_CNT

CELL_LO

WAKEUP

SYSOVP

SRN

V

SYSOVP

**

EN_AUDIOFREQ

EN_LDOMODE

EN_AUDIOFREQ

CELL_LOW

EN_PRECHRG

EN_FASTCHRG

EN_SUPPLEMENT

EN_PRECHRG

EN_FASTCHRG

EN_SUPPLEMENT

EN_CHRG

EN_REGN

IOUT_SEL

EN_LDOMODE

VCC

ACDET

ACOK

ACP

ACN

IOUT

SRP

SRN

SDA

SCL

CELL

GND

LODR

V

REGN

PHASE

HIDRV

BTST

BATDRV

CMSRC

ACDRV

SRP

VREF_SYSMIN

bq24715J

** Threshold is adjustable

by ChargeOption()

SRN

SRN-6V

20

6

5

2

1

7

13

12

8

9

10

14

15

16

19

18

17

11

3

4

PWM

DRIVER

LOGIC

EN_DPM

CONVERTER

CONTROL

www.ti.com

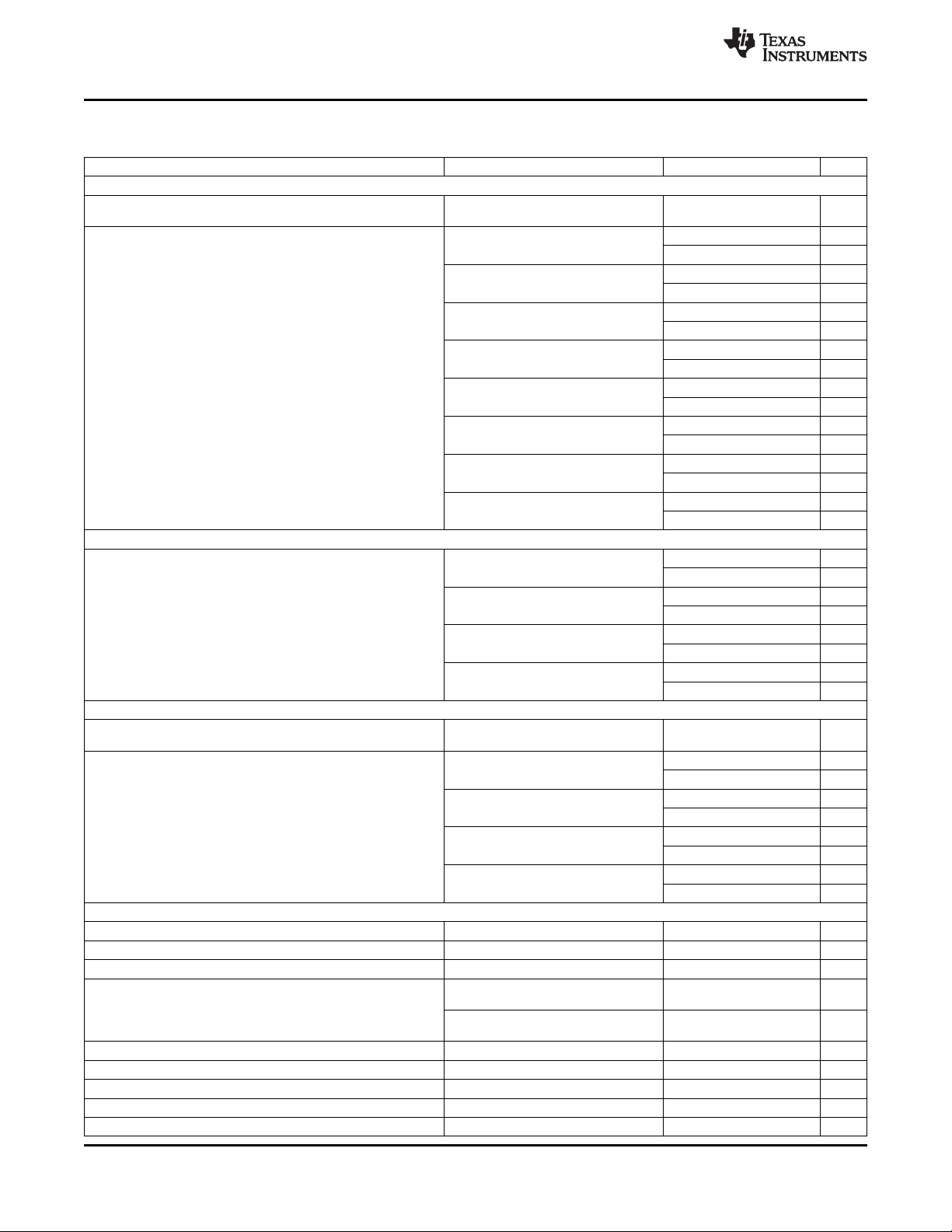

bq24715J

SLUSBQ1 –AUGUST 2013

Copyright © 2013, Texas Instruments Incorporated 11

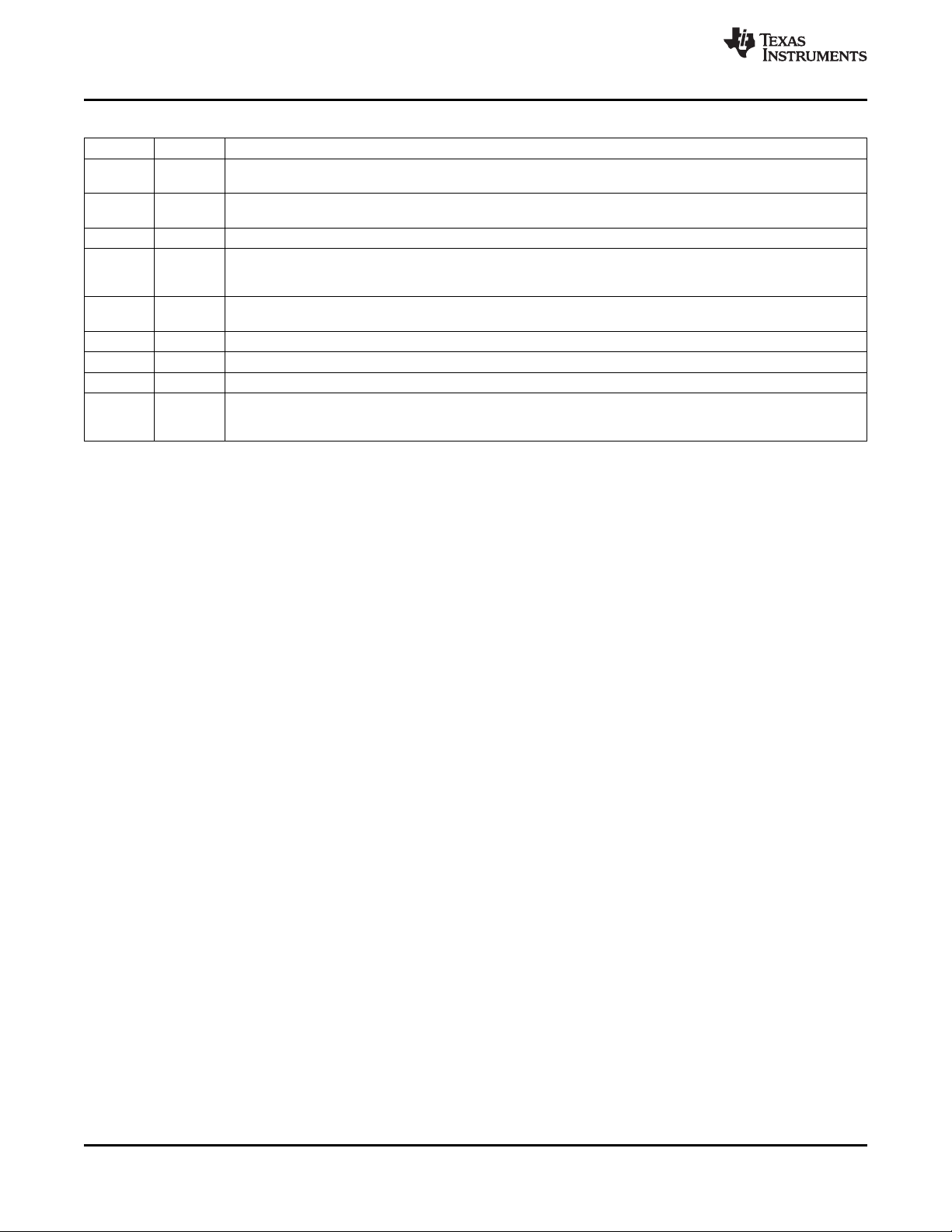

Figure 2. Block Diagram

REGN

BTST

HIDRV

PHASE

LODRV

GND

SRP

SRN

/BATDRV

Q3

L: 2.2µH

SYSTEM LOAD

Csys

10µFx2

Rsns

10mΩ

R1

430kΩ

R2

66.5kΩ

C3

0.1µF

C6

10µFx2

VCC

Q4

Q1B

C8

47nF

Adapter

RAC 10mΩ

Battery

Pack

C9

C7:1µF

HOST

Dig I/O

SMBus

+3.3V

R8

10kΩ

ACN

ACP

CMSRC

ACDRV

ACDET

SDA

SCL

ACOK

IOUT

PowerPAD

D1

R6

10Ω

C5

1 Fµ

R9

10kΩ

Q2

C4

0.1µF

C2

1µF

R3

4kΩ

C1

0.1µF

R4

4kΩ

C11

100

pF

A/D

bq24715J

GND

Q1A

C12

200 µF

C13

D2

R5

C10

1µF

15 Ω

BAT54

BAT54

CSD17308Q3

CSD25401Q3

CSD87312Q3E

CSD17308Q3

0.1µF

0.1µF

10kΩ

R7

R10

100k

Ω

REGN

CELL

bq24715J

SLUSBQ1 –AUGUST 2013

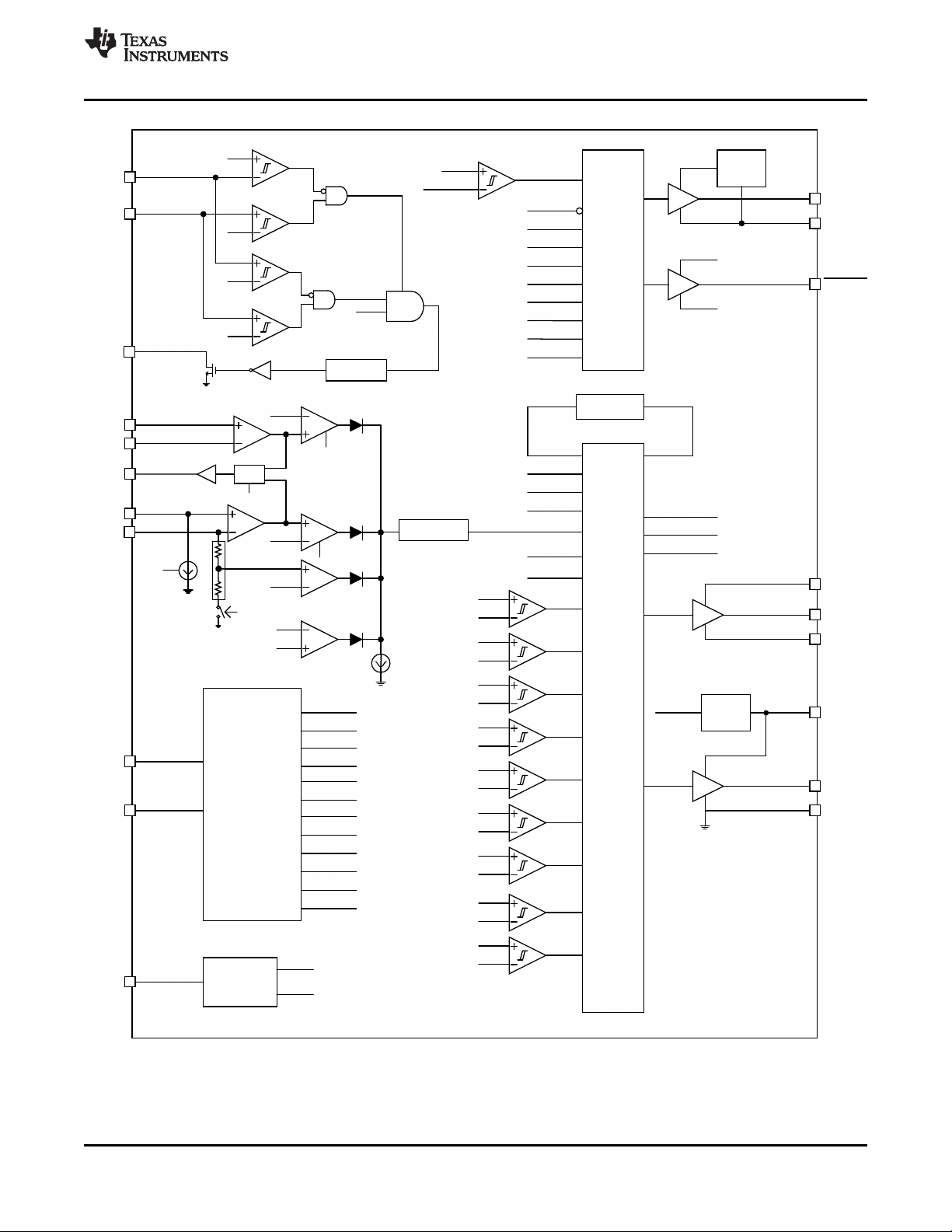

TYPICAL APPLICATION DIAGRAM

www.ti.com

Fs = 800kHz, I

Csys : 200 µF is lumped system bus capacitance

ADPT

= 3.0A, I

CHRG

= 2.944A, I

SYSTEM

= 5A, V

= 12.592V, 65W adapter and 3S2P battery pack

CHRG

Figure 3. Typical Application Circuit

12 Copyright © 2013, Texas Instruments Incorporated

Loading...

Loading...