Texas Instruments BQ2058SN-C5TR, BQ2058SN-C5, BQ2058RSN-C5TR, BQ2058RSN-C5, BQ2058DSN-C5 Datasheet

...

bq2058

Lithium Ion Pack Supervisor

for 3- and 4-Cell Packs

Features

Protects and individually moni

➤

tors three or four Li-Ion series

cells for overvoltage, undervolt

age

Monitors pack for overcurrent

➤

Designed for battery pack inte

➤

gration

Minimal external components

➤

Drives external FET switches

➤

Selectable overvoltage (V

➤

thresholds

Mask-programmable by

-

Unitrode

- Standard version–4.25V

➤ Supply current: 25µA typical

➤ Sleep current: 0.7µA typical

➤ 16-pin 150-mil narrow SOIC

General Description

The bq2058 Lithium Ion Pack Super

visor is designed to control the charge

and discharge cell voltages for three or

four lithium ion (Li-Ion) series cells,

accommodating battery packs contain

ing series/parallel configurations. The

low operating current does not over

discharge the cells during periods of

storage and does not significantly in

crease the system discharge load. The

bq2058 can be part of a low-cost Li-Ion

charge control system within the bat

tery pack.

)

OV

The bq2058 controls two external FETs

to limit the charge and discharge potentials. The bq2058 allows charging when

each individual cell voltage is below V

(overvoltage limit). If the voltage on any

cell exceeds V

delay period (t

driven high, shutting off charge to the

battery pack. This safety feature pre-

for a user-configurable

OV

), the CHG pin is

OVD

vents overcharge of any cell within

the battery pack. After an overvolt

age condition occurs, each cell must

fall below V

for the bq2058 to re-enable charging.

(charge enable voltage)

CE

The bq2058 protects batteries from

-

overdischarge. If the voltage on any

cell falls below V

-

limit) for a user-configurable delay pe

riod (t

-

high, shutting off the battery dis

), the DSG output is driven

UVD

(undervoltage

UV

charge. This safety feature prevents

overdischarge of any cell within the

-

battery pack.

The bq2058 also stops discharge on

detection of an overcurrent condition,

such as a short circuit. If an overcurrent condition occurs for a userconfigurable delay period (t

OV

DSG

output is driven high, disconnecting the load from the pack. DSG

mains high until removal of the short

circuit or overcurrent condition.

OCD

-

-

-

), the

re-

Pin Connections

16

1

2

15

3

14

4

13

5

12

6

11

7

10

8

9

1/99 I

BAT

BAT

BAT

BAT

CHG

CTL

V

CSL

SS

4N

3N

2N

1N

16-Pin Narrow SOIC

DSG

NSEL

UVD

OVD

OCD

V

CC

CSH

BAT

PN205801.eps

Pin Names

CHG Charge control output

CTL Pack disable input

V

SS

Low potential input

CSL Current sense low-side

input

BAT

BAT

1P

BAT

BAT

Battery 4 negative input

4N

Battery 3 negative input

3N

Battery 2 negative input

2N

Battery 1 negative input

1N

1

DSG Discharge control output

NSEL 3- or 4-cell selection

UVD Undervoltage delay input

OVD Overvoltage delay input

OCD Overcurrent delay input

V

CC

High potential input

CSH Current sense high-side

input

BAT

Battery 1 positive input

1P

bq2058

Pin Descriptions

CHG Charge control output

This push-pull output controls the charge

path to the battery pack. Charging is al

lowed when low.

CTL Pack disable input

When high, this input allows an external

source to disable the pack by making both

DSG

and CHG inactive. For normal opera

tion, the CTL pin is low.

V

SS

CSL Overcurrent sense low-side input

BAT

BAT

BAT

BAT

Low potential input

This input is connected between the low-side

discharge FET (or sense resistor) and BAT

to enable overcurrent sensing in the battery

pack’s ground path.

Battery 4 negative input

4N

This input is connected to the negative terminal of the cell designated BAT4 in Figure 2.

Battery 3 negative input

3N

This input is connected to the negative terminal

of the cell designated BAT3 in Figure 2.

Battery 2 negative input

2N

This input is connected to the negative termi

nal of the cell designated BAT2 in Figure 2.

Battery 1 negative input

1N

This input is connected to the negative termi

nal of the cell designated BAT1 in Figure 2.

This input is connected to BAT

cell configuration.

DSG

-

Discharge control output

This push-pull output controls the discharge

path to the battery pack. Discharge is al

lowed when low.

NSEL Number of cells input

This input selects the number of series cells

-

in the pack. NSEL should connect to V

four cells and to V

for three cells.

SS

UVD Undervoltage delay input

This input uses an external capacitor to V

to set the undervoltage delay timing.

OVD Overvoltage delay input

4N

This input uses an external capacitor to V

to set the overvoltage delay timing.

OCD Overcurrent delay input

This input uses an external capacitor to V

to set the overcurrent delay timing.

V

CC

High potential input

CSH Overcurrent sense high-side input

This input is connected between the

high-side discharge FET (or sense resistor)

-

BAT

-

and BAT

the battery pack’s positive supply path.

Battery 1 positive input

1P

This input is connected to the positive terminal

of the cell designated BAT1 in Figure 2.

to enable overcurrent sense in

1P

in a three-

1P

CC

-

for

CC

CC

CC

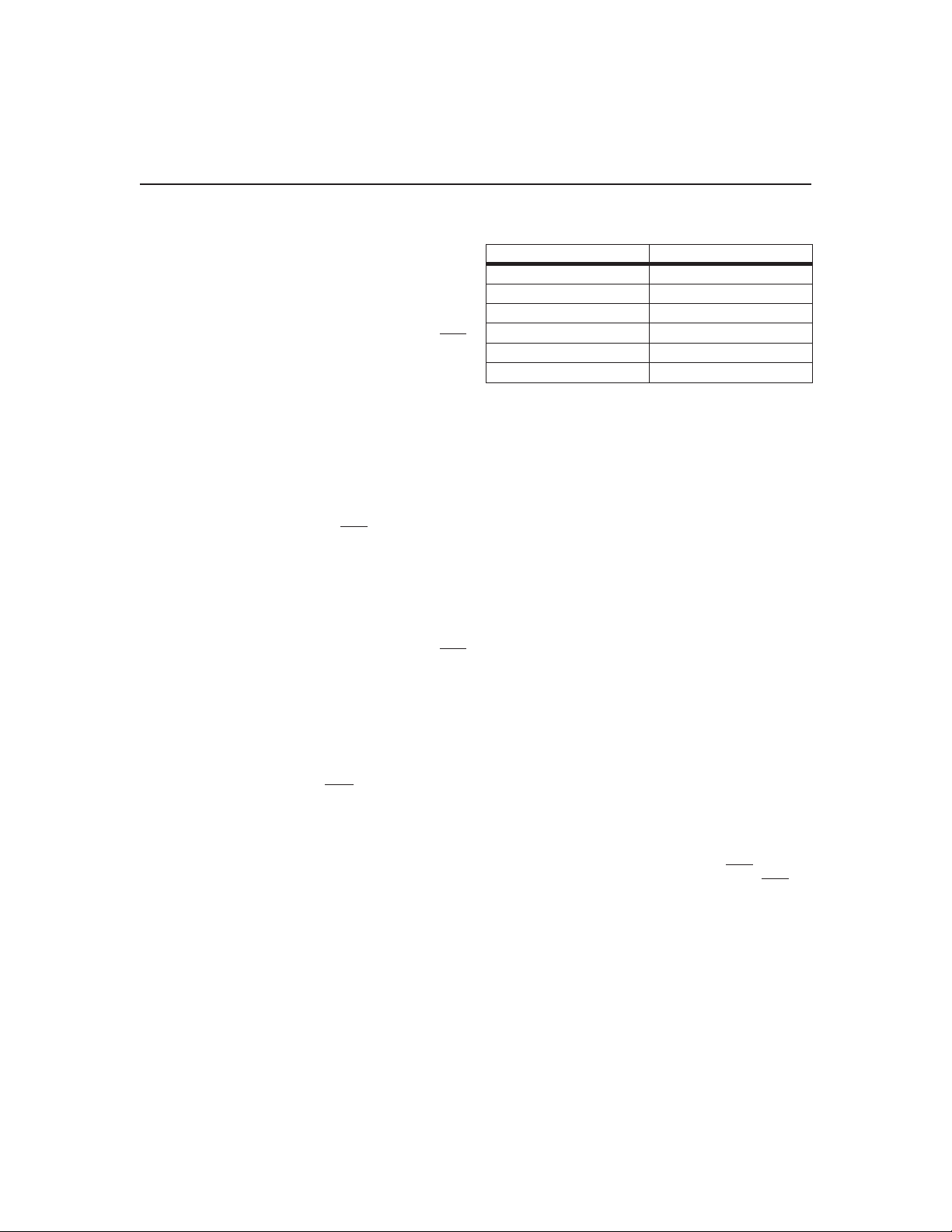

Table 1. Pin Configuration for 3- and 4-Series Cells

Number of Cells Configuration Pins Battery Pins

BAT1N– Positive terminal of first cell

BAT

– Negative terminal of first cell

3 cells

4 cells

BAT

tied to BAT

1N

NSEL = V

NSEL = V

1P

SS

CC

2

2N

BAT

– Negative terminal of second cell

3N

BAT

– Negative terminal of third cell

4N

BAT1P– Positive terminal of first cell

BAT

– Negative terminal of first cell

1N

BAT

– Negative terminal of second cell

2N

BAT

– Negative terminal of third cell

3N

BAT

– Negative terminal of fourth cell

4N

Cell Inputs

Pin 9

Pin 8

Pin 7

Pin 6

Pin 5

Pin 3

Chip Negative

Supply

B1P

B1N

B2N

B3N

B4N

V

Sel4

Sel3

Sel2

Sel1

OV

V

V

bq2058

+

-

+

Sel4

Sel3

Sel2

Sel1

Sel4

Sel3

Sel2

+

Sel1

CE

Sel4

+

Sel3

UV

Sel2

Sel1

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Q

D

CK

QB

Pin 10

Pin 9

Pin 4

Pin 5

CSH

B1P

CSL

B4N

160mV

160mV

Number of Cells Select

Pin 15

NSEL

Sleep

Any_Above_V

Any_Below_V

OV

OVD

Pin 13

Discharge Off Delay Capacitor Input

UV

Edge

Reset

Capacitor

UVD

Pin 14

Charge Off Delay Capacitor Input

Sense High-side Input

CSH

Pin 10

Pin 9

Pin 4

Pin 5

Overcurrent Delay

Capacitor Input

+

+

70mV

B1P

Sense Low-side Input

CSL

70mV

B4N

+

Pin 12

OCD

NSEL

Sleep

Clock

Sel4

Sel3

Sel2

Sel1

Edge

Non-Retrigger

Oneshot

Reset

Capacitor

All_Below_V

Out

Non-Retrigger

Oneshot

+

Edge

Reset

Out

Non-Retrigger

Oneshot

Capacitor

Pin 2

CTL

External Output Control

Out

Sel4

Sel3

Sel2

Sel1

D

CK

Reset

QB

CE

D

CK

Reset

D

CK

Reset

Sleep

Q

QB

QB

Overcharge

Pin 1

CHG

Charge Control

Output

Pin 16

DSG

Discharge Control

Output

Overcurrent

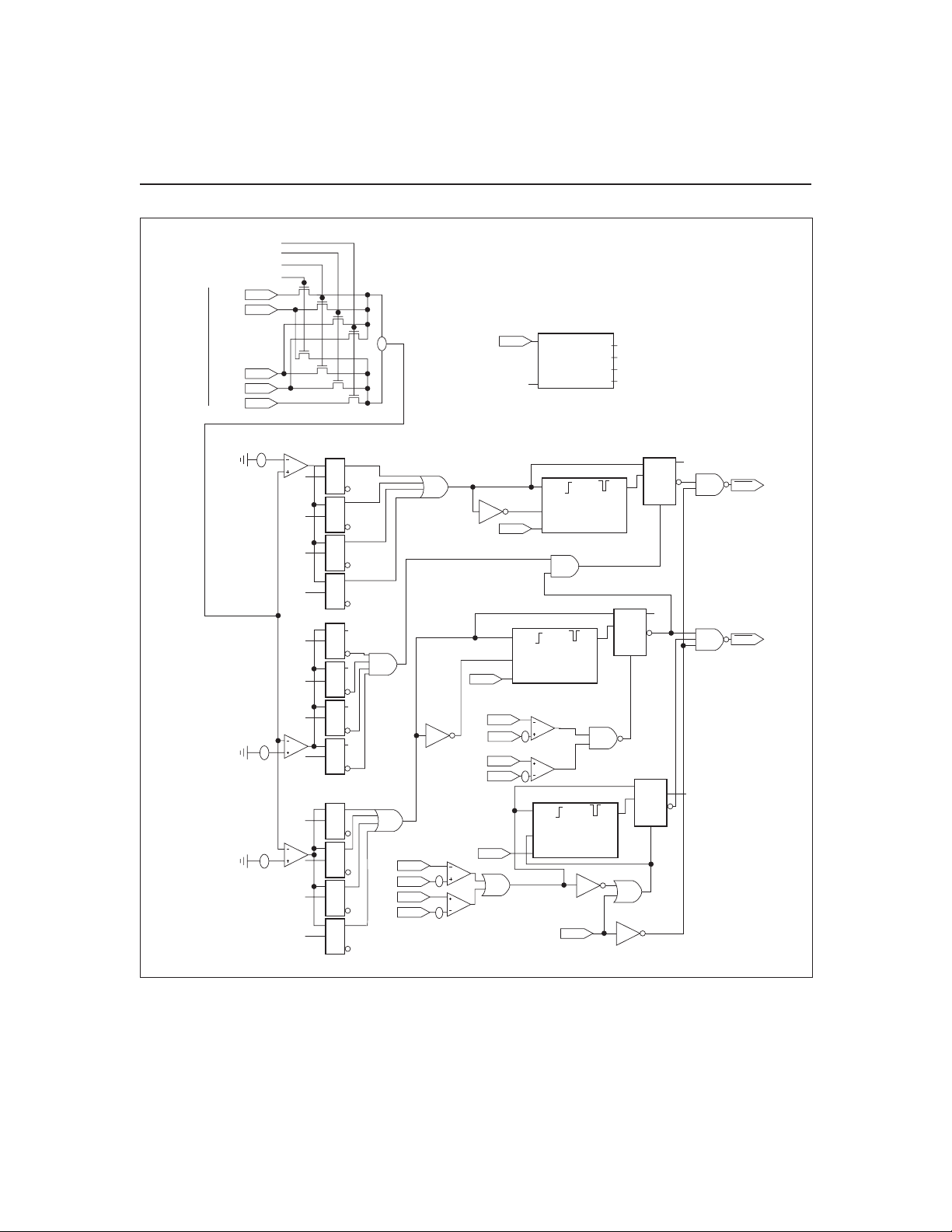

Figure 1. Block Diagram

3

bq2058

Functional Description

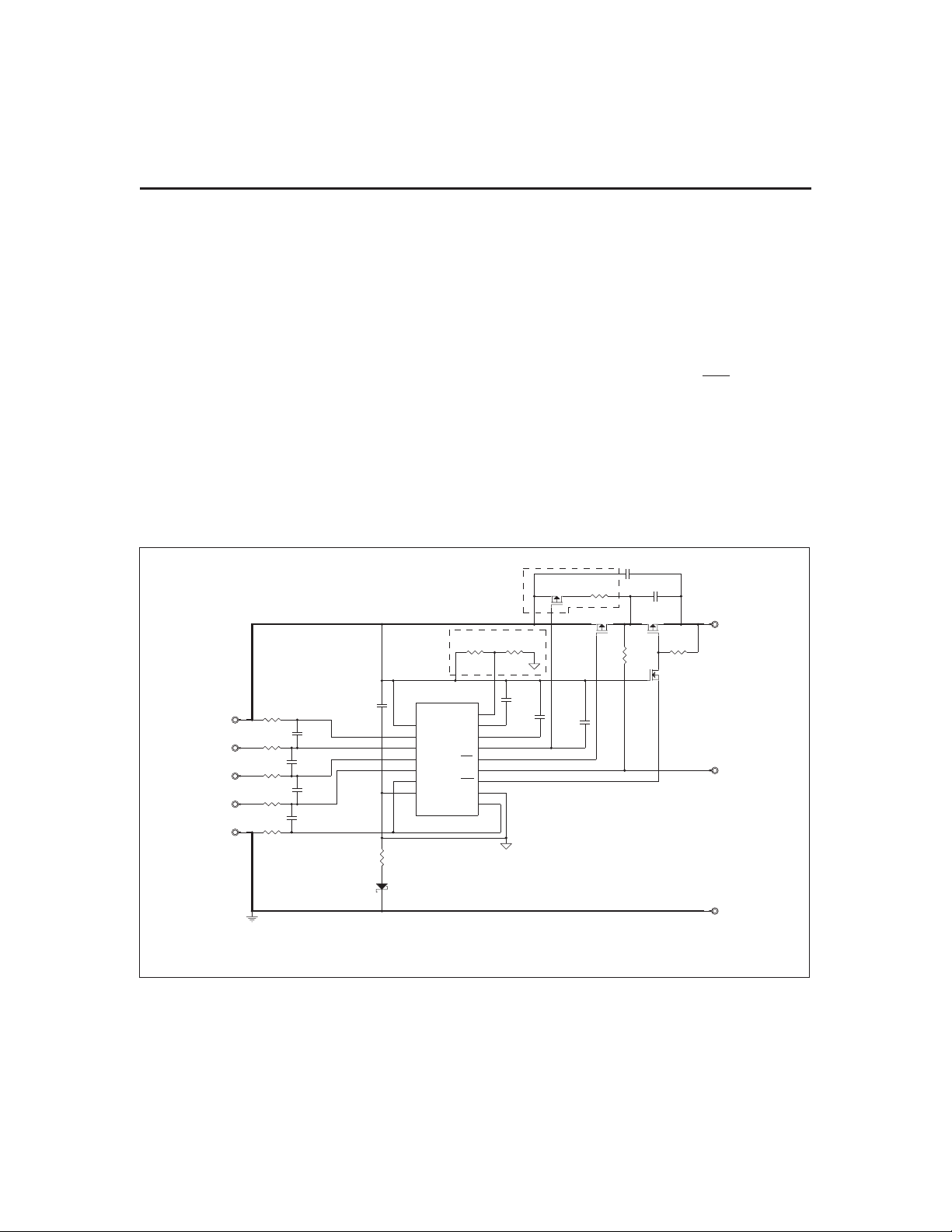

Figure 1 is a block diagram outlining the major compo

nents of the bq2058. Figure 2 shows a 3- or 4-cell pack

supervisor circuit. The following sections detail the vari

ous functional aspects of the bq2058.

Thresholds

The bq2058 monitors the lithium ion pack for the condi

tions listed below. Shown with these conditions are the

respective thresholds used to determine if that condition

exists:

Overvoltage (VOV)

■

Undervoltage (VUV)

■

Overcurrent (V

■

Charge Enable (VCE)

■

Charge Detect (VCD)

■

B1P

B1N

B2N

B3N

B4N

OCH,VOCL

R3

10K

R4

10K

R5

10K

R7

10K

R8

10K

Notes:

1. For automatic short circuit recovery.

2. Remove R11 for 4-cell. Remove R10 and connect

B1P to B1N for 3-cells.

0.001uF

C2

0.001uF

0.001uF

C4

0.001uF

)

* See note 2.

U1

C9

0.1uF

C1

C3

R1

2.7K

D1

BAT54

bq2058

11

VCC

9

BAT1P

8

BAT1N

7

BAT2N

6

BAT3N

5

BAT4N

3

VSS

The bq2058 samples a cell every 40ms (typical). Every

sample is a fully differential measurement of each cell.

During this sample period, the bq2058 compares the

measurements with these thresholds to determine if any

of the these conditions exist: V

-

OV,VUV

, and VCE.

Overcurrent and charge detect are conditions that are

not sampled, but are continuously monitored.

Initialization

-

On initial power-up, such as connecting the battery pack

for the first time to the bq2058, the bq2058 enters the

low-power sleep mode, disabling the DSG

output. It is

recommended that a top to bottom cell connection

be made at pack assembly for proper initializa

tion. A charging supply must be applied to the bq2058

circuit to enable the pack. See Low-Power Sleep Mode

and Charge Detect sections.

R2

6.98K

Q2

Si4435DY

100K

C8

0.1uF

C6

0.1uF

Q1

Si4435DY

R9

Q3

2N7002

1M

R6

POS

TP1

NEG

NSEL

4-Cell

OVD

UVD

OCD

DSG

CSH

CHG

CTL

CSL

R10

0 Ohm

* See note 1.

Q4

ZVP3306F

R11

0 Ohm

3-Cell

C10

0.1uF

15

C5

13

0.1uF

14

12

16

10

1

2

4

0.01uF

C7

-

Figure 2. 3- or 4-Cell Li-Ion Battery Pack Supervisor

4

bq2058

Low-Power Sleep Mode

The bq2058 enters the low-power sleep mode in two dif

ferent ways:

1. On initial power-up.

2. After the detection of an undervoltage condi

UV

.

tion–V

When the bq2058 enters the low-power sleep mode, DSG

is driven high and the device consumes 0.7µA (typical).

The bq2058 only comes out of low-power sleep mode

when a valid charge-detect condition exists.

Charge Detect

The bq2058 continuously monitors for a charge-detect con

dition. A valid charge-detect condition exists when either

of the conditions are true:

CSL < BAT

CSH > BAT

A valid charge-detect enables the DSG

- 70mV (VCD)

4N

+ 70mV (VCD)

1P

output, allowing

charging of the lithium ion cells. This is accomplished

by applying the charging supply to the pack.

Undervoltage

Undervoltage (or overdischarge) protection is asserted

when any cell voltage drops below the V

and remains below the V

exceeding a user-configurable delay (t

threshold for a time

UV

UV

). The DSG

UVD

threshold

output is driven high disabling the discharge of the

pack. The bq2058 then enters the low-power sleep

mode.

Overvoltage

Overvoltage (or overcharge) protection is asserted when

any cell voltage exceeds the V

above the V

configurable delay (t

disabling charge into the battery pack. Charging is dis

threshold for a time exceeding a user-

OV

). The CHG pin is driven high,

OVD

abled until a valid charge enable exists. See Charge En

able section.

Important note: If any battery pin floats (BAT

BAT

), the bq2058 assumes an overvoltage has

1N–4N

occurred.

Because of different manufacturers specifications for

overvoltage thresholds, the bq2058 can be available with

different V

options. Table 2 summarizes these differ

OV

ent voltage thresholds.

threshold and remains

OV

1P

Table 2. Overvoltage Threshold Options

-

bq2058 4.25V

bq2058C 4.325

bq2058D 4.30V

bq2058G* 4.375V

bq2058R 4.35V

bq2058W 3.4V

The overvoltage threshold limits are programmed

at Unitrode. The bq2058 is the standard option

-

that is more readily available for sampling and

prototyping purposes. Please contact Unitrode

for other voltage threshold and tolerance options.

Part No. VOVLimit

Charge Enable

A valid charge enable indicates that an overvoltage

(overcharge) condition no longer exists and that the

pack is ready to accept further charge. Once overvoltage

protection is asserted, charging will not be enabled until all cell voltages fall below V

a function of V

its.

and changes with different VOVlim-

OV,

V

= VOV- 150mV

CE

. The VCEthreshold is

CE

Overcurrent

The bq2058 detects an overcurrent (or short circuit) condition only in the discharge direction. Overcurrent pro

tection is asserted when either of the conditions occurs

and remain for a time exceeding a user-configurable de

lay (t

where:

-

-

,

When either of these conditions occurs, DSG

high, disconnecting the load from the pack. DSG

mains high until both of the voltage conditions are false,

indicating removal of the short-circuit condition. The

user can facilitate clearing these conditions by inserting

-

the battery pack into a charger.

The low-side overcurrent sense can be disabled by con

necting CSL to BAT

greater than BAT

high-side detection must be used with CSH.

OCD

):

CSL > BAT

CSH < BAT1P- V

V

= 160mV (low-side detect)

OCL

V

= 160mV (high-side detect)

OCH

. This ensures that CSL is never

4N

. If low-side detection is disabled,

4N

4N

+ V

OCL

OCH

is driven

re

-

-

-

-

5

Loading...

Loading...