Texas Instruments 5962-9679002NXB, 5962-9679001NXB Datasheet

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

D

Military Operating Temperature Range

– 55°C to 125°C; QML Processing

D

High-Performance Floating-Point Digital

Signal Processor (DSP)

SMQ320C32-50 (5 V)

– 40-ns Instruction Cycle Time

– 275 MOPS

– 50 MFLOPS

– 25 MIPS

SMQ320C32-60 (5 V)

– 33-ns Instruction Cycle Time

– 330 MOPS

– 60 MFLOPS

– 30 MIPS

D

32-Bit High-Performance CPU

D

16-/32-Bit Integer and 32-/40-Bit

Floating-Point Operations

D

32-Bit Instruction Word, 24-Bit Addresses

D

Two 256 × 32-Bit Single-Cycle, Dual-Access

On-Chip RAM Blocks

D

Flexible Boot-Program Loader

D

On-Chip Memory-Mapped Peripherals:

– One Serial Port

– Two 32-Bit Timers

– Two-Channel Direct Memory Access

(DMA) Coprocessor With Configurable

Priorities

D

Enhanced External Memory Interface That

Supports 8-/16-/32-Bit-Wide External RAM

for Data Access and Program Execution

From 16-/32-Bit-Wide External RAM

D

SMJ320C30 and SMJ320C31 Object Code

Compatible

D

Fabricated Using 0.7-µm Enhanced

Performance Implanted CMOS (EPIC)

Technology by Texas Instruments

D

144-Pin Plastic Quad Flatpack

(PCM Suffix) 5 V

D

Eight Extended-Precision Registers

D

T wo Address Generators With Eight

Auxiliary Registers and Two Auxiliary

Register Arithmetic Units (ARAUs)

D

Two Low-Power Modes

D

Two- and Three-Operand Instructions

D

Parallel Arithmetic Logic Unit (ALU) and

Multiplier Execution in a Single Cycle

D

Block-Repeat Capability

D

Zero-Overhead Loops With Single-Cycle

Branches

D

Conditional Calls and Returns

D

Interlocked Instructions for

Multiprocessing Support

D

One External Pin, PRGW, That Configures

the External-Program-Memory Width to

16 or 32 Bits

D

Two Sets of Memory Strobes (STRB0 and

STRB1

) and One I/O Strobe (IOSTRB)

Allow Zero-Glue Logic Interface to Two

Banks of Memory and One Bank of External

Peripherals

D

Separate Bus-Control Registers for Each

Strobe-Control Wait-State Generation,

External Memory Width, and Data Type Size

D

STRB0 and STRB1 Memory Strobes Handle

8-, 16-, or 32-Bit External Data Accesses

(Reads and Writes)

D

Multiprocessor Support Through the HOLD

and HOLDA Signals Is Valid for All Strobes

description

The SMQ320C32 is a member of the ’320C3x generation of digital signal processors from Texas Instruments.

The SMQ320C32 is an enhanced 32-bit floating-point processor manufactured in 0.7-µm triple-level-metal

CMOS technology. The enhancements to the ’320C3x architecture include a variable-width external-memory

interface, faster instruction cycle time, power-down modes, two-channel DMA coprocessor with configurable

priorities, flexible bootloader, relocatable interrupt-vector table, and edge- or level-triggered interrupts.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

EPIC is a trademark of Texas Instruments Incorporated.

Copyright 1999, Texas Instruments Incorporated

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

description (continued)

The internal busing and special digital signal processing instruction set of the SMQ320C32 have the speed and

flexibility to execute up to 50 million floating-point operations per second (MFLOPS). The SMQ320C32

optimizes speed by implementing functions in hardware that other processors implement through software or

microcode. This hardware-intensive approach provides performance previously unavailable on a single chip.

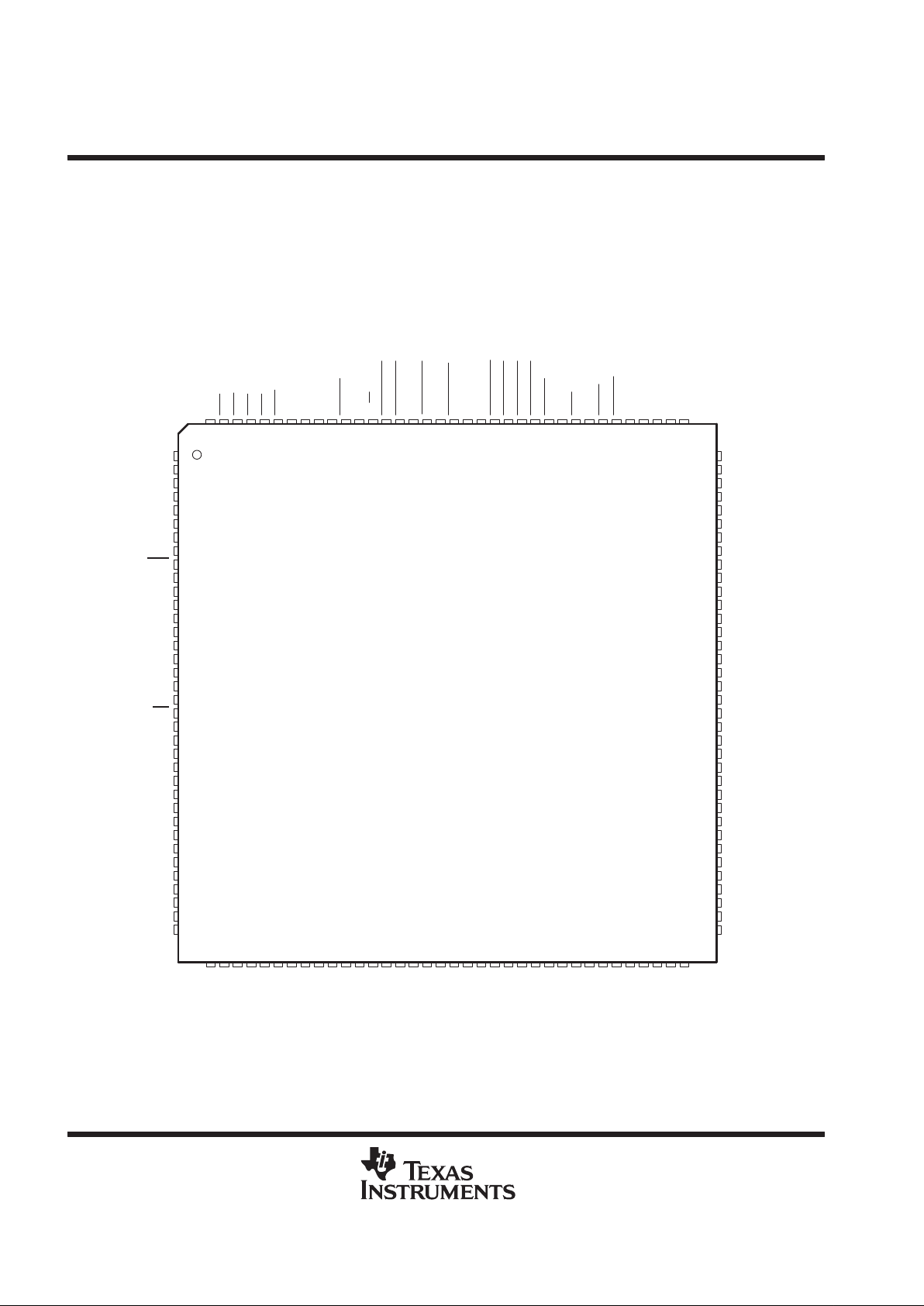

STRB1_B2/A

PCM PACKAGE

†

(TOP VIEW)

V

V

H3

H1

D0

D1

D2

D3

DV

DD

D4

D5

D6

D7

D8

D9

V

SSL

V

SSL

DV

SS

CV

SS

D10

DV

DD

D11

IV

SS

D12

V

DDL

V

DDL

D13

D14

D15

D16

D17

DV

DD

D18

D19

D20

D21

DV

SS

CV

SS

DR0

DV

DD

FSR0

CLKR0

CLKX0

FSX0

DX0

IV

SS

SHZ

TCLK0

TCLK1

DV

DD

EMU3

EMU0

V

DDL

V

DDL

EMU1

EMU2

V

SSL

MCBL/MP

CV

SS

DV

SS

A23

A22

A21

A20

A19

A18

DV

DD

A17

A16

A15

A14

A13

CV

SS

DV

SS

NC

144

INT3

INT2

143

142

INT1

141

INT0

140

IACK

139

XF1

138

XF0

137DV136CV135

RESET

134

PRGW

133

R/W

132

STRB1_B0

131

STRB1_B1

130

129

128

127

STRB1_B3/A

126

125V124

STRB0_B0

123

STRB0_B1

122

STRB0_B2/A

121

STRB0_B3/A

120

IOSTRB

119IV118

117DV116

HOLD

115

HOLDA

114

CLKIN

113

112

373839404142434445464748495051525354555657585960616263646566676869

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

NC

A12

A11

A10

A9A8A7

A6DDA5A4A3

DDL

SSL

SSL

A0

DD

D31

D30

D29

D28

D27

D26SSD25DDD24

D23

A1

DDL

111

CV

110

NC

109

707172

D22

NC

RDY

SS

–1

V

DV

A2

SS

CV

DD

DV

–2

DV

V

V

DV

V

V

DV

IV

DV

SS

SS

SSL

DDL

DDL

SS

DD

SS

SS

SUBS

DV

DD

–2

–1

†

NC=No internal connection

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

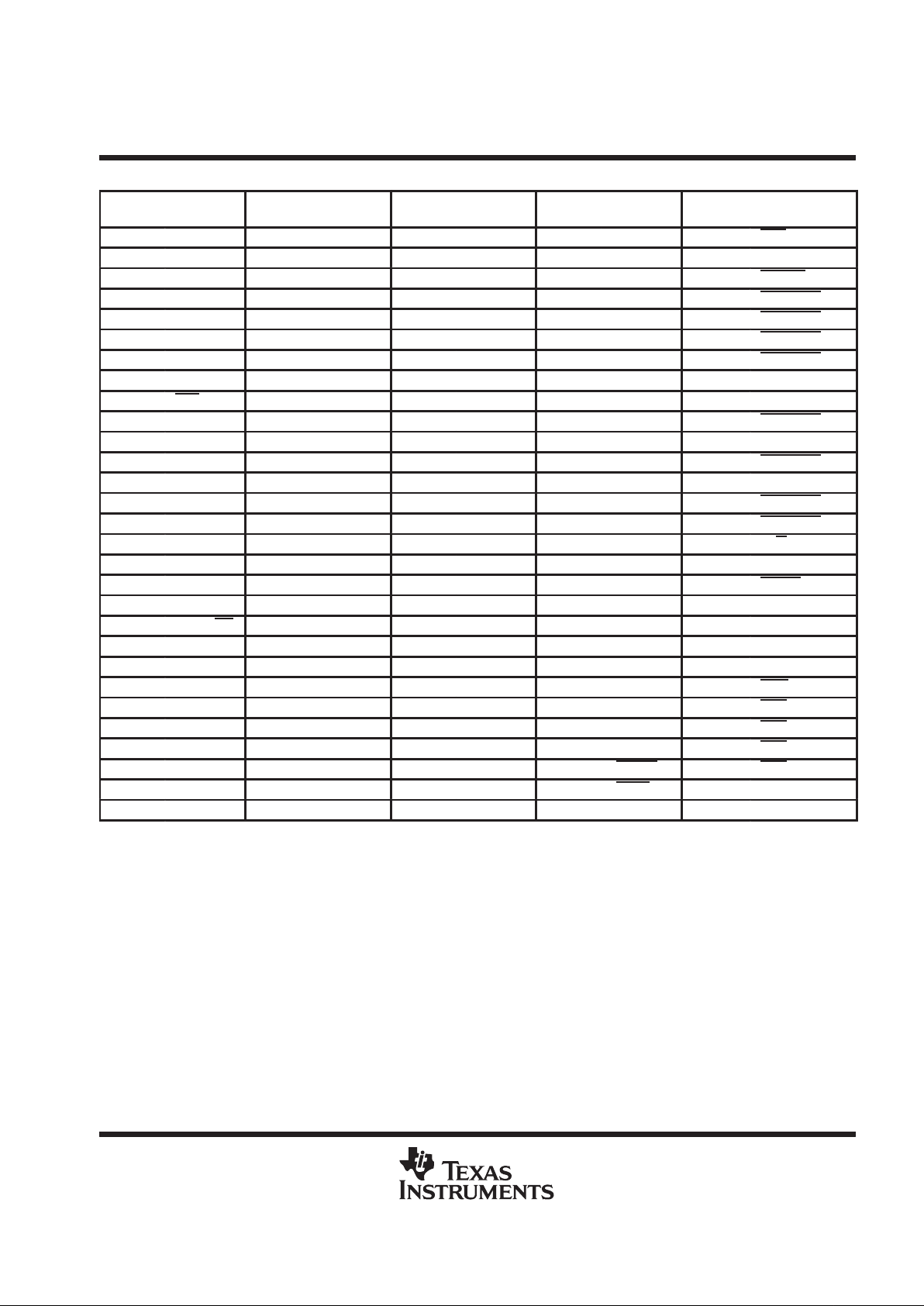

Pin Assignments

PIN PIN PIN PIN PIN

NUMBER NAME NUMBER NAME NUMBER NAME NUMBER NAME NUMBER NAME

1 DR0 30 A17 59 DV

DD

88 IV

SS

117 RDY

2 DV

DD

31 A16 60 D31 89 D11 118 IV

SS

3 FSR0 32 A15 61 D30 90 DV

DD

119 IOSTRB

4 CLKR0 33 A14 62 D29 91 D10 120 STRB0_B3/A

–1

5 CLKX0 34 A13 63 D28 92 CV

SS

121 STRB0_B2/A

–2

6 FSX0 35 CV

SS

64 D27 93 DV

SS

122 STRB0_B1

7 DX0 36 DV

SS

65 D26 94 V

SSL

123 STRB0_B0

8 IV

SS

37 NC 66 IV

SS

95 V

SSL

124 V

DDL

9 SHZ 38 A12 67 D25 96 D9 125 V

DDL

10 TCLK0 39 DV

DD

68 DV

DD

97 D8 126 STRB1_B3/A

–1

11 TCLK1 40 A11 69 D24 98 D7 127 V

SSL

12 DV

DD

41 A10 70 D23 99 D6 128 STRB1_B2/A

–2

13 EMU3 42 A9 71 D22 100 D5 129 DV

DD

14 EMU0 43 A8 72 NC 101 D4 130 STRB1_B1

15 V

DDL

44 A7 73 CV

SS

102 DV

DD

131 STRB1_B0

16 V

DDL

45 A6 74 DV

SS

103 D3 132 R/W

17 EMU1 46 DV

DD

75 D21 104 D2 133 PRGW

18 EMU2 47 A5 76 D20 105 D1 134 RESET

19 V

SSL

48 A4 77 D19 106 D0 135 CV

SS

20 MCBL/MP 49 A3 78 D18 107 H1 136 DV

SS

21 CV

SS

50 V

DDL

79 DV

DD

108 H3 137 XF0

22 DV

SS

51 V

DDL

80 D17 109 NC 138 XF1

23 A23 52 A2 81 D16 110 V

SUBS

139 IACK

24 A22 53 CV

SS

82 D15 111 CV

SS

140 INT0

25 A21 54 DV

SS

83 D14 112 DV

SS

141 INT1

26 A20 55 A1 84 D13 113 CLKIN 142 INT2

27 A19 56 V

SSL

85 V

DDL

114 HOLDA 143 INT3

28 A18 57 V

SSL

86 V

DDL

115 HOLD 144 NC

29 DV

DD

58 A0 87 D12 116 DV

DD

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

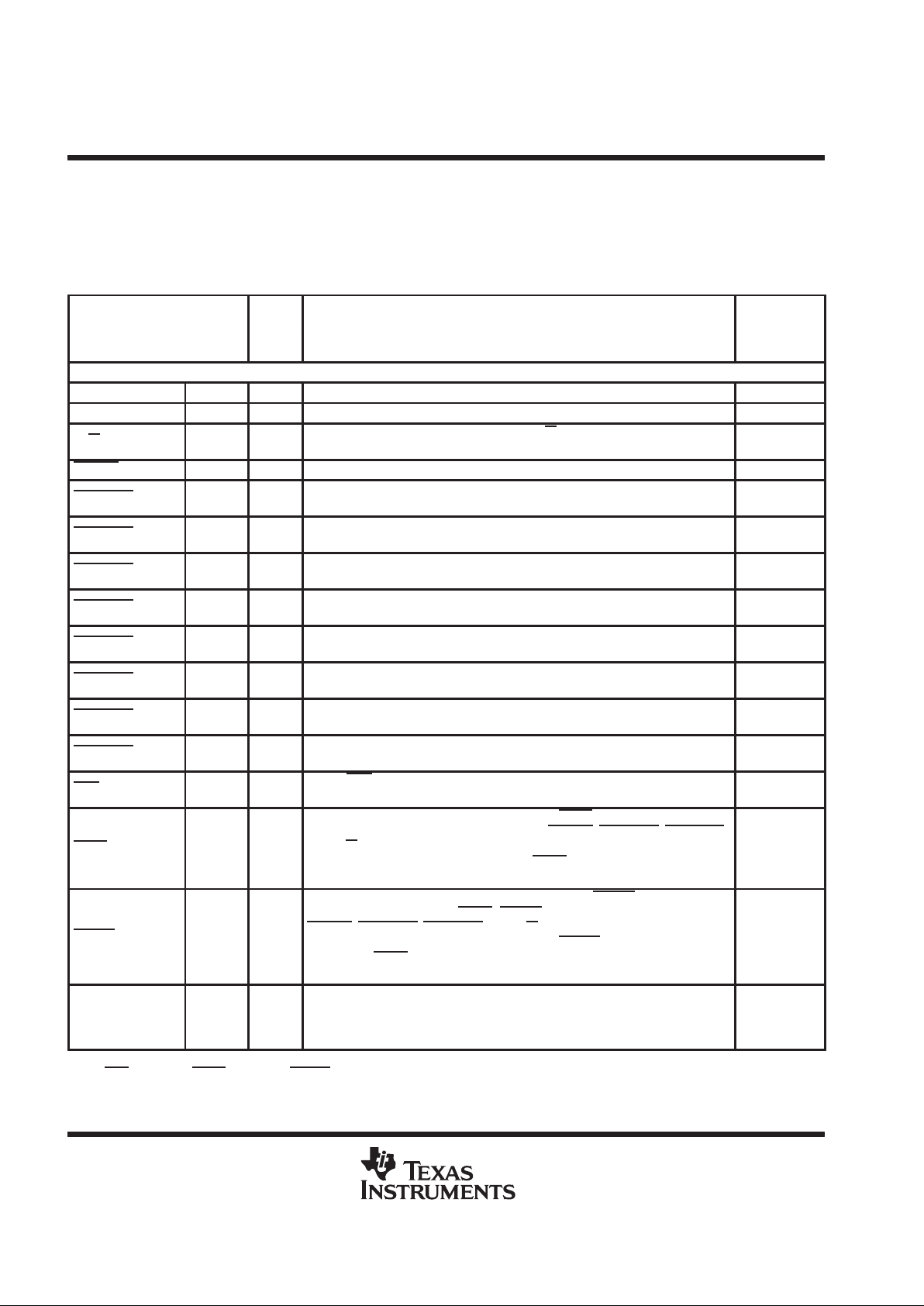

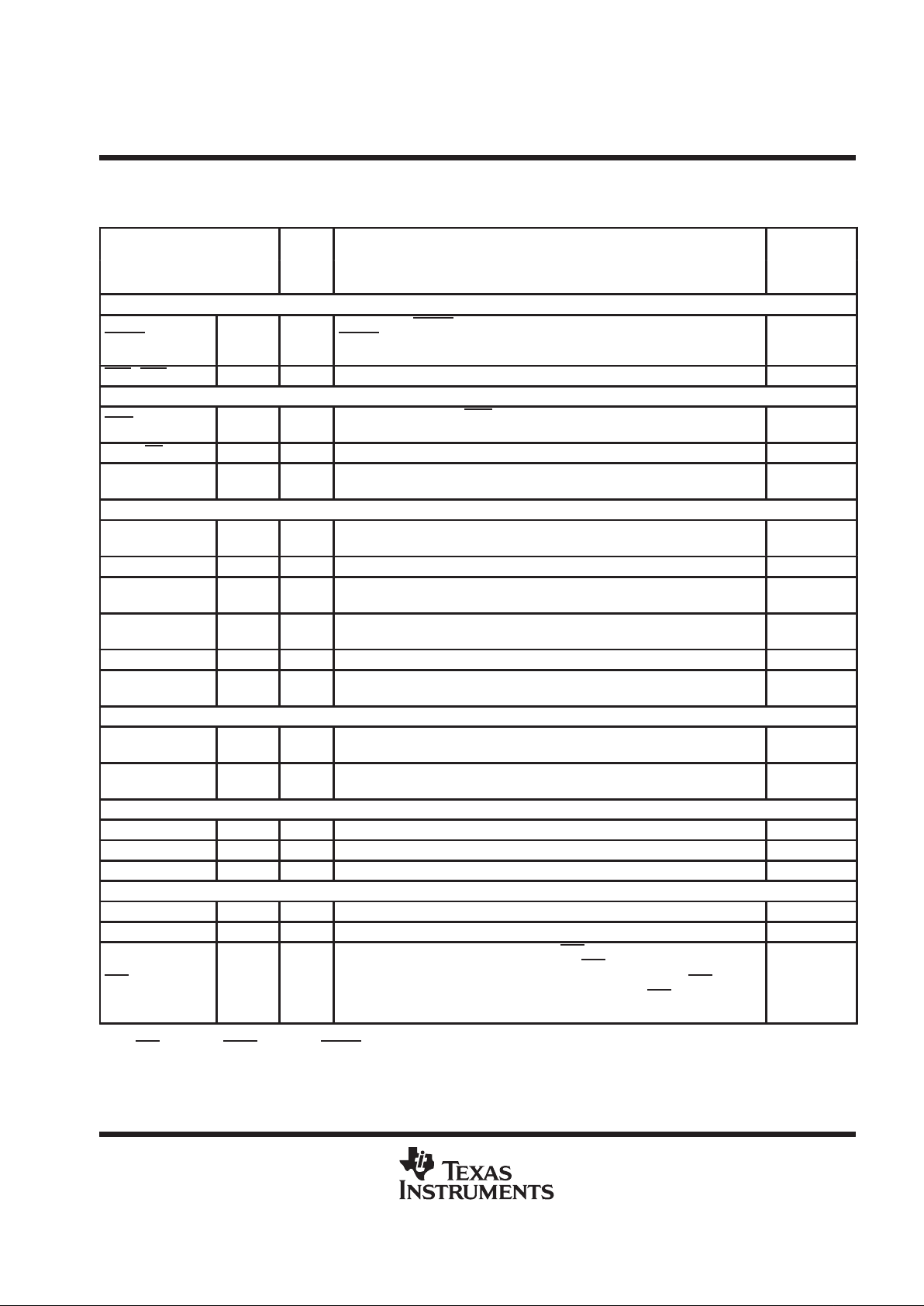

pin functions

This section provides signal descriptions for the SMQ320C32 device. The following table lists each signal

(grouped by function), the number of pins, operating modes, and a brief signal description.

Pin Functions

PIN

CONDITIONS

WHEN

NAME NO.

TYPE

†

DESCRIPTION

SIGNAL IS

IN HIGH Z

‡

EXTERNAL BUS INTERFACE (70 PINS)

D31–D0 32 I/O/Z 32-bit data port of the external bus interface S H R

A23–A0 24 O/Z 24-bit address port of the external bus interface S H R

R/W 1 O/Z

Read/write for external memory interface. R/W is high when a read is performed

and low when a write is performed over the parallel interface.

S H R

IOSTRB 1 O/Z External peripheral I/O strobe for the external memory interface S H

STRB0_B3/A

–1

1 O/Z

External memory-access strobe 0, byte enable 3 for 32-bit external memory

interface and address pin for 8-bit and 16-bit external memory interface

S H

STRB0_B2/A

–2

1 O/Z

External memory-access strobe 0, byte enable 2 for 32-bit external memory

interface and address pin for 8-bit external memory interface

S H

STRB0_B1 1 O/Z

External memory-access strobe 0, byte enable 1 for the external memory

interface

S H

STRB0_B0 1 O/Z

External memory-access strobe 0, byte enable 0 for the external memory

interface

S H

STRB1_B3/A

–1

1 O/Z

External memory-access strobe 1, byte enable 3 for 32-bit external memory

interface and address pin for 8-bit and 16-bit external memory interface

S H

STRB1_B2/A

–2

1 O/Z

External memory-access strobe 1, byte enable 2 for 32-bit external memory

interface and address pin for 8-bit external memory interface

S H

STRB1_B1 1 O/Z

External memory-access strobe 1, byte enable 1 for the external memory

interface

S H

STRB1_B0 1 O/Z

External memory-access strobe 1, byte enable 0 for the external memory

interface

S H

RDY 1 I

Ready. RDY indicates that the external device is prepared for an external memory

interface transaction to complete.

HOLD 1 I

Hold signal for external memory interface. When HOLD is a logic low, any ongoing

transaction is completed. A23–A0, D31–D0, IOSTRB

, STRB0_Bx, STRB1_Bx,

and R/W

are placed in the high-impedance state, and all transactions over the

external memory interface are held until HOLD

becomes a logic high or the

NOHOLD bit of the STRB0 bus-control register is set.

HOLDA 1 O/Z

Hold acknowledge for external memory interface. HOLDA is generated in

response to a logic low on HOLD

. HOLDA indicates that A23 – A0, D31 – D0,

IOSTRB

, STRB0_Bx, STRB1_Bx, and R/W are in the high-impedance state and

that all transactions over the memory are held. HOLDA

is high in response to a

logic high of HOLD

or when the NOHOLD bit of the external bus-control register

is set.

S

PRGW 1 I

Program memory width select. When PRGW is a logic low, program is fetched as

a single 32-bit word. When PRGW is a logic high, two 16-bit program fetches are

performed to fetch a single 32-bit instruction word. The status of PRGW at device

reset affects the reset value of the STRB0 and STRB1 bus-control register.

†

I = input, O = output, Z = high-impedance state

‡

S = SHZ

active, H = HOLD active, R = RESET active

§

Recommended decoupling capacitor is 0.1 µF.

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Pin Functions (Continued)

PIN

CONDITIONS

WHEN

SIGNAL IS

IN HIGH Z

‡

DESCRIPTIONTYPE

†

NAME

CONDITIONS

WHEN

SIGNAL IS

IN HIGH Z

‡

DESCRIPTIONTYPE

†

NO.

CONTROL SIGNALS (9 PINS)

RESET 1 I

Reset. When RESET is a logic low, the device is in the reset condition. When

RESET

becomes a logic high, execution begins from the location specified by the

reset vector.

INT3–INT0 4 I External interrupts

CONTROL SIGNALS (9 PINS) (CONTINUED)

IACK 1 O/Z

Interrupt acknowledge. IACK is set to a logic high by the IACK instruction. This

signal can be used to indicate the beginning or end of an interrupt-service routine.

S

MCBL/MP 1 I Microcomputer bootloader/microprocessor mode

XF1–XF0 2 I/O/Z

External flags. XF1 and XF0 are used as general-purpose I/Os or used to support

interlocked-processor instructions.

S R

SERIAL PORT SIGNALS (6 PINS)

CLKX0 1 I/O/Z

Serial port 0 transmit clock. CLKX0 is the serial shift clock for the serial port 0

transmitter.

S R

DX0 1 I/O/Z Data transmit output. Serial port 0 transmits serial data on DX0. S R

FSX0 1 I/O/Z

Frame-synchronization pulse for transmit. The FSX0 pulse initiates the

transmit-data process over DX0.

S R

CLKR0 1 I/O/Z

Serial port 0 receive clock. CLKR0 is the serial shift clock for the serial port 0

receiver.

S R

DR0 1 I/O/Z Data receive. Serial port 0 receives serial data on DR0. S R

FSR0 1 I/O/Z

Frame-synchronization pulse for receive. The FSR0 pulse initiates the

receive-data process over DR0.

S R

TIMER SIGNALS (2 PINS)

TCLK0 1 I/O/Z

Timer clock 0. As an input, TCLK0 is used by timer 0 to count external pulses. As

an output, TCLK0 outputs pulses generated by timer 0.

S R

TCLK1 1 I/O/Z

Timer clock 1. As an input, TCLK1 is used by timer 1 to count external pulses. As

an output, TCLK1 outputs pulses generated by timer 1.

S R

CLOCK SIGNALS (3 PINS)

CLKIN 1 I Input to the internal oscillator from an external clock source

H1 1 O/Z External H1 clock. H1 has a period equal to twice CLKIN. S

H3 1 O/Z External H3 clock. H3 has a period equal to twice CLKIN. S

RESERVED (5 PINS)

EMU0–EMU2 3 I Reserved for emulation. Use 18 kΩ–22 kΩ pullup resistors to 5 V.

EMU3 1 O/Z Reserved for emulation S

SHZ 1 I

Shutdown high impedance. When active, SHZ shuts down the ’C32 and places

all 3-state I/O pins in the high-impedance state. SHZ

is used for board-level testing

to ensure that no dual drive conditions occur. CAUTION: A low on SHZ

corrupts

’C32 memory and register contents. Reset the device with SHZ

high to restore it

to a known operating condition.

†

I = input, O = output, Z = high-impedance state

‡

S = SHZ

active, H = HOLD active, R = RESET active

§

Recommended decoupling capacitor is 0.1 µF.

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

6

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

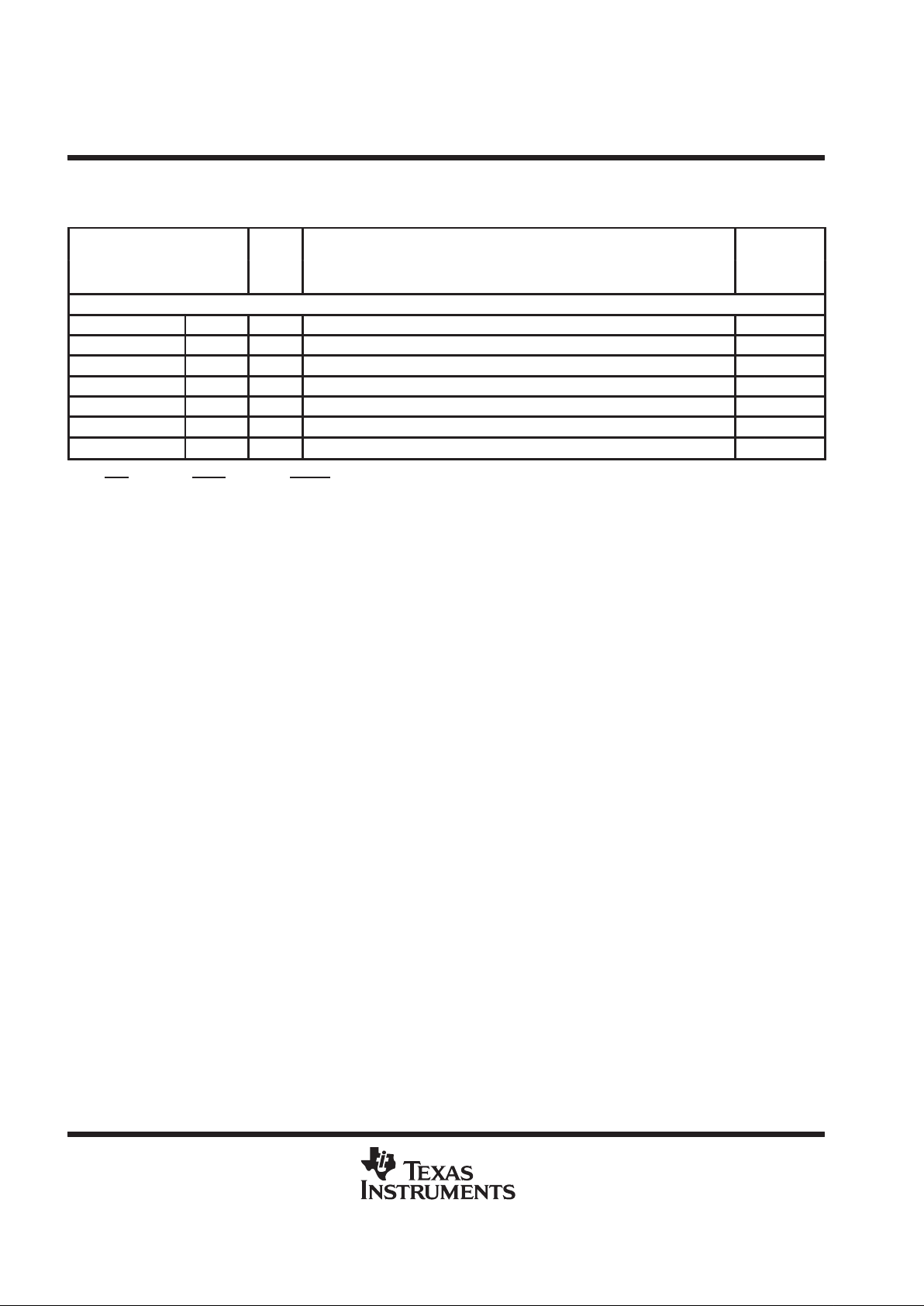

Pin Functions (Continued)

PIN

CONDITIONS

WHEN

SIGNAL IS

IN HIGH Z

‡

DESCRIPTIONTYPE

†

NAME

CONDITIONS

WHEN

SIGNAL IS

IN HIGH Z

‡

DESCRIPTIONTYPE

†

NO.

POWER/GROUND

CV

SS

7 I Ground

DV

SS

7 I Ground

IV

SS

4 I Ground

DV

DD

12 I 5 Vdc supply

§

V

DDL

8 I 5 Vdc supply

§

V

SSL

6 I Ground

V

SUBS

1 I Substrate, tie to ground

†

I = input, O = output, Z = high-impedance state

‡

S = SHZ

active, H = HOLD active, R = RESET active

§

Recommended decoupling capacitor is 0.1 µF.

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

7

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

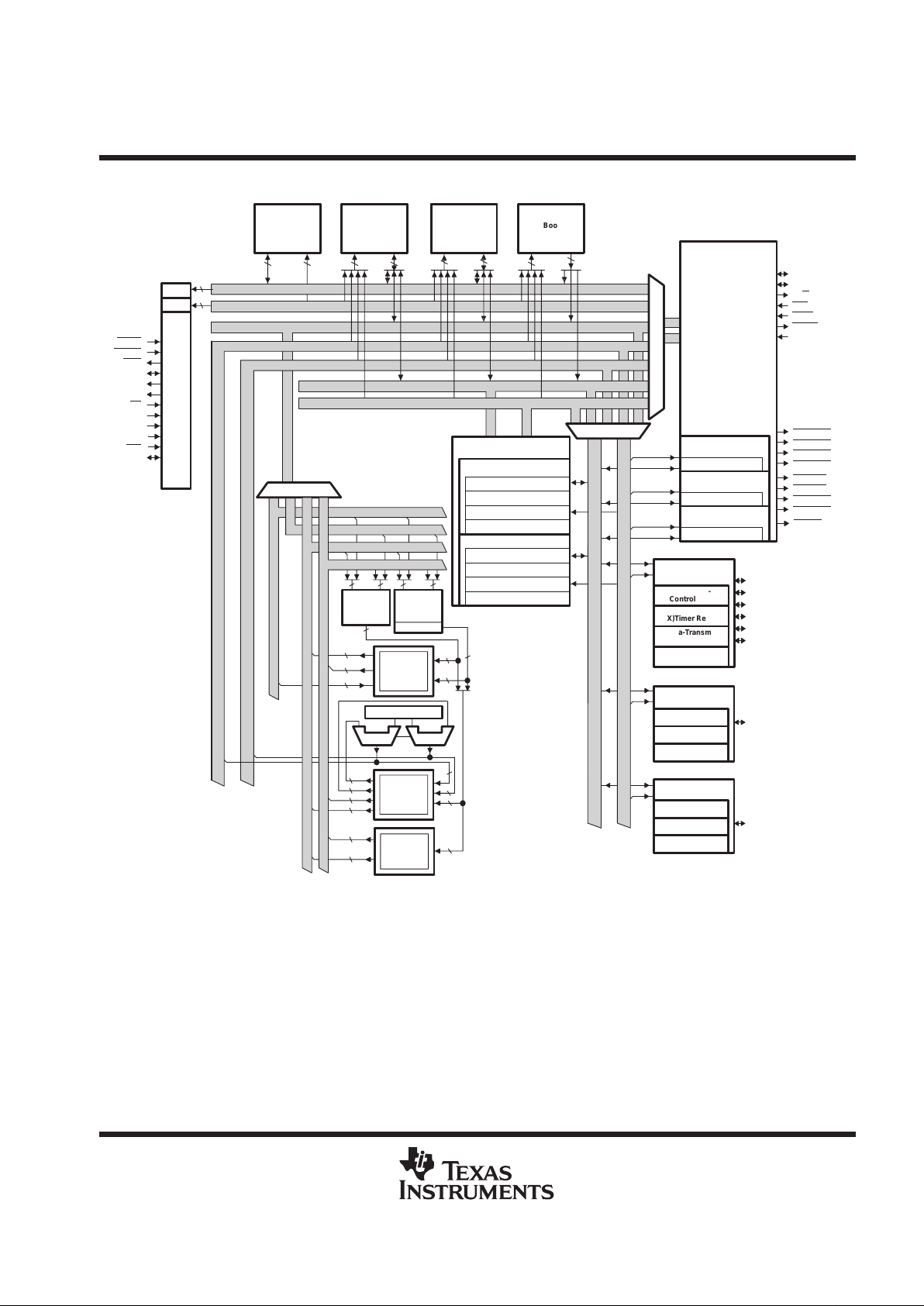

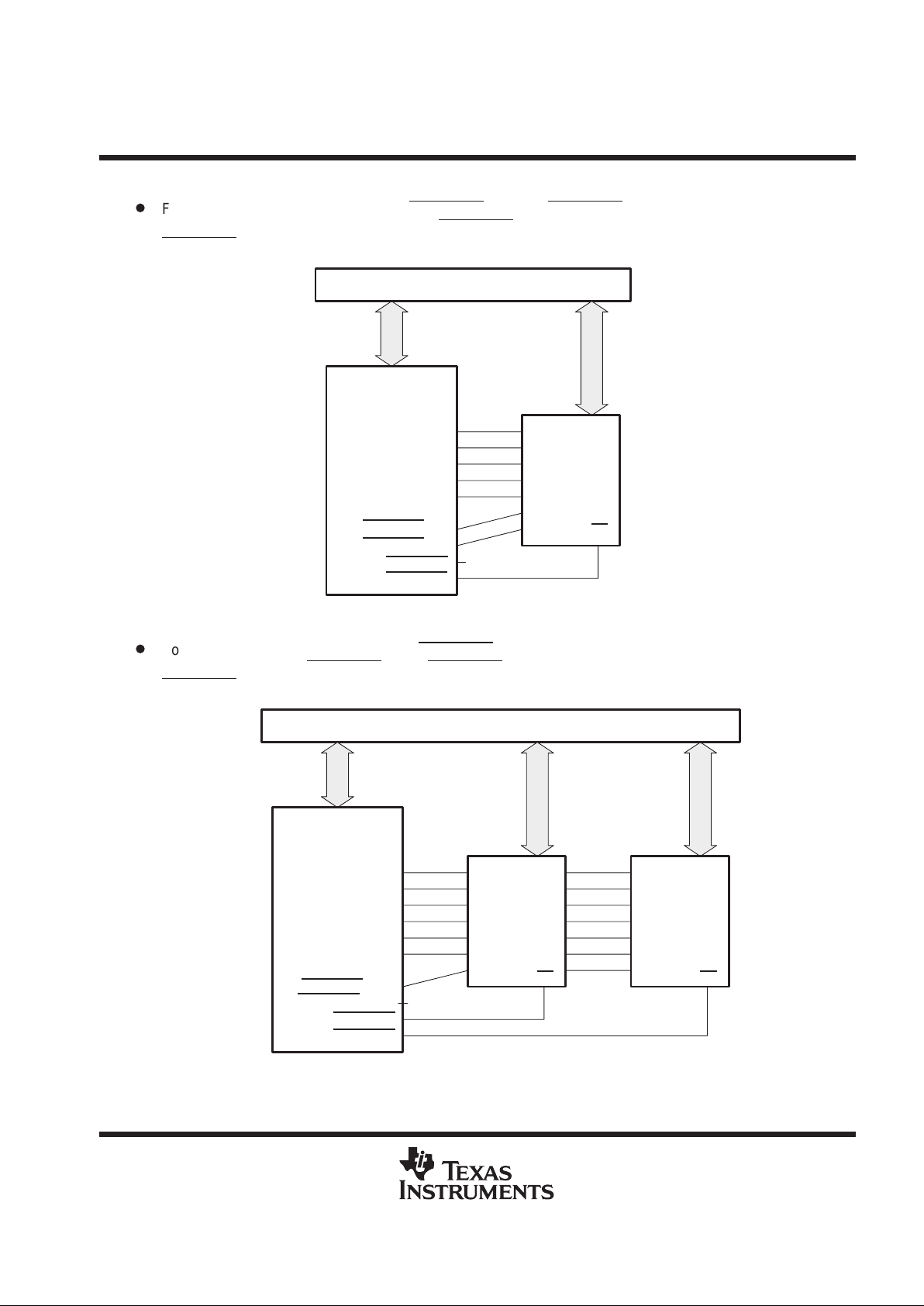

functional block diagram

Boot

ROM

Program

Cache

(64 × 32)

RAM

Block 0

(256 × 32)

RAM

Block 1

(256 × 32)

IR

PC

CPU1

REG1

REG2

Multiplexer

40

32

32

32

32

32

32

32

24

24

24

24

BK

ARAU0 ARAU1

DISP0, IR0, IR1

Extended-

Precision

Registers

(R0–R7)

Auxiliary

Registers

(AR0 – AR7)

Other

Registers

(12)

40

40

40

40

Multiplier

32-Bit

Barrel

Shifter

ALU

External

Memory

Interface

Serial Port

Data-Transmit

Register

Data-Receive

Register

FSX0

DX0

CLKX0

FSR0

DR0

CLKR0

Timer 0

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

TCLK0

Timer 1

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

TCLK1

PDATA Bus

PADDR Bus

DDATA Bus

DADDR1 Bus

DADDR2 Bus

DMADATA Bus

40

32 24

24

24 2432 32 32

CPU2

32 32 40 40

Serial Port-

Control Reg.

Receive/Transmit

(R/X)Timer Register

Controller

Peripheral Address Bus

CPU1

REG1

REG2

DMAADDR Bus

STRB0 Control Reg.

STRB1 Control Reg.

IOSTRB Control Reg.

STRB1

IOSTRB

STRB0

Peripheral Data Bus

RESET

INT(3-0)

IACK

XF(1,0)

H1

H3

MCBL / MP

CLKIN

V

DD

V

SS

SHZ

EMU0–3

32

24

Multiplexer

A23 – A0

D31 – D0

R/W

RDY

HOLD

HOLDA

PRGW

STRB0_B3/A

–1

STRB0_B2/A

–2

STRB0_B1

STRB0_B0

IOSTRB

Multiplexer

DMA Controller

Global-Contol Register

Source-AddressRegister

Destination-Address Reg.

Transfer-Counter Reg.

DMA Channel 0

Global-Control Register

Source-AddressRegister

Destination-Address Reg.

Transfer-Counter Reg.

DMA Channel 1

STRB1_B3/A

–1

STRB1_B2/A

–2

STRB1_B1

STRB1_B0

operation

Operation of the SMQ320C32 is identical to the ’320C30 and ’320C31 digital signal processors, with the

exception of an enhanced external memory interface and the addition of two CPU power-management modes.

external memory interface

The SMQ320C32 has a configurable external memory interface with a 24-bit address bus, a 32-bit data bus,

and three independent multi-function strobes. The flexibility of this unique interface enables product designers

to minimize external memory-chip count.

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

8

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

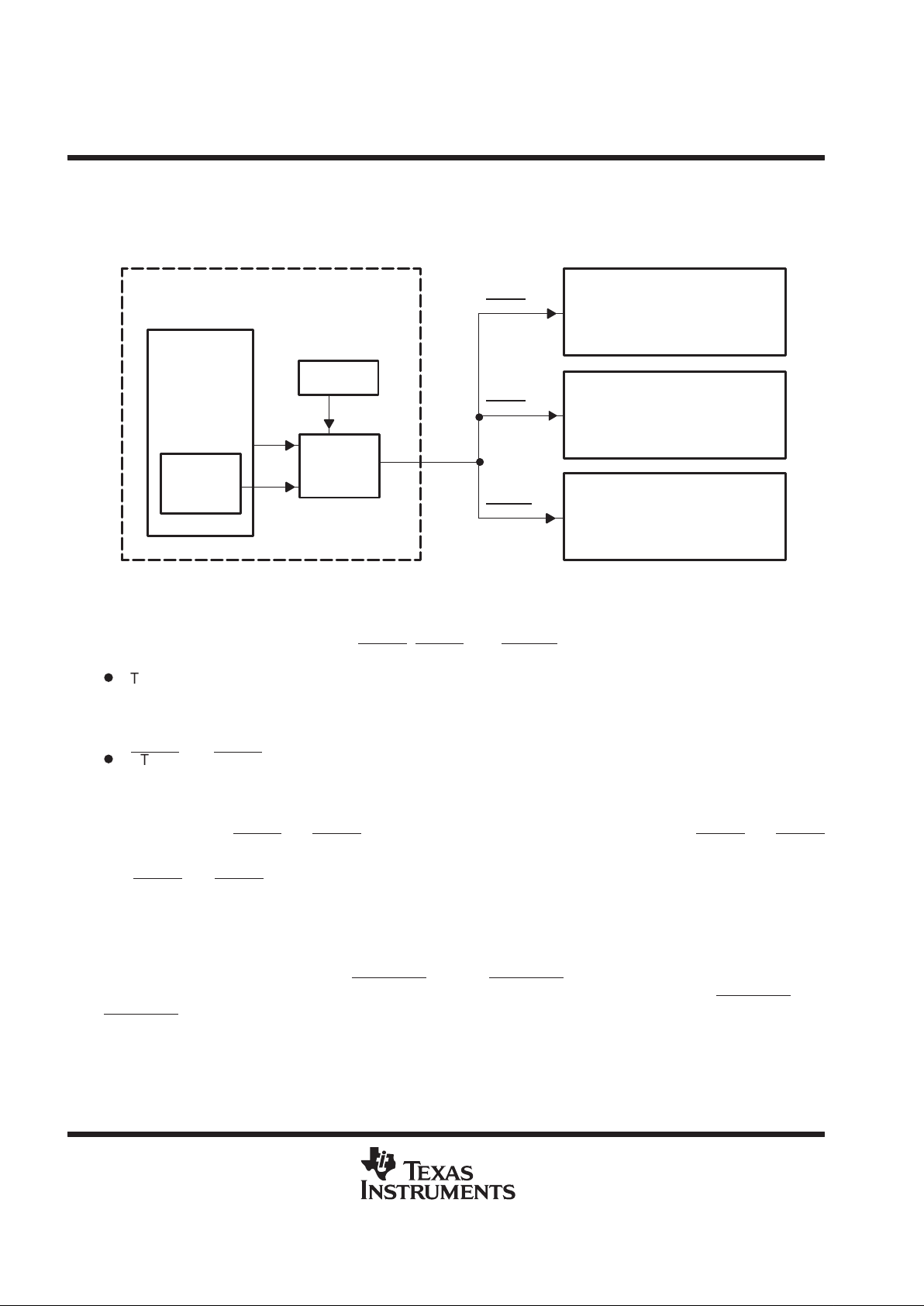

external memory interface (continued)

Up to three mutually exclusive memory areas—one program area and two data areas—can be implemented.

Each memory area configuration is independent of the physical memory width and independent of the other

memory areas configurations. See Figure 1.

’C32

StrobeControl

Registers

32-Bit

CPU

PRGW Pin

STRB0

STRB1

IOSTRB

Memory

Interface

8-/16-/32-Bit Data in

8-/16-/32-Bit-Wide Memory

32-Bit Program in 16-/32-Bit-

Wide Memory

8-/16-/32-Bit Data in

8-/16-/32-Bit-Wide Memory

32-Bit Data in 32-Bit-Wide

Memory

32-Bit Program in 16-/32-Bit-

Wide Memory

32-Bit Program in 32-Bit-

Wide Memory

Figure 1. ’C32 External Memory Interface

The SMQ320C32 external memory configuration is controlled by a combination of hardware configuration and

memory-mapped control registers and can be reconfigured dynamically. The signals that control external

memory configuration are the PRGW, STRB0, STRB1, and IOSTRB. The signals work as follows:

D

The SMQ320C32 is a 32-bit microprocessor, that is, the CPU operates on 32-bit program words. The

external memory interface provides the capability of fetching instructions as either 32-bit words or two 16-bit

half words from consecutive addresses. Program memory width is 16 bits if the PRGW signal is high,

32 bits if the PRGW signal is low.

D

STRB0 and STRB1 are sets of control signals, four signals each, that are mapped to specific ranges of

external memory addresses. When an address within one of these ranges is accessed by a read or write

instruction (CPU or DMA), the corresponding set of control signals is activated. Figure 8 illustrates the

SMQ320C32 memory map, showing the address ranges for which the strobe signals become active.

The behavior of the STRB0

and STRB1 control signals is determined by the contents of the STRB0 and STRB1

control registers.

The STRB0

and STRB1 control registers each have a field that specifies the physical memory width (8, 16, or

32 bits) of the external memory address ranges they control. Another field specifies the data width (8, 16, or

32 bits) of the data contained in those addresses. The values in these fields are not required to match. For

example, a 32-bit-wide physical memory space can be configured to segment each 32-bit word into four

consecutive 8-bit locations, each having its own address.

Each control signal set has two pins (STRBx_B2

/A–2 and STRBx_B3/A–1) that can act as either byte-enable

(chip-select) pins or address pins, and two dedicated byte-enable (chip-select) pins (STRBx_B0 and

STRBx_B1). The pins’ functions are determined by the physical memory width specified in the corresponding

control register:

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

9

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

external memory interface (continued)

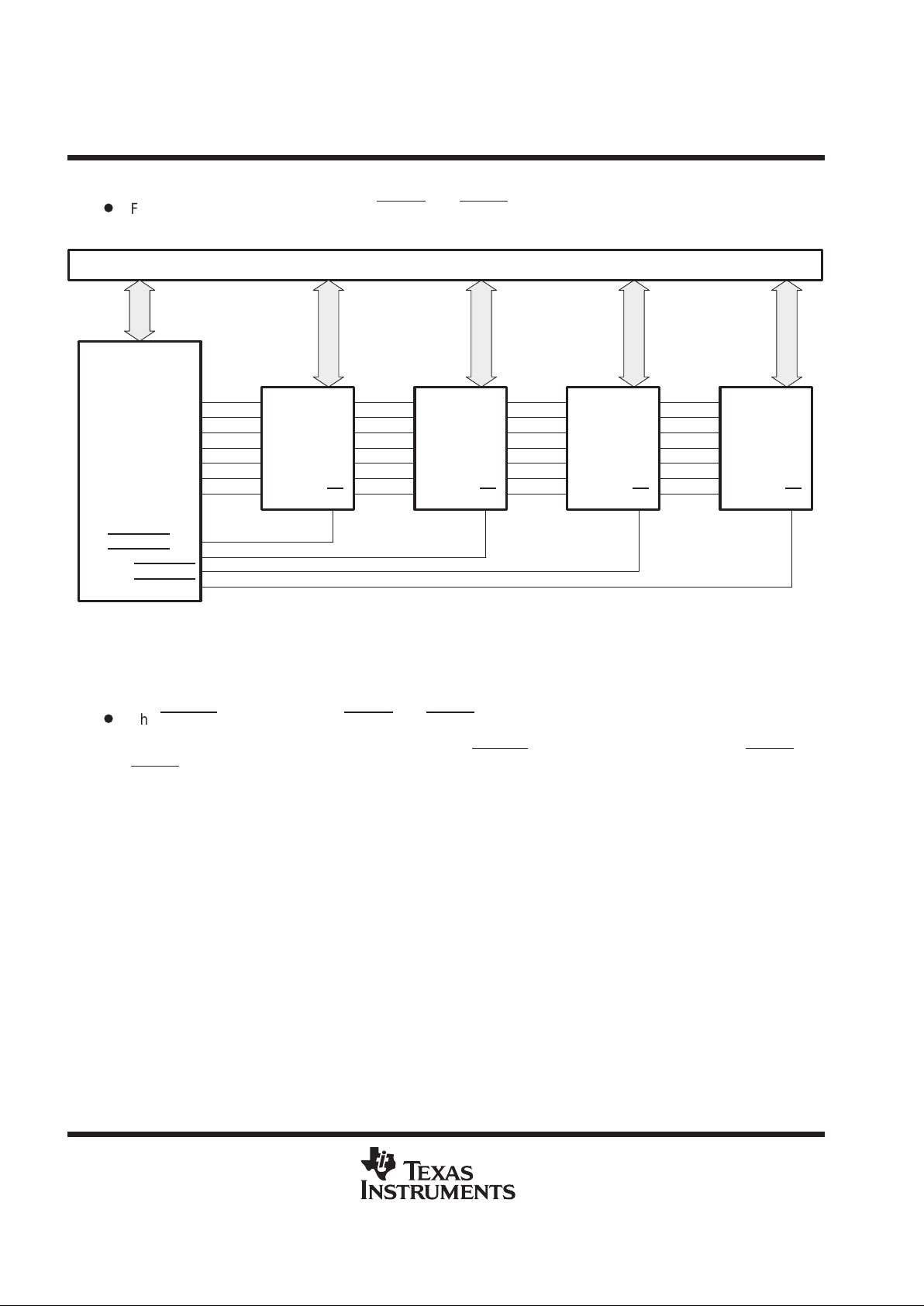

D

For 8-bit-wide physical memory, the STRBx_B2/A–2 and STRBx_B3/A–1 pins function as address pins

(least significant address bits) and the STRBx_B0 pin functions as a byte-enable (chip-select) pin.

STRBx_B1 is unused. See Figure 2.

8

8-Bit Data Bus

CS

Data

A0

A1

A2

A14

STRB0_B0

STRB0_B2/A

–2

STRB0_B3

/A

–1

A0

A1

.

A13

A14

Data

TMS320C32

Memory

8

A3

.

.

STRB0_B1

A12

.

NC

Figure 2. ’C32 With 8-Bit-Wide External Memory

D

For 16-bit-wide physical memory, the STRBx_B3/A–1 pin functions as an address pin (least significant

address bits). The STRBx_B0 and STRBx_B1 pins function as byte-enable (chip-select) pins.

STRBx_B2/A

–2

is unused. See Figure 3.

CS

Data

A2

.

A14

A0

A1

16-Bit Data Bus

CS

Data

A0

A1

A2

.

A14

STRB0_B0

STRB0_B1

STRB0_B3/A

–1

A0

A1

A2

A13

A14

Data

TMS320C32

Memory

Memory

16

8

8

..

.

A3A3

.

STRB0_B2/A

–2

NC

Figure 3. ’C32 With 16-Bit-Wide External Memory

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

10

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

external memory interface (continued)

D

For 32-bit-wide physical memory, all STRB0 and STRB1 pins function as byte-enable (chip-select) pins.

See Figure 4.

STRB0_B2/A

–2

CS

A14

A13

A2

A1

A0

Data

CS

Data

A14

A13

A2

A1

A0

STRB0_B3/A

–1

CS

Data

A2

A13

A14

A0

A1

32-Bit Data Bus

CS

Data

A0

A1

A2

A13

A14

STRB0_B0

STRB0_B1

A0

A1

A2

A13

A14

Data

TMS320C32

.

.

.

.

.

.

.

.

.

.

Memory

Memory

Memory

Memory

8888

32

Figure 4. ’C32 With 32-Bit-Wide External Memory

For more detailed information and examples, see

TMS320C32 Addendum to the TMS320C3x User’s Guide

(literature number SPRU132B) and

Interfacing Memory to the SMQ320C32 DSP Application Report

(literature

number SPRA040).

D

The IOSTRB control signal, like STRB0 and STRB1, is also mapped to a specific range of addresses but

it is a single signal that can access only 32-bit data from 32-bit-wide memory . Its range of addresses appears

in Figure 8, the SMQ320C32’s memory map. The IOSTRB

bus timing is different from the STRB0 and

STRB1 bus timings to accommodate slower I/O peripherals.

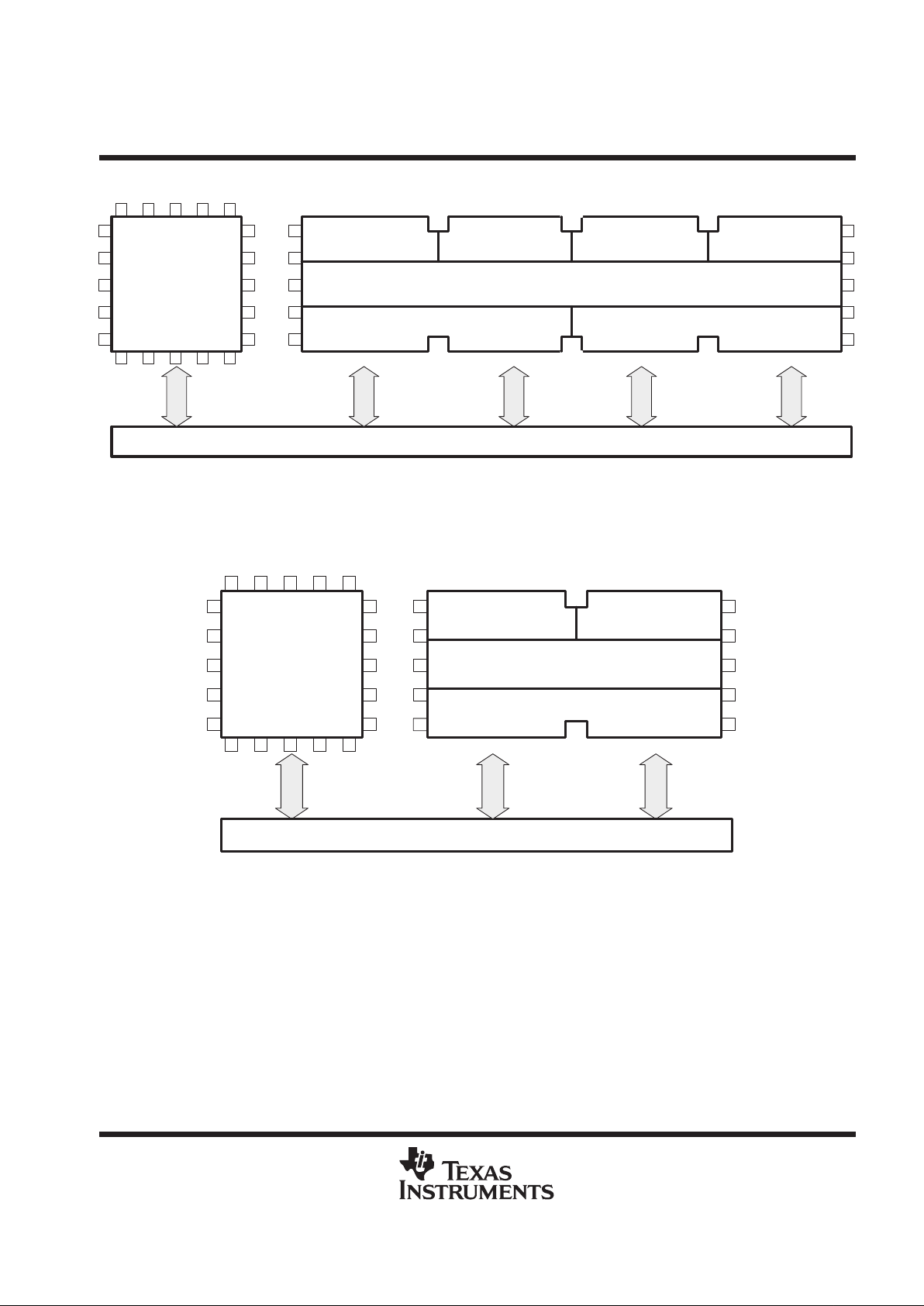

examples

Figure 5 and Figure 6 show examples of external memory configurations that can be implemented using the

SMQ320C32’s external memory interface. The first example has a 32-bit-wide external memory with 8- and

16-bit data areas and a 32-bit program area.

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

11

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

examples (continued)

32-Bit-Wide Memory

8-Bit Data 8-Bit Data8-Bit Data

16-Bit Data16-Bit Data

8-Bit Data

32-Bit Program

320C32

32-Bit-Wide Data Bus

88

8

8

32

Figure 5. ’C32 With 32-Bit-Wide External Memory Configured With 8- and 16-Bit Data Areas and 32-Bit

Program Memory

Figure 6 shows a configuration that can be implemented with a 16-bit external memory. Note that 32-bit data

and program words can be stored and retrieved as half words.

16-Bit-Wide Memory

8-Bit Data

16-Bit Data

8-Bit Data

32-Bit Program

320C32

16

16-Bit-Wide Data Bus

88

Figure 6. ’C32 With 16-Bit-Wide External Memory Configured With 8- and 16-Bit Data Areas and a 32-Bit

Program Area

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

12

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

examples (continued)

Figure 7 shows one possible configuration that can be implemented with 8-bit external memory. Program words,

which are 32-bit, cannot be executed from 8-bit-wide memory.

8-Bit-Wide Memory

16-Bit Data

8-Bit Data

320C32

8-Bit-Wide Data Bus

8 8

Figure 7. ’C32 With 8-Bit-Wide External Memory Configured With 8- and 16-Bit Data Areas

SMQ320C32

DIGITAL SIGNAL PROCESSOR

SGUS027B – APRIL 1998 – REVISED MARCH 1999

13

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

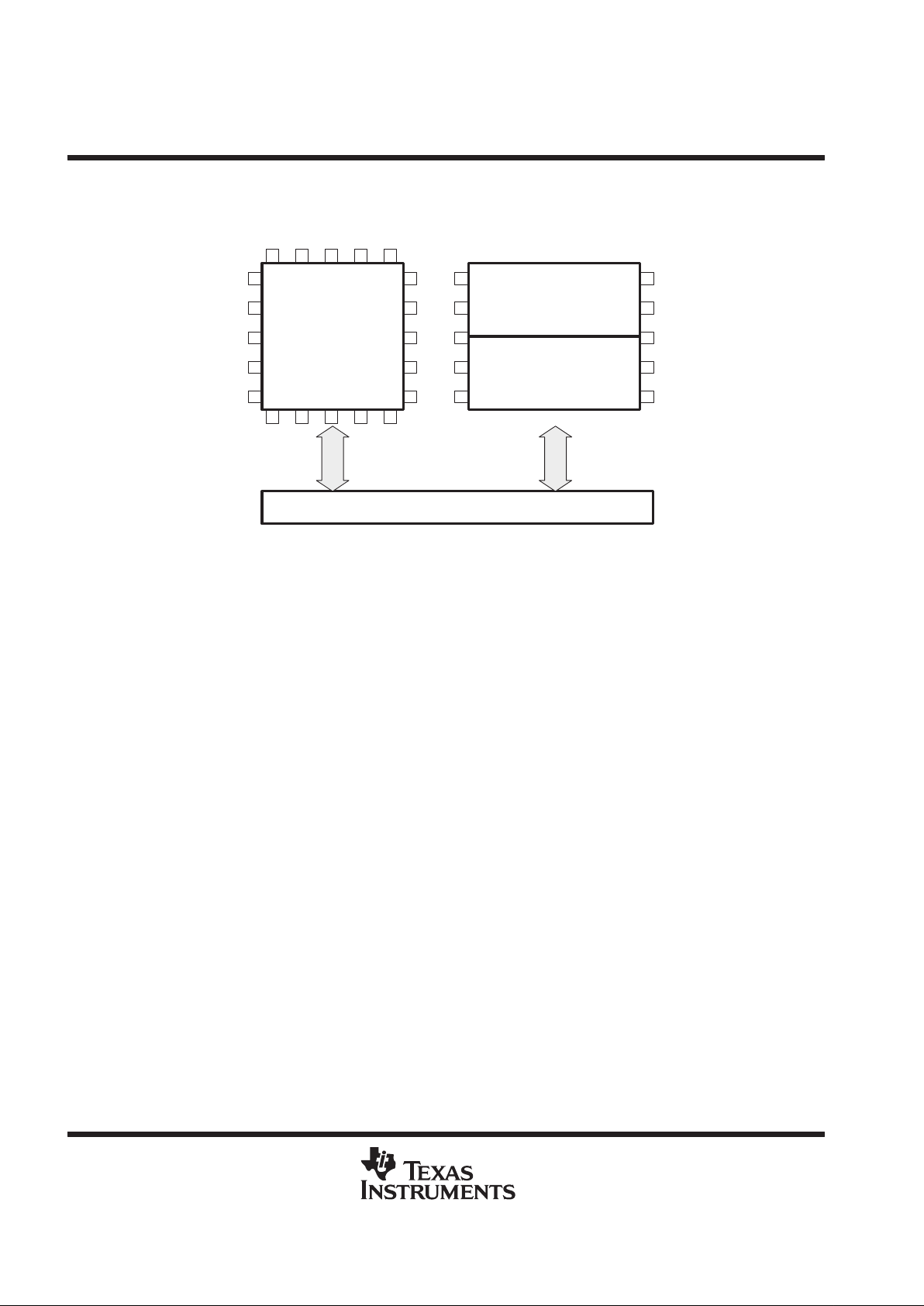

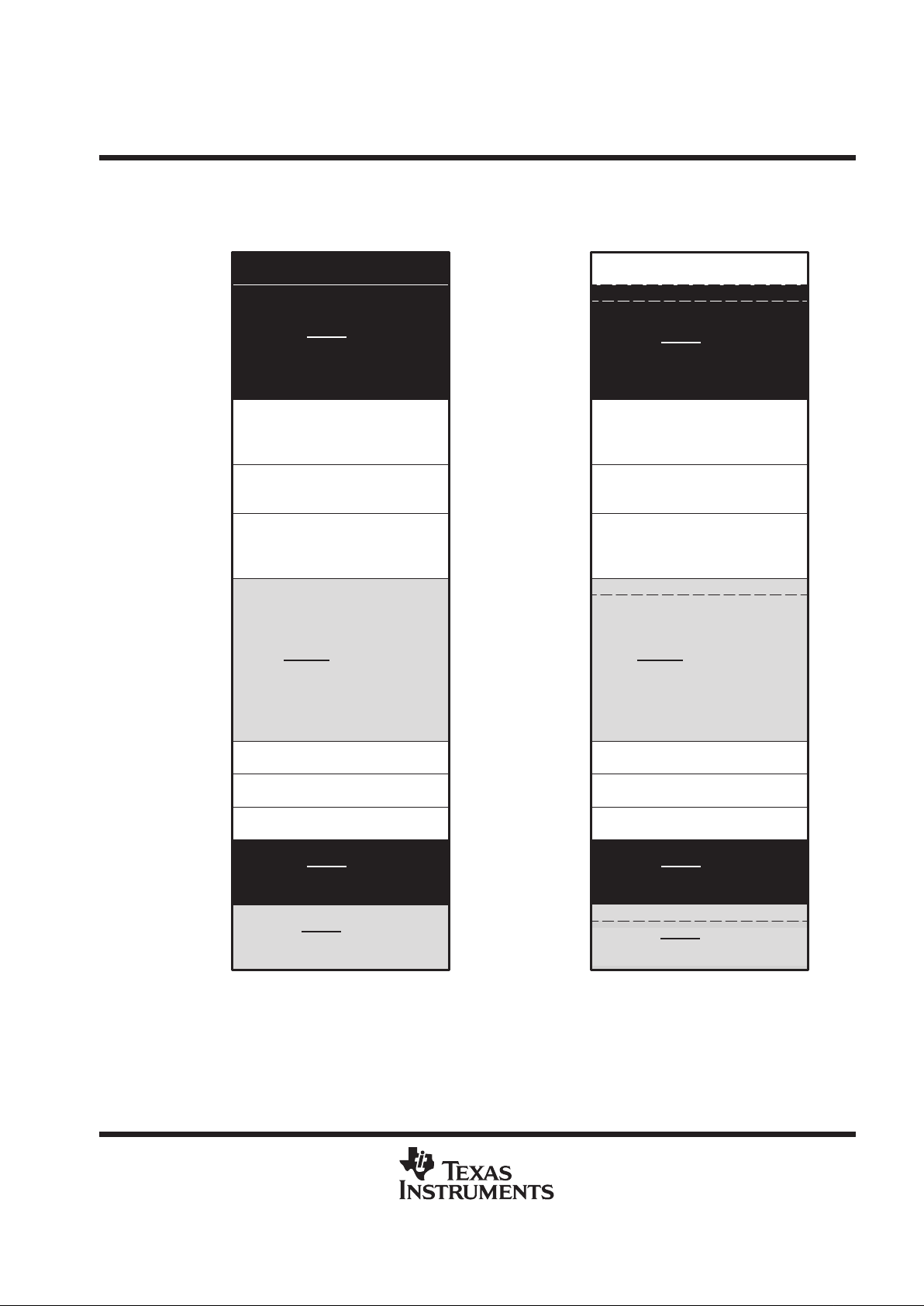

memory map

Figure 8 depicts the memory map for the SMQ320C32. See the

TMS320C32 Addendum to the TMS320C3x

User’s Guide

(literature number SPRU132B) for a detailed description of this memory mapping.

Boot 3

External Memory

STRB1

Active

(7.168M Words)

Microprocessor Mode Microcomputer/Boot-LoaderMode

900001h

Boot 2

810001h

Boot 1

1001h

1000h

FFFh

Boot-Loader Operations

Reserved for

External Memory

STRB0

Active

(8.188M Words)

Reserved

(32K Words)

Reserved

(26K Words)

Peripheral-Bus

Memory-Mapped Registers

(6K-Word Internal)

0h

7FFFFFh

800000h

807FFFh

808000h

809800h

80FFFFh

810000h

8097FFh

Reserved

(319.5K Words)

Internal Memory

RAM Block 0 (256-Word Internal)

Internal Memory

External Memory

IOSTRB

Active (128K)

(128K Words)

RAM Block 1 (256-Word Internal)

External Memory

STRB1

Active

(7.168M Words)

External Memory

STRB0

Active

(512K Words)

82FFFFh

830000h

87FDFFh

87FE00h

87FEFFh

87FFFFh

880000h

900000h

8FFFFFh

87FF00h

FFFFFFh

87FEFFh

RAM Block 1

(256-Word Internal)

RAM Block 0

(256-Word Internal)

Reserved

(314.5K Words)

External Memory

IOSTRB

Active (128K)

(128K Words)

Reserved

(26K Words)

(6K-Word Internal)

Memory-Mapped Registers

Peripheral-Bus

Reserved

(32K Words)

FFFFFFh

900000h

8FFFFFh

880000h

87FFFFh

87FF00h

87FE00h

87FDFFh

830000h

82FFFFh

810000h

80FFFFh

809800h

8097FFh

808000h

807FFFh

800000h

7FFFFFh

0h

External Memory

STRB0

Active

(8.192M Words)

Reset-Vector Location

External Memory

STRB0

Active

(512K Words)

Figure 8. SMQ320C32 Memory Map

Loading...

Loading...