73M1866B/73M1966B

MicroDAA™ with PCM Highway

Simplifying System Integration™

DS_1x66B_001 April 2010

DESCRIPTION

The 73M1866B and 73M1966B use the Teridian

patented D ata Access Arrangement function

(MicroDAA

Exchange-Office (FXO) in Voice-over-IP (VoIP)

applications. These devices provide much of the

circuitry required to c onnect PCM formatted

voice c hannels to a PSTN via a two-wire twisted

pair i nterface. The package opti ons provide the

necessary functional progr am mability and

prot ection required for easy wo r ldwide

homologation.

The family of devices consists of the 73M1866B

and the 73M1966B. The 73M1866B MicroDAA

is the world’s first sing le-p ackage si l icon Dat a

Access Arrangement (DAA). Suitable

applications for the 73M1866B and 73M1966B

devices include VoI P equipment that m ust

provid e connec tivity to the P STN for purposes of

gu ar anteein g emergency service calling,

redundancy for s upplementary connectivity for

voice, and mai ntenance services .

The 73M1966B device set c onsists of the

73M1906B Host-Side Devic e that provides digital

data, cont r ol interfac es and power to the

73M1916 Line-Sid e Device.

These d evices are based on an innovative and

patented technology, which sets new standards

in reliability and cost. A small pulse trans former

forms a digital isolation barri er , transferrin g both

power and data to the PS TN line-side

components. This method r esults in reliable

operat ion in the presence of EMI and a toler ance

to line voltage variations by providing power to

the Line-Side Device across the barr i er . The

devices also support the ability to provide up to

an additional +6 dB of analog gain to the linesid e transmit and +3 dB i n the receive s i gnal

paths. The devic e supports t r ansmit and r eceive

digital g ai n ranging from –18 dB to +7.375 dB by

increments of 0.125 dB.

The digital side provides a PCM highway

interface with automatic clock rate detecti on.

With an 8-kHz sampling rate, the devices inc l ude

an ITU-T G .711 compliant codec with selectable

µ-law and A-law companding modes. The

devices also provide a 16-bit linear mode, which

is suitable for interfacing with wide band codecs,

as well as 16 kHz sampl i ng rate. D evice contr ol

is p er formed over an SPI interface. The SPI

supports daisy chain operation.

Rev. 1.6 © 20 10 Teridian Semiconductor C or poration 1

®

) designed exclusively for Foreign-

Through its PCM interface, the 73M1966B can

be connect ed to other PCM enabled devices

such as POTS codecs, ISDN codecs, E1/T1

framers , etc.

Add i tional DAA func tions sup ported by t he

73M1x66B devices include a call progress

monitor, Caller ID Type I and II, ring detection,

pulse dialing, billing tone detection and polarity

reversal detection.

APPLICATIONS

• Computer Telephony

• VOIP Equipment

• PBX Systems

• Internet Appliances

• Voicemail Systems

• POTS Terminat i on Equipment

FEATURES

• PCM highway data i nterface supporting both

slave and master modes

• PCM highway interface supporting both E-1

and T-1

• SPI control i nterface, with daisy chain

support for up to 16 devices

• Designed to meet global DAA com plianc e

FCC, ETSI ES 203 021-2, JATE and other

PTT standards.

• 8 kH z and 16 kHz sample rat es

• 16-bit linear mod e

• TX and RX gains adjustable in 0.125 dB

increments

• μ-Law , A-law ITU-T Recomm endatio n G.7 11

compliant compander operation

• Au tomatic c lock rate detecti on

• Low power modes

• Polarity Reversal detection

• GPIO for user-configurable I/O ports

• Call P r ogress Monitor

• Isolation u p to 6 kV

• THD -80 dB

• 5 V tolerant I/O on selected pins

• 3.0 V – 3.6 V operating voltage

• Industrial temperature range (-40 °C to +85 °C)

• 5x5 mm 32-p in QFN or 20-pin TSSOP

packages

• RoHS compliant (6/6 ) lead-free p ackage

DATA SHE ET

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

Table of Contents

1 Introduction ................................................................................................................................... 6

2 Pinout ............................................................................................................................................. 8

2.1 73M1906B 20-Pin TSSOP Pinout ............................................................................................ 8

2.2 73M 19 16 2 0-Pin TSSOP Pinout .............................................................................................. 9

2.3 73M1906B 32-Pin QFN Pinout .............................................................................................. 10

2.4 73M1916 32-Pin QFN Pinout ................................................................................................ 12

2.5 73M1866B Pinout ................................................................................................................. 14

2.6 Requisite Use of Exposed Bottom Pad on 73M1866B and 73M196 6B QFN Packages .......... 15

3 Electrical Characteristics and Specifications............................................................................. 16

3.1 Isolation Bar r ier Char acteristics ............................................................................................. 16

3.2 Electrical Specifications......................................................................................................... 16

3.2.1 Ab solute Maximum Ratings ....................................................................................... 16

3.2.2 Recommended Operating Conditions ........................................................................ 16

3.2.3 DC Characteristics..................................................................................................... 17

3.3 Interface Timing Specification................................................................................................ 18

3.3.1 SPI Interface ............................................................................................................. 18

3.3.2 PCM Highway In terface ............................................................................................. 19

3.4 An al og Specifications ............................................................................................................ 20

3.4.1 DC Specifications ...................................................................................................... 20

3.4.2 Call P r ogress Monitor ................................................................................................ 21

3.5 73M1x66B Line-Side Electrical Specifications ( 73M1916) ...................................................... 22

3.6 Reference and Regulation ..................................................................................................... 23

3.7 DC Transfer Characteristics .................................................................................................. 23

3.8 Transmit Path ....................................................................................................................... 24

3.9 Receive Path ........................................................................................................................ 25

3.10 Transmit Hybrid Cancellation ................................................................................................ 26

3.11 Receive Notch Filter .............................................................................................................. 26

3.12 Detectors .............................................................................................................................. 27

3.12.1 Over-Voltage Detector ............................................................................................... 27

3.12.2 Over-Current Detec tor ............................................................................................... 27

3.12.3 Under-Voltage Detect or ............................................................................................. 27

3.12.4 Over-Load D etector ................................................................................................... 27

4 Applications Information ............................................................................................................. 28

4.1 Example Schematic of the 73M1966B and 73M1866B .......................................................... 28

4.2 Bill of Materials...................................................................................................................... 30

4.3 Over-Voltage and EMI Protection .......................................................................................... 31

4.4 Isolation Bar r ier Pulse Transformer ....................................................................................... 32

5 SPI Interface ................................................................................................................................. 33

6 Control and Status Registers ...................................................................................................... 37

7 Hardware Control Functions ....................................................................................................... 41

7.1 Device Revision .................................................................................................................... 41

7.2 Interrupt C ontrol .................................................................................................................... 41

7.3 Power Managem ent .............................................................................................................. 42

7.4 Device Clock Man agemen t.................................................................................................... 42

7.5 GPIO Registers ..................................................................................................................... 43

7.6 Call P r ogress Monitor ............................................................................................................ 44

7.7 16 kHz Operation of Call Progress M onitor ............................................................................ 44

7.8 Device Reset ........................................................................................................................ 44

8 PCM Highway Interface and Signal Processing ......................................................................... 45

8.1 PCM Highway Interface Timing ............................................................................................. 45

8.2 PCM Clock Freq uencies ........................................................................................................ 47

8.3 Master M ode ......................................................................................................................... 47

8.4 A-law / μ-law Compander ...................................................................................................... 47

2 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

8.5 Transmit and Receive Levels ................................................................................................ 48

8.5.1 A-Law........................................................................................................................ 48

8.5.2 μ-Law ........................................................................................................................ 48

8.5.3 Transmit and Receive Level Control .......................................................................... 48

8.6 Transmit Path Signal Processing ........................................................................................... 49

8.6.1 Gener al Description ................................................................................................... 49

8.6.2 Total T r ansmi t Path Respons e................................................................................... 49

8.6.3 73M1x66B Transmit Spectrum................................................................................... 50

8.7 Receive Path Signal Processing ............................................................................................ 50

8.7.1 Gener al Description ................................................................................................... 50

8.7.2 Total R eceive Path Res ponse.................................................................................... 51

8.7.3 Receiver DC Offset Subtract ion ................................................................................. 51

8.8 PCM Control Functions ......................................................................................................... 52

8.8.1 Transmit and Receive Level Control .......................................................................... 57

8.8.2 Time S l ot Assi gnment Example ................................................................................. 59

9 Barrier Information ...................................................................................................................... 60

9.1 Isolation Bar r ier ..................................................................................................................... 60

9.2 Barrier Powered Opt i ons ....................................................................................................... 60

9.2.1 Barrier Powered Operation ........................................................................................ 60

9.2.2 Line Powered Operation ............................................................................................ 60

9.3 Sync hroniz ation of the Barrier ............................................................................................... 60

9.4 Auto-Poll ............................................................................................................................... 61

9.5 Barrier Cont r ol Func tions ...................................................................................................... 61

9.6 Line-Si de Device Operatin g Modes ....................................................................................... 63

9.7 Fail-Safe Operation of Line-Side Device ................................................................................ 63

10 Configurable Direct Access Arrangement (DAA) ....................................................................... 64

10.1 P ulse Dialing ......................................................................................................................... 64

10.2 DC Termination ..................................................................................................................... 64

10.3 AC Termination ..................................................................................................................... 66

10.4 B illing Tone Rejection ........................................................................................................... 67

10.5 Trans-Hybrid Cancellati on ..................................................................................................... 68

10.6 Direct Access A r r angement Control Functi ons ....................................................................... 68

10.7 International Regist er Settings Table for DC and AC Terminat i ons ........................................ 72

11 Line Sensing and Status ............................................................................................................. 73

11.1 A uxiliary A/D Converter ......................................................................................................... 73

11.2 Ring Detection ...................................................................................................................... 73

11.3 Line In U se Detect ion (LIU) ................................................................................................... 73

11.4 P arallel Pick Up (PPU) .......................................................................................................... 73

11.5 Polarity Reversal D etection ................................................................................................... 73

11.6 Off-hook Detection of Caller ID Type II .................................................................................. 73

11.7 Voltage and Current Detection .............................................................................................. 74

11.8 Under V oltage Detection ( UVD) ............................................................................................. 74

11.9 Over Voltage Detection (OVD) .............................................................................................. 74

11.10 AC Signal Overload Detection ............................................................................................. 74

11.11 Over Current Detection (OID) .............................................................................................. 74

11.12 Line Sensing Control Func tions........................................................................................... 75

12 Loopback and Testing Mod es ..................................................................................................... 78

13 Performance ................................................................................................................................ 80

13.1 Transmit................................................................................................................................ 80

13.2 Receive................................................................................................................................. 82

14 Package Layout ........................................................................................................................... 85

15 Order i ng Information ................................................................................................................... 87

16 Contact Information ..................................................................................................................... 87

Revision Hi st ory .................................................................................................................................. 88

Rev. 1.6 3

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

Figures

Figure 1: Simple 73M1x66B Reference Block Diagram ............................................................................ 6

Figure 2: 73M1906B 20-Pin TSSOP Pinout

Figure 3: 73M1916 20-Pi n T SS OP Pi no u t

Figure 4: 73M1906B 32-Pin QFN Pinout

Figure 5: 73M1916 32-Pin QFN Pi no ut

Figure 6: 73M1866B 42-Pin Pin out

Figure 7: SPI Timing Diag ram

Figure 8: PCM Timing Diagram for P ositive Edge Tran smit M ode and Neg ative Edge R eceive Mode

Figure 9: PCM Timing Diagram for Negative E dge Transmit M ode and Positive Edge Receive Mode

Figure 10: Frequenc y Respons e of the Call Progress M onitor Fi l ter

Figure 11: D em o Board Cir cuit Connecting AOUT to a S peaker

Figure 12: R ecommend ed Circuit for the 73M1966B

Figure 13: R ecommend ed Circuit for the 73M1866B

Figure 14: Suggest ed Over-Voltage Protection an d EMI Suppression Circu i t

Figure 15: D aisy-Chain Configuration

Figure 16: SPI Write Operation – 8-bit Mode

Figure 17: SPI Read Transaction – 8-bit Mode

Figure 18: SPI Write Transaction – 16-bit Mode

Figure 19: SPI Read Transaction – 16-bit Mode

Figur e 20: 8-bit Transmission Example

Figur e 21: 16-bit Tr ansmission Example

Figure 22: Example of PCM H ighway In terconnect

Figure 23: Example of PCM Highway Intercon nect for Typical Large Systems

Figure 24: M apping of A-law Code to 16-bit Code

Figure 25: Mapping of μ-law Code to 16-bit Code

Figure 26: Transmit Path Overall F requency Response to Fs of 8 kHz ................................................... 49

Figure 27: Transmit Path Passband Response for an 8 kHz Sample Rate

Figure 28: Transmit Spectrum to 32 kHz for an 8 kHz Sam ple Rate

Figure 29: Overall Frequency Response of t he Receive Path

Figure 30: Pass-band Response of t he Overall Receive P ath

Figure 31: Timing Relation s hips with Various TTS, TCS, TPOL, and RTS, RCS, RPOL Settings

Figur e 32: Li ne -Side Device AC and DC Circuit s

Figure 33: DC-IV Char acterist ics

Figure 34: Tip-Ring Voltage versus C urrent Using Different D CIV Settings

Figure 35: Voltage versu s Current in the Seize Mode is the Same for All DCIV Set tings

Figure 36: M agnitud e R espons e of Impedance Matc hing Filt er , ACZ (3:0)=001 0 (ES 203 021-2)

Figure 37: M agnitud e R espons e of Billin g Tone Notc h Filter

Figure 38: Trans-hybrid Cancellation

Figure 39: Loopback M odes Highlighted

Figure 40: Vari ation of Transmit Gain Digital Input to Analog Output at the Line

Figure 41: Gain versus Frequency for Digital Input to Analog Output at the Line

Figure 42: Signal to Total Distortion versus Input Level for Digital Input to Analog Output to the Line

Figure 43: Vari ation of Receiver Analog Gain at the Line to the Dig i tal DX Out put

Figure 44: Gain versus Frequency for Analog Input at the Line to the Digital DX Output

Figure 45: Signal to Total D istortion versus Input Level for Anal og at the Line to the Digital D X Output

Figure 46: Return Loss, @ 80 mA

Figur e 47: 20-Pin TSSOP Package Dimensions

Figur e 48: 32-Pin QFN Package Dimen sions

Figur e 49: 42-Pin QFN Package Dimensions

.............................................................................................. 8

................................................................................................ 9

................................................................................................ 10

.................................................................................................. 12

........................................................................................................ 14

................................................................................................................ 18

..... 19

..... 20

....................................................... 21

............................................................. 21

.............................................................................. 28

.............................................................................. 29

......................................... 31

.................................................................................................... 34

.......................................................................................... 34

....................................................................................... 35

..................................................................................... 35

..................................................................................... 35

.................................................................................................. 45

................................................................................................ 46

................................................................................. 46

....................................... 46

.................................................................................. 48

.................................................................................. 48

.............................................. 49

....................................................... 50

................................................................. 51

................................................................. 51

............ 59

.................................................................................... 63

............................................................................................................ 64

............................................. 65

......................... 66

........... 67

.................................................................. 67

..................................................................................................... 68

................................................................................................ 78

..................................... 80

..................................... 81

...... 81

.................................. 82

......................... 83

... 83

.......................................................................................................... 84

..................................................................................... 85

......................................................................................... 85

......................................................................................... 86

4 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

Tables

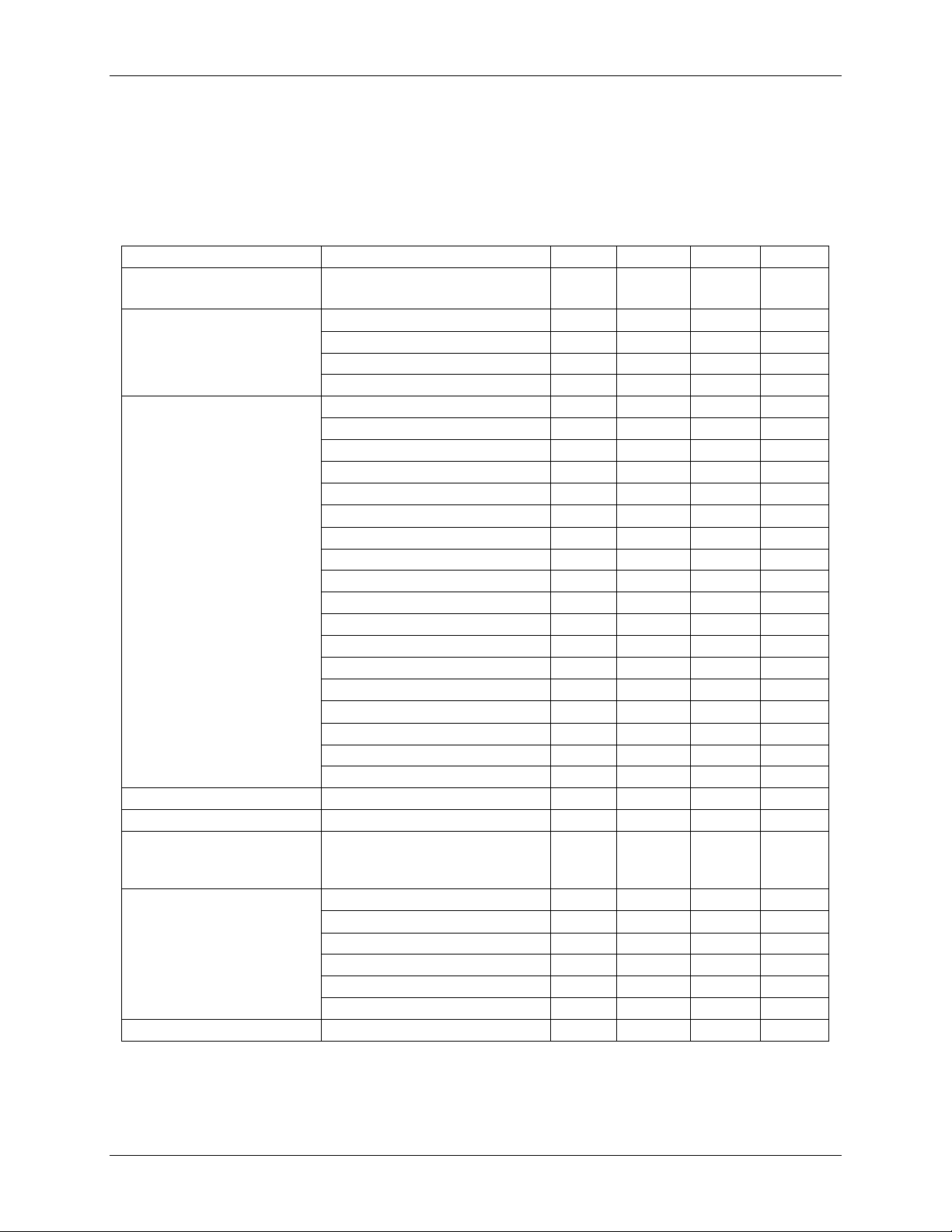

Table 1: 73M1906B 20-Pin TSSOP Pin Definitions .................................................................................. 8

Table 2: 73M1916 20-Pin TSSOP Pin Definition s

Table 3: 73M1906B 32-Pin QFN Pin Definitions

Table 4: 73M1916 32-Pin QFN Pin Definitions

Table 5: 73M1866B Pin Definitions

Table 6: Isolation Barr i er Characteristics

Table 7: Absolute Maximum Device Ratings

Table 8: Recommended Operating Conditions

Table 9: DC Char acteristics

Table 10: SPI Inter fac e Switc hing Characteristics

Table 11: Swit ching Character istics – PCM Int er fac e ( Slave M ode)

Table 12: Swit ching Character istics – PCM Int er fac e ( Master M ode)

Table 13: Refer ence Voltage Specificat i ons

Table 14: Component Val ues for the Speak er D r iver

Table 15: Call Progress Monitor Specification

Table 16: Line-Side Absolute Maximum Ratings

Table 17: VBG Specifications

Table 18: Maximum DC Transmit Levels

Table 19: Transmit Path

Table 20: Recei ve Path

Table 21: Transmit Hybrid Cancellation Characteristics

Table 22: Recei ve Notch Filter

Table 23: Over-voltage D etector

Table 24: Over-current Detector

Table 25: Und er -v oltage Detector

Table 26: Over-load Detec tor

Table 27: Refer ence Bil l of Materials for 73M1x66B

Table 28: Refer ence Bil l of Materials for Figure 14

Table 29: Compatible Pulse Transformer Sources

Table 30: Pulse Transformer Electrical C haracteristics

Table 31: Con trol and Status Register M ap

Table 32: Al phabeti cal Bit M ap

Table 33: PC M C ontrol Functions

Table 34: Transmit Gain Contr ol

Table 35: Recommended Gain Setting

Table 36: Recei ve Gain Control

Table 37: Barr ier Control Functions

Table 38: DA A C ontrol Functions

Table 39: Recommended Regi st er Settings for International Compatibi lity

Table 4 0: Li ne Sensing Control F unctions

Table 41: Loopback M odes

Table 42: Loopback M odes Summ ar y

Table 43: Order Numbers and Pac kaging M ar ks

..................................................................................... 9

..................................................................................... 10

....................................................................................... 12

........................................................................................................ 14

................................................................................................ 16

.......................................................................................... 16

....................................................................................... 16

................................................................................................................... 17

.................................................................................. 18

........................................................ 19

...................................................... 19

........................................................................................... 20

.............................................................................. 21

........................................................................................ 22

.................................................................................... 22

................................................................................................................ 23

................................................................................................ 23

......................................................................................................................... 24

......................................................................................................................... 25

.......................................................................... 26

............................................................................................................... 26

............................................................................................................ 27

............................................................................................................. 27

.......................................................................................................... 27

................................................................................................................. 27

............................................................................... 30

................................................................................. 31

................................................................................. 32

........................................................................... 32

............................................................................................ 37

.............................................................................................................. 38

.......................................................................................................... 52

............................................................................................................ 57

................................................................................................... 57

............................................................................................................. 59

........................................................................................................ 61

........................................................................................................... 68

............................................. 72

.............................................................................................. 75

.................................................................................................................... 78

.................................................................................................... 79

.................................................................................... 87

Rev. 1.6 5

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

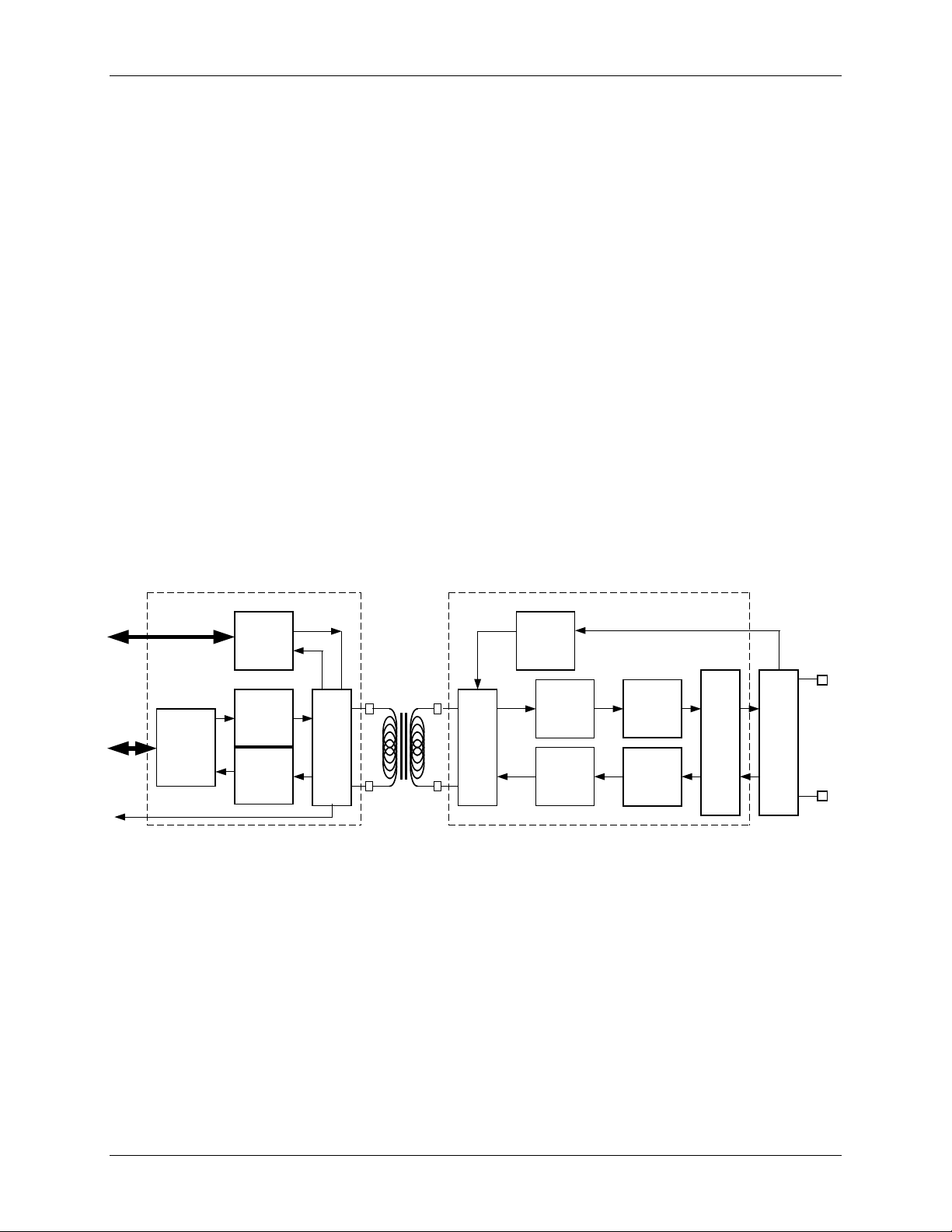

PRM SCM

(LSBI)

SinC3

Filter

On-Chip

LIC

(OnLIC)

SPI

Interface

PCM

Interface

Interpolation

Filter

Filter

PCM

SPI

Tip

Ring

PRP SCP

Host -Side Device

73M1906B

Line-Side Device

73M1916

Aux A/D

TxA

RxA

Off-Chip

LIC

(OffLIC)

(HSBI)

Decimation

Transmit

Receive

Host

Interface

Side

Barrier

Interface

Side

Barrier

Line

Digital

Sigma

Delta

Modulator

Transmit

Analog

Front End

Receive

Analog

Front End

(with Sigma

Delta

Modulator)

Call Progress Monitor Audio Out

1 Introduction

The 73M1966B is a two-device chip set that provides embedded FXO functionality by connecting a PCM

interface to a voice-band PSTN. The device set supports ITU-T Rec omm endat ion G.711 µ-law and A-law

companding, and als o a 16-bit linear mode. High-voltage isolation is provided by the physical separation

of the H ost-Side (73M19106) and Line-Side (73M1916) Devices. The Host-Side and the Li ne -Side

Devices communicate with each other using a single pu l se trans former. A few low-cost components

complete the DAA interface to the network. The pulse transformer tr ansmi ts encoded digital data rather

than analog signals as with other transformer designs. Data is transmi tted and received without the usu al

deg r adation from common mode noise and magneti c coupling typic al of other capacitive an d voice-band

tran sformer techniques. The data str eam passed between the Host -Side and Line-Side Devices includes

the m edia stream dat a, control, status, and cl ocking informati on.

This data sheet describes both the 73M19 66B and 73M 1866B, which will be collectively referred to as the

73M1x66B in this document.

A un i que capability of the 73M1x66B Host Side device (73M1906B) is its ability to provide power to the

73M1x66B Line Side device (73M1916) via the pulse transformer.

The 73M1906B exchanges control and status information with the host us in g the SPI interface, while the

PCM encoded media streams connect with other PC M-enabled devices using the PCM highway bus

interface.

Figure 1 shows a referenc e block diagram of the 73M1x66B connected by a pulse transform er and

example external lin e i nterface circu itry shown for clarification.

The Host-Side Device (73M1906B) consists of:

1. PCM Interface Bloc k (PCM)

2. SPI Inter face Bloc k (SPI)

3. Transmit Interpolation Filter

4. Receive Decimati on Filt er

5. Host-Side Barrier I nterface Circui t (HSBI)

6 Rev. 1.6

Figure 1: Simple 73M1x66B Reference Block Diagram

DS_1x66B_001 73M1866B/73M1966B Data Sheet

The Line-Side Device (73M1916) consist s of:

1. Di gital Sigma Delta Modulator

2. Transmit Analog Front End

3. Receive Analog Front End including Sigma Delta Modulator

3

4. Sinc

Filter (Sinc3)

5. On-chip Line Interface Circuit

6. Line-Side Barrier Interface Cir cuit (LSBI)

Received data from a h ost connected to the PCM bus is interpolated from the s am pling frequency of

8 kH z or 16 kHz (for PCM encoded str eams) to twice the sampling frequency. The control information is

multiplexed with th e audio stream sig nals and transmi tted across the isolation barrier to the Li ne-Side

Device. In the Line-Side Device, the t wo stream s are separated and the audio signal is convert ed to

analog for transmission t o the line.

An audio stream received at the analog line inpu t pins is c onverted to a seriali zed data stream and, along

with s tatus information such as line condit ion from the Auxiliar y Analog to Digital Converter, is transmitted

over the isolation barrier using th e pulse tr ansformer. The dat a i s extracted with status informat ion being

tran smitted on the SPI. The audio stream is sent to a host using the PC M bus.

The 73M1x66B is an enhanced version of the 73M1966 that includes the additional functionality of finer

resolution of t r ansmi t and receive gain, receiver DC offset sub traction and support for T-1 PCLK

frequencies.

Rev. 1.6 7

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

73M1906B

1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

CS

VPD

DR

DX

FS

PCLKO

PCLKI

VNA/VND

AOUT

VPA VNT

SCLK

SDI

SDIT

SDO

RST

PRM

PRP

VPT

INT

20

SCLK

I

SPI clock

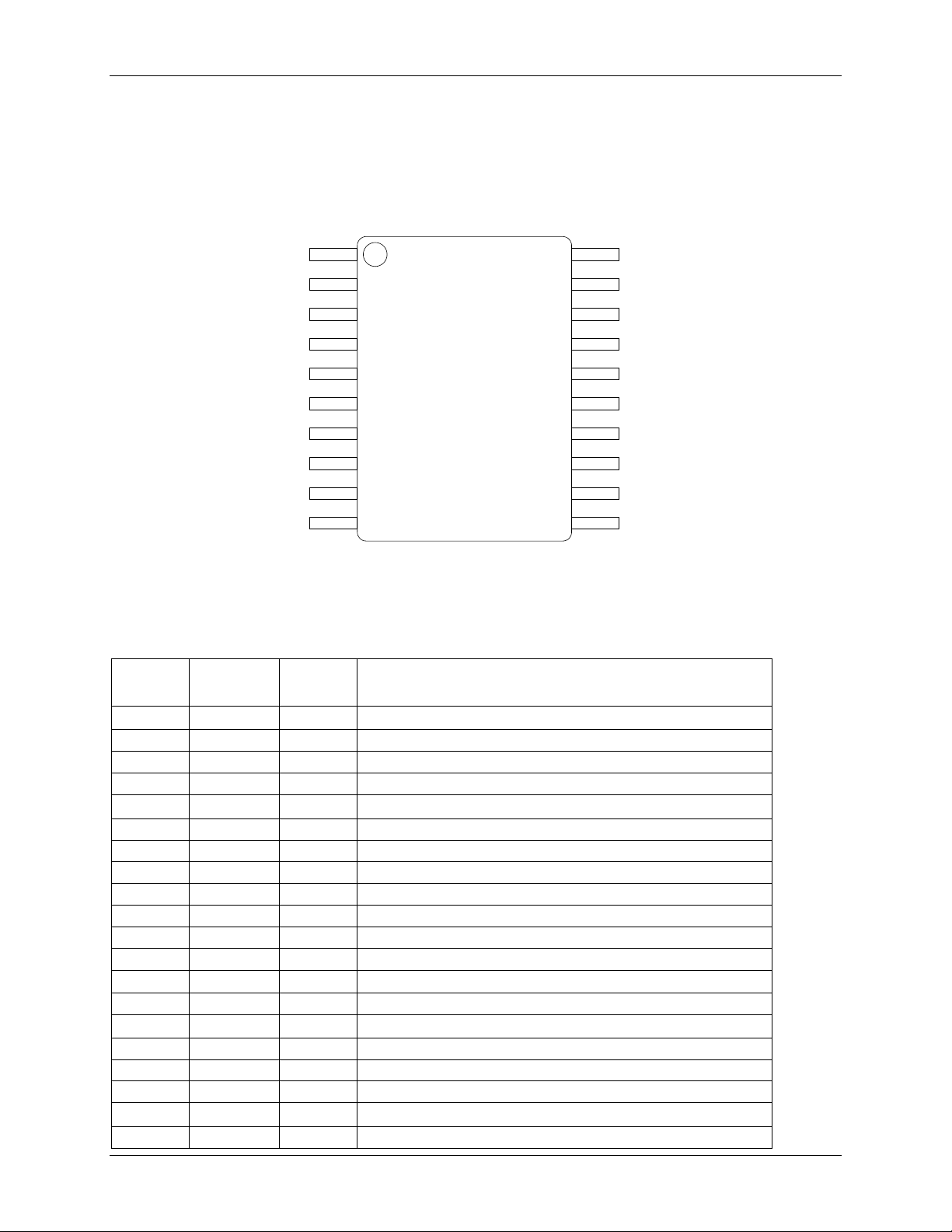

2 Pinout

The 73M1906B and the 73M1916 are supplied as 20-pin TSSOP packages and as 32 -pin QFN packages.

2.1 73M1906 B 20-Pin TSSOP Pinout

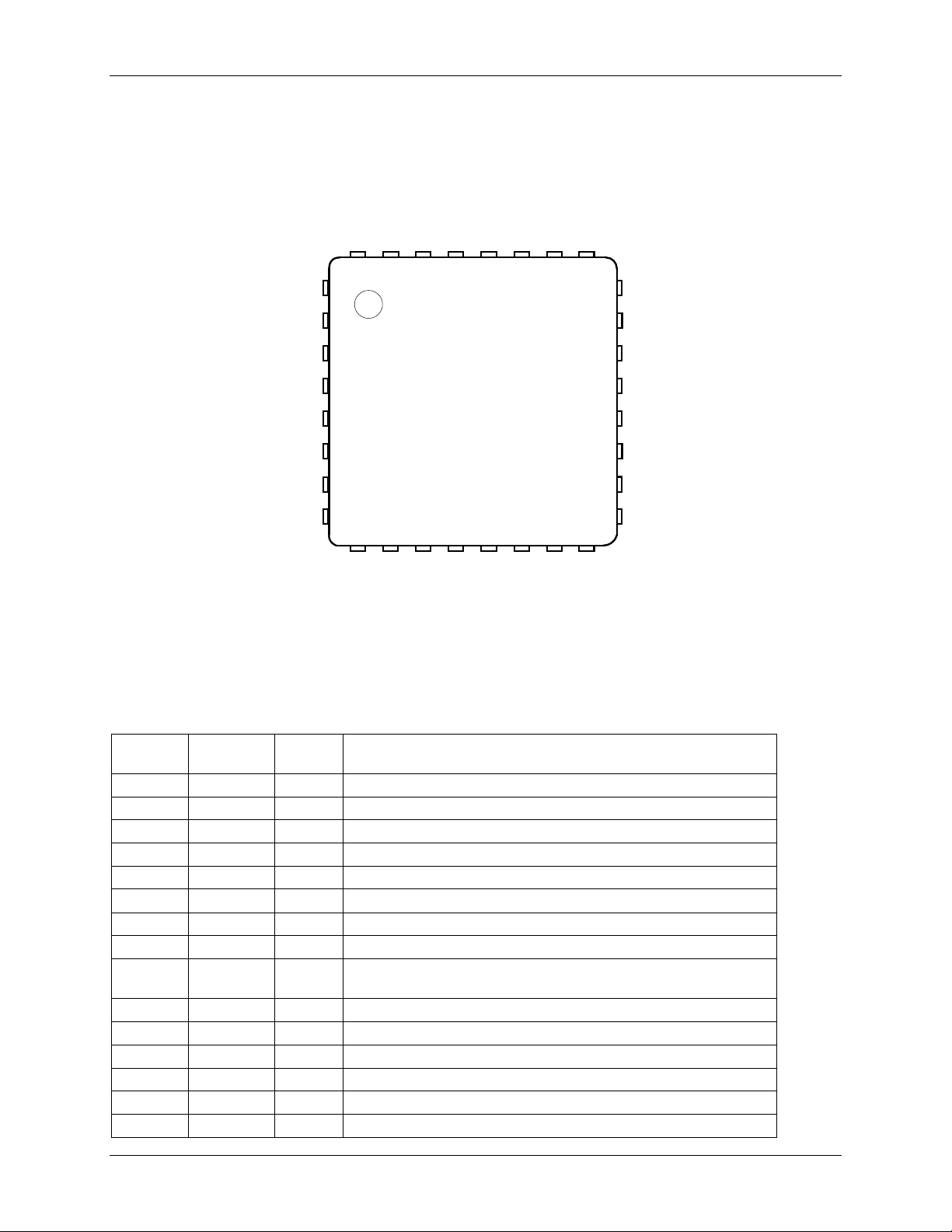

Figure 2 shows t he 73M1906B 20-pin TSSOP pinout.

Figure 2: 73M1906B 20-Pin TSSOP Pinout

Table 1 describes the pin functions for th e device. Dec oupling capacitors on the power supplies should

be included for each pair of supply pins.

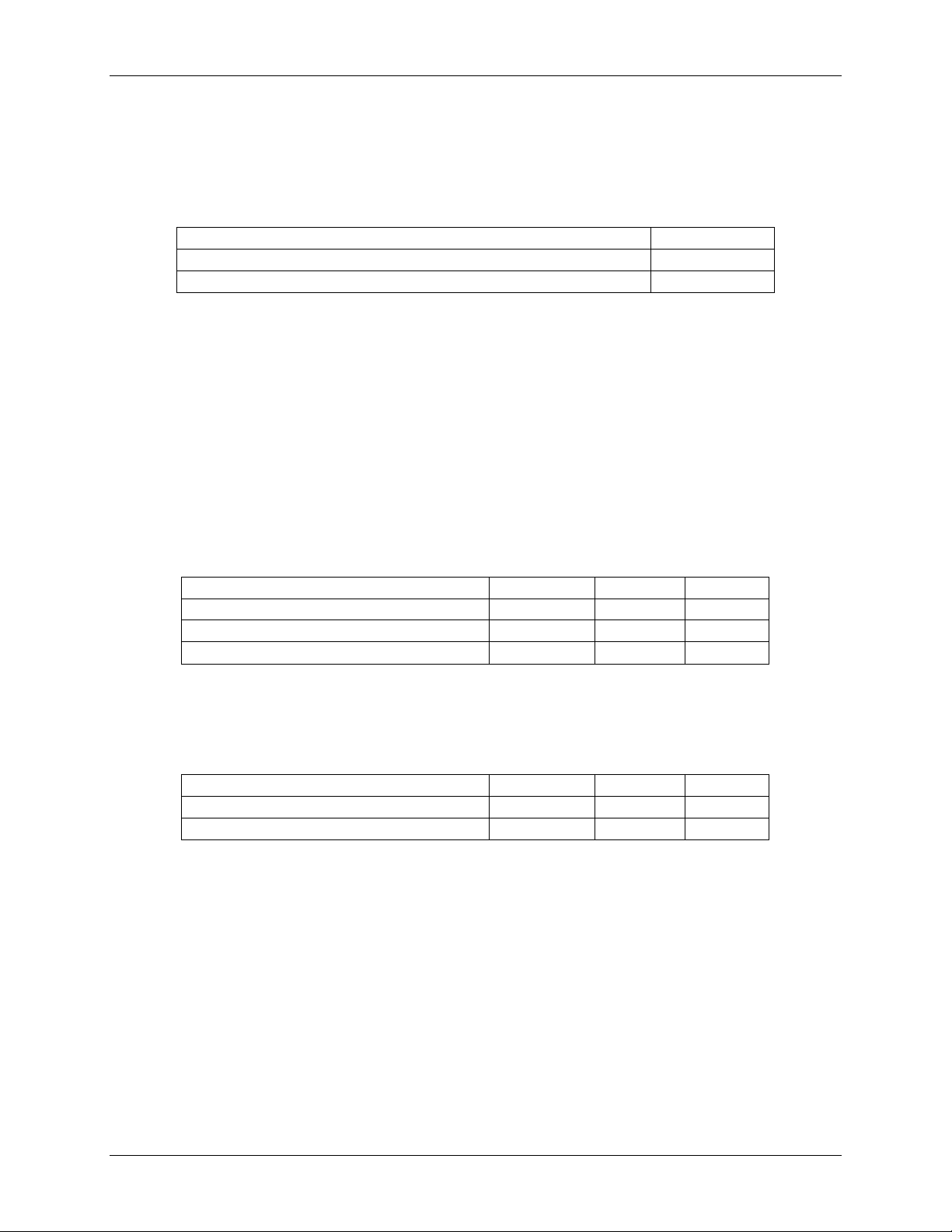

Table 1: 73M1906B 20-Pin TSSOP Pin Definitions

Pin

Number

1

Pin

Name

CS

Type Description

I SPI chip selec t (active low)

2 VPD PWRI Positive digital supply

3 DR I PCM transmit data sen t to the D to A

4 DX O PCM received data from the A to D

5

FS

I/O PCM frame synchronization

6 PCLKO O PCM clock output

7 PCLKI I PCM clock in

8 VNA/VND GND Negative analog/digital ground

9 AOUT O Aud i o output – must be buffered for speaker

10 VPA PWRI Positive anal og supply

11 VNT GND Negative transformer supply

12 PRM I/O Transformer pr imary minus

13 PRP I/O Transformer pr imary plus

14 VPT PWRI Positive tr ansformer supply

15

RST

16 SDIT O S PI data out for dais y c hain mode

17 SDI I SPI data in

18 SDO O SPI data out

19

INT

I Hardw ar e reset (active low)

O Interrupt / ring detect (active low – open drain)

8 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

73M1916

1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

DCI

RGN

RGP

OFH

VNX

SCP

MID

VPX

SRE

SRB VBG

DCS

DCD

TXM

RXM

RXP

ACS

VNS

VPS

DCG

8

VPX

PWR

Sup ply from the barrier

11

VBG

O

VBG bypass, connect to 0.1 μF capacitor to VNS

2.2 73M1916 20-Pin TSSOP Pinout

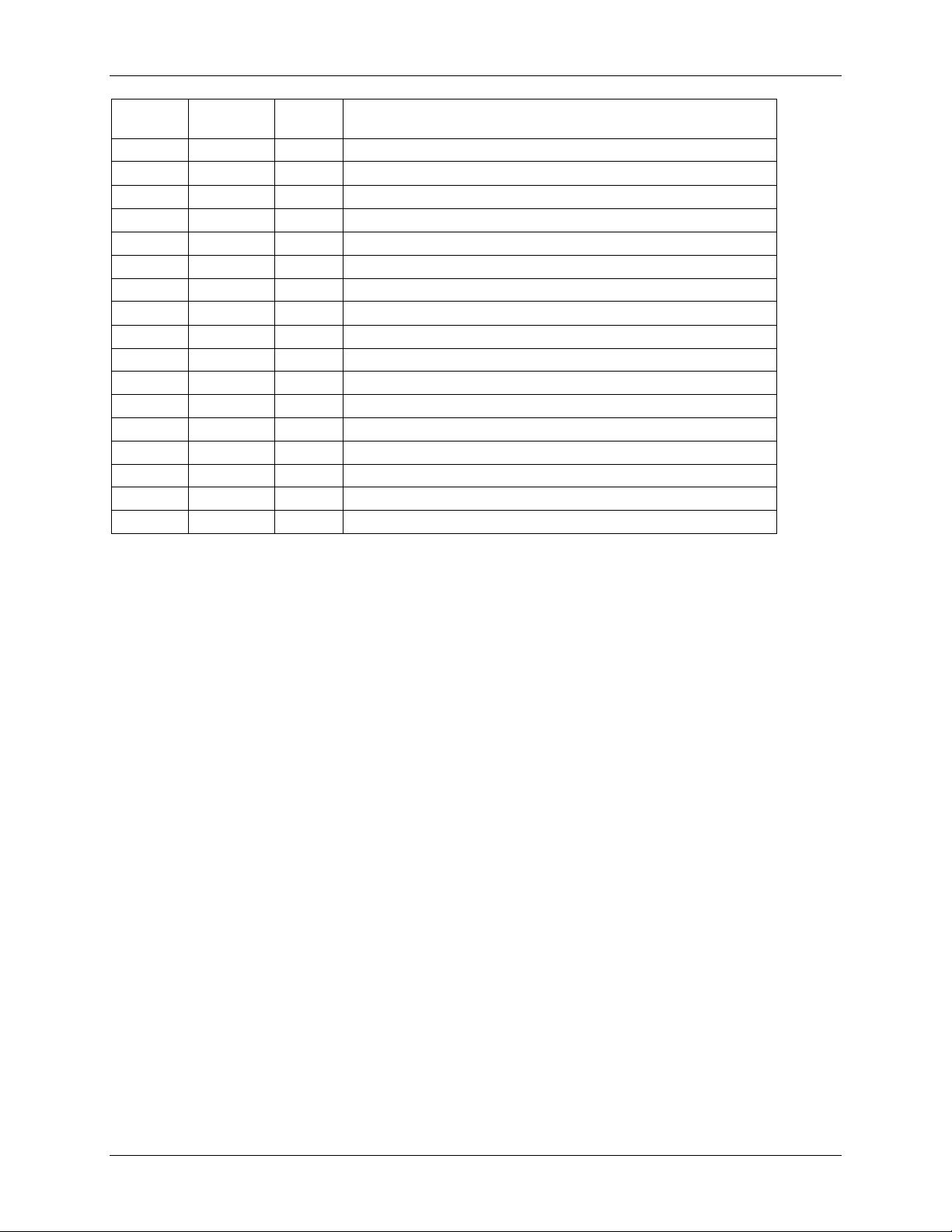

Figure 3 shows the 73M1916 20-pin TSS O P pi no u t.

Figure 3: 73M1916 20-Pin TSSOP Pinout

Table 2 describes the pin functions for the device. Decoupling capacitors on the power supplies should

be included for each pair of supply pins.

Table 2: 73M1916 20-Pin TSSOP Pin Definitions

Pin

Number

Pin N ame Type Description

1 DCI I DC loop input

2 RGN I Ring detect neg ative voltage input

3 RGP I Ring detect positive voltage input

4 OFH O Off-hook c ontrol

5 VNX GND Negative supply voltage (line s i de of the barrier)

6 SCP I/O P ositive side of th e second ar y pulse t r ansformer winding

7 MID I/O Char ge pum p mi d po i nt

9 SRE I Voltage r egulat or sense

10 SRB O V ol tage reg ulator drive

12 ACS I A C current sense

13 VNS GND An al og negative supply voltage

14 VPS PWRO An al og positive supply voltage (output)

15 RXP I R eceive plus – signal input

16 RXM I Rec eive minus – signal input

17 TXM O Transmi t minus – transhybrid cancellation output

18 DCD O DC loop output

19 DCS I DC loop curren t sense

20 DCG O DC l oop control

Rev. 1.6 9

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

6

7

8

9

5

4

3

2

1

17

18

19

20

24

23

22

21

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

GPIO7

TSC

DX

VPD

FS

PCLKO

PCLKI

VND

SDO

SDI

SDIT

RST

VPD

VPT

PRP

PRM

VNA /

VNPLL

VBG

AOUT

VPA /

VPPLL

N/C

VNT

N/C

N/C

73M1906B

GPIO5

GPIO6

DR

VPD

CS

SCLK

INT

VND

Pin

Pin N ame

7

PCLKI

I

PCM clock in

12

VPA/VPPLL

PWR

Positive anal og/PLL supply

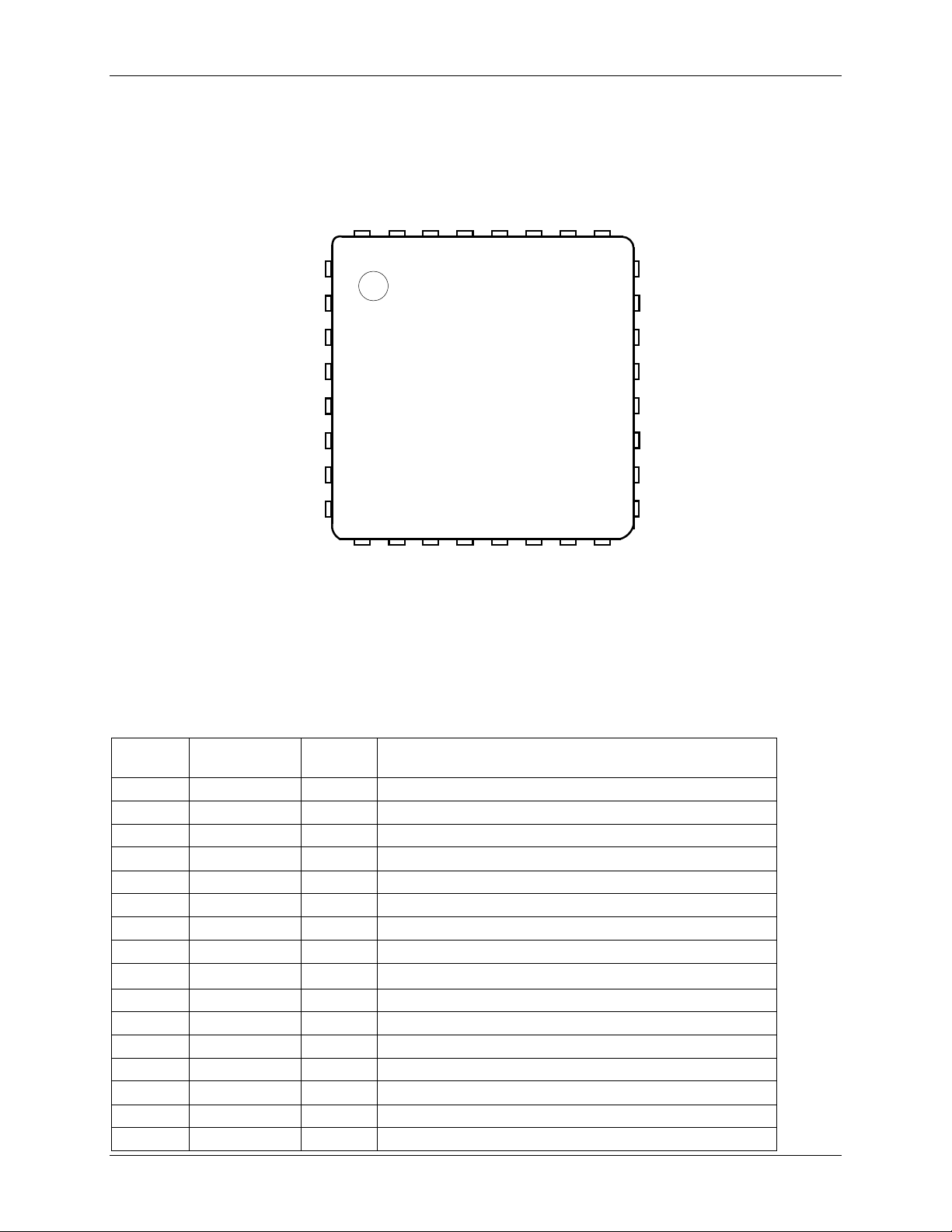

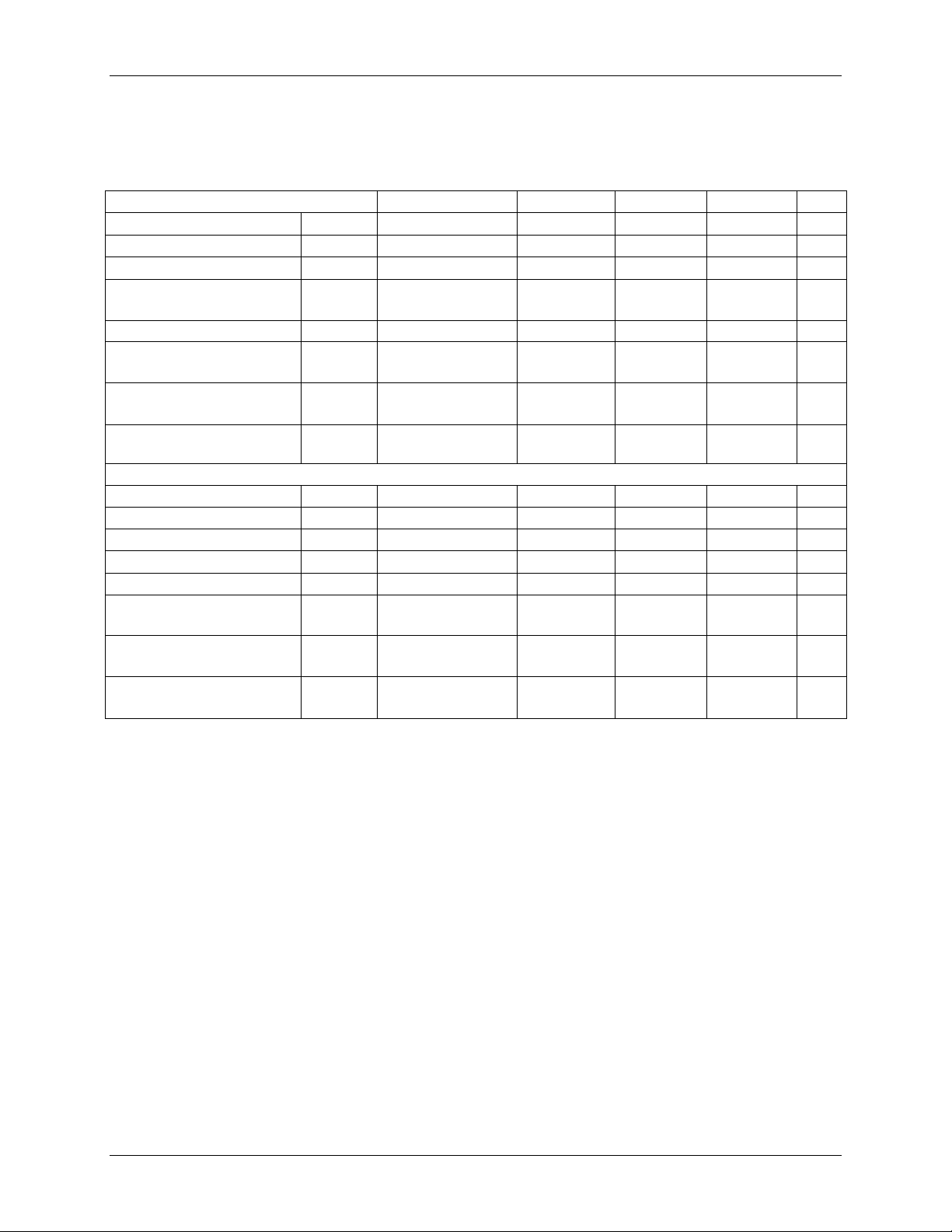

2.3 73M1906 B 32-Pin QFN Pinout

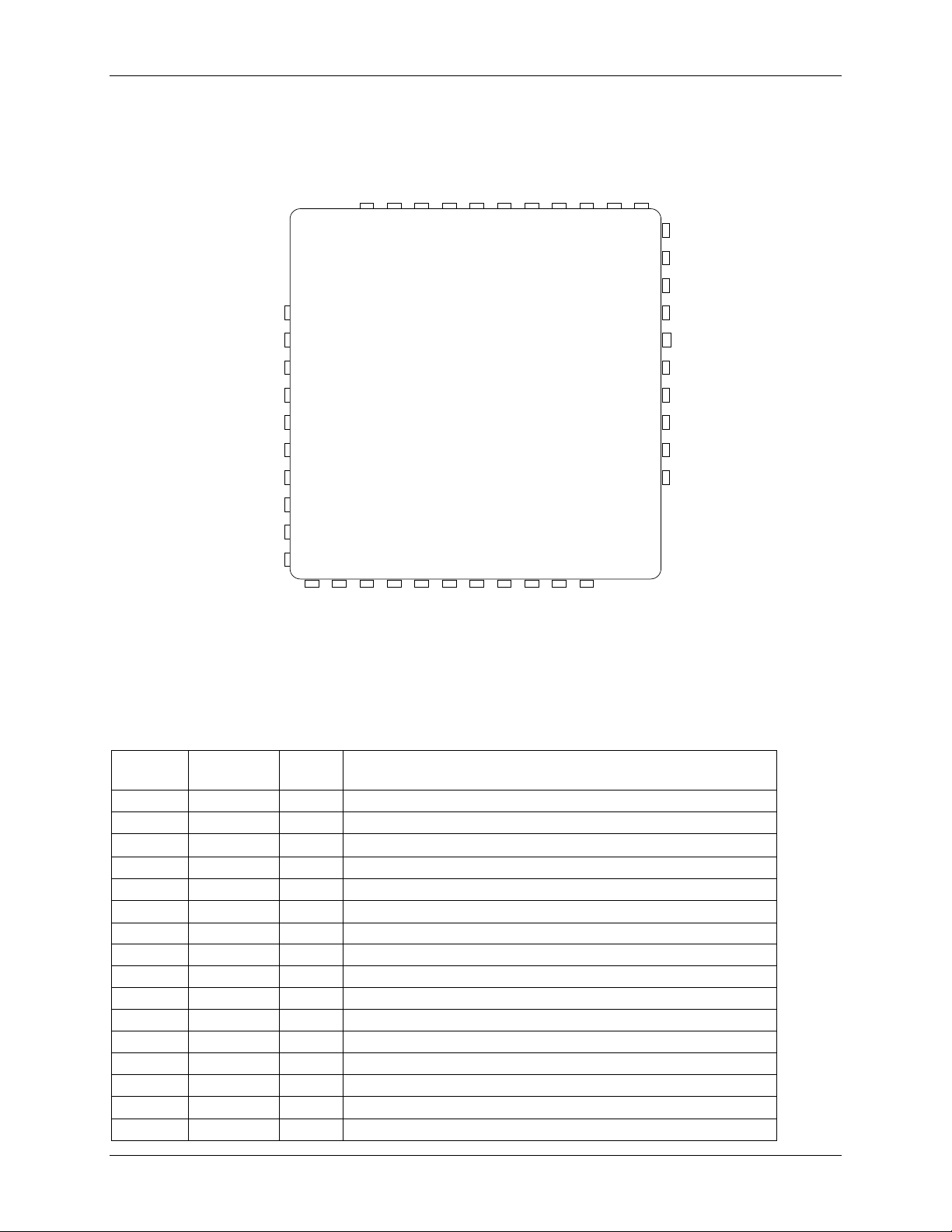

Figure 4 shows t he 73M1906B 32-pin QFN pinout.

Figure 4: 73M1906B 32-Pin QFN Pinout

Table 3 describes the pin functions for the device. Decoupling capacitors on the power supplies should

be included for each pair of supply pins.

Table 3: 73M1906B 32-Pin QFN Pin Definitions

Number

Type Description

1 GPIO7 I/O Configurable input/output pin

2 TSC O P C M time slot control ( active low)

3 DX O P C M r eceived data from the A to D

4 VPD PWR Positive digital su pply

5

6 PCLKO O PCM clock output

8 VND GND Negative digital g r ound

9 VNA/VNPLL GND Negative analog/PLL ground

10 VBG O B and gap voltage reference monitor

FS

I/O P C M frame synchroniz ation

11 AOUT O Audio output – must be buffered for speaker

13 N/C – No con nect

14 VNT GND Negative t r ansformer supply

15 N/C – No con nect

16 N/C – No con nect

10 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

21

I

Hardw ar e reset (active low)

Pin

Number

17 PRM I/O Transformer pr imary minus

18 PRP I/O Transformer p r imary plus

19 VPT PWR Positive transformer suppl y

20 VPD PWR Positive digital su pply

RST

22 SDIT O S PI data out for daisy-chain mode

23 SDI I S PI data in

24 SDO O S PI data out

25 GPIO5

26 VND

27 INT

28 SCLK

29 CS

30 VPD PWR Posit ive dig ital supply

31 DR I P C M transmi t data sen t to the D to A

32 GPIO6 I/O Configurable input/output pin

Pin N ame

Type Description

I/O Configurable input/output pin

GND Negative digital ground

O Interrupt / ring detect (active low – open drain)

I SPI clock

I S PI chip s el ect (active low)

Rev. 1.6 11

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

6

7

8

9

5

4

3

2

1

17

18

19

20

24

23

22

21

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

CKO

OFH

CKI

VNX

SCP

MID

SCM

VPX

RST

DCD

TST

TXM

SACIN

RXM

RXP

VPS

RCT

BYP

SRE

SRB

VNS

VBG

ACS

VNS

73M1916

DCS

GPO

GPI

VNS/VND

RGP

RGN

DCI

DCG

Pin

Pin

9

RCT

I

External rectification – disables intern al r ectifier wh en low,

14

VBG

O

VBG bypass, connect to 0.1μF capacitor to VNS

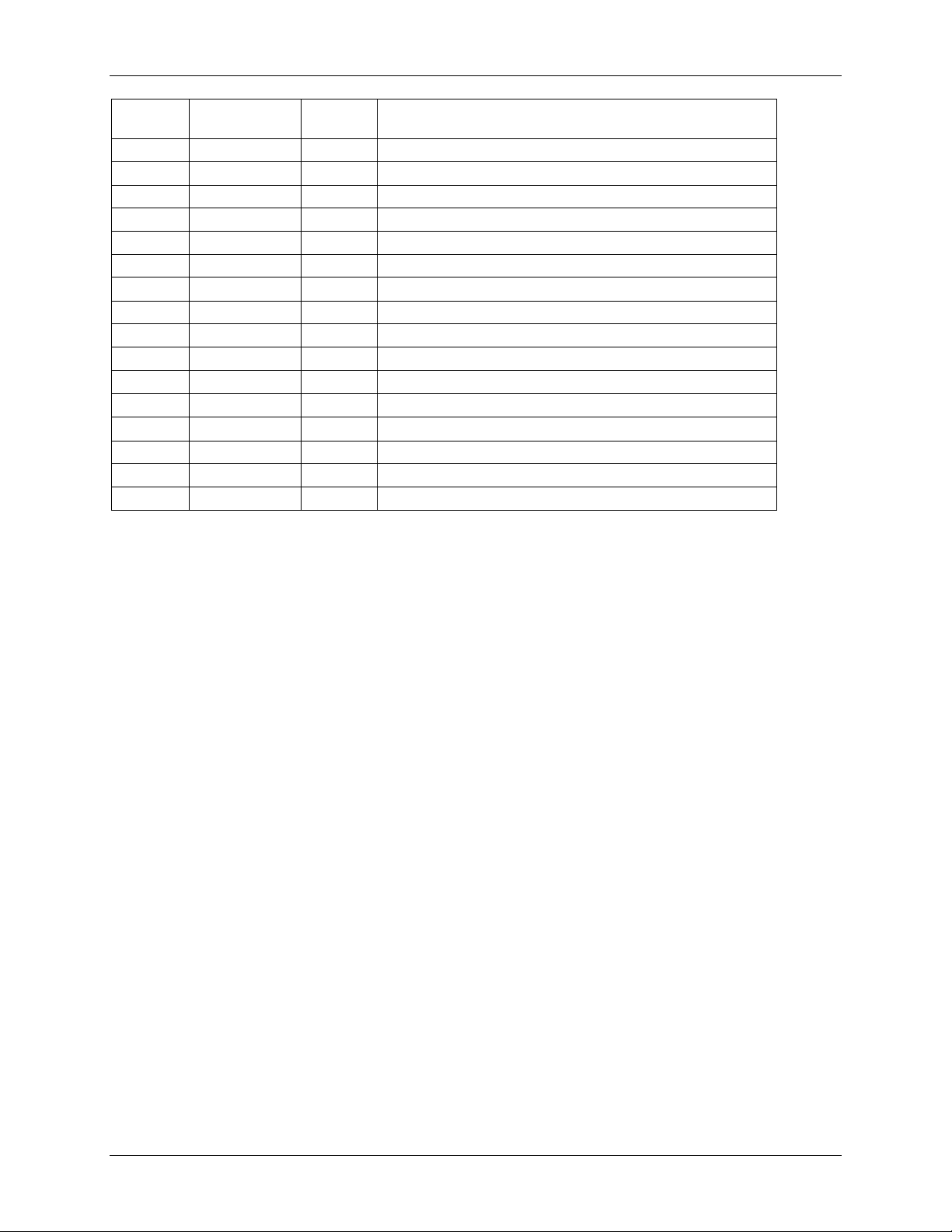

2.4 73M1916 32-Pin QFN Pinout

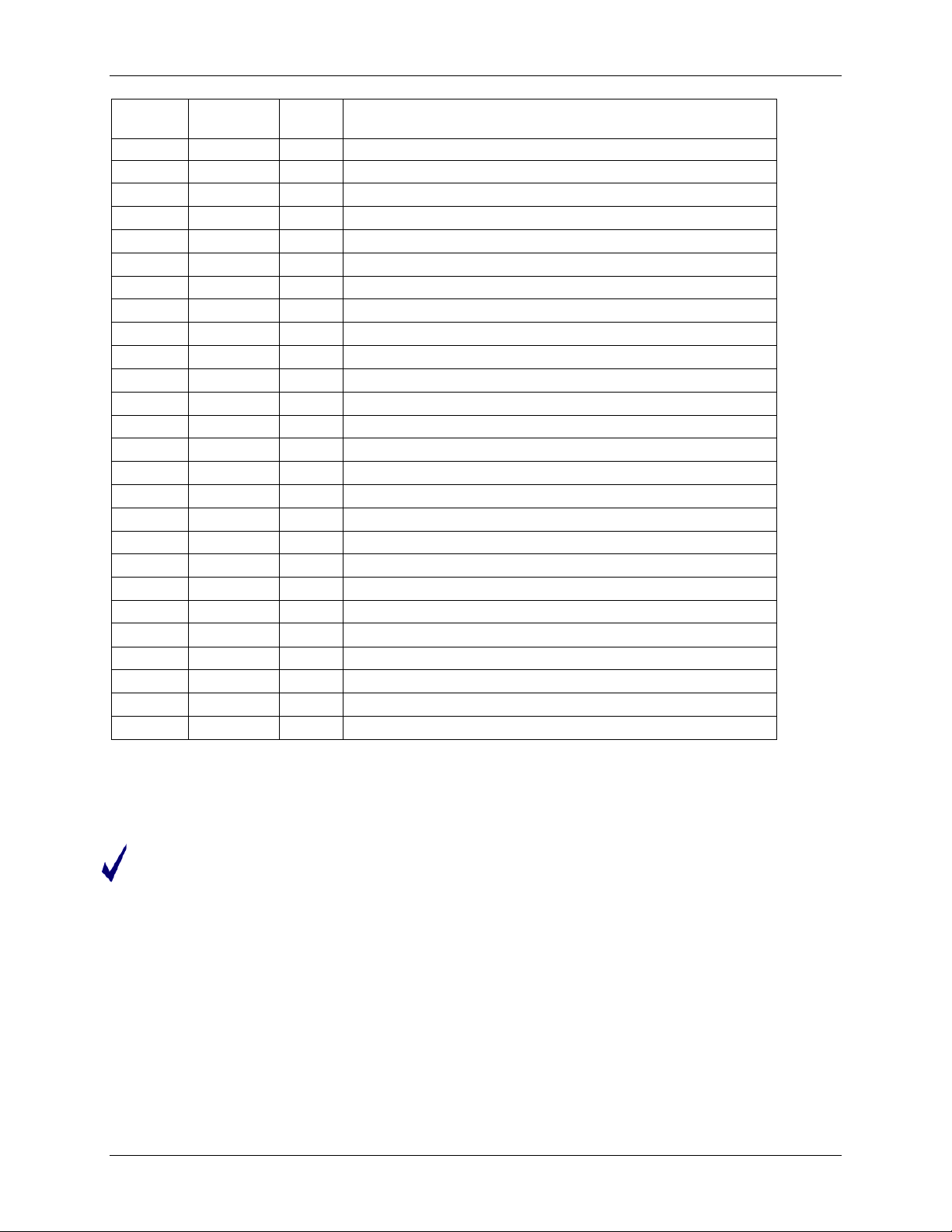

Figure 5 shows the 73M1916 32-pin QFN pi no ut.

Figure 5: 73M1916 32-Pin QFN Pinout

Table 4 describes the pin functions for the device. Decoupling capacitors on the power supplies should

be included for each pair of supply pins.

Table 4: 73M1916 32-Pin QFN Pin Definitions

Number

Name

Type Description

1 CKO O Test point for r ecovered clock

2 OFH O Off-hook control

3 CKI I Test input for clock

4 VNX GND Negative supply voltage

5 SCP I/O Positive side of the secondary pulse t r ansformer windi ng

6 MID I/O Charge pump mi d po i nt

7 SCM I/O Negative side of the second ar y pulse transformer winding

8 VPX PWR Supply from the barrier

10 BYP I Test pin, leav e open

11 SRE I Voltage regulator sense

12 SRB O Voltage regulator drive

13 VNS GND Digital negative supply voltage

leave open

15 ACS I AC current sense

12 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

26

DCG

O

DC loop control

29

RGP

I

Ring detect positive voltage input

Pin

Number

Pin

Name

Description

Type

16 VNS GND An al og negative supply voltage

17 VPS PWRO Analog positive supply voltage (output)

18 RXP I Receive plus – signal i nput

19 RXM I Receive minus – signal input

20 SACIN I Call er ID mode AC impedanc e connecti on

21 TXM O Transmit Minus – trans hybrid cancellati on output

22

23

TST

RST

I Factory test mode, leave open

I Resets the control registers to default – weakly pulled high

24 DCD O DC loop output

25 DCS I DC loop current sense

27 DCI I DC loop input

28 RGN I Ring detect negati ve voltage input

30 VNS GND Negative supply voltage (line s i de of the barrier)

31 GPI I General purpos e input ( test pin)

32 GPO O General purpose output (test pin)

Rev. 1.6 13

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

DX

VPD

FS

PCLKO

VNA

PCLKI

AOUT

VPA

VNT

PRM

PRP

VPT

RST

SDIT

SDI

VND

SDO

INT

SCLK

CS

DR

SRE

SRB

VBG

ACS

VNS

VPS

RXM

RXP

TXM

DCD

DCS

DCG

DCI

RGN

RGP

OFH

M20PB

VNX

SCP

MID

VPX

73M1866B

1

2

3

4

5

6

7

8

9

10

20

11

12

13

14

15

16

17

18

19

21

22

23

24

25

26

27

28

29

30

31

32

33

35

34

36

37

38

39

40

41

42

Pin

1

O

PCM received data from the A to D

8

PWR

Positive anal og supply

2.5 73M1866 B Pinout

Figure 6 shows t he 73M18 66B 42-pin pinout.

Figure 6: 73M1866B 42-Pin Pinout

Table 5 describes the pin functions for the device. Decoupling capacitors on the power supplies should

be included for each pair of supply pins.

Table 5: 73M1866B Pin Definit ions

Number

2 VPD PWR Positive digital supply

3

4 PCLKO O PCM clock output

5 VNA GND Negativ e analog ground

6 PCLKI I PCM clock in

7 AOUT O A udio out put – must be buffered for speaker

9

10

11 PRP I/O Transform er primary plu s

12 VPT PWR Positive transfor mer su pply

13

14 SDIT O SPI data out for d ai sy-chain mode

15 SDI I SPI dat a in

16 SDO O SPI data out

14 Rev. 1.6

Pin N ame Type Description

DX

FS

VPA

VNT

PRM

RST

I/O PCM frame synchron ization

GND Negative transformer supply

I/O Tr ansformer primary minus

I Hardware reset (active low)

DS_1x66B_001 73M1866B/73M1966B Data Sheet

31

O

DC loop output

41

I/O

Char ge pum p mi d po i nt

Pin

Number

Pin N ame Type

Description

17 VND GND Negative digital g r ound

18 INT O Interrupt / ring detect (active low – open drain)

19

SCLK

I SPI clock

20 CS I SPI chip sel ect (act i ve low)

21

22

DR

SRE I Voltag e r egulat or sense

23 SRB

24

VBG

25 ACS

26

27

28

29

30

VNS

VPS PWRO Analog positive supply voltage (output)

RXP

RXM

TXM

DCD

I PCM transmit data sent to the D to A

O Voltage regulator drive

O VBG bypass, connect to 0.1μF capacitor to VNS

I AC current sense

GND A nalog negative supply voltage

I Receive pl us – signal inp ut

I Receive m inus – s ignal inp ut

O Transmit Minus

– transhybri d cancellation output

32 DCS I DC l oop current sense

33

34

35

36

37

38

39

DCG

DCI

RGN

RGP

OFH

M20PB

VNX

O DC loop contr ol

I DC loop input

I Ring detect negative voltage input

I Ring detect positive voltage input

O Off-h ook con trol

I Test pin . Connect to VNX.

GND Negative supply voltage

40 SCP I/O Positive si de of the secondary pulse trans former winding

MID

42

VPX

PWR Supply from the bar r i er

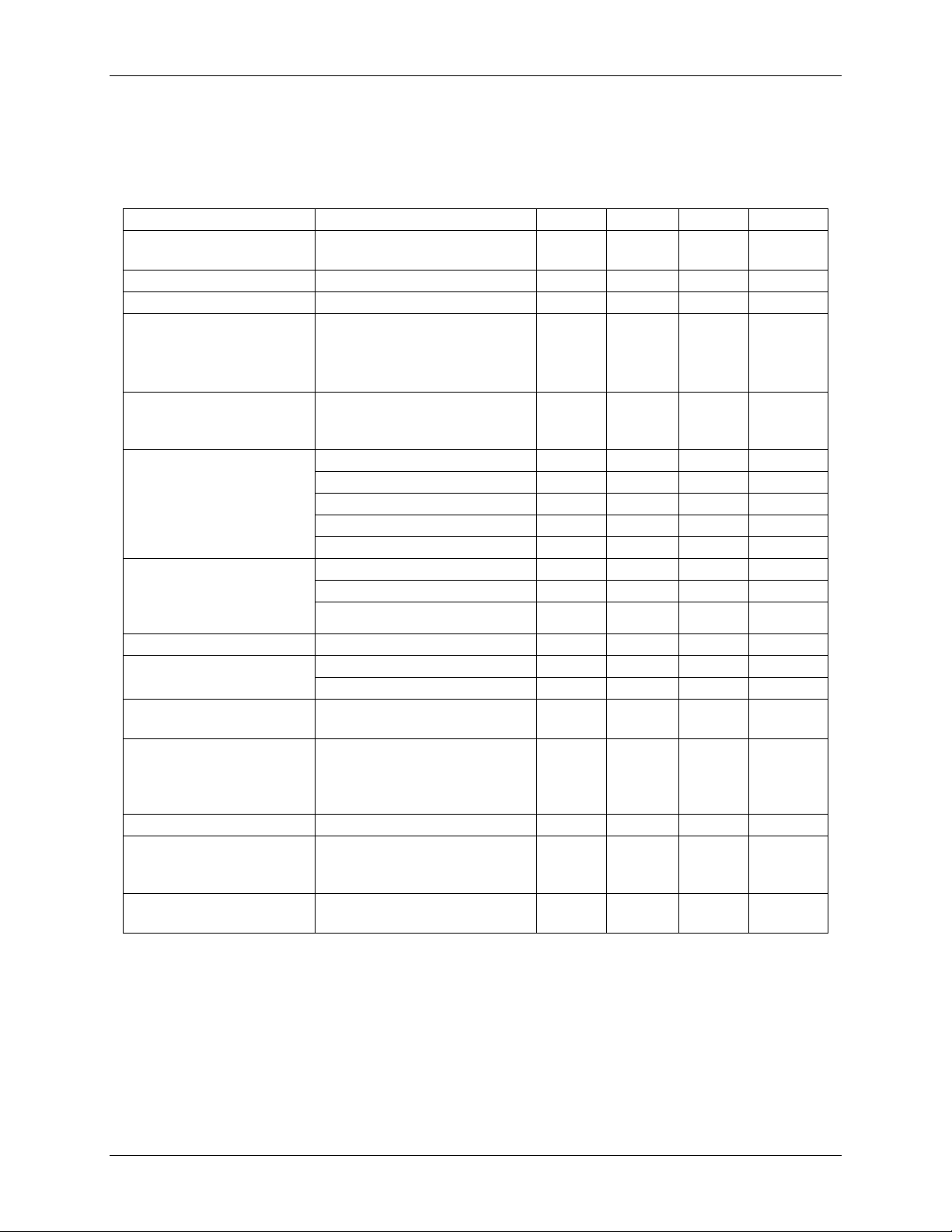

2.6 Requisite Use of Expos ed Bottom Pa d o n 73M1866 B and 73M1966B QFN Packages

The exp osed bottom pad is not intended for t hermal r elief (heat diss i pation ) and should not be

sold er ed to the PCB. Soldering of the expos ed pad could also comprom i se electrical

isolation/insulation requir ements for proper voltage isolation. Avoid any PCB traces or through -hole

vias on the PCB beneath the exposed pad area.

Rev. 1.6 15

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

Parameter

Rating

Parameter

Min

Max

Unit

Parameter

Min

Max

Unit

3 Electrical Characteristics and Specifications

3.1 Isolation Barrier Characteristics

Table 6 provides the character istics of the 73M1x66B Isolati on Barrier.

Table 6: Isolation Barrier Characteristics

Barrier frequ en cy 768 kHz

Data t r ansfer rate across the barrier for the sampling r ate of 8 kHz 1.536 Mbps

When 16 kHz sampling rate is selec ted, the frequency and data transfer rates are twic e those shown

above.

3.2 Electrical Specif ic ati ons

This s ection provides t he absolute m aximum ratings, the recomm ended oper ating conditions and the DC

characteristics.

3.2.1 Absolute Maximum Ratings

Table 7 l i sts the maximum operating condition s for the 73M1x66B. Perman ent device d amage may occ ur

if absol ute m aximum ratings are exceeded. Exposure to the extremes of the abs olut e m aximum rating for

extended peri ods may af fect devi ce reliability.

Table 7: Absolute Maximum Device Ratings

Sup ply voltage -0.5 4.0 V

Pin input voltage (except OSCIN) -0.5 6.0 V

Pin input voltage (OSCIN) -0.5 to VDD 0.5 V

3.2.2 Recommended Operating Conditions

Function operation should be restri cted t o the recommended op er ating conditions speci fied in Table 8.

Table 8: Recommended Operating Conditions

Sup ply voltage (VDD) wit h respect to VSS 3.0 3.6 V

Operating temperature -40 85 °C

16 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

Parameter

Condition

Min

Nom

Max

Unit

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

3.2.3 DC Characteristics

Table 9 lists the 73M1x66B DC chara cte ristics.

Table 9: DC Characteristics

Input low voltage VIL – -0.5 –

Input high voltage VIH1 – 0.7 VDD

Output low voltage VOL IOL=4 mA

Output low voltage

VOL IOL= 1 mA

FSB,SCLK,

Output high voltage VOH IOH=-4 mA VDD - 0.45

Output high voltage

VOH IOH=-1 mA VDD - 0.45

FSB, FSBD, SCLK

Input low leakage current IIL1 VSS < Vin < VIL1 10

Input high l eakage

IIH1 VIH1 < Vin < 5.5 –

current

IDD curr en t at 3.0 V – 3.6 V Nominal at 3.3 V

Active digital current IDD1

Active PLL current IDD1

Active analog current IDD1

IDD total current* IDD1

IDD total current* IDD2

IDD cu rrent

IDD3

dig

pll

ana

1.0 1.5 mA

1.0 1.5 mA

12 17 mA

15 20 mA

20 30 mA

1.0 5 μA

PWDN=1

IDD cu rrent

IDD4

0.5 1.0 mA

SLEEP=1 (Ext Ref Clk)

IDD cu rrent

IDD6

1.0 1.5 mA

ENFEH=0 (Ext Ref Clk)

0.2 ∗ VDD

5.5 V

0.45 V

0.45 V

V

V

40 μA

1 μA

V

*Note: IDD1 is with the secondary of the barrier left open.

IDD2 is with the secondary of the barrier connected to 73M1916 fully powered.

Rev. 1.6 17

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

–

–

–

–

–

–

–

–

–

–

–

–

–

–

SDO turn off delay

t

– – 20

ns

SDO hold time

t

– – 20

ns

CS

SCLK

SDI

SDO

t

ics

t

scy

t

ids

t

idh

t

odd

t

odh

t

odo

t

ich

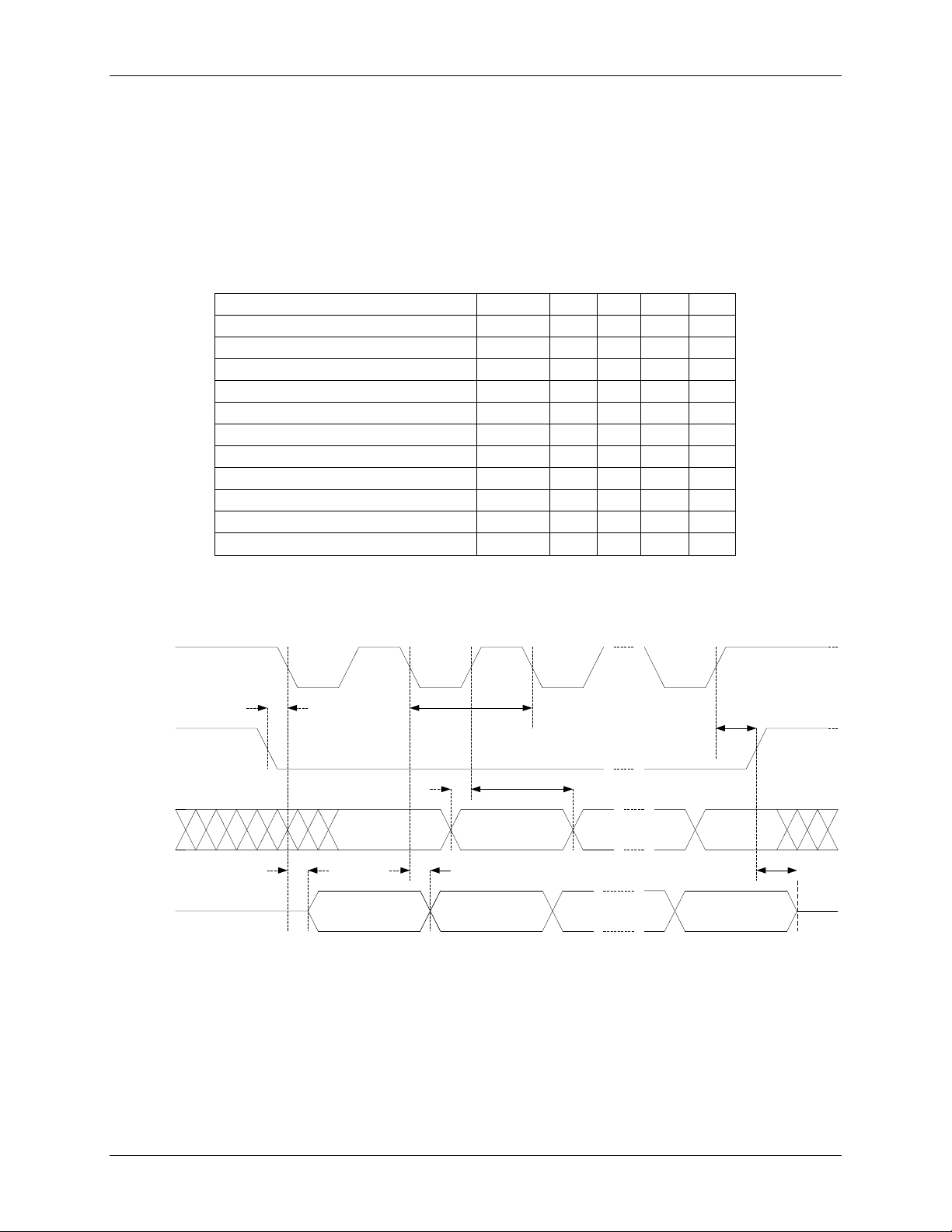

3.3 Interface Timing Specification

There ar e three interfaces assoc iated with the 73M1x66B: th e SPI interfac e, the PCM highway interface

and the line interface. This sec tion p r ovides the timi ng specific ation for the SPI interfac e and the PCM

highway interface.

3.3.1 SPI Interface

Table 10 li sts the character i stics for the SPI interfac e.

Table 10: SPI Interface Switching Characteristics

Parameter Symbol Min Typ Max Unit

SCLK cycle time1 t

SCLK rise tim e t

SCLK fall time t

CS setup time t

CS hold time t

SDI setup time t

SDI hold time t

SDO turn on d el ay t

SDI to SDITHRU propagation del ay t

Note1: The minimal value of this paramet er is for the case where only one 73M1906B is connect ed to the

host. If the daisy chai n mode is used, th e m inimum S CL K cycle time increas es according t o the numb er

of slaves in t he chain.

62.5

scy

scr

scf

25

ics

20

ich

25

ids

20

idh

–

odd

odo

odh

– 6 – ns

idt

– ns

25 ns

25 ns

20 ns

ns

ns

ns

ns

18 Rev. 1.6

Figure 7: SPI Timing Diagram

DS_1x66B_001 73M1866B/73M1966B Data Sheet

Parameter

Symbol

Min

Typ

Max

Unit

pcy

–

–

–

–

–

–

–

–

–

–

ids

–

–

idh

–

–

odd

–

–

odo

–

–

–

–

Parameter

Symbol

Min

Typ

Max

Unit

PCLK_OUT cycle time

t

–

488 – ns

–

–

–

–

–

–

–

–

–

–

–

–

–

DX tu r n on delay

t

–

–

20

ns

DX turn off delay

t

–

–

20

ns

–

–

FS

PCLK

DR

DX

t

ifs

t

pcy

t

ids

t

idh

t

ird

t

odd

t

odo

t

ifh

t

ifc

t

odh

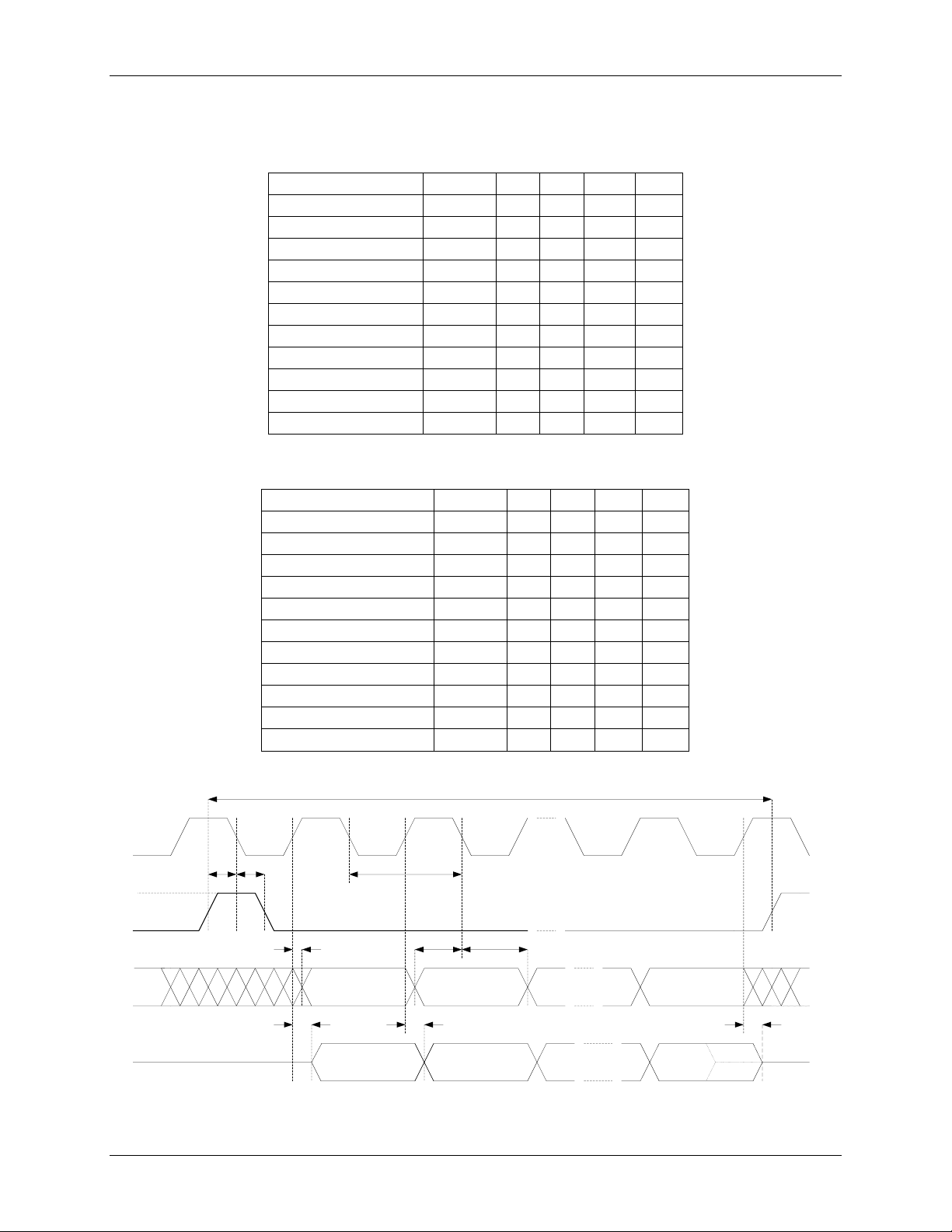

3.3.2 PCM Highway Interface

Table 11: Switching Characteristics – PCM Interface (Slave Mode)

PCLK_IN cycle time t

PCLK_IN rise tim e t

PCLK_IN fall time t

FS s etup tim e t

FS hold time t

FS cycle time t

DR setup tim e t

DR hold time t

DX tu r n on delay t

DX turn off delay t

DX hold time t

122

pcr

pcf

25

ifs

20

ifh

– 125

ifc

25

20

odh

3906 ns

25 ns

25 ns

ns

ns

μs

ns

ns

20 ns

20 ns

20 ns

Table 12: Switching Characteristics – PCM Interface (Master Mode)

pcy

PCLK_OUT rise tim e t

PCLK_OUT fall time t

FS s etup tim e t

FS hold time t

FS cycle time t

DR setup tim e t

DR hold time t

DX hold time t

pcr

pcf

50

ifs

50

ifh

– 125

ifc

25

ids

20

idh

odd

odo

odh

25 ns

25 ns

ns

ns

μs

ns

ns

20 ns

Figure 8: PCM Timing Diagram for Positive E dg e T ran smit Mode and Neg at ive Edg e R ec eiv e Mo de

Rev. 1.6 19

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

FS

PCLK

DR

DX

t

ifs

t

pcy

t

ids

t

idh

t

ird

t

odd

t

odo

t

ifh

t

odh

Figure 9: PCM Timing Diagram for Negative Edge Transmit Mode and Positive Edge Receive Mode

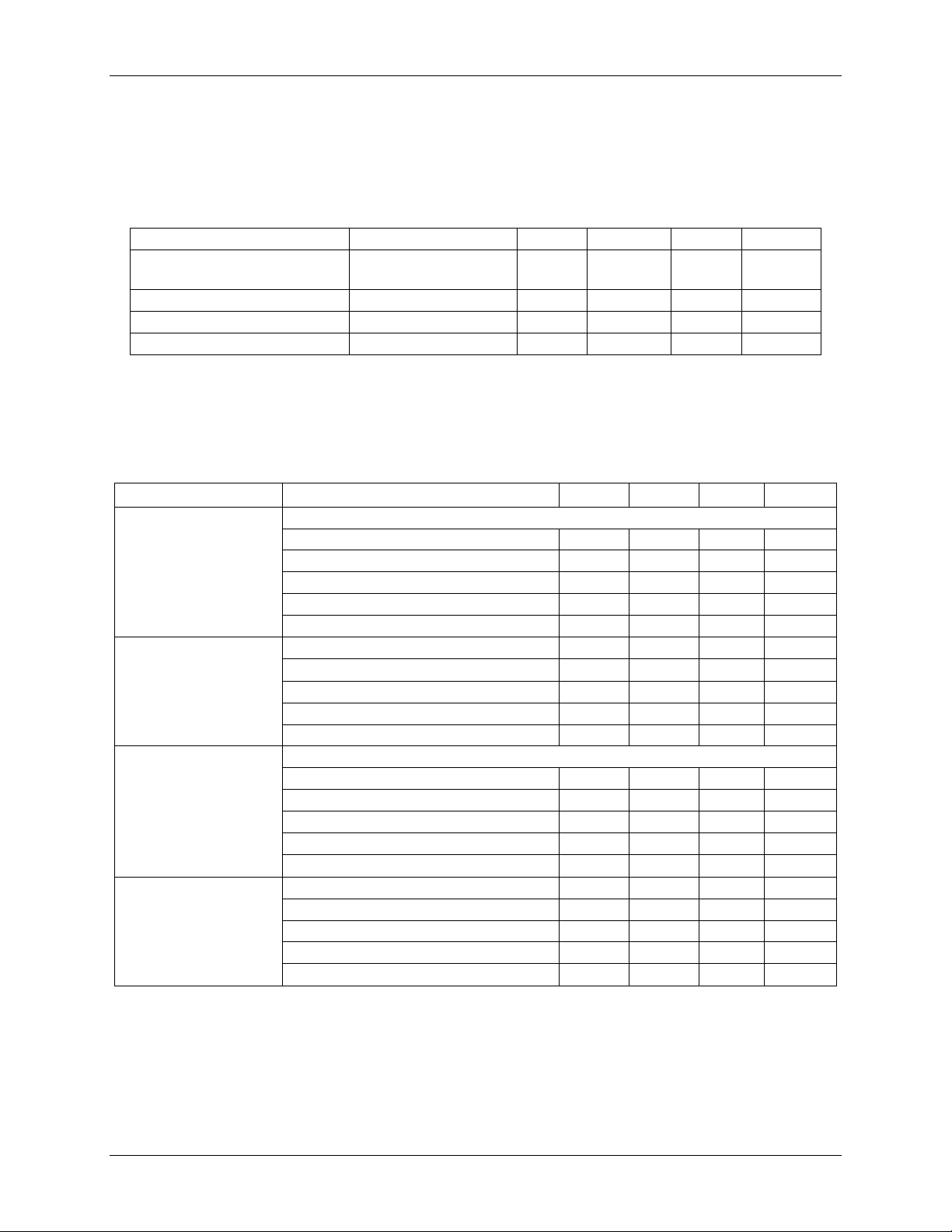

3.4 Analog Specifications

This s ection provides t he electrical characteri zations of the 73M1x66B analog circui try.

3.4.1 DC Sp ecifications

VBG i s to be connected to an external bypass c apacitor with a minimum value of 0.1 μF. This pin is not

intended for any other external use.

Table 13: Reference Voltage Specifications

Parameter Te st Condition Min Nom Max Units

VBG VDD=3.0 V – 3.6 V 0.9 1.19 1.4 V

VBG Noise 300 Hz – 3.3 kHz – -86 -80 dBm

600

VBG PSRR 300 Hz – 30 kHz 40 – – dB

20 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

U1 NJM2135

CD

1

-VIN

4

V+

6

GND

7

VOUT1

5

VOUT2

8

VREF1

2

VREF2

3

AOUT

VCC

VCC

R3 120K

+

C2

2.2uF

LS1

INTERVOX

AT-2308

C4

1uF

R2 120KR1 120K

C3

1uF

C1 0.1uF

Quantity

Reference

Part Description

Part

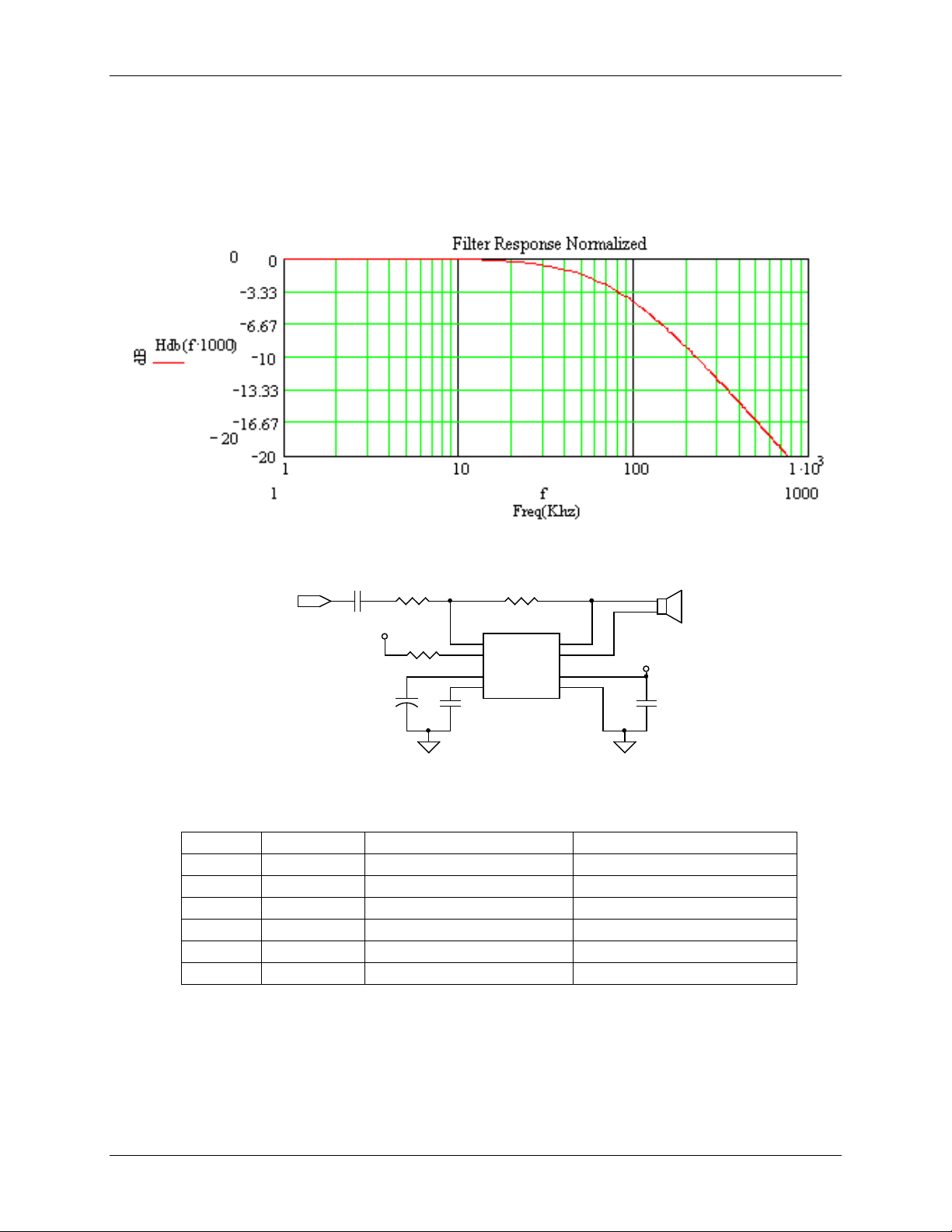

3.4.2 Call Progress Monitor

The Call Progress Monitor monitors activities on the line. The audio output contains both transmit and

receive data with a configurable level individually set by Register 10h.

Figure 10 shows the frequency response of the Call Progress Monitor Filter b ased upon the

characteristics of the devic e plus the external c ircuitry as shown.

Figure 10: Frequency Response of the Call Progress Monitor Filter

Figure 11: Demo Board Circuit Connecting AOUT to a Speaker

Table 14: Component Values for the Speaker Driver

1 C1 Ceramic cap acitor 0.1 μF

1 C2 Ceramic cap acitor 2.2 μF (optional)

2 C3 , C4 C er amic capacitor 1 μF

1 LS1 Sound transducer Speaker (Intervox)

3 R1 , R2 , R3 1/8 W resistor 0603 120 kΩ

1 U1 Audio amplifier NJM2135 (N ew Japan Radio)

All measurements are at the AO UT pin with CMVSEL= 0. Note that when CMVSEL=1, the peak signal at

AOU T is increas ed to approximately 1.11 Vpk.

Rev. 1.6 21

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

Parameter

Test Condition

Min

Nom

Max

Units

– – –

–

AOUT transm it THD

CMTXG=00

–

40 – dB

– – –

–

CMRXG=00

–

0.96

–

Vpk

–

–

–

–

–

–

–

–

–

–

Table 15: Call Progress Monitor Specification

AOUT for transmit

AOU T for receiv e

AOU T rec eive THD CMRXG=00

AOUT output

impedance

1 kHz full swing code (ATX)

CMRXG=11 (Mute)

Observe AOUT pi n

CMTXG=00 – 0.98 – Vpk

CMTXG=01 relat i v e

to CMTXG=00

CMTXG=10 relat i ve

to CMTXG=00

CMTXG=11 (Mute) – Mute – dB

1.0 Vpk, 1 kHz at the line or 0.5

Vpk at RXP/RXM with

RXG=10

CMTXG=11 (Mute)

Observe AOUT pi n

CMRXG=01 relative

to CMRXG=00

CMRXG=10 relative

to CMRXG=00

CMRXG=11 (Mute)

– -6 – dB

– -12 – dB

-6

-12

Mute

40

10

3.5 73M1x66 B Lin e-Side Electrical Specifications (73M1916)

dB

dB

dB

dB

kΩ

Table 16 li sts the absolute maximum r ating s for the li ne side. Operation outside these rating limits may

cause permanent damage to this device.

22 Rev. 1.6

Table 16: Line-Side Absolute Maximum Ratings

Parameter Min Max Unit

Pin input voltage from VPX to V NX -0.5 6.0 V

Pin input voltage (all ot her pins) to V N S -0.5 4.0 V

DS_1x66B_001 73M1866B/73M1966B Data Sheet

Parameter

Test Condition

Min

Nom

Max

Units

VBG noise

300 Hz – 3.3 kHz

–

-86*

-80

dBm

VBG PSRR

300 Hz – 30 kHz

40 – –

dB

DCIV=01

0.83

0.92

1.00

V

DCIV=10

1.08

1.16

1.24

V

*Noise

–

3.6 Reference and Regulation

Table 17 list s the VBG specifications. V BG shou ld be connected to an external bypass capacit or with a

minimum value of 0.1 μF. This pin is not intended for any other external use.

The following conditions apply: VPX=5 V; Barri er Powered Mode; Barrier Data Rate across the

Barrier=1.5 Mbps; VBG connected to 0.1 μF extern al cap.

Table 17: VBG Specifications

VBG See condit ions above. – 1.19 – V

600

VPS VPX=5.5 V – 3.15 – V

VPS PSRR VPX=4.5 V to 5.5 V – 40 – dB

3.7 DC Transfer Characteristics

Table 18 list s the maximum DC transmit levels. All tests are driven at pin DCI and measured at pin DCS.

DCEN=1. ILM=1.

Table 18: Maximu m DC Tr an smit Lev el s

Parameter Test Condition Min Nom Max Units

V

DCON

(DC "On" Voltage)

With ENAC=0 DCIV=XX 0.20 0.26 0.30 V

DC Gain V

I

bef or e ILIM ILM=1 V

DCI

I

after ILIM ILM=1 V

DCI

Delta V

Delta I

DCS

DCI

DCIV=00 0.62 0.69 0.78 V

DCIV=11 1.32 1.42 1.53 V

DCON<VDCI

8.2∗45mA< V

At the line with 300 Ω(ac) (0.15 - 4.0 kHz )

<0.4V+V

=0.28V+V

DCI

=0.44V+V

DCI

DCS

< 8.2∗60mA

-0.30 0 .0 +0.25 dB

DCON

DCON

DCON

– – 10 µA

20 – – µA

– 0.85 – mA/V

-85 -80 dBm

Rev. 1.6 23

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

–

–

–

–

–

–

ACZ=0001

–

0.211

–

Vpk

ACZ=0010

–

0.211

–

Vpk

–

–

–

–

–

–

–

–

–

–

–

–

–

–

ACZ=1010

–

0.223

–

Vpk

ACZ=1011

–

0.313

–

Vpk

–

–

–

–

–

–

–

–

–

–

–

–

Passband ripple

150 Hz – 3.3 kHz

-0.125

–

+0.125

dB

– – –

–

–

– 0 –

–

–

–

–

–

–

3.8 T r ansm it Pat h

Table 19 li st th e transmi t path characteristi cs. A pattern for a s inusoid of 1 kH z, full scal e ( code word of

+/- 32,767) from the 73M1x66B is forced and ACS is measured with R10=174 Ω. Unless stated

otherwise, test conditions are: ACZ=0000 (600 Ω termination), THEN=1, ATEN=1, DAA=01, TXBST=0,

sample rate=8kHz.

Table 19: Transmit Path

Parameter Test Condition Min Nom Max Units

Offset volt age

8 an d 16 kHz samp le rate

Tx gain, relative to

DAA[1:0]=01

AC swing

(1 kHz sinusoid)

8 an d 16 kHz samp le rate

50% 1’s density relative to 1.4

V common mode.

DAA=00 2.5 +3 3.5 dB

DAA=01 -0.5 0 0.5 dB

DAA=10 -4.5 -4 -3.5 dB

DAA=11 -8.5 -8 -7.5 dB

DAA=01

DAA=00

TXBST=1, DAA=xx

– 25 – mV

0.317

0.447

0.634

Vpk

Vpk

Vpk

ACZ=0011

ACZ=0100

ACZ=0101

ACZ=0110

ACZ=0111

ACZ=1000

ACZ=1001

ACZ=1100

ACZ=1101

ACZ=1110

ACZ=1111

Idle noise 300 Hz – 4 kHz

THD 300 Hz – 4 kHz

Intermod distort i on

1.0 kHz and 1.2 kHz

summed

Aliased image Fs +/- 1 kHz, relati ve t o 1 kHz

300 Hz – 4 kHz – -85 – dB

Gain relative to 1 kHz

0.5 kHz

1.0 kHz

2.0 kHz

3.3 kHz

0.200

0.254

0.220

0.171

0.194

0.222

0.205

0.208

0.211

0.285

0.235

-80

-80

0.17

0.193

-0.12

-75

Vpk

Vpk

Vpk

Vpk

Vpk

Vpk

Vpk

Vpk

Vpk

Vpk

Vpk

dBm

dB

dB

dB

dB

dB

dB

dB

24 Rev. 1.6

DS_1x66B_001 73M1866B/73M1966B Data Sheet

Parameter

Test Condition

Min

Nom

Max

Units

Intermod Dist 1.0 kH z

3.9 Rec ei v e Pat h

Table 20 li sts the receive pat h characteristics. All test inputs are driven through an AC coupling net work

shown in Figure 29. The receive bit stream is measu r ed at the DX pin. RXE N=1.

Table 20: R eceive Path

Differential input

resistance

Input level Differential, RX P/RXM – 1.1 1.16 Vpk

Input level Common mode, R XP/RXM – 1.37 – V

Overall sigma-delta A DC

modulation gain inclusive

of 73M1906B processing

Offset voltage R6=17.4 kΩ, R8=52.3 kΩ,

Rx gain

(See Note 1.)

Overal l r eceive

frequ ency response

inclusive of 73M1906B

processing

Idle noise 300 Hz – 4 kHz – -80 – dBm

THD RXG=00 – -85 – dB

Normalized t o VBG=1.19 V.

RXP/RXM – 1000 – kΩ

RXG=00

Divide Vrxp/m by PCM

Output

R9=21 kΩ.

See Figure 12.

RXG=00 -0.5 0 0.5 dB

RXG=01 2.5 3 3.5 dB

RXG=10 5.5 6 6.5 dB

RXG=11 8.5 9 9.5 dB

RXBST=1, RXG=00 18.3 19.3 20.3 dB

Relative to 1 kHz

0.3 kHz – 3.3 kHz -0.25 0 +0.25 dB

Fs (8 kHz) – -75 – dB

RXBST=1 – -60 –

– 47.3 – µV/bit

– 0 +/- 30 mV

– – –

–

and 1.2 kHz sum med

Crosstalk 1 Vpk 1 kHz sine wave at

CMRR RXP=RXM 1 Vpk 40 – – dB

PSRR -30 dBm signal at VPX in

On-Hook AC Impedance 300 Hz – 4 kHz, without EMI

Note 1: RXG controls the amount of gain or attenuation of the receiver analog gain element as specifi ed

in Table 20. The overall r eceiver c hann el gain has 6 dB of attenuat ion and th e net effect of t he

RXG bits on the receiver c hannel gain is defined i n Table 36.

Rev. 1.6 25

300 Hz – 4 kHz – -85 – dB

TXP; FFT on Rx ADC

samples, fir st four harmoni cs

reflec ted to the lin e.

Barrier Powered Mode;

300 Hz – 30 kHz.

caps.

– -90 – dBm

– – 40* dB

– 2 – MΩ

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

Parameter

Test Condition

Min

Nom

Max

Units

RLPNH=0 (12 kHz Notch)

–

–

–

–

–

–

–

Pass band Ripple (0. 3 kHz – 3.4 kHz)

–

+/- 0.15

–

dB

– 28.8 – μs

–

–

–

–

–

–

–

–

RLPNH=1 (16 kHz Notch)

–

–

–

–

3 kHz

–

+0.11

–

dB

16 kHz

-30

-50 – dB

–

–

–

–

–

–

–

–

–

–

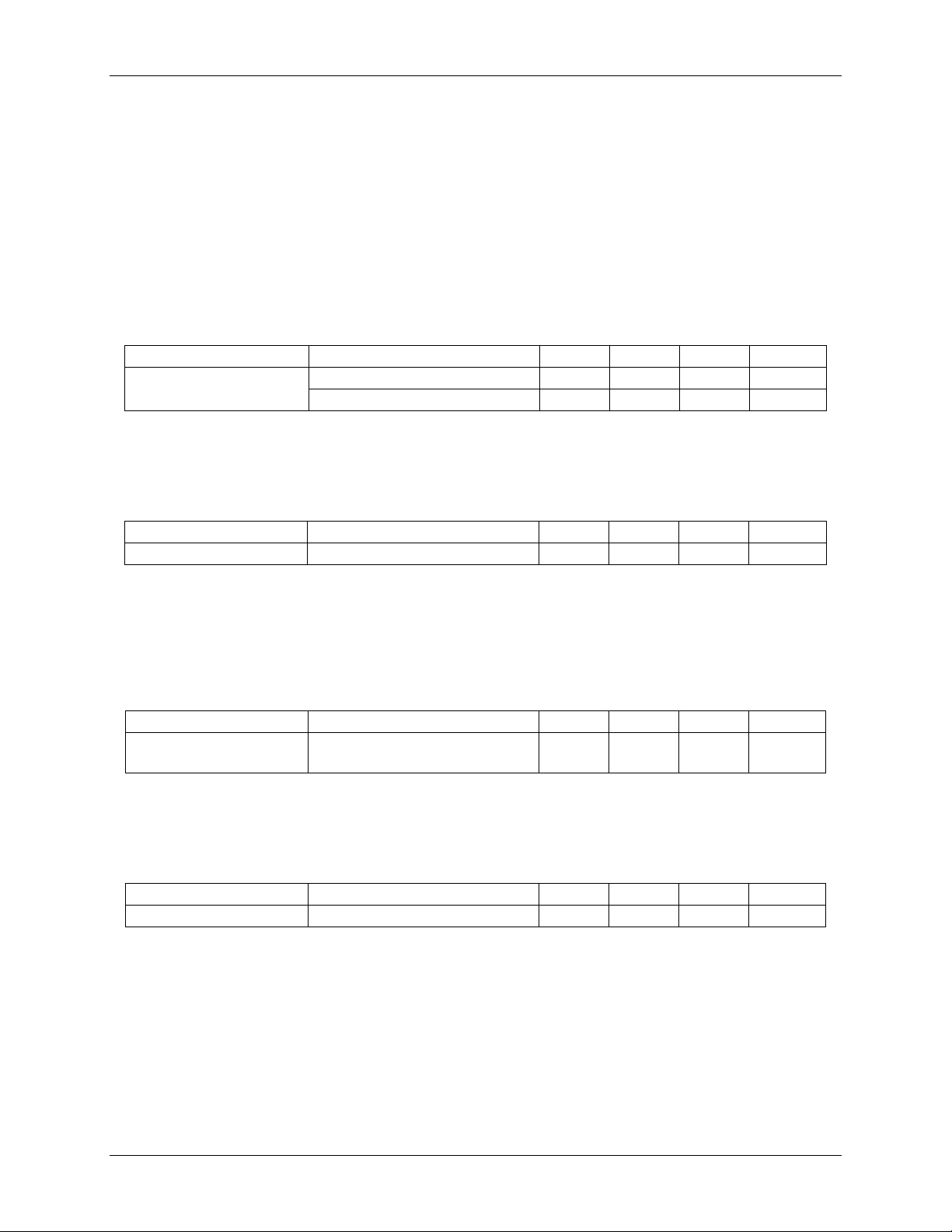

–

3.10 Transmit Hybrid Cancellation

Table 21 li sts the transmit hybrid cancellation characterist ics. Un less stated otherwise, test conditi ons

are: ACZ[3:0]=0000 (600 Ω termination), THEN=1, ATEN=1, DAA[1:0]=01, TXBST=0. TXM is externally

fed back into the 73M1916 to effect cancellation of transmit signal.

Table 21: Transmit Hybrid Cancellation Characteristics

Transmit hybrid cancellation Measure in

73M1906B

Offset volt ag e 50% 1’s dens i ty – 0 25 mV

AC swing 1 kHz sinusoid 1.00 1.05 1.10 Vpk

Idle noise 300 Hz – 4 kHz – -80 – dBm

– 20 – dB

3.11 Receive Notch Filter

Table 22 li sts the receive not ch filter charact eristics. A ll measurements taken with RLPNEN=1, TXEN= 0,

RXG=00, ATEN=1. RXP is driven with 1 Vpk signal.

Table 22: Receive Notch Filter

Parameter Test Condition Min Nom Max Unit

Magnitude respons e

Delay

300 Hz

1 kHz

3 kHz

12 kHz -30 -50

300 Hz

1 kHz

3 kHz

12 kHz

0.0

+0.03

+0.04

28.93

30.25

41.62

9.95

dB

dB

dB

dB

μs

μs

μs

μs

Magnitude respons e

Delay

26 Rev. 1.6

300 Hz

1 kHz

Pass band Ripple (0. 3 kHz – 3.4 kHz)

300 Hz

1 kHz

3 kHz

16 kHz

0.0

+0.04

+/- 0.15

30.53

30.66

31.93

42.26

4.74 – μs

dB

dB

dB

μs

μs

μs

μs

DS_1x66B_001 73M1866B/73M1966B Data Sheet

Parameter

Test Condition

Min

Nom

Max

Unit

3.12 Detectors

This s ection provides electrical charac teristics fo r the foll owing detector s:

• Over-Voltage.

• Over-Current.

• Under-Voltage.

• Over-Load.

3.12.1 Over-Voltage Detector

The values in Table 23 were measured between RGP and RG N .

Table 23: Over-voltage Detector

Parameter Test Condition Min Nom Max Unit

Over voltage levels OVDTH=0 0.52 0.6 0.68 V

OVDTH=1 0.59 0.7 0.77 V

3.12.2 Over-Current Detector

The values in Table 24 were measured in Barrier Powered Mode.

Table 24: Over-current Detector

Parameter Test Condition Min Nom Max Unit

Over current level Meas ured at DCS. 0.90 1.025 1.20 V

3.12.3 Under-Voltage Detector

The values in Table 25 were measured in Barrier Powered Mode. In the recommended schemati c (see

Figure 12), disconnect Q5 collector and connect to an exter nal power supply, VPE, through a 600 Ω

resistor.

Table 25: Under-voltage Detector

Parameter Test Condition Min Nom Max Unit

Under voltage detect Measure VPE when UVD is

detected as VPE is dec r eased.

– 7.5 – V

3.12.4 Over-Load Detector

The values in Table 26 were measured in Barrier Powered Mode.

Table 26: Over-load Detector

Over l oad level Measu r ed at DCI with 1 k H z. 0.6 0.75 0.9 Vpk

Rev. 1.6 27

R69

100K*

C14

15pF

INT\

SCLK

C41

220pF, 300V

SDO

SDI

VCC

SDITHRU

+

C8

4.7uF

R2

10M, 0805

R12 5.1K

R11

3K

C39

5.6nF

Q7

MMBTA42

1

3

2

R68

1M, 0805

C3 0.022uF, 200V

RST\

C48

0.1uF

Q6

BCP-56

1

23

4

DR

VPS

C49

100pF

C1 0.022uF, 200V

R8

52.3K, 1%

R9

21K, 1%

R5 8.2, 0805

R3

412K, 1%

U1 73M1916-20

OFH

4

VNX

5

SCP

6

MID

7

VPX

8

VBG

11

ACS

12

SRE

9

SRB

10

VNS

13

VPS

14

RXP

15

RXM

16

TXM

17

DCS

19

DCD

18

DCI

1

RGN

2

RGP

3

DCG

20

R6

17.4K, 1%

R66

1M, 0805

C38

0.1uF

C12

0.1uF

R4

100K, 1%

C7

4.7uF, 25V

U2 73M1906B-20

CS

1

AOUT

9

VPD

2

VPT

14

PCLKO

6

PCLKI

7

SCLK

20

DX

4

DR

3

FS

5

SDIT

16

SDO

18

SDI

17

VPA

10

VNA/VND

8

PRM

12

PRP

13

RST

15

VNT

11

INT

19

DX

AUDIO

C33

1nF

FSIO

IS OL ATION BARRIER

C31

0.1uF

CLKO

C35

220pF, 3KV

CLKI

-+

BR1

HD04

4

1

3

2

C36

220pF, 3KV

C37

0.01uF

TP15

VPS

1

TP14

OFH

1

R58 240

L1

2K Ohms @ 100 MHz

C9

0.22uF

T1

1 4

2 3

F1

TRF600-150

L2

2K Ohms @ 100 MHz

C10

0.22uF

TISP4290T3BJ

R10

174, 1%

Q3

MMBTA42

1

32

R65 200

Q4

MMBTA92

1

3 2

E1

P3100SBRP

Q5

MMBTA06

1

32

C24

NC (TBD as needed, 3KV)

C13

15pF

C26

1nF

CS\

SRE

SRB

C20

1nF

SCP

C43

1nF

NOTE: GND for C35 and

C36 should be on the host

side of the barrier

+

C4

10uF

VCC

C30

1nF

+

C21

3.3uF

C17

0.1uF

+

C45

3.3uF

VCC

TIP

RING

D1

MMSZ4710T1*

73 M1 866B/73M1966B D ata Sheet DS_1x66B_001

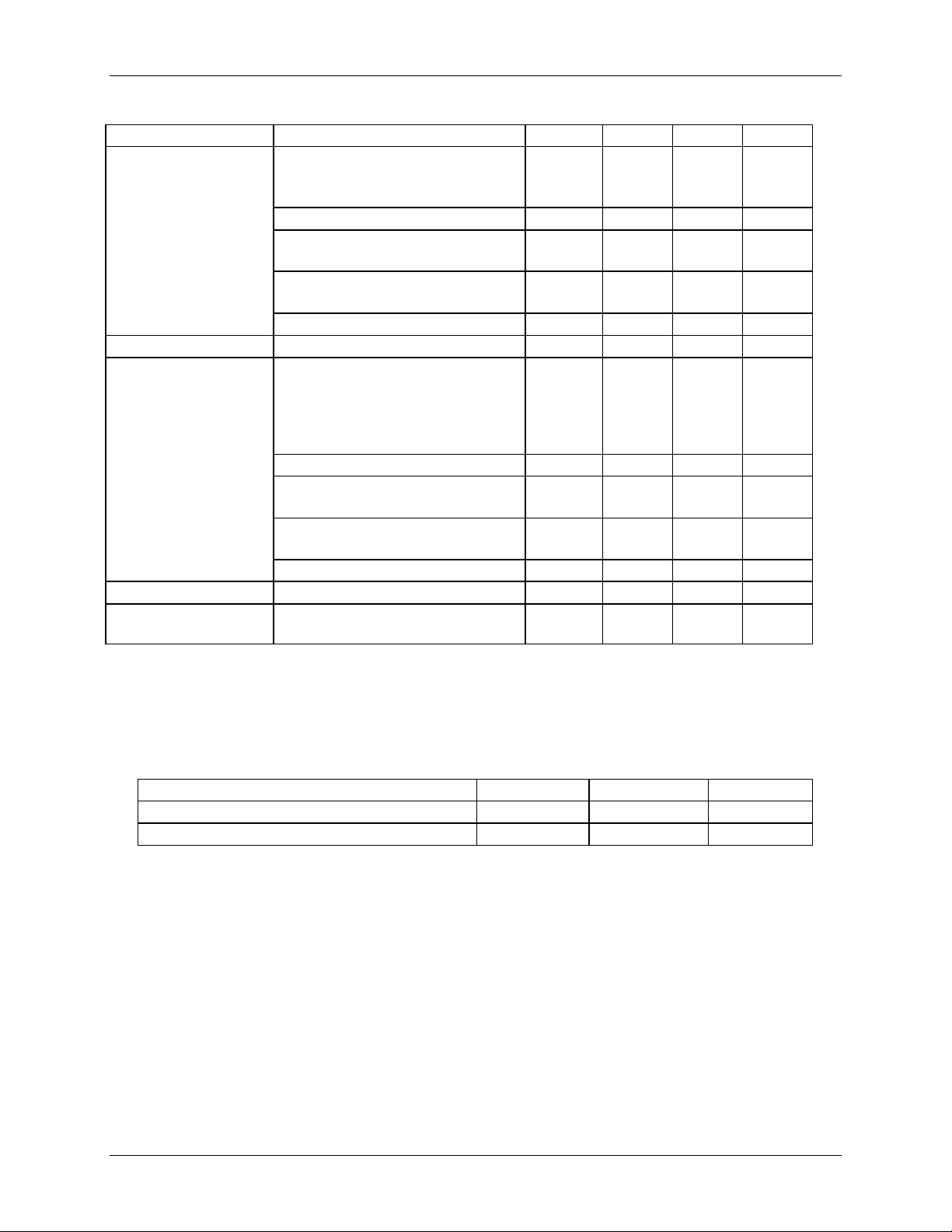

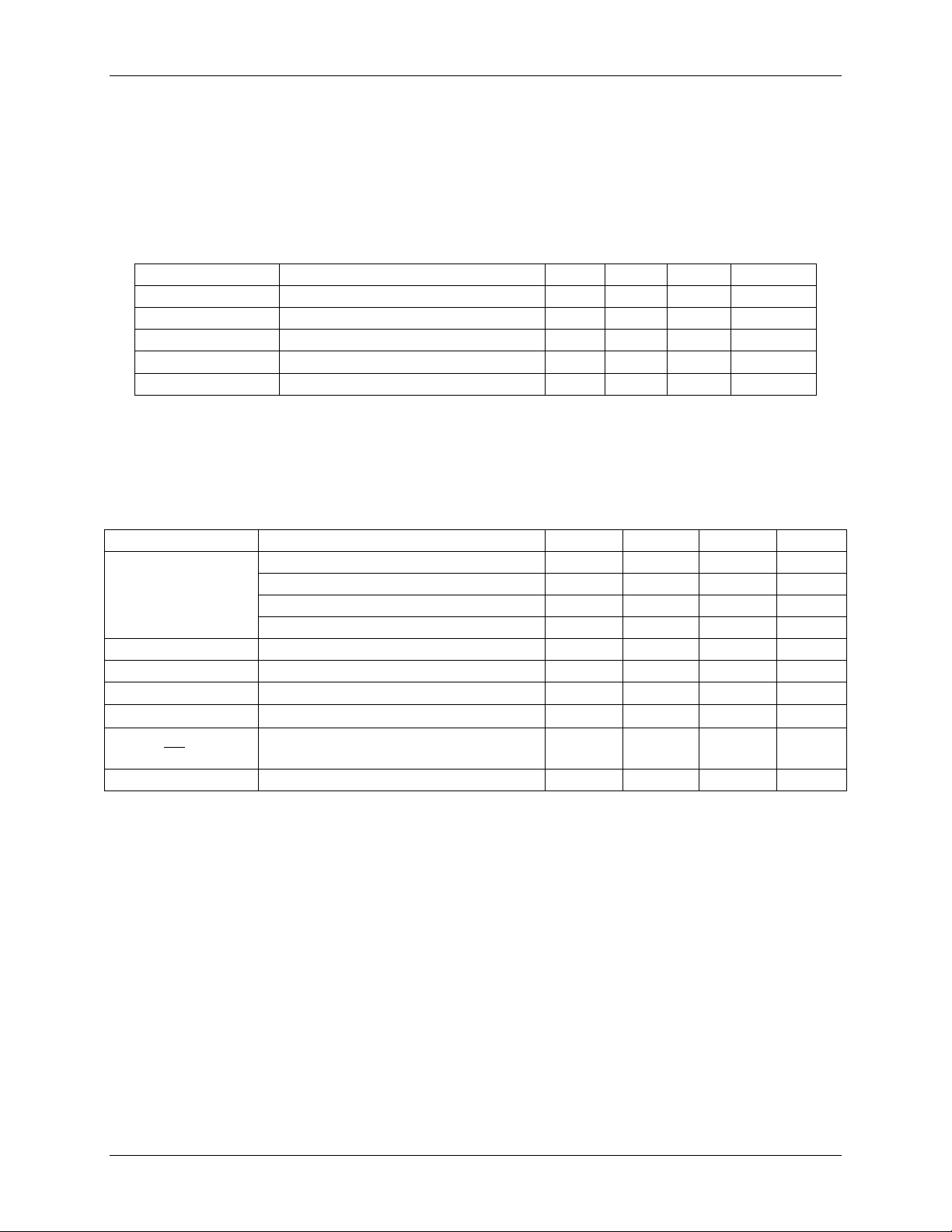

4 Applications Information

This s ection provides general u sage information for th e design and implement ation of the 73M1x66B.

4.1 Exa mple Schematic of the 73M1966B and 73M1866 B

Figure 12 shows a typical application schemat i c for the implementation of the 73M1966B. Figure 13 shows a typical application schematic for the

implement ation of the 73M1866B. Note that min or changes m ay oc cur to the reference material from tim e to time and the reader is encouraged to

contact Teridian for t he latest inform ation. For more information about schematic and layout design, s ee the 73M 1 86 6B/73M 19 6 6B S c hematic an d

Layout Guidelines.

28 Rev. 1.6

Figure 12: Recommended Circuit for the 73 M1 9 66B

DS_1x66B_001 73 M1 866B/73M1966B D ata Sheet

R6

17.4K, 1%

T1

Pulse Transf ormer

1

4

2 3

C1

0.022uF, 200V

C3

0.022uF, 200V

C43

1nF

C49

100pF

C35

220pF, 3k V

C30

1nF

R5

8.2

C33

1nF

R3 412K, 1%

R66

1M, 0805

VNS

VCC

C37

0.01uF

M aintain 2.5 mm Spacing Between

Line and Host Side Components

Isolation Bar r ier

C38

0.1uF

F1

TRF600-150

E1

P3100SBRP

C20

1nF

U1

73M1866B

DX

1

VPD

2

FS3PCLKO

4

VNA5PCLKI

6

AOUT

7

VPA8VNT

9

PRM

10

PRP

11

VPT

12

RST

13

SDIT

14

SDI

15

SDO

16

VND

17

INT

18

SCLK

19

CS

20

DR

21

SRE22SRB23VBG24ACS25VNS

26

VPS

27

RXP

28

RXM

29

TXM

30

DCD

31

DCS

32

DCG

33

DCI

34

RGN

35

RGP

36

OFH

37

M20PB

38

VNX

39

SCP

40

MID

41

VPX

42

RSTB

C26

1nF

SDITHRU

SPI OUT

SPI IN

SPI CLK

C39

5.6nF

C36

220pF, 3k V

VNS

SPI CSB

C9

0.22uF

PC M TX

C41

220pF, 300V

INTB

R11

3K

VCCVCCVCC

R68

1M, 0805

C17

0.1uF

PCM CLKIN

C13

15pF

C12

0.1uF

L1 2 k Ohm @100MHz

PCM CLKO

C14

15pF

VNS

VNS

AOUT

R2

10M

+

C45

3.3uF

+

C21

3.3uF

+

C8

4.7uF

RING

TIP

R12

5.1K

-+

BR1

HD04

4

1

3

2

R58 240

R9

21K, 1%

Q3

MMBTA42

1

32

Q6

BCP56

1

23

4

L2 2 k Ohm @100MHz

Q4

MMBTA92

1

3 2

R10

174, 1%

R4

100K, 1%

Q5

MMBTA06

1

3

2

PCM FS

C10

0.22uF

Q7

MMBTA42

1

32

C7

4.7uF, 25V

PCM RX

R65

200

NOTE: GND for C35 and C36 should be on

the host side of the barrier

C31

0.1uF

C48

0.1uF

R8

52.3K, 1%

C24

NC (as needed, 3KV)

+

C4

10uF

D1

MMSZ4710T1*

R69

100K*