Page 1

TDS 520B Mod CM

Digitizing Oscilloscope

Component Service Manual

070-9710-03

First Edition: May 30, 1996

Revised: February 26, 1998

Serial Numbers: B030000 and above

Warning

The servicing instructions are for use by qualified

personnel only. To avoid personal injury, do not

perform any servicing unless you are qualified to

do so. Refer to all safety summaries prior to

performing service.

Page 2

Copyright T ektronix, Inc. 1996. All rights reserved.

T ektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes

that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

T ektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070–1000

TEKTRONIX and TEK are registered trademarks of T ektronix, Inc.

Pursuant to DFARS 252.227-7013(e), Tektronix Inc. hereby grants to the Government a nonexclusive, paid-up license

throughout the world of the scope set forth therein for Government purposes for any commercial manuals provided by

T ektronix Inc. under this contract.

Page 3

WARRANTY

T ektronix warrants that this product will be free from defects in materials and workmanship for a period of three (3) years

from the date of shipment. If any such product proves defective during this warranty period, T ektronix, at its option, either

will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the

defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the

warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for

packaging and shipping the defective product to the service center designated by T ektronix, with shipping charges prepaid.

T ektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the

T ektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any

other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate

maintenance and care. T ektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting

from attempts by personnel other than T ektronix representatives to install, repair or service the product; b) to repair

damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been

modified or integrated with other products when the effect of such modification or integration increases the time or

difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY

OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY

IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

TEKTRONIX’ RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND

EXCLUSIVE REMEDY PROVIDED TO THE CUST OMER FOR BREACH OF THIS WARRANTY. TEKTRONIX

AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT , SPECIAL, INCIDENTAL, OR

CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS

ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Page 4

Page 5

Table of Contents

Theory of Operation

Maintenance

General Safety Summary v. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Service Safety Summary ix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Preface xi. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Logic Conventions 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Module Overview 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Detailed Circuit Description 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Acquisition System A10 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Processor System A11 1–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Display System A11 1–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Firmface A11 1–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Front Panel A12 1–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D1 Bus D14 1–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Low Voltage Power Supply A16 1–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Display Driver Board A20 1–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Maps 1–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Firmware Reprogramming 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Minimum Tool & Equipment List 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instructions 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage and Shipment Instructions 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instructions 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Specifications 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Replaceable Electrical Parts

Replaceable Electrical Parts 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Replaceable Mechanical Parts

Replaceable Mechanical parts 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diagrams and Circuit Board Illustrations

Diagrams and Circuit Board Illustrations 5–1. . . . . . . . . . . . . . . . . . . . . .

Symbols 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Component Values 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Graphic Items and Special Symbols Used in This Manual 5–1. . . . . . . . . . . . . . . . .

Component Locator Diagrams 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TDS 520B Mod CM Component Service Manual

i

Page 6

Table of Contents

List of Figures

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–1: PC & TDS Setup 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–2: Selecting the I/O system in the Main Menu 2–2. . . . . . . . . . .

Figure 2–3: Accessing the Protection Switch 2–5. . . . . . . . . . . . . . . . . . . .

Figure 4–1: Cabinet 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–2: Front 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–3: Chassis and rear 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–4: Circuit boards 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–5: LV Power Supply 4–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 4–6: Accessories 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–1: A10 Acquisition board front (section A) 5–2. . . . . . . . . . . . . .

Figure 5–2: A10 Acquisition board front (section B) 5–3. . . . . . . . . . . . . .

Figure 5–3: A10 Aquisition board front (section C) 5–4. . . . . . . . . . . . . . .

Figure 5–4: A10 Acquisition board front (section D) 5–5. . . . . . . . . . . . . .

Figure 5–5: A10 Acquisition board back (section A) 5–6. . . . . . . . . . . . . .

Figure 5–6: A10 Aquisition board back (section B) 5–7. . . . . . . . . . . . . . .

Figure 5–7: A10 Acquisition board back (section C) 5–8. . . . . . . . . . . . . .

Figure 5–8: A10 Acquisition board back (section D) 5–9. . . . . . . . . . . . . .

Figure 5–9: A10 Aquisition component locator 5–10. . . . . . . . . . . . . . . . . .

Figure 5–10: A10 Aquisition component locator (Cont.) 5–11. . . . . . . . . . .

Figure 5–11: A11 Processor board (section A) 5–66. . . . . . . . . . . . . . . . . . .

Figure 5–12: A11 Processor board (section B) 5–67. . . . . . . . . . . . . . . . . . .

Figure 5–13: A11 Processor board (section C) 5–68. . . . . . . . . . . . . . . . . . .

Figure 5–14: A11 Processor board (section D) 5–69. . . . . . . . . . . . . . . . . . .

Figure 5–15: A11 Processor component locator 5–70. . . . . . . . . . . . . . . . . .

Figure 5–16: A11 Processor component locator (Cont.) 5–71. . . . . . . . . . .

Figure 5–17: A12 Front Panel board front 5–126. . . . . . . . . . . . . . . . . . . . . .

Figure 5–18: A12 Front Panel board back 5–127. . . . . . . . . . . . . . . . . . . . . .

Figure 5–19: A12 component locator 5–128. . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–20: A14 D1 Bus board 5–136. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–21: A17 RBL Mother board (sections A, B) 5–138. . . . . . . . . . . . .

Figure 5–22: A17 RLB Mother board (sections C, D) 5–139. . . . . . . . . . . . .

Figure 5–23: A17 RLB Mother component locator 5–140. . . . . . . . . . . . . . .

ii

TDS 520B Mod CM Component Service Manual

Page 7

Table of Contents

Figure 5–24: A18 TBL Secondary Monitor board 5–146. . . . . . . . . . . . . . . .

Figure 5–25: A20 CRT Driver board 5–150. . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 5–26: A20 component locator 5–151. . . . . . . . . . . . . . . . . . . . . . . . . . .

TDS 520B Mod CM Component Service Manual

iii

Page 8

Table of Contents

List of Tables

Table 1-1: Relay Driver Control Data (CD) Bit Pattern 1-6..........

Table 1-2: Bandwidth Limit Selection Bits(Cont.) 1-8...............

Table 1-3: Gain Set Bits 1-8....................................

Table 1-4: Preamps to Track/Hold Input 1-9......................

Table 1-5: Track/Hold Outputs to A/D Input 1-9...................

Table 1-6: Preamps to Track/Hold Input 1-10......................

Table 1-7: 68020 Memory Map 1-37..............................

Table 1-8: Kernel Memory Map (0000 0000 to 00FF FFFF)

All 8 Bits Wide 1-38.........................................

Table 1-9: Bus Control Register (0040 0000 R/W) 1-38..............

Table 1-10: 7 Segment LED (0060 0000 Write Only) 1-39............

Table 1-11: DSP Interrupt Mask Register 1-40.....................

Table 1-12: DSP Interrupt Read Register 1-40.....................

Table 1-13: DSP Memory Map 1-41..............................

Table 1-14: D2MMIO Miscellaneous Register 1-42.................

Table 1-15: 68020 to DSP Instruction Memory Accesses 1-42.........

Table 1-16: Display Memory Map 1-43............................

Table 1-17: BDSACK Combinations For 68020 Memory Space

1-45......................................................

Table 1-18: A11 DRAM Processor/Display Wait State

Generation 1-46............................................

Table 1-19: A11 DRAM Processor/Display DUART Interface

Signals 1-47................................................

Table 1-20: A10 Acquisition Demultiplexer DB Memory Map 1-48....

Table 1-21: Device Interrupt Levels 1-49..........................

Table 1-22: Interrupt Mask Register 0900 0000 (R/W) 1-49..........

Table 1-23: Miscellaneous Register 0920 0000 (R/W) 1-50............

Table 1-24: Interrupt Read Register 1 0940 0000 (Read Only) 1-50....

Table 1-25: Interrupt Read Register 2 0960 0000 (Read Only) 1-51....

Table 1-26: Troubleshooting Procedure For LED Display 1-52........

Table 1-27: DIP Switch Options 1-53.............................

Table 1-28: A11 DRAM Processor/Display LED (DS1) 1-54..........

Table 2–1: Characteristics — Environmental 2–8. . . . . . . . . . . . . . . . . . .

iv

TDS 520B Mod CM Component Service Manual

Page 9

General Safety Summary

Review the following safety precautions to avoid injury and prevent damage to

this product or any products connected to it. To avoid potential hazards, use the

product only as specified.

Only qualified personnel should perform service procedures.

Injury Precautions

Use Proper Power Cord

Avoid Electric Overload

Ground the Product

Do Not Operate Without

Covers

Use Proper Fuse

Do Not Operate in

Wet/Damp Conditions

Do Not Operate in

Explosive Atmosphere

To avoid fire hazard, use only the power cord specified for this product.

To avoid electric shock or fire hazard, do not apply a voltage to a terminal that is

outside the range specified for that terminal.

This product is grounded through the grounding conductor of the power cord. To

avoid electric shock, the grounding conductor must be connected to earth

ground. Before making connections to the input or output terminals of the

product, ensure that the product is properly grounded.

To avoid electric shock or fire hazard, do not operate this product with covers or

panels removed.

To avoid fire hazard, use only the fuse type and rating specified for this product.

To avoid electric shock, do not operate this product in wet or damp conditions.

To avoid injury or fire hazard, do not operate this product in an explosive

atmosphere.

Keep Probe Surface Clean

To avoid electric shock and erroneous readings, keep probe surface clean.

Product Damage Precautions

Use Proper Power Source

TDS 520B Mod CM Component Service Manual

Do not operate this product from a power source that applies more than the

voltage specified.

v

Page 10

General Safety Summary

Use Proper Voltage

Setting

Provide Proper Ventilation

Do Not Operate With

Suspected Failures

Do Not Immerse in Liquids

Before applying power, ensure that the line selector is in the proper position for

the power source being used.

To prevent product overheating, provide proper ventilation.

If you suspect there is damage to this product, have it inspected by qualified

service personnel.

Clean the probe using only a damp cloth. Refer to cleaning instructions.

Safety Terms and Symbols

Terms in This Manual

These terms may appear in this manual:

WARNING. Warning statements identify conditions or practices that could result

in injury or loss of life.

Terms on the Product

CAUTION. Caution statements identify conditions or practices that could result in

damage to this product or other property.

These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the

marking.

WARNING indicates an injury hazard not immediately accessible as you read the

marking.

CAUTION indicates a hazard to property including the product.

vi

TDS 520B Mod CM Component Service Manual

Page 11

General Safety Summary

Symbols on the Product

The following symbols may appear on the product:

DANGER

High Voltage

Certifications and Compliances

CSA Certified Power

Cords

CSA Certification includes the products and power cords appropriate for use in

the North America power network. All other power cords supplied are approved

for the country of use.

Protective Ground

(Earth) T erminal

ATTENTION

Refer to

Manual

Double

Insulated

TDS 520B Mod CM Component Service Manual

vii

Page 12

General Safety Summary

viii

TDS 520B Mod CM Component Service Manual

Page 13

Service Safety Summary

Only qualified personnel should perform service procedures. Read this Service

Safety Summary and the General Safety Summary before performing any service

procedures.

Do Not Service Alone

Disconnect Power

Use Caution When

Servicing the CRT

Use Care When Servicing

With Power On

Do not perform internal service or adjustments of this product unless another

person capable of rendering first aid and resuscitation is present.

To avoid electric shock, disconnect the main power by means of the power cord

or, if provided, the power switch.

To avoid electric shock or injury, use extreme caution when handling the CRT.

Only qualified personnel familiar with CRT servicing procedures and precautions

should remove or install the CRT.

CRTs retain hazardous voltages for long periods of time after power is turned off.

Before attempting any servicing, discharge the CRT by shorting the anode to

chassis ground. When discharging the CRT, connect the discharge path to ground

and then the anode. Rough handling may cause the CRT to implode. Do not nick

or scratch the glass or subject it to undue pressure when removing or installing it.

When handling the CRT, wear safety goggles and heavy gloves for protection.

Dangerous voltages or currents may exist in this product. Disconnect power,

remove battery (if applicable), and disconnect test leads before removing

protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

X-Radiation

TDS 520B Mod CM Component Service Manual

To avoid x-radiation exposure, do not modify or otherwise alter the high-voltage

circuitry or the CRT enclosure. X-ray emissions generated within this product

have been sufficiently shielded.

ix

Page 14

Service Safety Summary

x

TDS 520B Mod CM Component Service Manual

Page 15

Preface

Manual Structure

This preface contains information needed to properly use this manual to service

the TDS 520B Digitizing Oscilloscope, as well as general information critical to

safe and effective servicing of this oscilloscope.

This manual is divided into sections, such as Theory of Operation and Parts

Lists. Further, it is divided into subsections, such as Product Description and

Removal and Installation Procedures.

Sections containing procedures also contain introductions to those procedures.

Be sure to read these introductions because they provide information needed to

do the service correctly and efficiently. The following is a brief description of

each manual section.

H Theory of Operation contains circuit descriptions that support general service

and fault isolation down to the module level.

H Electrical Parts List contains a statement referring you to Mechanical

Replaceable Parts, where both electrical and mechanical modules are listed.

Manual Conventions

Modules

H Mechanical Parts List includes a table of all replaceable modules, their

descriptions, and their Tektronix part numbers.

H Schematics contains schematic diagrams of the various circuit boards in the

TDS 520B.

H Dollies contains diagrams of the various circuit boards in the TDS 520B.

This manual uses certain conventions which you should become familiar with

before doing service.

Throughout this manual, any replaceable component, assembly, or part of these

Digitizing Oscilloscope is referred to generically as a module. In general, a

module is an assembly, like a circuit board, rather than a component, like a

resistor or an integrated circuit. Sometimes a single component is a module; for

example, each chassis part of the oscilloscope is a module.

TDS 520B Mod CM Component Service Manual

xi

Page 16

Preface

Safety

Symbols

Related Manuals

Symbols and terms related to safety appear in the Safety Summary found at the

beginning of this manual.

Besides the symbols related to safety, this manual uses the following symbols:

STOP. The stop labels information which must be read in order to correctly do

service and to avoid incorrectly using or applying service procedures.

The clock icon labels procedure steps which require a pause to wait for

the oscilloscope to complete some operation before you can continue.

Various icons such as the example icon at the left are used in procedures

to help identify certain readouts and menu functions on screen.

The TDS 520B Digitizing Oscilloscope, Option CM comes with the following

manuals:

TDS 520B, TDS 540B, TDS 620B, TDS 644B, TDS 680B, TDS 684B, TDS 724A,

TDS 744A, & 784A User Manual (Tektronix part number 070-9383-XX)

contains a tutorial to quickly show you how to operate the TDS 520B Digitizing

Oscilloscope and an in depth discussion of how to more completely use their

features. Applications are also discussed.

TDS 520B, TDS 540B, TDS 620B, TDS 644B, TDS 680B, TDS 684B, TDS 724A,

TDS 744A, & TDS 784A Reference (Tektronix part number 070-9382-XX)

contains a brief overview of oscilloscope operation.

TDS Family (400A, 500B, 600B, and 700A) Programmer Manual (Tektronix part

number 070-9556-XX) contains information for programmed operation via the

GPIB interface. Included are the complete command set, setup information, and

programming examples.

TDS 520B, TDS 540B, TDS 620B, TDS 644B, TDS 680B, TDS 684B, TDS 724A,

TDS 744A, & TDS 784A Technical Reference (Tektronix part number

070-9384-XX) contains performance verification procedures and specifications.

TDS 520B, TDS 540B, TDS 620B, TDS 644B, TDS 680B, TDS 684B, TDS 724A,

TDS 744A, & TDS 784A Service (Tektronix part number 070-9386-XX) contains

repair procedures to the modular level.

xii

TDS 520B Mod CM Component Service Manual

Page 17

Theory of Operation

Page 18

Page 19

Theory of Operation

This section describes the electrical operation of the TDS 520B Digitizing

Oscilloscope. First, an overview discussion, based on the block diagram, gives

an overall view of the module design. Next, a detailed circuit description, based

on the schematic diagrams in Section 5, gives a more detailed view. These

descriptions, together with the troubleshooting information in the TDS 500B,

600B, and 700A Service Manual, Tektronix part number 070-9386-01, should

enable a qualified technician with the appropriate test equipment to isolate a

problem to the appropriate level.

This section has three main parts:

H Logic Conventions describes how logic functions are discussed and

represented in this manual.

H Module Overview describes circuit operation from a functional-circuit block

perspective.

H Detailed Circuit Description provides detailed information about TDS

520B Digitizing Oscilloscope hardware with reference to the numbered

schematics in Section 3.

Logic Conventions

Module Overview

The Digitizing Oscilloscope contain many digital logic circuits. This manual

refers to these circuits with standard logic symbols and terms. Unless otherwise

stated, all logic functions are described using the positive-logic convention: the

more positive of the two logic levels is the high (1) state, and the more negative

level is the low (0) state. Signal states may also be described as “true” meaning

their active state or “false” meaning their nonactive state. The specific voltages

that constitute a high or low state vary among the electronic devices.

Active-low signals are indicated by a tilde prefixed to the signal name

(~RESET). Signal names are considered to be either active-high, active-low, or

to have both active-high and active-low states.

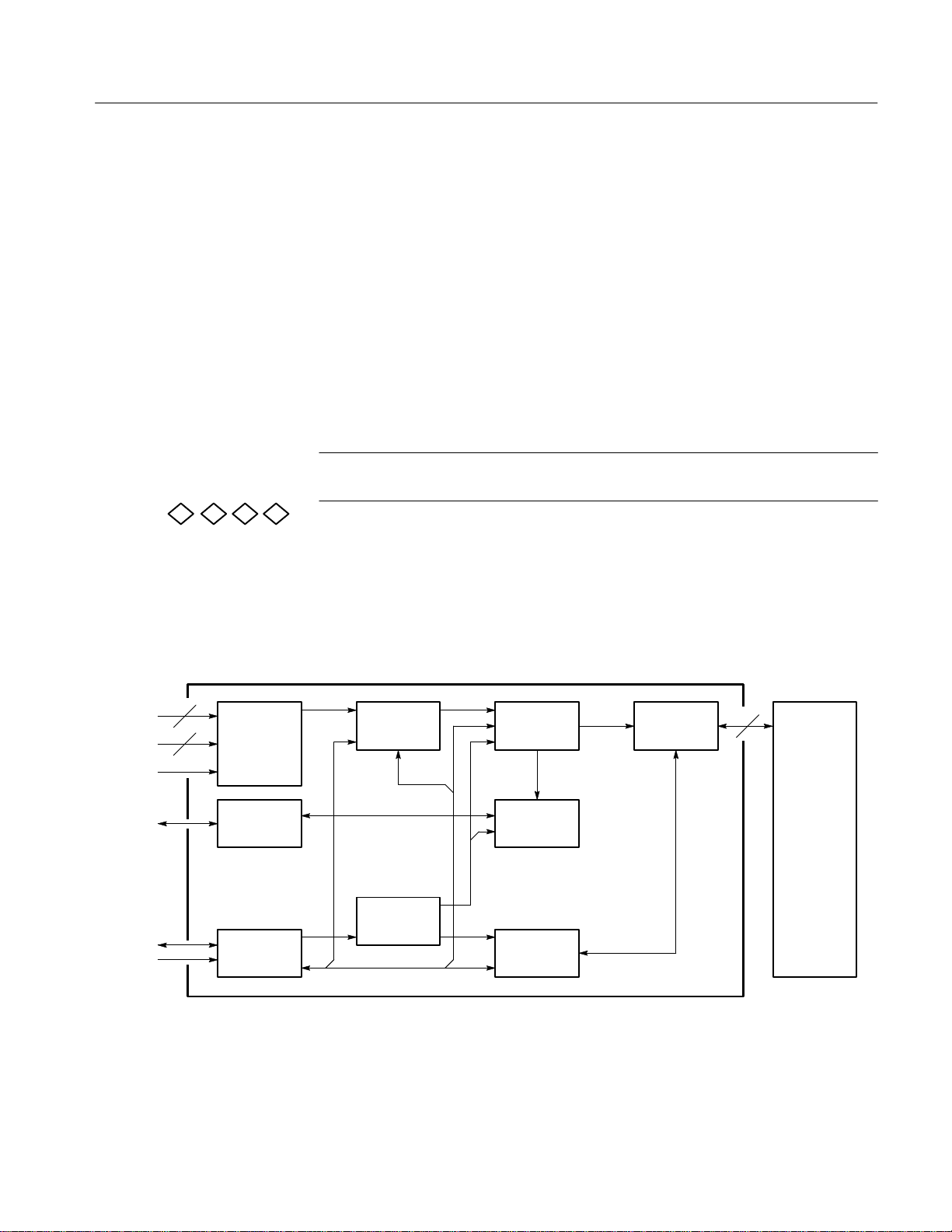

This module overview describes the basic operation of each functional circuit

block as shown in Diagram

. Figure 5-2.

TDS 520B Mod CM Component Service Manual

1–1

Page 20

Theory of Operation

General

Input Signal Path

The TDS 520B Digitizing Oscilloscope is a portable two-channel instrument.

Each channel provides a calibrated vertical scale factor.

A signal enters the oscilloscope through a probe connected to a BNC on the A10

Attenuator/Acquisition board.

Attenuators. Circuitry in the attenuator selects the input coupling, termination,

and the attenuation factor. The processor system, by way of the acquisition

system, controls the attenuators. For example, if 50 input termination is

selected and the input is overloaded, the processor system switches the input to

the 1 M position.

Probe Coding Interface. Probe coding interface signals pass through the attenuator

portion of the A10 Attenuator/Acquisition to the acquisition system, where they

are sensed and controlled.

Acquisition System. The acquisition system amplifies the input signals, samples

them, converts them to digital signals, and controls the acquisition process under

direction of the processor system. The acquisition system includes the trigger,

acquisition timing, and acquisition mode generation and control circuitry.

D1 Bus. The acquisition system passes the digital values representing the

acquired waveform through the A14 D1 Bus to the A11 DRAM Processor/Display board. This happens after a waveform acquisition is complete if the digital

signal processor in the processor system requests the waveform.

Processor System. The processor system contains a 68020 microprocessor that

controls the entire instrument. This system also includes the firmware and a

GPIB interface. You can reprogram the firmware from a remote controller using

the GPIB and an external software package.

The processor also includes a digital signal processor. This signal processor

processes each waveform as directed by the system processor. Waveforms and

any text to be displayed are passed on to the display system. The A11 DRAM

Processor/Display board contains both the processor and display systems.

Display System. Text and waveforms are processed by different parts of the

display circuitry. The display system sends the text and waveform information to

the tube assembly as a video signal. The display system also generates and sends

vertical (VSYNC) and horizontal (HSYNC) sync signals to the tube assembly. A

VGA-compatible video output is at the rear of the TDS 520B.

1–2

TDS 520B Mod CM Component Service Manual

Page 21

Theory of Operation

Tube Assembly

Front Panel

Rear Panel

All information (waveforms, text, graticules, and pictographs) is displayed by

the A20 Display system. The A20 generates the high voltages necessary to drive

the display tube. It also contains the video amplifier, horizontal oscillator, and

the vertical and horizontal yoke driver circuitry.

The processor system sends instructions to and receives information from the

Front Panel Processor on the A12 Front Panel board. The Front Panel Processor

reads the front-panel switches and potentiometers. Any changes in their settings

are reported to the processor system. The Front Panel Processor also turns the

LEDs on and off and generates the bell signal.

Front-panel menu switches are also read by the Front Panel Processor. The

processor sends any changes in menu selections to the processor system. The

ON/STBY switch is one of the menu switches. However, it is not read by the

Front Panel Processor, but passes through the A12 Front Panel board and the

A11 DRAM Processor/Display board to the low voltage power supply.

The front panel also generates the probe compensation signals SIGNAL

and GND.

The GPIB connector provides access to stored waveforms, and allows external

control of the oscilloscope. Other rear panel connectors are the AUX TRIGGER

INPUT, MAIN and DELAYED TRIGGER OUTPUT, and a CHANNEL 3

SIGNAL OUTPUT.

Low Voltage Power Supply

Fan

You can make hardcopies on the GPIB port. If your TDS 520B has the optional

RS-232 and Centronics ports, you can also use those.

The low voltage power supply is a switching power converter with active power

factor control. It supplies power to all of the circuitry in the oscilloscope.

The principal POWER switch, located on the rear panel, controls all power to

the oscilloscope including the Low Voltage Power Supply. The ON/STBY

switch, located on the front panel, also controls all of the power to the oscilloscope except for part of the circuitry in the Low Voltage Power Supply.

The power supply sends a power fail (~PF) warning to the processor system if

the power is going down.

The fan provides forced air cooling for the oscilloscope. It connects to +25 V

from the Low Voltage Power Supply by way of the A11 DRAM Processor/Display module.

TDS 520B Mod CM Component Service Manual

1–3

Page 22

Theory of Operation

1–4

TDS 520B Mod CM Component Service Manual

Page 23

Detailed Circuit Description

This detailed circuit description describes the operation of the oscilloscope

circuitry shown in schematic diagrams in the Diagrams section. While reading

this description, refer to the block diagrams and the schematic diagrams in the

Diagrams section.

Acquisition System A10

The A10 Acquisition board amplifies, via the attenuator assembly, and acquires

the analog signal. The acquisition system converts the signal to digital and stores

it in acquisition memory. Acquisition and trigger control circuitry controls the

acquisition process. DSP and the 68020 monitor and control the overall system,

and transfer the acquired waveform to the display system.

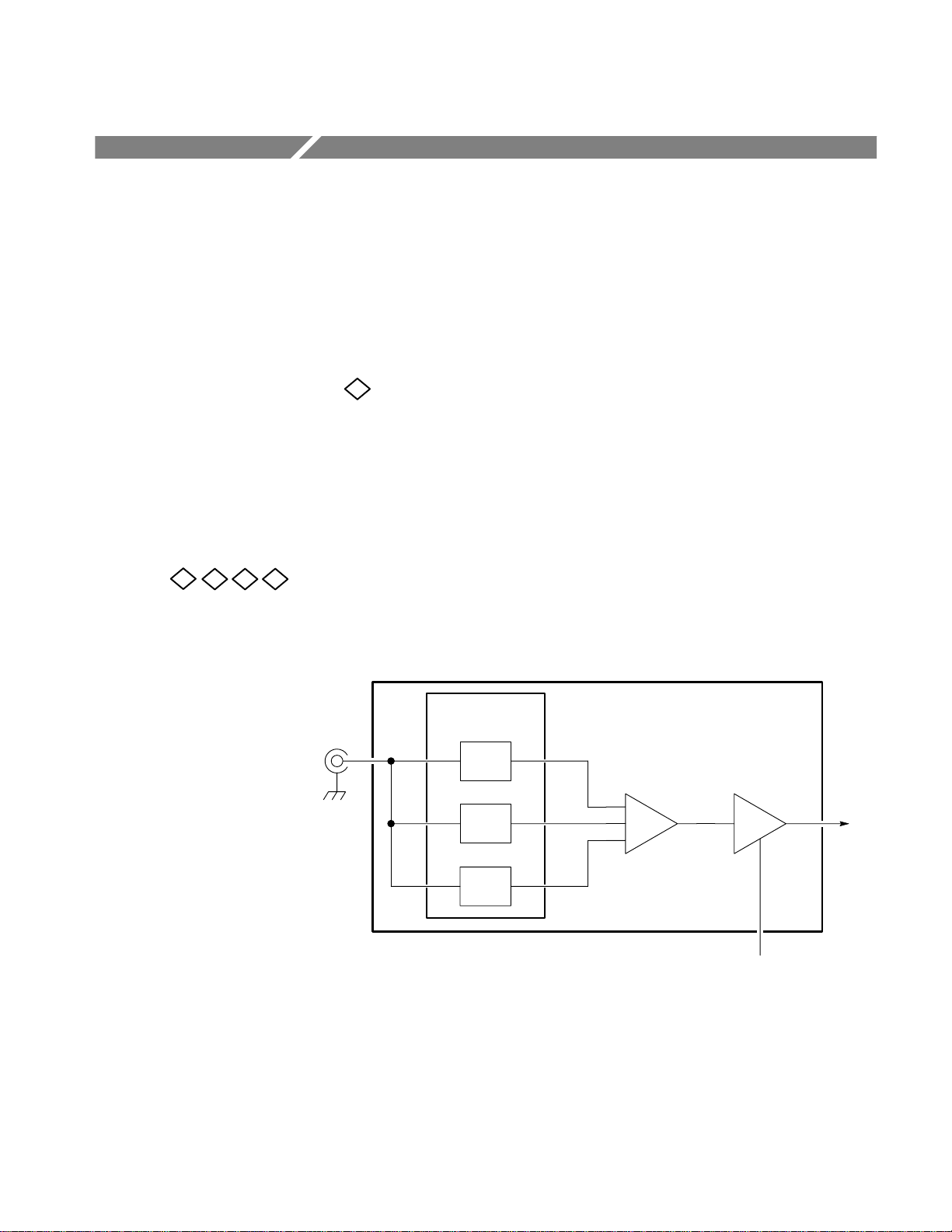

Attenuators A10

3

4 5 6

The attenuator assembly contains four attenuator hybrids, see Figure 1–1, and

four probe connectors. Each attenuator hybrid contains resistive dividers, an AC

coupling capacitor, relays, a 50 terminator, a buffer amplifier, and a preamp.

The outputs of the attenuator assembly (the preamp output) drive the track and

hold.

BNC

1

Resistive

dividers

1

Buffer Preamp

10

Figure 1–1: Attenuator hybrid

From here on the theory refers only to Ch4. The other channels work in similar

ways.

TDS 520B Mod CM Component Service Manual

100

Gain and

BW controls

1–5

Page 24

Detailed Circuit Description

Mode

The 68020 interprets user commands and initiates changes to the settings. The

Acquisition Processor monitors the input overload sense (OVLS1–OVLS4) and

the probe data (PRDATA1–PRDATA4) communication lines.

Each attenuator hybrid has five relays. One or more of the relays must be turned

on if a signal is to pass from the BNC to the output of the attenuator.

The AC/DC coupling relay couples the output of the BNC to the other relays in

the attenuator hybrid. For AC signals, the AC/DC coupling relay inserts a

coupling capacitor into the input signal path.

When active, the 1 M/50 relay terminates the input in 50 .

A relay driver (U1102, sheet 6) selects an attenuator’s attenuation factor by

connecting one of its relays to the input BNC, and connecting all of its other

relays to the ATTNCAL adjustment signal.

When ATTENSTB goes high, all attenuators enter their inactive state. Attenuator

clock CCATTN clocks control data (DIN, U1102, pin 3) from the processor

system into the attenuator Relay Driver. With a new pattern in the Relay Driver,

the processor system sets ATTENSTB low, enabling the attenuators.

The serial data line (DIN, U1102, pin 3) comes from sheet 21, U1050, pin 27.

The strobe (ATTENSTB, U1102, pin 8) comes from sheet 21, U1050 pin 11

(SCLK2). The DOUT line (U1102, pin 6) feeds the shifted data to the Ch3 relay

driver, where it becomes DIN for Ch3 (U1202, pin 3). This continues until Ch1.

After Ch1, the DOUT pin (sheet 3, U1402, pin 6) is sent back to sheet 21,

U1050, pin 6. By feeding the serial data back to the control IC (U1050), the

system can perform diagnostics on the serial data path.

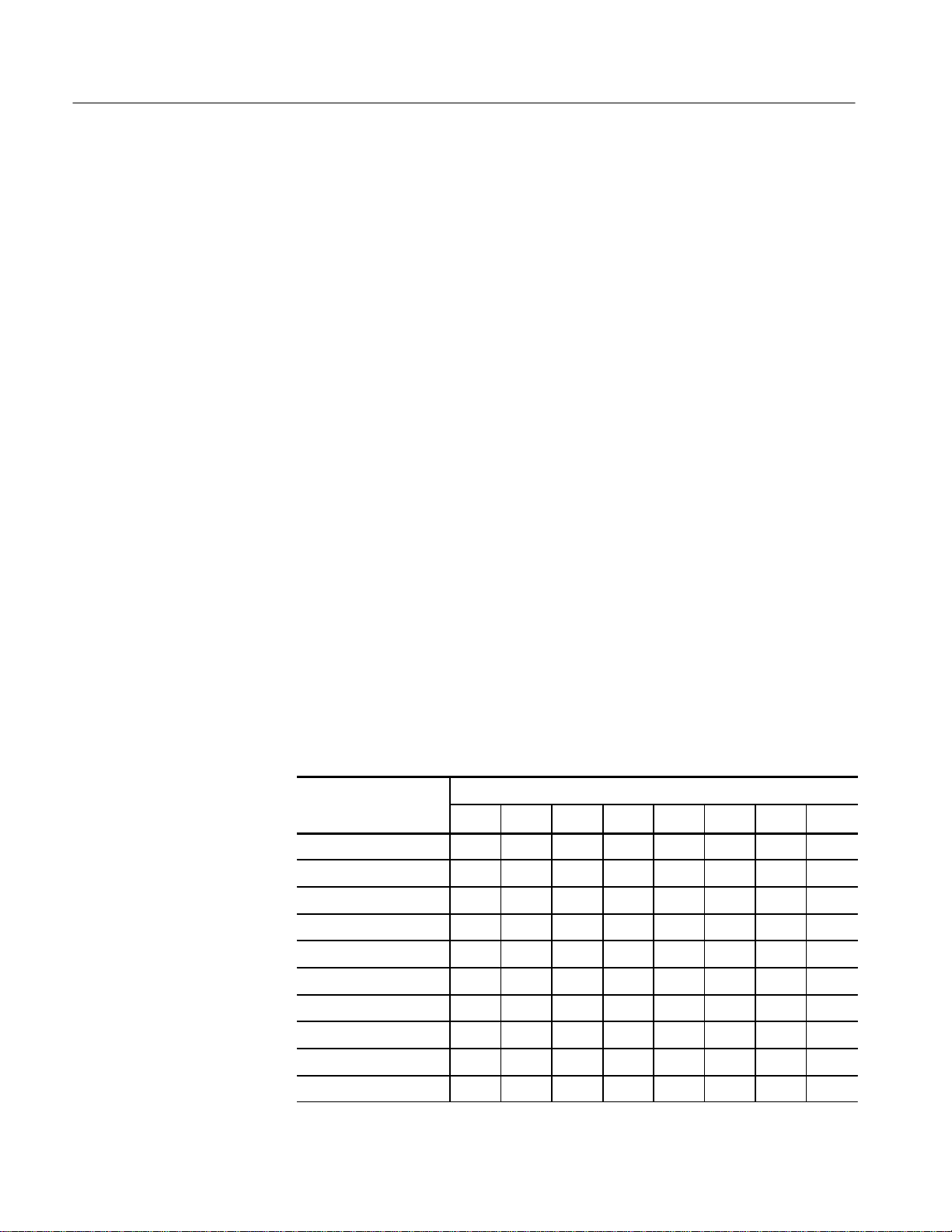

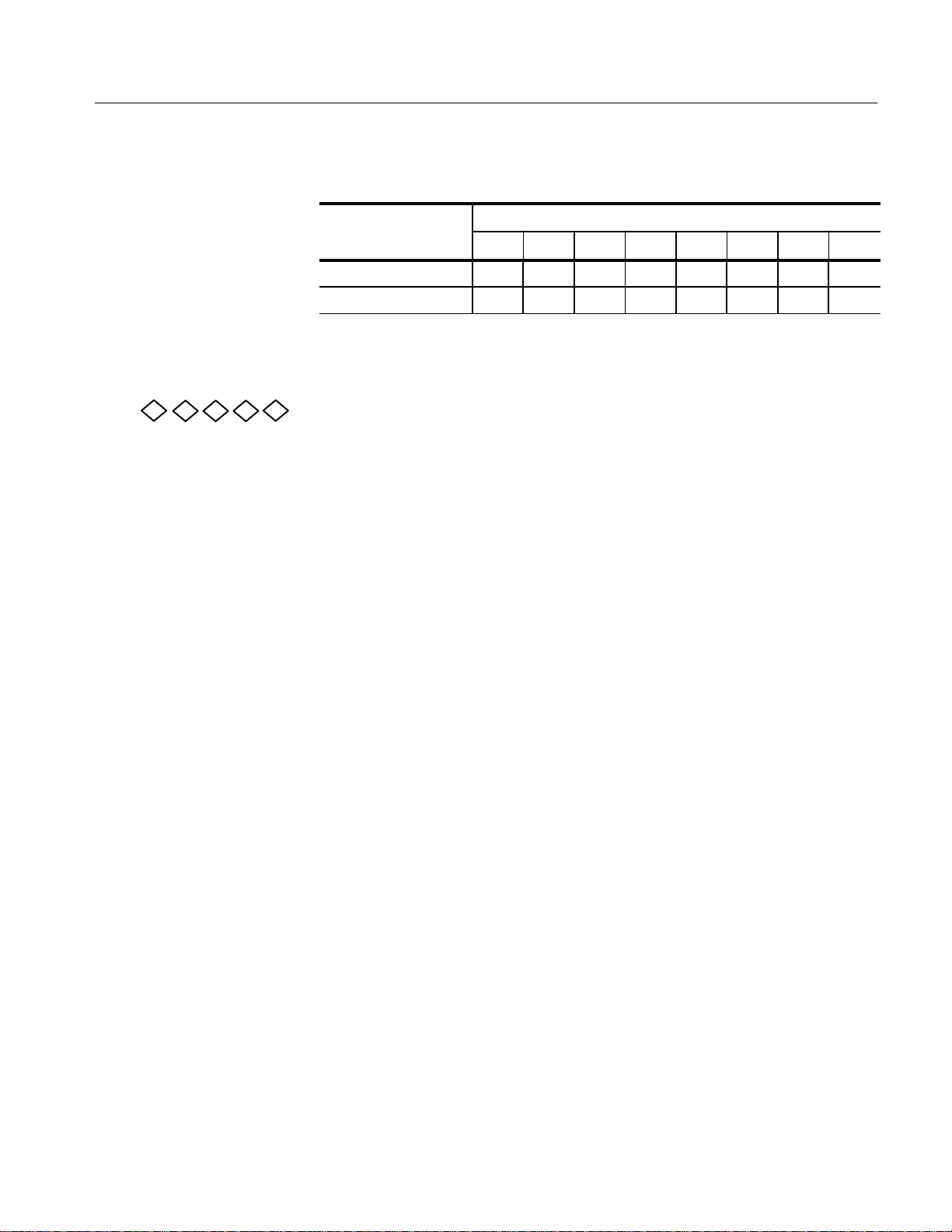

T able 1–1: Relay Driver Control Data (CD) Bit Pattern

Bit

7 6 2 8 5 4 1 3

AC 1 NC

DC 0 NC

50 NC

1 M NC

1X BNC NC

10X BNC NC

100X BNC NC

1

1

1

1

1

1 NC

0 NC

NC

NC

NC

1

1

1

1

1

NC

NC

1

1

1

1

NC

NC

NC

NC

1

1

1

1

NC

NC

NC

NC

1

1

1

1

NC

NC

NC

NC

1

1

1

1

NC

NC

NC

NC

1

1

1

1

1 0 0 1 0 0

0 1 0 0 1 0

0 0 1 0 0 1

NC

NC

NC

NC

1

1

1

1

1–6

OFF 0 0 0 0 0 0 0 1

1XCAL NC

10XCAL NC

1

1

NC

NC

1

0 0 0 1 0 0

1

0 0 0 0 1 0

TDS 520B Mod CM Component Service Manual

Page 25

Detailed Circuit Description

T able 1–1: Relay Driver Control Data (CD) Bit Pattern (Cont.)

Bit

Mode

Mode 31458267

100XCAL NC

INACTIVE 0 0 0 0 0 0 0 0

1

NC equals no change.

1

NC

1

0 0 0 0 0 1

Preamps A10

3

4 5 6

Since the preamp circuitry for each preamp is similar, only the circuitry for

Preamp 4 is described. Preamp 4 provides gain switching, bandwidth limit

7

filters, and outputs for the display, trigger, and other signal paths.

The system processor controls the Preamp 4 functions. It sends commands over

serial data line.

The Analog DAC Control system provides DC voltage signals that set the

Preamp offset. The Acquisition Processor (U600) stores the digital values of

each of the voltage levels in digital-to-analog converter (DAC) U900. The

Acquisition Processor transfers each voltage through DAC Multiplexer U934 to

Preamp 4. Preamp variable gain, HF adjust, fine offset and balance controls are

controlled by the daculator (U904) which is controlled by the GTL (U1050) via

the serial data bus (SDOUT U1050).

Preamp 4 Control Buffers. (sheet 6) The Preamp 4 Control Buffers provide offset,

balance, variable gain, and high frequency compensation voltages for the

preamp.

The offset control voltage is sampled by U934 (sheet 26) and held on capacitor

C1101. U1405 buffers the hold voltage so it can be fed into the attenuator hybrid

and then to the preamp. Fine offset and balance controls do not need a hold cap

because they come from the daculator (U904) which internally holds the

voltages. Fine offset and balance are buffered by U1101 and then summed

together with offset. HF adjust and var gain are fed directly to the preamp from

the daculator (U904).

Preamp Control 4. U1403 and U1404 (sheet 7) are the serial in, parallel out shift

registers that load the preamp control bits. Serial data flows into U1403 pin 1

(from sheet 21, U1050, pin 27). The data is shifted into the registers by SCLK3

(U1403 and U1404, pin 8). SCLK3 comes from sheet 21, U1050, pin 12. Data

flows from the last bit of U1043 to the serial input pin of U1404 and then from

the last bit of U1404 back to sheet 21, U1050, pin 7 for diagnostic purposes.

There are three steps in the process of programming the preamps. First, 16 bits

are shifted into the two registers (U1403 and U1404) – only QA, QB, QC, QD,

and QE of each register will be used. The Ch1/Ch3 preamp strobe (sheet 3,

TDS 520B Mod CM Component Service Manual

1–7

Page 26

Detailed Circuit Description

JP1400, pin 112 and sheet 5, JP1200, pin 112) is strobed to latch the gain and

bandwidth bits into Ch1 and Ch3. This strobe pin comes from sheet 21, U1050,

pin 17. Next, 16 more bits are shifted in and again only the 10 bits mentioned

above are used. However, this time, the Ch2/Ch4 preamp strobe (sheet 4,

JP1400, pin 212 and sheet 6, JP1200, pin 212) is strobed to latch the gain and

bandwidth bits into Ch2 and Ch4. Finally, 16 more data bits are shifted in. These

are left there to set the output controls of all four channels.

Preamp 4. The preamps amplify the input voltage. Input signals come from the

attenuator. The nominal gain of each preamp is 1.05 (at 50 mV per division); the

gain of the attenuator is 0.95 (in 1X attenuation). The combined gain from BNC

connector to A/D Converter D is 1.00.

Preamp 4 is an integrated circuit containing:

H Two four-pole bandwidth-limit filters: 20 MHz and 250 MHz. Inputs B0–B1

control the bandwidth of Preamp 4. See Table 1–2.

H Six gain settings of 1 mV, 2 mV, 5 mV, 10 mV, 20 mV, and 50 mV per

division (see Table 1–3). Inputs G0–G2 control the gain of Preamp 4.

H High-frequency adjust inputs.

H A variable gain control input which linearly adjusts the overall gain. The

gain is zero at –1 V and maximum at +1 V.

H Three separate differential outputs that can be turned on or off using the

output enable control signals (out1en, out2en, out3en). The inv controls are

left at 0.

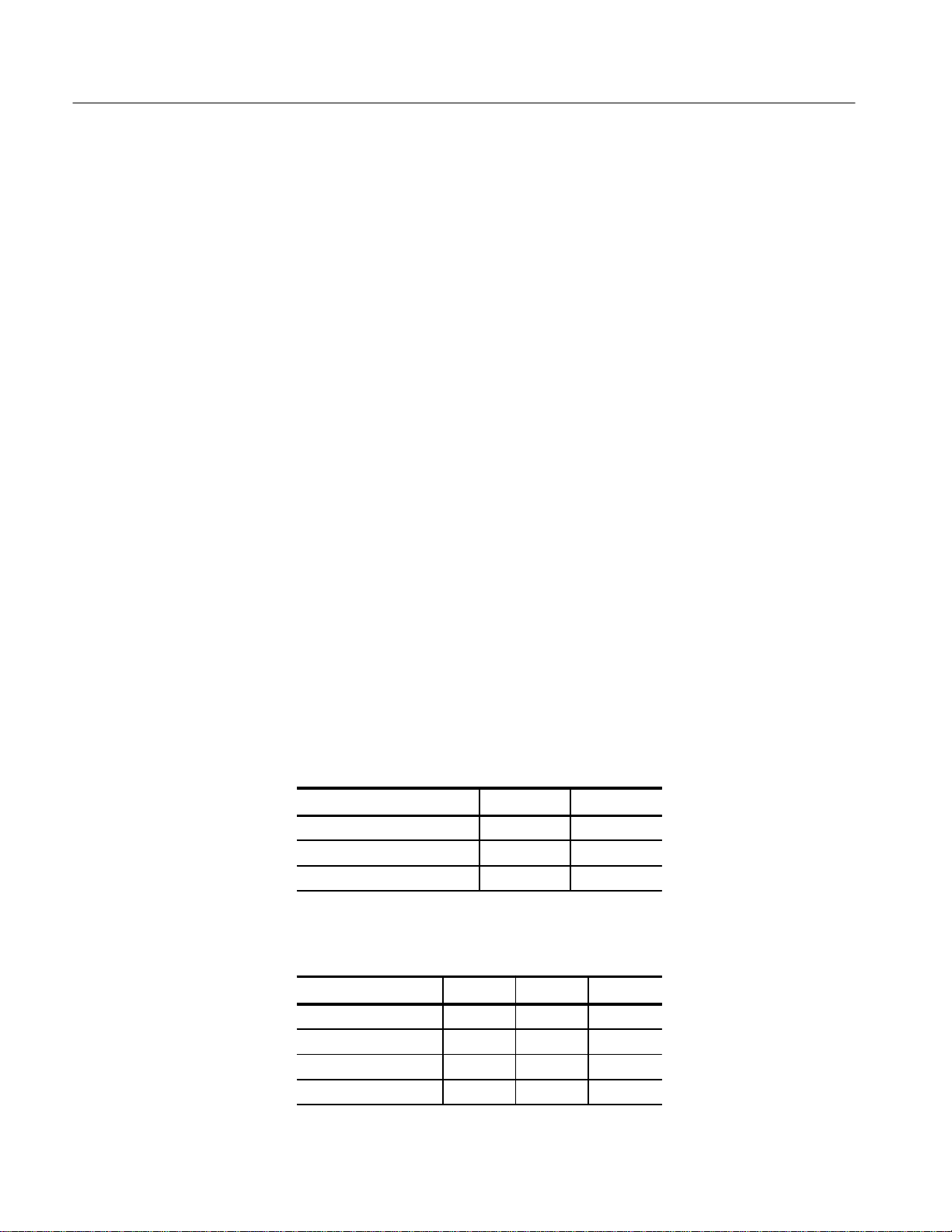

T able 1–2: Bandwidth Limit Selection Bits(Cont.)

Bandwidth B1 B0

20 MHz 0 0

250 MHz 0 1

Maximum 1 X

T able 1–3: Gain Set Bits

Gain Setting G2 G1 G0

1 mV 0 0 0

2 mV 0 0 1

5 mV 0 1 0

10 mV 0 1 1

1–8

TDS 520B Mod CM Component Service Manual

Page 27

T able 1–3: Gain Set Bits (Cont.)

Gain Setting G0G1G2

20 mV 1 0 X

50 mV 1 1 X

Detailed Circuit Description

Track/Hold A10

8

The track/hold IC (U1250) samples the differential analog signals coming from

the preamps before sending them to the A/D converters. The A/D clocks are also

provided by the track/hold. The track/hold IC also provides all channel switching

necessary to facilitate 2–way and 4–way interleaving. There are 8 control bits

that are serially shifted into U1251 and parallel fed to the track/hold. The data

line (SDATA, U1251 pin 1) comes from sheet 21, U1050, pin 27. The data is fed

back (SDIAG1, U1251, pin 13) to U1050, pin 5 for diagnostic purposes). The

data is clocked in by U1251, pin 8 (which comes from sheet 21, U1050 pin 10.)

The differential analog signals coming from the preamps are labelled

DISP1+/DISP1– thru DISP4+/DISP4–. The differential clocks going to the A/D

converters are labelled CLKAH/CLKAL thru CLKDH/CLKDI. The differential

analog sampled signals going to the A/D converters are labelled AP+/AP–

through DP+/DP–. Note, from the top level block diagram, that the signals going

from the preamps to the A/D converters get crossed (see Tables 1–4, 1–5, and

1–6 to verify this).

T able 1–4: Preamps to Track/Hold Input

Track/Hold

Preamps

Ch1 DISP1

Ch2 DISP2

Ch3 DISP4 Ch3 and Ch4 cross here

Ch4 DISP3

Input

Comments

T able 1–5: Track/Hold Outputs to A/D Input

Track/Hold

Outputs

AP SIGB AP and BP cross here

BP SIGA

CP SIGC CP and DP are inactive on

DP SIGD

A/D Input Comments

TDS 520B Mod CM Component Service Manual

the TDS 520B and

TDS 724A

1–9

Page 28

Detailed Circuit Description

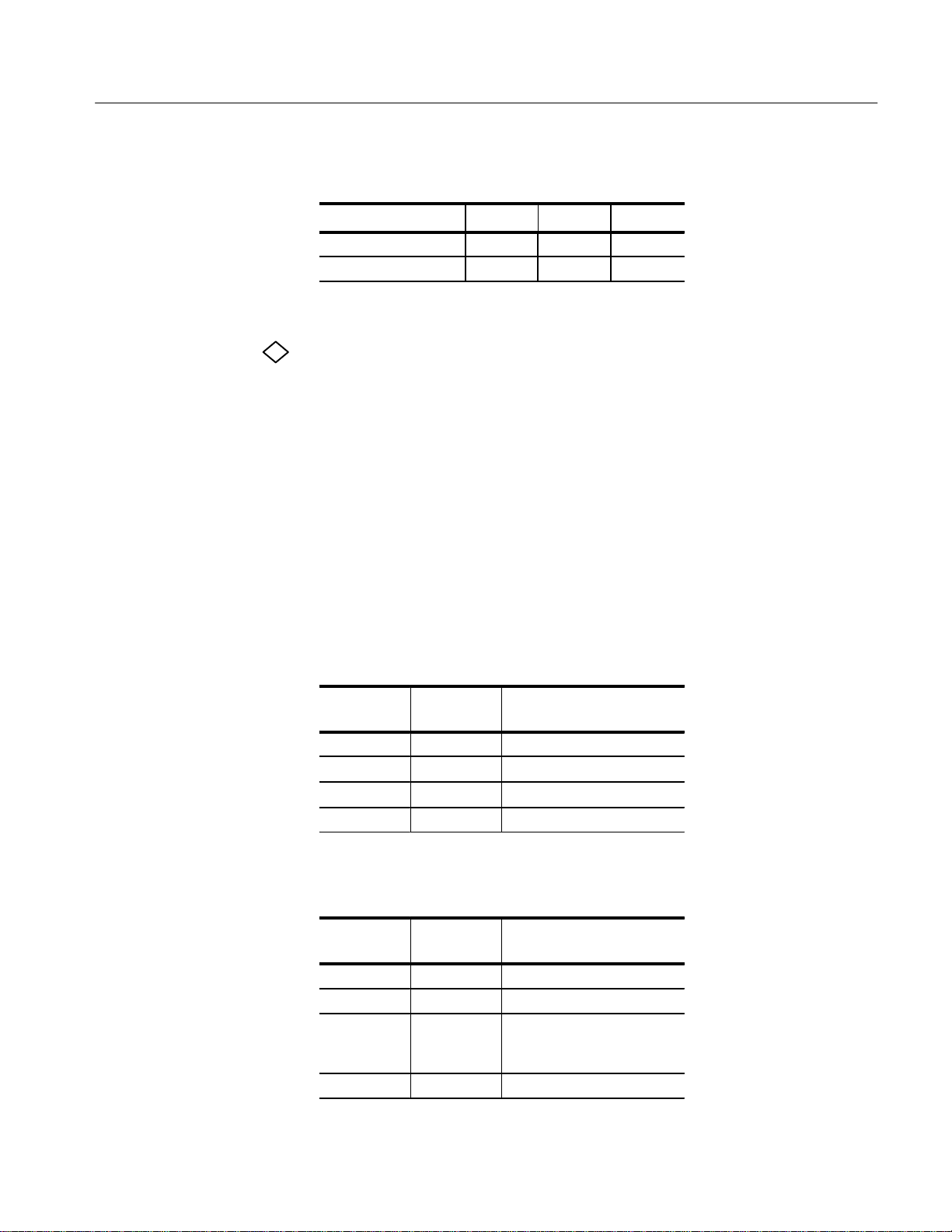

T able 1–6: Preamps to Track/Hold Input

Track/Hold

Clock

Outputs

CLKA CLKB

CLKB CLKA

CLKC CLKC CLKC and CLKD are inactive

CLKD CLKD

A/D Clock

Input

Comments

on the TDS 520B and

TDS 724A

In order to provide interleave capability, the Track/Hold must independently

adjust the delays of each of the sample clocks going to the A/D converters. These

are controlled by PHSA, PHSB, PHSC, and PHSD (pins 10, 111, 31, and 90

respectively of U1250) analog control voltages from the daculator (sheet 24,

U906). A three phase version of the 1GHz timebase clock is fed in through the

PHS1, PHS2, and PHS3 signals.

A/D Converters A10

1211109

NOTE. The TDS 520B and 724A only have A/D converts A and B. C and D are

not placed.

Since each A/D converter is similar, only the circuitry for A/D Converter D is

described. A/D Converter D (U700) converts the selected differential analog

input voltage to an 8-bit binary number. The analog input sensitivity is 2 mV per

digitizing level. Conversions occur at the 1 GHz clock rate (CLKD U700, pins

53 and 55). Even though conversions occur at this rate, data is output as two

differential 8-bit words (D0H/D0L–D7H/D7L and A0H/A0L–A7H/A7L) at a

500 MHz rate.

Pipes C and D (sheets 11 and 12) are not placed in the TDS 520B and TDS

724A.

Inputs. The A/D converter has one differential input (pins 60 and 62) fed from

the track/hold. Tables 1–4, 1–5, and 1–6 show which track/hold output connects

to which A/D converter. The 1 GHz differential input clocks from the track/hold

are fed into pins 53 and 55. Each side of the differential clock is 250 mV p–p

swing with the high level at 0 V.

Outputs. Outputs from the A/D Converter are differential, 500 mV digital swings

(peak to peak on each side.) The output resistance is 65 ohms. The two 8–bit 500

1–10

TDS 520B Mod CM Component Service Manual

Page 29

Detailed Circuit Description

MS/s streams become valid on alternate edges of the clock cycle (D is valid on

the rising edge, A is valid on the falling edge.)

Control. The A/D converter has two DC analog controls: OFFSET, which sets the

A/D offset, and VREF, which adjusts the gain. These controls come from a

daculator IC (U906, sheet 24). The VREF control voltage is preconditioned by

U701 so that it ranges from 1.56 V to 3.44 V.

Sampling of the analog input voltage occurs on the positive going transition of

convert clock (CLK0, pins 53 and 55). Digitized value is available after the 11th

subsequent clock cycle.

DMUX & Acquisition

Memory A10

ADATA_D

DDATA_D

ADCLK_D

8

8

16151413

Level shift

Trigger

interface

NOTE. The TDS 520B and 724A only have pipes A and B placed. They do not use

C and D.

Since the circuitry for each demultiplexer and acquisition memory is similar,

only the circuitry for pipe D Acquisition Memory is described. The demultiplexer is the time base and memory control system for the output of an A/D

converter. Each demultiplexer has an A/D data input (Ch4D and Ch4A),

acquisition memory output, DSP bus interface, and a trigger interface (see

Figure 1–2).

Demultiplexer Level shiftDecimators

Counters

64

Acquisition

memory

Decode

TriStar

interface

Figure 1–2: Demultiplexer Block Diagram

TDS 520B Mod CM Component Service Manual

Formatter

1–11

Page 30

Detailed Circuit Description

Demultiplexer D. Demultiplexer D has two operating modes. In acquire mode,

Demultiplexer D (U100) collects data from an A/D converter and writes the data

into Acquisition Memory D. In save mode, the DSP reads the acquired data from

Acquisition Memory D. The display system then processes and displays the data.

In acquire mode, Demultiplexer D (U100) gets its data (ADATA_DH0/ADATA_DL0 – ADATA_DH7/ADATA_DL7 and DDATA_DH0/DDATA_DL0 –

DDATA_DH7/DDATA_DL7) from A/D Converter D (U700) at a rate of two

new 8-bit samples every 2 ns. The input data sample is a 500 mV swing with

Von 4.2V. It latches the data on the falling edge of clock ADCLK_D and

converts it to CMOS levels. Data then passes to a demultiplexer at full speed, or

is decimated under program control.

The decimation mode determines the sample-rate. When the digital trigger is the

source of the trigger, the state of the decimators is latched at the trigger to assist

in point placement.

There are three decimation modes: normal, min/max, and hires:

H Normal (sub-sample) mode throws away samples between saved sample

points.

H Min/max mode saves the maximum and minimum samples over the

decimation interval.

H Hires mode gives extra resolution by averaging the samples, on a single-shot

basis, over the decimation interval.

An internal demultiplexer splits the two 8-bit data streams coming out of the

decimators into 16 8-bit data streams. The data streams are 2–way interleaved

resulting in a 64–bit data bus, with two memory chips on each byte. This results

in a 64-bit wide data word.

Demultiplexer D has three programmable counters that keep track of the number

of samples before the trigger, the number of samples after the trigger, and the

location in Acquisition Memory D where the trigger occurred. Before a trigger

occurs, the RUNM signal is asserted by the trigger logic (U1001, pin 146, sheet

20). After the trigger when the proper number of post–trigger samples have been

taken, RUNM is deasserted which stops the DMUX and causes it to interrupt the

processor.

During save mode, the DSP can access Acquisition Memory D. Memory mapped

I/O select MMIO accesses pin 74, the internal programming and status registers.

To further decode the MMIO select, the middle address bits are used as

sub-system selects.

1–12

Input MMIOA (U100, pin 73) acts as the sub-system selector for the memory

mapped I/O in the demultiplexers. To address the internal registers, DSP asserts

both MMIO and MMIOA.

TDS 520B Mod CM Component Service Manual

Page 31

Detailed Circuit Description

During DSP writes to Acquisition Memory D, circuitry in Demultiplexer D

aligns the byte-wide data for byte writes into Acquisition Memory D.

DSP can clock Demultiplexer D for test purposes. Diagnostics can switch in a

counter instead of A/D Converter D so that Demultiplexer D acquires a

predictable pseudorandom sequence.

Acquisition Memory D. During acquire mode, Demultiplexer D writes to

Acquisition Memory D when eight samples accumulate. The full 64 bits are

always written in parallel. Two address buses allow two sets of memory to share

the 64-bit data bus on alternate 8ns cycles.

Phase lock loop/clock

generator A10

17

Analog Triggers A10

18

The 1 GHz system timebase is generated from a VCO (centered around Q531)

that is phase locked to a 25 ppm, 25 MHz reference crystal oscillator. U510 is

the phase/frequency detector. The integrator is made from U502 and surrounding

components. The single–ended 1 GHz VCO output is converted to differential

(via delay lines) and fed to the trigger logic (U1001, sheet 20, pins 140 and 142).

The trigger logic divides the clock down to 25 MHz and feeds it back to the PLL

(from U1001, pins 12 and 13).

The analog triggers are free-running analog comparators with channel switching.

The following is described in terms of the Ch1 and Ch2 analog triggers:

The analog trigger comparator (U1551, sheet 18) is a channel switch and analog

comparator combination. Ch1 is differentially fed into IN1(H/L) (pin 5,4), CH2

is fed into IN2(H/L) (pin 41,41). The main trigger output is OUT11(H/L) (pins

20, 21) and the delay trigger output is OUT21(H/L) (pins 26, 25). The channel

switch allows either Ch1 or Ch2 to be the main or delay trigger event or both.

The comparators are after the channel switch, so the trigger level and hysteresis

controls are associated with the main delay trigger rather than Ch1 or Ch2

trigger. Trigger coupling is generated with U1560/U1561 filter circuits. Referring

to Ch1, AC coupled trigger occurs when C1556 is connected to ground via

U1556 and the analog trigger (U1551) is programmed to subtract this filter

output from the Ch1 trigger input signal. LF reject is achieved similarly except

C1556 is disconnected from ground. HF reject is like LF reject except that rather

than subtracting the CP1 input signal (pin 7) from the Ch1 trigger signal, the

CP1 input signal itself is used as the input. Noise reject is done by increasing the

trigger hysteresis via those analog control voltages (pins 11 and 35 for main and

delay hysteresis respectively).

U1552 does the same thing for Ch3 and Ch4. The EVNT1–4 outputs from

U1551 and U1552 are fed to the trigger logic IC (U1001, sheet 20), The trigger

logic chooses between Ch1/2 and Ch3/4 for main and delay trigger events.

U1551 and U1552 contain built–in shift registers for programming of the

channel switch and coupling modes. The serial data SDATA comes from U1050,

TDS 520B Mod CM Component Service Manual

1–13

Page 32

Detailed Circuit Description

sheet 21, pin 27. The data is fed serially into U1551, then U1552, and then back

to U1050, pin 91. The data is clocked into the shift registers with SCLK0

(U1551/U1552, pin 13) from sheet 21, U1050, pin 92. Once the shift registers

are loaded, the data is latched in by strobing DSTR0 (U1551/1552, pin 33).

DSTRB0 comes from sheet 21, U1050, pin 93.

Trigger Logic A10

20 21

Extended Trigger A10

22

Trigger Logic is the digital part of the trigger system. It is composed of two IC’s

referred to as U1001 and U1050. The circuitry has many clock generation and

triggering functions:

H Divides the 1 GHz VCOH/VCOL by 4 to get 250 MHz. The 250 MHz is

used to drive the time interpolators. It is further divided to operate the trigger

logic. It is also divided by 10 to generate the 25 MHz used by the scope’s

timebase PLL.

H Provides proper timing on the two resets (ACQRST1 and ACQRST2).

H Selects the trigger event.

H Puts the oscilloscope into posttrigger mode when the trigger is detected.

H Places the trigger point with respect to the data in memory.

H Provides trigger measurement functions.

H Provides part of the trigger holdoff and time interpolator functions.

The Extended Trigger (EXTL) is primarily used to trigger on the end of an event

pulse, qualified by the width of that pulse in time. Extended Trigger also allows

the trigger system to act as a flip-flop, as in state trigger.

1–14

The Extended Trigger responds to digital signals or “events” provided by the

Analog Triggers and the Trigger Logic. When a trigger condition is satisfied, the

Extended Trigger, (U1703, sheet 22) generates EEVNT.

A combination of analog ramps and the Trigger Logic define the reference pulse

widths. The analog ramps cover fast timing settings, while the Trigger Logic

counts pulse widths greater than 1 microsecond. For time references less than or

equal to this (where only the ramp is used), the Trigger Logic counter is disabled

and the outputs are set high.

Daculator-derived ramp currents at pins 10,11,12, 34, 35, and 36 define the

analog ramp times. The pins should always be within 25 mV of ground.

Each pulse width timer has two DAC/resistor networks. The slow range uses a

150 kW resistor for 30 ns to 1 ms. The fast range uses 4.75 kW for 2 ns to 28 ns.

TDS 520B Mod CM Component Service Manual

Page 33

Detailed Circuit Description

Time Interpolators A10

23

There are two time interpolators. One is for the main trigger, and the other is for

the delay trigger. The time interpolator allows the trigger system to determine the

time of occurence of a trigger event to the sub clock cycle resolution needed at

fast time/div settings.

A triple ramp technique is employed to perform the interpolation. When the

trigger event occurs, a large current is injected onto a capacitor generating what

is called the fast ramp. When the second subsequent clock occurs, the fast

current stops and the capacitor has a voltage that is proportional to the amount of

time from the trigger event to the next clock cycle plus a fixed offset. After the

fast current shuts off, a medium current starts to discharge the capacitor

generating what is called the medium ramp. This drains off most of the fixed

offset. At the end of the medium ramp, the medium current shuts off and is

replaced by a small current which slowly discharges the capacitor generating the

slow ramp. The time taken by the slow ramp to finish discharging the capacitor

is proportional to the initial time interval between the trigger event and following

clock edge. This system measures this much slower slow ramp time to obtain the

measurement.

For the main time interpolator (U1600, sheet 23), the fast ramp is set by R1640

and R1641. The slow and medium ramp currents are set by the control voltages

ISMAIN and IMMAIN respectively during SPC. The control voltages are

buffered by U1601 before being applied to the current setting resistors (R1639

and R1638).

Daculators A10

24

The trigger event is fed differentially into pins 10 and 11 of U1600 (MAUTH/L).

The differential clock is fed into pins 4 and 3 (TICLKMH/L). The timing ramps

are all internal to U1600 – an internal clock is generated that clocks a five-bit

counter for the duration of the slow timing ramp. The MSB of this counter

(CNTENMP/N, pins 44, 43 of U1600) is fed to U1050, sheet 21 where it clocks

a larger counter in that chip thus effectively concatenating the two counters to

make one counter. When the clock in U1600 stops, the counter is left with a

number proportional to the time from the trigger event to the next clock edge.

Once the system stores the trigger measurement, the trigger event line MAUT/L

is set low which resets the time interpolator.

The time interpolator also synchronizes the trigger event (U1600, pins 28, 27)

and returns it to U1001, sheet 20, pins 18 and 19. Operation for the delay time

interpolator is identical except it is in U1650, sheet 23 and operates on delay

trigger events.

Most of the analog control voltages are generated from the daculator ICs (U904,

U905, and U906). The daculators contain an internal 12–bit DAC, 1:16 analog

multiplexing circuit, and buffers. Serial data SDATA is shifted into the three

daculators (starting with U904) which are strung together daisy chain style. The

data serially shifts out of U906 (SDIAG4) back to U1050, sheet 21, pin 8.

SCLK4 clocks the serial shift registers (it comes from U1050, sheet 21, pin 14).

TDS 520B Mod CM Component Service Manual

1–15

Page 34

Detailed Circuit Description

DSTRB6 (from U1050, sheet 21, pin 25) causes the shifted data to take effect.

The data contains information on which daculator voltage to change and what

voltage to change it to. This is a total of 16 bits per daculator or 48 bits total.

Calibrator A10

25

Acq Processor A10

26

DAC and analog

MUXs A10

26

U962, U963, and U950 along with the supporting circuitry on that sheet form the

circuitry that generates the calibration voltages for Signal path Compensation

(SPC). U962 samples VDAC10 and stores that voltage on C956. VDAC10

comes from the DAC on sheet 26 (U900, pin 9). U963 selects an attenuated

version of this stored voltage for 1x, 10x, or 100x calibration. It can also select

ground for offset calibration. U962 and U963 are controlled from the trigger

logic (sheet 21, U1050, CVR0–6). The percent error of VDAC10 is characterized

at factory cal and stored along with all other calibration constants in NVRAM

(U1052 and U1055, sheet 21).

The system processor communicates commands to the Acquisition Processor

(U600) via the D1 Bus. The Acquisition Processor in turn controls the acquisition process. It controls the DAC and analog multiplexers that send control

voltages to the preamps. The Acquisition Processor also controls the probe

interface and senses internal temperature and timebase PLL lock.

U900 is a 12-bit DAC that is controlled by the acquisition processor. The analog

MUX (U934) stores the DAC output on hold capacitors. As the acquisition

processor changes the DAC output through a sequence of output voltages, the

analog multiplexor switches in sync with the DAC to store each voltage on a

different hold cap. There are 8 hold caps connected to U934 – four of them

(C939 C942) control probe offset, the other four (C1401, C1301, C1201, C1101

on sheets 3, 4, 5, and 6 respectively) control offset to the preamps. The output of

the DAC is reduced by a factor of four to ±2.5 V before being fed to U934. The

full ±10 V output of the DAC is also fed to U962 in the calibrator system on

sheet 25 where its held value is used for calibration voltage generation. The

acquisition processor controls the cycling of both the DAC and the analog MUX.

1–16

TDS 520B Mod CM Component Service Manual

Page 35

Detailed Circuit Description

Processor System A11

The processor system includes two processors: the 68020 (U1155) and U1097

the Digital Signal Processor (TriStar). The 68020 processor coordinates all

oscilloscope activities. It also directs the activities of the Acquisition Processor

and the Front Panel Processor via a parallel to serial interface using DUART

U1317. The Digital Signal Processor (DSP) manipulates acquisitions. It

performs tasks as directed by the 68020 processor and reports results back either

through interrupts or by using the FIFO (U1074). The 68020 has access to

everything on the DSP bus, allowing it to run diagnostics, retrieve waveforms,

pass data, and load DSP instruction memory.

Processor/Display Board

Connectors A11

2 3

Decode A11

4 5

All connectors for the A11 DRAM Processor/Display board are grouped together

on these schematics. Regulator U12 supplies power for the NVRAM write

enable circuitry. Connector J20 connects power to the fan.

The Decode circuitry decodes the 68020 memory space (U1055, U1056),

generates wait states, data transfer and size acknowledge signals U2001, byte

enables U2001, and the system ON/STBY signal.

Main Decode. The Main Decode. circuitry decodes the 68020 address space into

16 blocks of 16 Megabytes each. Table 1–7 shows the memory map for the

Processor System.

1

68020 Interrupts, Kernel

Registers, and

Decode A11

5

Wait State

. Dynamic bus sizing allows the 68020 to automatically determine

5

the size of a port on each access by using DSACK signals.

Wait states are generated either from the device or port being accessed.

Data transfer and size acknowledge signals ~DSACK0 and ~DSACK1 control

bus speed (by adding wait states) and dynamic bus sizing for circuitry that does

not generate its own data transfer and size acknowledge signals.

Byte Enable Decode

. Byte Enable Decoder prevents the 68020 from

5

overwriting data during writes to word and long-word ports.

The 68020 supports seven levels of auto-vectored interrupts. Level seven

auto-vector (non-maskable) interrupts are reserved for ~PF, an interrupt

indicating that power failure is imminent, and ~50OHMOVERLOAD, an

interrupt indicating an overload in the A15 Attenuator. Interrupts from other

modules are shared on the other 6 interrupt levels. Table 1–21 lists the device

assigned to each interrupt level, and the name of the interrupt signals.

TDS 520B Mod CM Component Service Manual

1–17

Page 36

Detailed Circuit Description

Interrupt Decode. Interrupt circuitry in U2000 decodes interrupts into the three

signals that notify the 68020 of an interrupt. The ENABLEINT from the Bus

Control Register in U2000 determines if only level seven and Kernel interrupts

are enabled, or if all interrupts are enabled. Because the Interrupt Read Registers

are outside the Kernel, in Kernel operation the 68020 must read from the

interrupting device itself to determine the source of the interrupt.

Interrupt Mask and Miscellaneous Registers. All interrupts other than level 7 are

maskable. By asserting the appropriate mask bit in the Interrupt Mask register

(see Table 1–22) for an interrupt, the 68020 can ignore that interrupt. The 68020

can still read the status of the interrupt using Interrupt Read Registers.

The 68020 processor writes to Miscellaneous Register to control system circuitry

and one interrupt mask (see Table 1–22). By reading Miscellaneous Registers,

the 68020 processor determines the status of the interrupt masks.

Clock Logic. Clock logic uses a 25 MHz clock to generate clocks for buss error

logic, GPIB, DUART.

Kernel CPU and

Control A11

5 6

DRAM Logic. DRAM logic generate address and control signals for DRAM.

Interrupt Read Registers. Since there is usually more than one interrupt per

priority level, the 68020 processor reads the Interrupt Read Registers to

determine which device caused the interrupt (see Tables 1–24 and 1–25).

At the start of power-up, the 68020 (U1155) disables as many subsystem buffers

as possible. This allows the 68020 processor to start execution with as small a

system as possible (the Kernel). As diagnostics progress, subsystems are turned

on and diagnosed one at a time.

CPU and Control. After the Kernel passes its power-up diagnostics, the firmware

enables the control bus buffer U1135. Gates U1001C, U1082B, and U1082D

generate the DSP read and write control signals ~ERDS and ~EWRS.

U2001

combine all data transfer and size acknowledge signals (DSACKs)

5

from circuitry throughout the system, and generate the actual data transfer and

size acknowledge signals.

Kernel Address Decode and Kernel Wait States

. To isolate the Kernel from the

5

rest of the system, the Kernel decodes its own address space using decoders

inside U2000. The DSACKS control bus speed and allow for dynamic bus sizing

(byte, word, or long word).

1–18

TDS 520B Mod CM Component Service Manual

Page 37

Detailed Circuit Description

Bus Control Register 5. The Bus Control Register contains system control bits.

They include interrupt mask and enable bits, main bus enables, power down

initiation, and other control bits.

Kernel Memory, IO and

Buffers A11

7

Bus Error Logic

. A “watchdog timer” inside U2001 of approximately 2

5

milliseconds monitors 68020 cycle times. If any cycle exceeds 2 milliseconds,

then it generates a bus error (~BERR). Bus error can also be asserted when the

68020 tries to write to the Boot ROM. .

Reset. The 68020 processor resets both at power-up and power-down using the

reset signal into U1155 pin C1. Reset controller U1175 controls system reset.

Power-on reset asserts for a minimum of 400 milliseconds after the +5 V supply

stabilizes. Power-off reset asserts when the supply falls below a usable threshold

or when the 68020 asserts PWRDWN.

Kernel resident memory, IO, and buffers allow diagnostics to run while isolated

from the rest of the oscilloscope.

Kernel RAM. Kernel RAM. (U1336) runs internal diagnostics and flash EPROM

burn routines. It can also run down-loaded diagnostics.

Boot ROM. The Boot ROM. contains the 68020 power-up instructions. The

instructions begin with diagnostics. In addition, the Boot ROM. has the software

for operating the GPIB and programming the system flash EPROMS.

Address Buffers and Data Buffers. These buffers isolate the kernel address and

data lines from the rest of the system. The Bus Control Register enables or

disables these buffers.

7 Segment LED. Power-up diagnostics use this seven segment LED to communicate the pass or fail status of kernel diagnostics.

DIP Switch

5

diagnostic or firmware routines to run.

GPIB. The circuitry is made up of GPIB controller U1305, with transceivers

U1302 and U1311 buffering signals to and from the GPIB.

ID Register

5

Processor/Display board type and revision number.

TDS 520B Mod CM Component Service Manual

. The 68020 reads this switch at power-up to determine which

. Two ID Registers inside U2000 determines the A11 DRAM

1–19

Page 38

Detailed Circuit Description

Memory A11

8

Clocks, FPP, ACQP, and

Display Interface A11

9

The Memory subsystem includes NVRAM for power-off storage and Dynamic

RAM for the main system RAM.

NVRAM. The NVRAM. consists of non-volatile memory IC. This RAM provides

long-term power-off storage of calibration constants, front-panel settings,

waveforms, and hardware write-protected calibration constants.

NVRAM Write Protect. NVRAM Write Protect. circuitry can prevent a write to

portions of the NVRAM. that are reserved for calibration constants.

DRAM. Dynamic RAM is organized as 512K long words of memory for a total of

2 Megabyte. The circuitry includes the DRAM ICs, a dynamic RAM controller/

driver U2001.

DRAM Controller

. DRAM Controller automatically refreshes the DRAM..

5

During a normal 68020 access the dynamic RAM controller multiplexes the

address (on A2 to A21) onto the UMA0 to UMA8 address lines.

Clocks for the Processor System and the Display System are shared and are

derived from 25 MHz and 32 MHz oscillators Y1, Y2. The clock circuitry

divides the 25MHz_OSC signal by varying amounts to produce the clocks

needed by oscilloscope circuitry.

The Bus Control Register buffers and enables the Clocks, FPP, ACQP, and

Display Interface subsystem prior to 68020 access. Devices on the Clocks, FPP,

ACQP, and Display Interface subsystem (SP bus) are the DUART and the 68020

port into the Display system.

SP Data Buffers. The SP Data Buffers. buffer the main system data bus (D16 to

D31) to the SP data bus (SPD16 to SPD31).

Clocks. Y1 (25 MHz), and Y2 (32 MHz) crystal oscillators generate required

clocks for processor and display circuits.

DUART (Front Panel and Acquisition Processor Interface). The DUART (U1317) is

the 68020’s parallel-to-serial interface for both the Front Panel Processor and the

Acquisition Processor.

Table 1–19 lists the serial port interface signals to both the Front Panel Processor

and the Acquisition Processor.

1–20

TDS 520B Mod CM Component Service Manual

Page 39

Detailed Circuit Description

68020 to DSP Buffers and

Latches A11

10

DSP and Instruction

Memory A11

11

DSP D1 Buffers, Latches

and Memory A11

12

DSP D2 Buffers, Latches

and Memory A11

13

The 68020 to DSP Buffers and Latches buffer the 68020 address and data buses

to the DSP address and data buses.

Digital Signal Processor U1097 (DSP) provides fast waveform processing. The

processor uses prefetched instructions, from DSP Instruction Memory, and two

data memories. DSP Instruction Memory is loaded at power-on by the 68020.

The memory is 24 bits wide, fetched twice per DSP cycle, for an effective 48-bit

instruction word.

Buffers U1084 and U1083B buffer the DSP’s read and write signals to its three

buses. When BUSGRANT goes high, the outputs enter their high impedance

state, so that the 68020 can use the DSP’s buses. Table 1–13 lists the memory

map for the DSP Memory.

In general, the acquisition system uses the D1 Memory. The buffers and latches

buffer and demultiplex the X bus from the DSP to create the D1 bus. When the

bus is granted to the 68020 (BUSGRANT is high), the outputs of the buffers and

latches enter their high impedance state.

In general, the display system uses the D2 Memory. The buffers and latches

buffer and demultiplex the Y bus from the DSP to create the D2 bus. When the

bus is granted to the 68020 (BUSGRANT is high), the outputs of the buffers and

latches enter their high-impedance state.

DSP Bus Arbitration

Interrupts D2MMIO and

FIFO A11

14

D2MMIO Decoding decodes the address space and generates chip selects for all

registers on the A11 DRAM Processor/Display board accessible by the DSP.

The DSP D2MMIO Misc Register inside U2111 controls 68020 interrupts and

tells both the DSP and the 68020 whether or not the FIFO is full. Table 1–14

describes the contents the D2MMIO Misc Register.

The DSP performs tasks as directed by the 68020 processor and reports results

back either through interrupts or by using the FIFO (U1074). The DSP can pass

data back to the 68020 through the FIFO without having to halt DSP processing.

Interrupt ~FIFOINT, to the 68020, is generated when any data is in the FIFO,

and ~FIFOFULL internal to U2111 tells the DSP not to write to it or data will be

lost.

DSP Bus Arbitration and

Interrupts A11

14

Many buses in the oscilloscope are accessed by more than one processor. The

bus arbitration circuitry inside U2111 ensures that only one processor at one time

may access a bus.

TDS 520B Mod CM Component Service Manual

1–21

Page 40

Detailed Circuit Description

Display System A11

Bus Arbitration. The 68020 has access to all of the DSP’s address space on the D1

Memory, the D2 Memory, and the DSP Instruction Memory buses (see Table

1–7, 68020 Memory Map).

DSP Interrupts. The DSP has only one interrupt level. The interrupt circuitry is

similar to the 68020 interrupt circuitry. Interrupt mask (see Table 1–11) and

status (see Table 1–12) registers allow the interrupt routine to determine which

device(s) have interrupts pending and allow the masking of each interrupt. Table

1–12 lists the interrupt signals.

The Display System drives a 60 Hz non-interlaced, raster-scan CRT.

The display circuit’s primary function is writing waveforms into a waveform

plane. The circuitry provides several different display modes. These modes

include the Vector (Raster), Dot, XY, and YT modes.

D2 Interface and Display

Control Register A11

14

There are four main blocks in the display circuit: the Pixel Processor, the Vector

Lists, the Address Counter, and the Rasterizer. These blocks are connected

together in different ways for different display modes.

The Display System is a graphics system with two bit maps: the text plane and

the waveform plane. All information displayed is first written to one of these two

planes. The information is sent at regular intervals to the RAMDAC, which

converts it into an analog video signal. The contents of the bit maps are modified

through two different paths. The waveform display circuit, which is on the DSP

D2 bus, normally modifies the waveform plane, and the 68020 modifies the text

plane. The Video System Controller. and Video Timing blocks inside U2100

generate signals which affect the display system.

To maximize the waveform update rate, only waveforms are written to the

waveform plane. All other displayable information such as the graticule, readout,

cursors, and menus is written to the text plane. Both planes may be updated at

the same time.

The waveform display circuit takes a list of sample points, translates them into

bit pattern, writes those bit pattern in the proper location, and interrupts the DSP

when it is done.

The DSP D2 Interface connects the Rasterizer, Pixel Processor, Vector Lists,

RAMDAC, Display Control Register, and part of the Video Timing to the DSP.

It also generates two interrupts and a wait signal to the DSP system.

1–22

Display Control Register inside U2111 is an 8-bit register whose data lines are

connected to D2D8–D2D15.

TDS 520B Mod CM Component Service Manual

Page 41

Detailed Circuit Description

Vector List 0 and Vlist

Address Counter A11

16

Vector List 1 A11

17

Rasterizer A11

18

A vector list stores waveform sample data. Before starting a normal display

mode, the DSP writes data to a vector list. After the DSP starts the Pixel

Processor, the Pixel Processor reads the waveform sample data from the vector

list.

The Pixel Processor controls the Vector List Address Counter which addresses

the vector lists during waveform display modes. It is an 11-bit counter (U28,

U29, U30) with three control lines: PIPEN, CLKOUT, and ~LINEND.

This circuitry performs the same function as Vector List 0.

The primary function of the Rasterizer is to “draw” vectors between sample

points. It also generates waveform display control signals.

To rasterize waveforms, the Rasterizer generates an intensity for every point in

the waveform plane. It generates points from left-to-right top-to-bottom, in the

same way a raster scan CRT scans the phosphor. The Rasterizer outputs the

intensities to the Pixel Processor on LV3–LV6.

Rasterizer U59 has internal registers and lookup tables that the DSP can access.

During internal accesses the Rasterizer uses address inputs D2A0-D2A8 to

determine which register or memory is being accessed. Signal ~VFVIEN is low

during an internal access.

Pixel Processor and

020/WFM Data

Buffers A11

19

The PP Data Buffers and the 020/WFM Data Buffers buffer and multiplex the

Pixel Processor data bus onto both the 68020 data bus and the SP data bus. The

PP Address Mux’s multiplex the DSP D2 address bus and the vector lists data

outputs onto the Pixel Processor address bus.

Like the Rasterizer, Pixel Processor U60 has both internal registers and lookup

tables that can be accessed from the DSP.

The DSP D2 Interface asserts ~MEMACC or ~INTACCP during accesses to

internal registers. The Pixel Processor asserts WAITP whenever it is in a display

cycle. A DSP access to Pixel Processor address space with WAITP asserted

causes a XWAIT (U2111 pin 37) signal to the DSP.

Pixel Processor U60 contains the display circuit state machine, the control

interface to the waveform planes, and hardware for implementing many of the

display modes. The display modes are selected from a register inside the Pixel

Processor.

A memory refresh or display update cycle forces the current display mode to be

temporarily suspended.

TDS 520B Mod CM Component Service Manual

1–23

Page 42

Detailed Circuit Description

For each display mode, except system processor access mode, the following

steps are taken to start the Pixel Processor state machine:

1. Select the desired mode.

2. Write to the X register.

3. Write to the Y register.

The Pixel Processor then asserts WAITP and starts the desired mode. When

finished, the Pixel Processor deasserts WAITP and asserts ~DISPINTTS, which

interrupts the DSP. (Random dot mode does not generate a ~DISPINTTS

interrupt.)

Waveform plane refresh cycles and 68020 access occur through the Pixel

Processor.

The Pixel Processor also performs the top and bottom clip display functions on

waveforms.

H Top Clip will not display points whose vertical coordinate is above the value

stored in the Pixel Processor’s top register. A vertical coordinate of 0 is

considered the top of the screen.

Waveform Plane

0 and 1 A11

20

H Bottom Clip will not display points whose vertical coordinate is below the

value stored in the Pixel Processor’s bottom register.

The waveform planes are 512 by 512 bit maps. Only the upper 480 lines are

displayed.

The Pixel Processor has exclusive control of all waveform plane control lines

with two exceptions: