Page 1

SDLA Visualizer

Serial Data Link Analysis V

Application Help

isualizer Software

*P 077021108*

077-021

1-08

Page 2

Page 3

SDLA Visualizer

Serial Data Link Analysis V

Application Help

isualizer Software

Register now!

Click the following link to protect your product.

www.tek.com/register

*P 077021108*

077-021

1-08

Page 4

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are

protected by national copyright laws and international treaty provisions. T

and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges

reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

ektronix products are covered by U.S. and foreign patents, issued

Page 5

Table of Contents

Table of Contents

Welcome....................................................................................................................................................................................... 7

OLH-ContactingTek.......................................................................................................................................................................8

Getting started...............................................................................................................................................................................9

Software updates from the Tektronix web site....................................................................................................................... 9

Requirements and installation................................................................................................................................................9

Conventions......................................................................................................................................................................... 10

Application file types and locations...................................................................................................................................... 10

Moving between applications...............................................................................................................................................10

Online help........................................................................................................................................................................... 11

Product overview.........................................................................................................................................................................12

SDLA visualizer product overview....................................................................................................................................... 12

Understanding the system................................................................................................................................................... 13

Understanding test points.................................................................................................................................................... 16

Using DPOJET and SDLA visualizer together..................................................................................................................... 21

Using JNB and SDLA Visualizer together............................................................................................................................22

Components and menus............................................................................................................................................................. 24

Main menu in detail..............................................................................................................................................................24

Test points................................................................................................................................................................................... 27

Test point and bandwidth manager (RT only)...................................................................................................................... 27

Test point and bandwidth manager (Sampling only)............................................................................................................ 31

Saving test points.................................................................................................................................................................35

Exporting filters for use with a 32-bit sampling oscilloscope................................................................................................37

Save test point filters for multiple sample rates (RT only) ...................................................................................................38

Creating a custom bandwidth limit filter............................................................................................................................... 39

De-embed block.......................................................................................................................................................................... 41

De-embed block overview....................................................................................................................................................41

De-embed-Embed menu......................................................................................................................................................42

How to re-normalize S-Parameters to different reference impedances............................................................................... 49

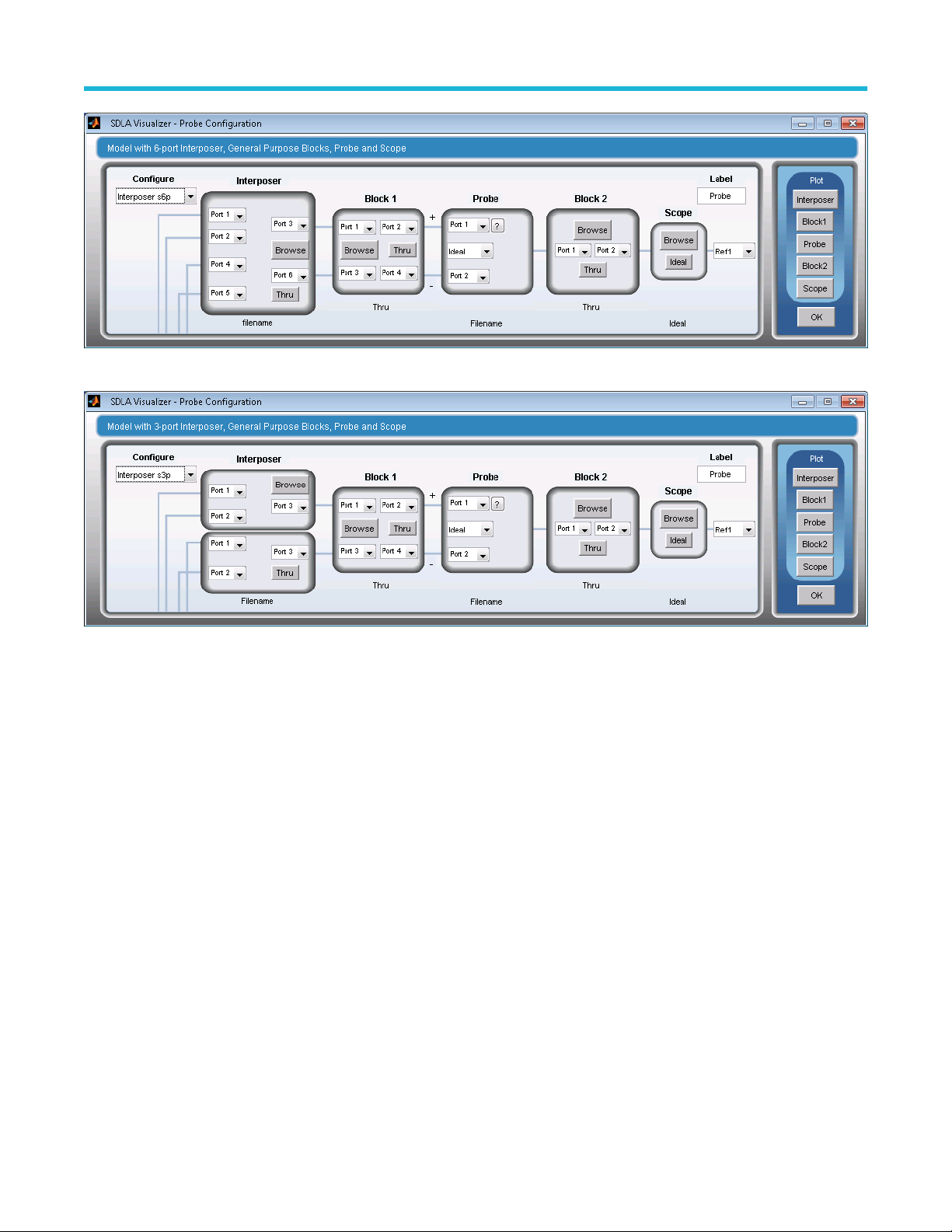

Configuring probes (RT only)...............................................................................................................................................51

Probe and tip selection (RT only).........................................................................................................................................54

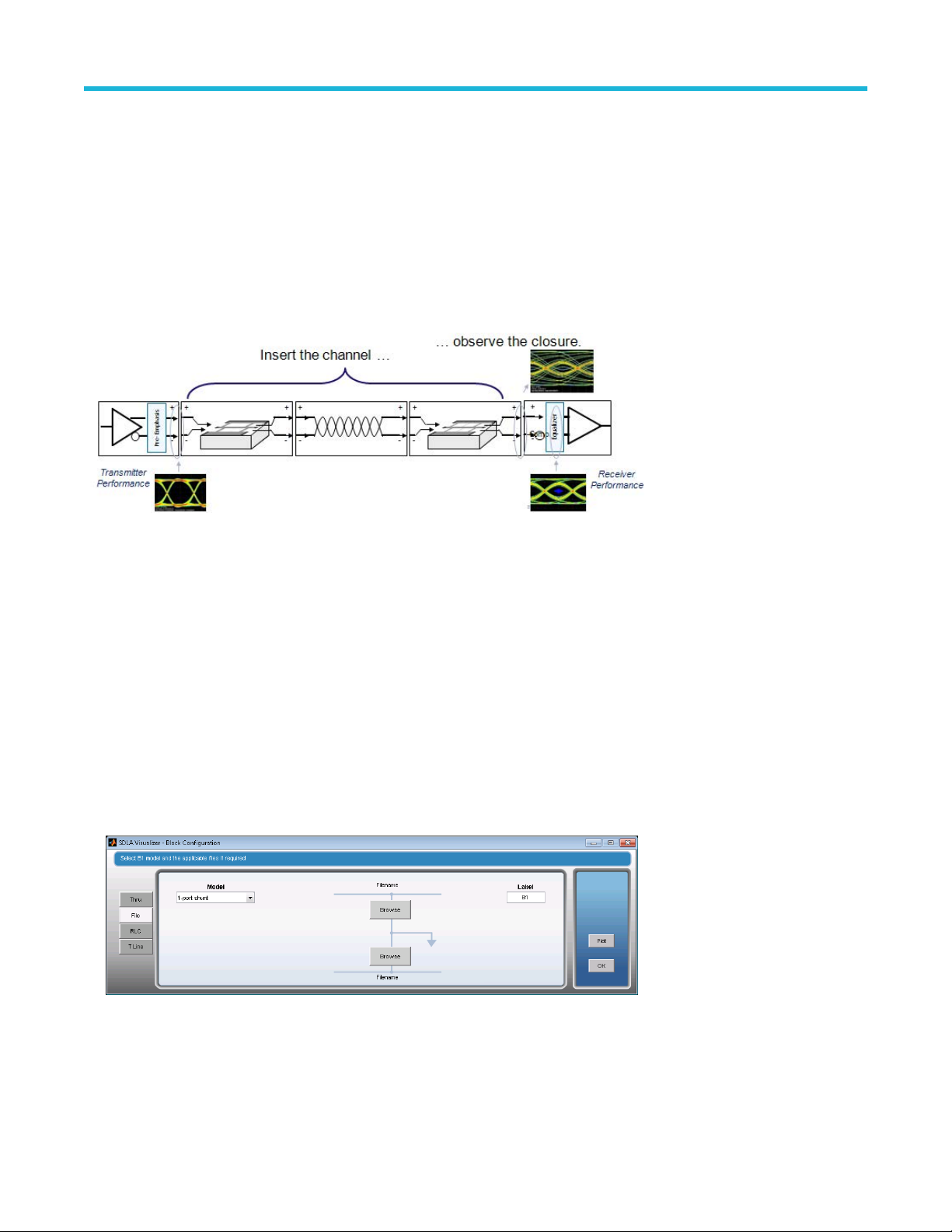

Block configuration menu.....................................................................................................................................................57

Load configuration menu..................................................................................................................................................... 67

Plots............................................................................................................................................................................................ 70

Plots..................................................................................................................................................................................... 70

Using plots for troubleshooting s-parameters...................................................................................................................... 74

Tx block (Transmitter modeling block)........................................................................................................................................ 78

Tx block overview................................................................................................................................................................ 78

Tx configuration menu......................................................................................................................................................... 78

Tx emphasis menu...............................................................................................................................................................79

Embed block............................................................................................................................................................................... 84

Embed block overview......................................................................................................................................................... 84

Rx block (Receiver modeling block)............................................................................................................................................86

Rx block overview (RT scopes)............................................................................................................................................86

Rx block overview (sampling scopes)..................................................................................................................................87

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 5

Page 6

Table of Contents

Rx configuration menu......................................................................................................................................................... 87

Using CTLE to improve signal recovery

...............................................................................................................................89

Using clock recovery for FFE-DFE equalization.................................................................................................................. 94

Using FFE-DFE to improve signal recovery.........................................................................................................................96

Using the taps tab................................................................................................................................................................ 98

Manual FFE/DFE configuration for Serial Data Standards.................................................................................................. 99

Equalizing PAM-4 signals...................................................................................................................................................100

Running the Rx equalizer...................................................................................................................................................100

AMI mode...........................................................................................................................................................................101

Configure actions for the apply and analyze buttons................................................................................................................ 104

Creating filters for a sampling oscilloscope...............................................................................................................................106

Running a test........................................................................................................................................................................... 108

Running a test: recommended order................................................................................................................................. 108

Examples and troubleshooting (RT only).................................................................................................................................. 113

Examples of tasks and troubleshooting..............................................................................................................................113

Example of de-embedding cables......................................................................................................................................113

Example of embedding a serial data link channel..............................................................................................................117

Example of de-embedding a high impedance probe......................................................................................................... 120

Example of de-embedding significant reflections with dual input waveforms.................................................................... 122

Example of removing a DDR reflection with a single input waveform................................................................................134

GPIB remote control..................................................................................................................................................................139

Using GPIB remote control................................................................................................................................................ 139

GPIB commands................................................................................................................................................................140

APPLICATION:ACTIVATE Serial Data Link Analysis.........................................................................................................140

VARIABLE:VALUE sdla, p:exit...........................................................................................................................................140

VARIABLE:VALUE? sdla....................................................................................................................................................140

VARIABLE:VALUE sdla, p:adapttaps:<value> ..................................................................................................................141

VARIABLE:VALUE sdla, p:bitrate:<value>.........................................................................................................................141

VARIABLE:VALUE "sdla", "p:ctletype:<type>" ..................................................................................................................141

VARIABLE:VALUE sdla, p:dfestate:<state> ......................................................................................................................141

VARIABLE:VALUE sdla, p:ffedfetype:<type>.....................................................................................................................142

VARIABLE:VALUE sdla, p:RunEQ ....................................................................................................................................142

VARIABLE:VALUE sdla, p:source:<source>......................................................................................................................142

VARIABLE:VALUE sdla, p:sourcetype...............................................................................................................................143

VARIABLE:VALUE sdla, p:recall:<path and file name >.................................................................................................... 143

VARIABLE:VALUE sdla, p:source2:<source2>..................................................................................................................143

VARIABLE:VALUE sdla, p:analyze.................................................................................................................................... 143

VARIABLE:VALUE sdla, p:apply........................................................................................................................................144

VARIABLE:VALUE “sdla”, “q:dfetaps?”..............................................................................................................................144

References................................................................................................................................................................................145

Index......................................................................................................................................................................................... 146

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 6

Page 7

Welcome

Welcome

Figure 1: The Tektronix SDLA Visualizer offers a powerful, flexible set of modeling tools for de-embedding, embedding and equalizing high speed serial signals. Using a

simple user interface with many configurable features, you can model a measurement circuit to de-embed the ef

from the acquired scope waveform back to the transmitter block. Likewise, you can model and embed a simulation circuit from the transmitter block that simulates possible

effects upon the signal. Both single and dual waveform input modes are available.

fects of scopes, probes, fixtures, cables and other equipment

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 7

Page 8

OLH-ContactingTek

OLH-ContactingTek

Tektronix, Inc.

14150 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

For product information, sales, service, and technical support:

• In North America, call 1-800-833-9200.

• Worldwide, visit www.tektronix.com to find contacts in your area.

Copyright © Tektronix. All rights reserved. Licensed software products are owned by Tektronix or its subsidiaries or suppliers, and are

protected by national copyright laws and international treaty provisions. Tektronix products are covered by U.S. and foreign patents, issued

and pending. Information in this publication supersedes that in all previously published material. Specifications and price change privileges

reserved.

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Compiled Online Help Part number: 076-0173-06

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 8

Page 9

Getting started

Getting started

Software updates from the Tektronix web site

Periodic software upgrades may be available from the Tektronix Web site.

To check for upgrades:

1. Go to the Tektronix Web site ( www.tektronix.com).

2. Press on Support and select the item Downloads, Manuals & Documentation.

3. Enter “SDLA” in the MODEL OR KEYWORD text box.

4. Select Software in the SELECT DOWNLOAD TYPE drop-down list.

5. Press Go to find the available software upgrades.

6. Press the appropriate software title. Read the application information to be sure that it is compatible with your instrument model.

7. Press Login to access this content and log in to access the download.

8. Press the Download File link.

Requirements and installation

The SDLA Visualizer application is installed on the following instruments:

• Tektronix DPO/DSA/MSO70000/C/D/DX Series oscilloscopes before they leave the factory

• Tektronix DSA8300 sampling oscilloscopes

The installation provides ten free uses of the full featured SDLA Visualizer application.

Requirements for Proper Operation

RT oscilloscope: The SDLA Visualizer application requires a Tektronix DPO/DSA/MSO70000/C/D/DX Series Oscilloscope with a single

shot bandwidth ≥4.0 GHz.

To perform jitter and timing analysis, it also requires the following:

• RT oscilloscope: Tektronix DPOJET Jitter and Eye-diagram Analysis software

• Sampling oscilloscope: Tektronix 80SJNB Jitter, Noise and BER Analysis software

To ensure accurate acquisitions, be sure to properly calibrate your oscilloscope by running the signal path compensation. The length of

time between SPC and temperature changes at the instrument location dictate when this should be done.

Software Compatibility

Refer to the product Release Notes or the Optional Applications Software Installation manual for the compatible versions of oscilloscope

software and for DPOJET (RT oscilloscopes) and for 80SJNB (sampling oscilloscopes).

Option Key Requirement

You must have a valid option key for the application. Without the key, there are free trials. Consult with your Tektronix Applications

Engineer or Account Manager for details.

Reinstalling the SDLA Visualizer Software

To install the latest version of SDLA Visualizer software, press Software Updates From the Tektronix Web Site.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 9

Page 10

Conventions

Getting started

The online help uses the following conventions:

• DUT refers to the Device Under Test.

• When a step requires a sequence of selections, the > delimiter indicates the path from menus to sub-menus and to menu options.

• The directory path to support files is C:\Users\Public\TekApplications\SDLA.

• (RT only) indicates a feature available on real-time oscilloscopes, but not available on sampling oscilloscopes.

Application file types and locations

The software uses the following file types and locations. The support files are arranged in folders with descriptive names at

C:\Users\Public\Tektronix\TekApplications\SDLA:

• Input filters – FIR and IIR filter files

• Input S-parameters – Touchstone 1.0 version

• Output filters – where the software stores generated FIR filters when the Apply button is pressed. The filenames are overwritten each

time you click the Apply button. You can rename the filter files to save a set of FIR filters for later use.

These filters are stored in the directory entitled C:/users/public/Tektronix/TekApplications/SDLA/output

filters.

Default naming conventions:

For Single Input mode, the filenames are:

Sdlatp1.flt, sdlatp2.flt, …. Sdlatp<n>.flt where n is the test point number.

For Dual Input mode: folders named

Tp1, Tp2, … Tp<n>

are created, where n is the test point number. Inside each folder is the set of files.

• Save recall – temporary location where software stores the SDLA Visualizer setup configuration files.

• Example waveforms (RT only) – Example waveform files to help you learn the application.

Your custom S-parameter files and filter files can reside at any path accessible to the instrument.

Moving between applications

The quickest way to move between software applications is to hold down the keyboard Alt key and tap the Tab key to pick an application.

An alternative is to use the triangle buttons on the right side of the Main Menu to switch between the SDLA Visualizer, TEKScope and

DPOJET/JNB applications:

•

Press the left triangle to bring the oscilloscope waveform display to the foreground.

• Press the right triangle to bring the oscilloscope waveform display into view with SDLA Visualizer application still in the foreground.

This option is handy when also using the DPOJET/JNB application.

You may bring all the SDLA Visualizer windows to the foreground by first pressing the minimize button at the upper right corner of the

oscilloscope window to collapse it to the Windows tool bar. Then press the right triangle on SDLA to expand the scope back to full screen

with SDLA in the foreground.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 10

Page 11

Getting started

Online help

Help in Different Languages

If you would like to download a .PDF file of the Online Help that has been translated into Japanese, simplified Chinese, or Korean, visit

.tektronix.com and press on “Change Country” at the top. Then enter the search term “SDLA Visualizer”.

www

Press the Help button in the upper right corner of the SDLA Visualizer Main Menu to bring up the online Help system. Pressing the F1 key

at any time also brings up the Online Help system.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 11

Page 12

Product overview

Product overview

SDLA visualizer product overview

The Tektronix SDLA Visualizer offers a powerful, flexible set of modeling tools for de-embedding, embedding and equalizing high speed

serial signals. Using a simple user interface with many configurable features, you can model a measurement circuit to de-embed the

effects of scopes, probes, fixtures, cables and other equipment from the acquired scope waveform back to the transmitter block. Likewise,

you can model and embed a simulation circuit from the transmitter block that simulates possible effects upon the signal. (RT only): Both

single and dual waveform input modes are available.

SDLA Visualizer offers full 4-Port S-parameter modeling support that takes into account the Tx and Rx impedance models, along with

all transmission line characteristics. The signal path is fully represented by a unique cascading S-parameter feature; if any parameter

changes anywhere in the cascade, it affects all test points in the cascade.

With the ever increasing data speeds for high speed serial links, PAM-4 is gaining popularity as the new signaling of choice to double the

date rate without doubling the bandwidth of the delivery network. SDLA now supports PAM-4 Rx modeling in its Rx Block, including PAM-4

aware clock date recovery and equalization methodology.

Many standards require that equalization is applied to the signal before measurements are taken. SDLA Visualizer provides CTLE, FFE

and DFE equalization modeling tools with support for serial standards such as PCI Express 3.0/4.0, USB 3.0/3.1, Thunderbold 10G/20G,

and SAS. Also available is an IBIS-AMI model (RT only) that lets you use equalization files supplied by a chip vendor.

Validation is simplified with a rich set of plotting tools, including S-parameter plots, time domain plots, Smith chart, and overlay tools. These

plots are available starting with the cascade block configuration stage, providing confidence that the input models (i.e. S-parameters) are

correct.

After the circuits are defined, SDLA Visualizer provides the ability to observe the signal via 12 user-defined test points, including 4 that

are movable within the De-embed and Embed Blocks. You may view multiple test points simultaneously, and observe areas of the signal

that you could not probe otherwise. Up to four math and two reference waveforms are visible on the scope graticule at one time. You

are able to see the differential, common mode, or individual inputs of the signal at once, without having to create multiple models for

each option. You can also create test point filter (transfer function) plots that allow for verification of the system setup. Magnitude, Phase,

Impulse and Step plots are available.

SDLA is intended to be used along with Tektronix DPOJET Real-time Jitter and Timing Analysis software (RT scopes) or JNB Jitter, Noise,

and BER Analysis software (sampling oscilloscopes). Together, these tools provide deep insight and analysis capabilities so that you can

visualize an entire signal processing path and accurately measure the true signal from the DUT.

Some tasks you can accomplish using SDLA Visualizer

• Remove the effects of reflections, cross-coupling, and loss caused by non-ideal probe points, fixtures and cables

• Remove the effects of interposers using 3, 4, or 6-port S-parameter models

• Simulate and measure at test points using actual captured waveforms where physical probing is not practical

• Observe the signal at the end of the link by embedding user-defined channel models into the waveform at the transmitter

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 12

Page 13

Product overview

• Add or remove transmitter equalization, using 2 or 3-tap filter coefficients or FIR filter

Open closed eyes using CTLE, clock recovery, DFE and FFE equalization

•

• Model silicon-specific receiver equalization algorithms using IBIS-AMI models (RT only), so you can virtually view the signal inside of

the receiver

• De-embed high impedance or SMA probes

• Model RLC, TDT waveforms, and lossless transmission lines in the absence of S-parameters

• Create S-parameter plots, time domain plots, and Smith Chart plots for quick verification of S-parameters and test point transfer

functions

• Perform quick analysis of jitter and timing parameters using integrated DPOJET/JNB support

• Work with DDR and next generation serial standards including PCI Express 3.0/4.0, USB 3.0/3.1, Thunderbolt 10G/20G, SAS 6G,

SATA, and DisplayPort (including interposer model)

For more information:

Understanding the System

Using DPOJET and SDLA Visualizer together

Using JNB and SDLA Visualizer together

Running a Test: Recommended Order

Note: Pressing the F1 key at any time brings up the Online Help system.

Note: If you would like to download a .PDF file of the Online Help that has been translated into Japanese, simplified Chinese, or

Korean, visit www

SEE ALSO:

• Main Menu in Detail

• Examples of T

asks and Troubleshooting

.tektronix.com and press on “Change Country” at the top. Then enter the search term “SDLA Visualizer”.

Understanding the system

SDLA Visualizer requires you to define two circuit models, the Measurement Circuit and the Simulation Circuit, that both connect to the

Tx Block. The Tx Block makes use of Thevenin equivalent voltage to provide a point where the acquired waveform is passed into the

simulation side of the system. (Thevenin's Theorem states that it is possible to simplify any linear circuit, no matter how complex, to an

equivalent circuit with just a single voltage source and impedance.)

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 13

Page 14

Product overview

The Measurement Circuit

The upper part of the Main Menu diagram stemming from the Tx Block represents the Measurement Circuit: the probes, scope, fixtures

and the portion of the channel between the Tx and the fixture. (Note that this diagram changes, reflecting whether Single or Dual Input

mode is specified.) This is where the S-parameter models that represent the physical test and measurement system used to acquire

the signal need to be defined and loaded into the De-embed Block. In the absence of S-parameters, you can use RLC or lossless

transmission line models.

The test points in this circuit represent simulated probing locations that allow visibility of the link at multiple test locations, including two

movable test points within the De-embed Block. The software derives the transfer function(s) and creates FIR filters for each test point.

When the filters are applied to the waveform(s) acquired from the scope, SDLA produces waveforms at the desired test points. The

waveform with the loading of the Measurement Circuit can be viewed at Tp1, Tp6, or Tp7.

Tp6 and Tp7 always mean the signals at the right side of the block at the left of the test point. When s6p or s3p interposer is considered,

to get the signals at the right side of the interposer

right of the block. For example, if the HiZ probe is located between B2 and B3, to get the signal at the left of the interposer, then set Tp6

between B2 and B3. To get the signal at the right side of the interposer, set B3 to Thru, and set Tp6 between B3 and B4.

, set the block at the right of the interposer to Thru, and Tp6 or Tp7 can be put to the

The Simulation Circuit

The lower part of the Main Menu diagram stemming from the Tx Block represents the Simulation Circuit. Now that the waveforms have

been de-embedded back to the Tx Block, the Simulation Circuit is used to embed a simulated channel to the Tx Block. The S-parameter

models for the link you would like to simulate need to be defined and entered into the Embed Block. Again, you may use an RLC or a

lossless transmission line models when S-parameters are not available. The load of the receiver is also modeled in the Embed Block. The

Rx Block allows you to specify Rx equalization. The test points in this circuit allow visibility in between link components, including two

movable test points within the Embed Block. Tp2 shows the Tx output waveform without the loading of the Measurement Circuit, but with

the loading of Simulated Circuit.

Note: The arrows on the Main Menu circuit diagram show the order in which SDLA processes the transfer functions. For the

Measurement Circuit part of the diagram, the ACTUAL signal flow is in the opposite direction of the arrows. For the Simulation

Circuit, the actual signal flow direction is the same as the signal processing flow arrows.

Using the Embed Block to Close the Eye and Rx Block to Open the Eye

The Embed Block lets you “insert” a simulated channel so that you can observe the closed eye (viewable at Tp3):

Now, you can use the Rx block to open the eye and observe the signal after CTLE (Tp10)

Rx Block allows you to specify Rx equalization. Serial data receivers typically contain three kinds of equalizers: a continuous-time linear

equalizer (CTLE), a feed-forward equalizer (FFE), and decision feedback equalizer (DFE)). CTLE, clock recovery, DFE and FFE equalizers

are available in the Rx Block; alternatively, IBIS-AMI models (RT only) can be used to model silicon specific equalization algorithms. Also,

three test points are available in the Rx Block. These allow for visibility of the waveform after CTLE and/or after FFE/DFE and recovered

clock, or an IBIS-AMI model has been applied.

or after FFE/DFE (Tp4) as been applied. The

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 14

Page 15

Test Points

Product overview

With 12 test points, SDLA V

signal that you could not probe otherwise. You can view the transmitter signal with the loading of the measurement circuit at Tp1, and at

the same time, view the de-embedded measurement circuit at Tp2 with an ideal 50 Ohm load. You have many flexible options for labeling

test points, and for mapping test points to math waveforms. It is easy to put the test point labels onto the scope waveform display, so

you can tell which waveform is which, and easy to apply the data to DPOJET/JNB, so that you know which waveform you’re doing the

measurement on. A Delay feature lets you move the waveforms in time with respect to each other. (By default, the delay is removed from

the test point filters, so that events are close to being time-aligned.)

SDLA Visualizer provides up to 6 waveforms (four math and two reference) that are simultaneously visible on the scope graticule at one

time, allowing visibility of the link at different locations. (You use the Test Point and Bandwidth Manager to map the SDLA test points to

the math and reference waveforms.) The software allows for dynamic configuration of test points in order to best utilize the scope math

channels (i.e. after de-embedding, CTLE, etc.) Also, four test points can be moved on the De-embed and Embed Menu cascade diagrams,

providing maximum flexibility. Press here for a deeper understanding of how test points work.

Once the simulation and measurement circuits have been defined, you can easily save test point filters that can be used with the scope

math system. For details, see Saving Test Points.

isualizer gives you visibility over multiple test points simultaneously, providing virtual “observation points” of the

Modeling Block View

Another way to view the system is as a series of modeling blocks for de-embedding the effects of the waveform acquisition hardware

setup, and modeling blocks for embedding link components that are not represented physically.

These diagrams illustrate the entire S-parameter processing path.

Figure 2: Single Input Mode

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 15

Page 16

Figure 3: Dual Input Mode

Dual and Single Input Modes

Product overview

In some cases, it is desired to process each leg of the signal individually through the network, in order to completely take into account

differences in the two sides of the signal. SDLA Visualizer offers a choice of Dual Input (RT only) or Single Input modes on the Main Menu.

In Single Input mode, the differential signal may be viewed at each test point. Dual Input mode (RT only) allows the viewing of individual

inputs, differential, or common mode. For additional information, see Full 4–port Modeling.

Algorithms, theory and math derivations

For in-depth information on several advanced SDLA topics, including algorithms, theory, math derivations for re-normalizing S-parameters

and converting single-mode S-parameters to mixed mode, see technical papers located at www.tek.com/sdla.

SEE ALSO:

• Using DPOJET and SDLA Visualizer Together

• Product Overview

Understanding test points

Test points output waveforms that represent the signal at a particular position in the system circuit diagram. Each test point waveform is

obtained by applying at least one filter to the input waveform(s) acquired by the oscilloscope.

SDLA Visualizer provides up to 12 test points (when using the REF waveforms). Up to 6 test point outputs are viewable on the scope

graticule at one time: four math and two reference. The SDLA processing and analysis operate only on waveforms that have been turned

on and are displayed on the oscilloscope.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 16

Page 17

Product overview

Table 1: Test Point Descriptions.

Test point Position Description

Tp1 Main Measurement circuit loading the Tx block output

Tp2 Main Simulation circuit loading the Tx block output,

measurement circuit de-embedded

Tp3 Main Rx block input. Simulation circuit loading the Tx block

output, measurement circuit de-embedded

Tp4 Rx Eq Data Data output of the Rx block after equalization

Tp5 Rx Eq Clock Test point for the recovered clock output of the Rx block

Tp6 De-embed Block Movable test point with the measurement circuit loading the

Tx block output

Tp7 De-embed Block Movable test point with the measurement circuit loading the

Tx block output

Tp8 Embed Block Movable test point with the simulation circuit loading the Tx

block output, measurement circuit de-embedded

Tp9 Embed Block Movable test point with the simulation circuit loading the Tx

block output, measurement circuit de-embedded

Tp10 CTLE CTLE output

Tp11 Tx Thevenin equivalent voltage of the Transmitter model

Tp12 Tx Test point for the output of the Tx Emphasis block (if on)

Test Point and Bandwidth Manager

Pressing on a test point on the Main Menu brings up the T

modes (Dual Mode only) and to save test point filters. For details, see Test Point and Bandwidth Manager.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 17

est Point and Bandwidth Manager, which is used to configure test points and

Page 18

Product overview

How Test Point Filters are Applied

The test point filters are derived from the S-parameter models that are contained in the De-embed, Tx, and Embed Blocks. These filters

are of type FIR, which are convolved in the time domain with the source waveforms acquired on the oscilloscope. Details on what generally

happens when test point filters are applied listed below

Real-Time Scopes

1. First, you have to enter the S-parameters or models that will determine S-parameters for each of the blocks and terminations

throughout the system using the Tx Block and De-embed/Embed Menu.

2. You also need to turn on and define the desired test points by pressing on a test point on the Main Menu and using the Test Point and

Bandwidth Manager.

3. Finally, you press the Apply button in the SDLA Visualizer Main Menu. The software computes the filters (transfer functions) for

each test point that has been turned on using the Test Point and Bandwidth Manager. These filters are then stored in the directory

entitled C:/users/public/Tektronix/TekApplications/SDLA/output filters. (You may also save the

filters from the Test Point and Bandwidth Manager into files using your own names or folder.)

.

Default Naming Conventions

For Single Input mode, the filenames are:

Sdlatp1.flt, sdlatp2.flt, …. Sdlatp<n>.flt where n is the test point number.

For Dual Input mode: folders named

Tp1, Tp2, … Tp<n>

are created, where n is the test point number. Inside each folder is the set of files.

At the same time, SDLA loads the filters that have been turned on into the oscilloscope math menu, and creates a math expression

that will display live waveforms for the selected test points on the oscilloscope graticule.

Sampling Scopes

The above holds for sampling scopes except that only Single Input mode is available.

Crosstalk and Reflection Handling

SDLA Visualizer uses all elements of the S-parameter models to compute the transfer functions for test points.

Shown below is an example of the signal flow graph for three cascaded 4-port networks. This illustrates the effects that cross-talk paths,

transmission paths, and reflection paths have on the overall transfer function from one point in the network to another point in the network.

SDLA Visualizer uses all of these S-parameter paths to compute the transfer functions for test points.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 18

Page 19

Full 4-port Modeling

Product overview

This system maintains full 4-port modeling. Therefore, the test points are dif

(test point modes) to view.

ferential, and each contains a set of four possible waveforms

Dual input mode (RT only)

• Dual input selection takes two waveforms from two channels, math functions or reference waveforms in the oscilloscope, and

processes them through the 4-port system to obtain test point waveforms. When Dual Input mode has been selected on the Main

Menu, the Test Point and Bandwidth Manager will show the options for Select Test Point Mode. The options are:

• A: the waveform on the upper line of the test point

• B: the waveform on the lower line

• A – B: the differential waveform and

• (A + B )/2: the common mode waveform.

In Dual Input mode, each test point can output waveforms for all four modes described above. Each of these four modes requires

two filters applied to the two input waveforms.

An example math expression that SDLA might set up in the oscilloscope Math menu:

Math1 = arbflt1(ch1) + arbflt2(ch2)

Mathematically, only four filters are required for a differential test point. However, this would require two filters each for A and B modes,

and all four filters for differential and common modes. In order to simplify to only two filters for any mode, an additional four filters are

created from linear combinations of the four basic filters. Thus SDLA creates eight filters for each test point, as shown below:

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 19

Page 20

Single Input mode

Product overview

• Real-T

• Sampling Scopes

ime Scopes

When Single Input mode is selected on the Main Menu, an assumption is made that a differential input waveform of form A – B is

acquired on a single source of the oscilloscope (Src1). SDLA then splits this waveform mathematically into an exactly balanced A and

B signal, which is then processed through the 4-port cascaded system.

For Single Input operation, the test points throughout the system only utilize the A – B Mode (differential waveform as output).

Only one filter is required, and is applied to the input source waveform to obtain the output test point waveform. An example math

expression that SDLA might set up in the Math oscilloscope menu:

Math1 = arbflt1(ch1)

Sampling scope waveforms are not acquired by SDLA.

Run SDLA on SX oscilloscope

• Single input

SX oscilloscopes allow three live channels: ch1, ch2 and ch3. Selecting channel 4 will display the following error message.

• Dual Input

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 20

Page 21

Product overview

SX oscilloscopes don't allow mixing ATI and non-ATI channels in Dual Input case. Either two ATI channels or two TekConnect channels

can be used as the input source; otherwise an error message is shown:

SEE ALSO:

• T

est Point and Bandwidth Manager

• Saving Test Points

• Main Menu in Detail

• Product Overview.

Using DPOJET and SDLA visualizer together

Together, SDLA Visualizer and DPOJET provide a complete solution for high-speed serial measurement and analysis. DPOJET operation

is integrated right into the SDLA Visualizer Main Menu Analyze and Config buttons. DPOJET gives you the flexibility to analyze and

compare the results at multiple points on the link. What’s more, it allows multiple measurement configurations; for example, you could

easily compare standard-specific vs. silicon-specific clock recovery measurement parameters.

The figure below shows an example where the Analyze button has been configured to automatically run DPOJET without changing the

SDLA setup. Here, the PCI Express 3.0 configuration has been defined by the user. Notice how using DPOJET and SDLA Visualizer

together gives you full link visibility of the eye diagram and associated measurements for each of the desired test points. The eye diagram

on the top left shows the acquired waveform and the input into SDLA. The eye diagram on the top right shows the Simulation Circuit

loading the Tx block output (Tp3). The eye diagrams on the bottom show the signal after CTLE (Tp10) and after FFE/DFE (Tp4).

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 21

Page 22

Product overview

To switch between SDLA Visualizer and DPOJET, use the Alt Tab keyboard combination or the navigation buttons (< and >) on the SDLA

Main Menu. Use the T

SEE ALSO:

• Configure Actions for Apply and Analyze Buttons

• Product Overview

• Understanding the System

ekScope application minimize button to minimize the scope window to view the DPOJET and SDLA applications.

Using JNB and SDLA Visualizer together

Together, SDLA Visualizer and JNB provide a complete solution for high-speed serial measurement and analysis. JNB operation is

integrated into the SDLA Visualizer Main Menu Analyze button. JNB gives you the flexibility to analyze and compare the results at multiple

points on the link.

SDLA Visualizer combines all its inputs into one filter, launches JNB and passes its filter to JNB. The figure below shows the JNB display.

Notice how using JNB and SDLA Visualizer together gives you full link visibility of the eye diagram and associated measurements for the

desired test points.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 22

Page 23

Product overview

To switch between SDLA Visualizer and JNB, use the Alt Tab keyboard combination or the navigation buttons (< and >) on the SDLA Main

Menu. Use the TekScope application minimize button to minimize the scope window to view the JNB and SDLA applications.

SEE ALSO:

• Configure Actions for Apply and Analyze Buttons

• Product Overview

• Understanding the System

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 23

Page 24

Components and menus

Main menu in detail

Components and menus

Use the SDLA V

The upper part of the circuit diagram shows the Measurement Circuit model, and the lower part shows the Simulation Circuit model. The

arrows show the order in which SDLA processes the transfer functions. Note that for the Measurement Circuit part of the diagram, the

ACTUAL signal flow is in the opposite direction of the arrows. For the Simulation Circuit, the actual signal flow direction is the same as the

signal processing flow arrows.

isualizer Main Menu to configure the blocks, models, and test points, and to apply, plot and analyze the data.

Inputs

Y

ou can use either one or two inputs with SDLA Visualizer by selecting either Single Input or Dual Input mode. Changing these radio

buttons will change the configuration panels here and elsewhere. The image above displays Dual Input mode and below deisplays Single

Input mode.

Global BW Limit

This displays the current bandwidth. Pressing on the BW button brings up the T

create custom BW limit filters.

est Point and Bandwidth Manager, where you can set and

Sources

The SDLA processing and analysis operate only on waveforms that are displayed on the oscilloscope. You can select from actively

acquired channel signals, Math waveforms or reference waveforms. For a live acquired waveform, select its channel number. To recall a

reference waveform, select File>Reference Waveform Controls in the oscilloscope menu. Then press Recall in the Reference menu to

bring up the Recall browser.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 24

Page 25

Components and menus

De-embed Block

The De-embed Block contains the circuit models that represent the actual hardware probe, fixtures, etc. that were used to acquire the

waveforms with the oscilloscope acquisition system. Here, you can define the ef

and measurement hardware upon the DUT signal, re-normalize the S-parameter reference impedance, perform singled-ended to mixed

mode conversion, reach the Block Configuration menu for Thru, File, RLC and T-line options, add and configure High Z, SMA probes, or

interposer, and many other tasks. For more information, see the De-embed/Embed Menu.

fects of the fixture, probe, scope and other acquisition

Test Points

Test points output waveforms that are displayed live on the oscilloscope. You may bring up the Test Point and Bandwidth Manager by

pressing a test point on the system circuit diagram on the Main Menu. From here, you can configure the individual output waveforms and

save test point filters. (When Dual Input mode has been selected on the Main Menu, you can also select test point modes.) You can also

set a Global BW limit and create a custom BW limit filter. For more information, see Test Point and Bandwidth Manager.

Tx Block (Transmitter Modeling Block)

The Tx Block represents the model of the serial data link transmitter that is driving both the Measurement Circuit model and the Simulation

Circuit model. Pressing Tx on the Main Menu brings up the Tx Configuration Menu, where you can select files and view plots. It also gives

you access to the Tx Emphasis Menu, where you can select emphasis, de-emphasis or pre-emphasis filters, read from FIR filters and

make other choices. For more information, see the Tx Block Overview.

Embed Block

The Embed Block allows the user to “insert” the channel based on its S-parameters, as a lossless transmission line, or as an RLC model,

in order to observe the waveforms at the various test points on the Simulation Circuit model. Pressing Embed on the Main Menu brings up

the De-embed/Embed Menu,. Use this for the same tasks as the De-embed Block above, except you cannot configure a probe.

Rx Block (Receiver Modeling block)

The Rx Block represents the model for the serial data link receiver for the simulation side of the circuit drawing. Pressing Rx on the

Main Menu brings up the Rx Configuration Menu. Here, you may apply CTLE equalization, perform clock recovery, and apply FFE/DFE

equalization. You also configure PAM-4 versus NRZ Rx modeling in this block. Alternatively, you may set up an AMI model that uses

imported equalization files to emulate actual silicon. For more information, see the Rx Block Overview. Note: the Rx load is defined in the

Embed Block, not the Rx Block.

Apply, Config and Analyze buttons

Apply

By default, this computes test point filters and applies them to the scope. If any SDLA configuration is changed, run Apply to get updated

results. Some configuration options are available, as described below.

Analyze

Pressing Analyze performs waveform analysis with the DPOJET/JNB application. The SDLA application is put into a sleep state and then

the DPOJET/JNB application is started with the test point signal(s), and the recovered data and clock signals selected for analysis. The

SDLA software may configure (RT only) the DPOJET application to analyze the link quality with eye diagrams and jitter measurements.

Note that you must first press the Apply button and wait for filter processing to complete before pressing the Analyze button. The

DPOJET/JNB application must be installed for this transfer to work.

Config

This button (RT only) lets you configure the action of the Apply button as well as the Analyze button with DPOJET, and to determine

whether to use a new or a previously acquired waveform. Press here for Apply and Analyze button configuration options.

Plot button

Press to show the results of running the enabled test points. Press here for more about plots.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 25

Page 26

Default button

Components and menus

Press to restore the SDLA V

isualizer system to its default settings.

Save button

Press to save the current SDLA Visualizer setup to a file with a .sdl file extension in the directory SDLA\Save recall.

Note: Only the SDLA setup is saved and recalled, not the entire oscilloscope setup.

Recall button

Press to recall saved setup files and to return the software to a previous configuration.

SEE ALSO:

• Product Overview

• Running a T

• Solving Problems with SDLA Visualizer

est: Recommended Order

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 26

Page 27

Test points

Test points

Test point and bandwidth manager (RT only)

SDLA Visualizer provides up to 12 test points (when using REF for two), including four test points that can be moved on the schematic

drawing. Up to six test point outputs are viewable on the scope graticule at one time (math plus reference). Press here for a Table of Test

Point Descriptions.

Note: For a conceptual overview of how test points work, see T

Test point Position Description

Tp1 Main Measurement circuit loading the Tx block output

Tp2 Main Simulation circuit loading the Tx block output,

Tp3 Main Rx block input. Simulation circuit loading the Tx block

est Point Locations.

measurement circuit de-embedded

output, measurement circuit de-embedded

Tp4 Rx Eq Data Data output of the Rx block after equalization

Tp5 Rx Eq Clock Test point for the recovered clock output of the Rx block

Tp6 De-embed Block Movable test point with the measurement circuit loading the

Tx block output

Tp7 De-embed Block Movable test point with the measurement circuit loading the

Tx block output

Tp8 Embed Block Movable test point with the simulation circuit loading the Tx

block output, measurement circuit de-embedded

Tp9 Embed Block Movable test point with the simulation circuit loading the Tx

block output, measurement circuit de-embedded

Tp10 CTLE CTLE output

Table continued…

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 27

Page 28

Test points

Test point Position Description

Tp11 Tx Thevenin equivalent voltage of the Transmitter model

Tp12 Tx Test point for the output of the Tx Emphasis block (if on)

The Test Point and Bandwidth Manager is reached by pressing any test point on the Main Menu. Use this to configure the individual output

waveforms, to save test point filters, to set the Global BW limit or to create a custom BW limit filter

if Dual Input is selected on the Main Menu. (If Single Input is selected, the Select Tp Mode column will not appear.) Scroll down for

descriptions of each feature.

. You can also select test point modes

Tp On/Off

Controls which of the six (4 math and 2 reference) active test point waveforms are on or of

available Math functions or a Ref memory waveform in the oscilloscope. If the button is off, then the waveform on the oscilloscope screen

is turned off. If the button is on, then the waveform on the oscilloscope screen is turned on.

f. Each radio button lists the name of one of the

Map Tp to Math

This drop-down menu allows a specific test point to be assigned to a math function of Math1, Math2, Math3, or Math4. The same test point

may be assigned to more than one math slot.

Note: SDLA only processes and creates test point filters for the enabled test points. An enabled test point is a Tp that has been

mapped to a Math or Ref waveform, and the corresponding Math or Ref is turned on.

Select Tp Mode

This column is only visible when Dual Input has been selected on the Main Menu.

This system maintains full 4-port modeling. Therefore, the test points are dif

(test point modes) to view. The options are:

• A: the waveform on the upper line of the test point

• B: the waveform on the lower line

• A – B: the differential waveform and

• (A + B )/2: the common mode waveform.

ferential, and each contains a set of four possible waveforms

Label

A label for the test point waveform can be entered into this box. It will appear on the oscilloscope screen along with the waveform.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 28

Page 29

Test points

Save Filters

ou can save each test point filter into the file folder you specify by pressing the Save button next to the test point label. For more

Y

information, see, Saving Test Points.

Filter Scaling Factor

Filter Scaling Factor is located at the bottom of the configuration menu in the single input case only. It scales the test point filter coefficient

according to the value.

The small square check box is used to enable or disable the Scaling Factor. The Scaling Factor value is not effected whether the check

box is on or not.

After the scaling factor is enabled and the main menu Apply is finished, the scaled filter coef

scaling factor is between 20% to 200%. The default is 90%.

ficient value can be saved. The range of the

Plotting Test Points

To plot test point transfer functions, return to the Main Menu and press Plot. Magnitude, Phase, Impulse and Step graphs are available.

It is useful to always check these plots AFTER the Apply button on the Main Menu has been pressed, in order to verify that the results

appear as expected. This helps ensure that no errors were made in setting up the configuration of the S-parameter blocks throughout the

system.

For cases where the auto bandwidth limit setting has been used (see below), the plot will reveal whether or not the auto bandwidth limit

is sufficient. If not, you may select Custom bandwidth and specify a more appropriate bandwidth limit filter. Then press Apply once more,

and re-check the plots.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 29

Page 30

Test points

Global Bandwidth Limit

This allows you to set up how the global BW limit filter will be applied to all test point waveforms. Under the Global Bandwidth Limit label,

three options are available, including the option to create a custom filter

• None. No bandwidth limit filter will be applied to test points.

• Auto. All test point transfer functions will be checked. The lowest frequency having gain of +14 dB from the DC gain will be

determined. The bandwidth limit filter will be set to the cutoff frequency value.

• Custom. Allows you to create a bandwidth limit filter. The Custom option is most useful when the Auto bandwidth filter is not

appropriate for your input data, or your test has specific bandwidth requirements. For more information, see Creating a Custom

Bandwidth Filter.

.

Delay

This allows you to control how SDLA Visualizer handles absolute and relative delay for the test points. By default, the absolute delay is

removed.

Keep Delay: The absolute delay between all test point waveforms is maintained.

Remove Delay: This is the default setting. The absolute delay of the test point filters is removed, so that the test point waveforms all have

the same events close to being aligned in time.

Adjust Delay: This button is only visible when the Remove Delay radio button is selected. Pressing that will bring up the Test Point Filter

Delay Slider.

Test Point Filter Delay Sliders

The Delay Slider menu allows the relative delay of each test point filter applied to Math to be adjusted over a range of -1 ns to +1 ns.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 30

Page 31

There are four delay sliders, one for each math waveform on the oscilloscope display.

There are several ways to control the relative delay using a slider:

enter a number in the text edit box next to the slider

•

• drag the slider button with a mouse

• fine position by pressing or holding down the arrow buttons

• course position by pressing or holding down on the space between the arrow button and the slider button.

Test points

Sliders that are assigned to the same test point will operate together, with their delays set to the same value.

As the delay is adjusted, the test point filters will be recalculated and will update live on the oscilloscope display. Hint: to obtain a more

lively interaction, you can make the record length shorter temporarily while setting up delay.

SEE ALSO:

• Understanding Test Points

• Creating a Custom Bandwidth Limit Filter

• Saving Test Point Filters (Transfer Function)

Test point and bandwidth manager (Sampling only)

SDLA Visualizer provides up to 12 test points (when using REF for two), including four test points that can be moved on the schematic

drawing. Up to six test point outputs are viewable on the scope graticule at one time (math plus reference).

Note: For a conceptual overview of how test points work, see T

est Point Locations.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 31

Page 32

Test points

Test point Position Description

Tp1 Main Measurement circuit loading the Tx block output

Tp2 Main Simulation circuit loading the Tx block output,

measurement circuit de-embedded

Tp3 Main Rx block input. Simulation circuit loading the Tx block

output, measurement circuit de-embedded

Tp4 Rx Eq Data Data output of the Rx block after equalization

Tp5 Rx Eq Clock Test point for the recovered clock output of the Rx block

Tp6 De-embed Block Movable test point with the measurement circuit loading the

Tx block output

Tp7 De-embed Block Movable test point with the measurement circuit loading the

Tx block output

Tp8 Embed Block Movable test point with the simulation circuit loading the Tx

block output, measurement circuit de-embedded

Tp9 Embed Block Movable test point with the simulation circuit loading the Tx

block output, measurement circuit de-embedded

Tp10 CTLE CTLE output

Tp11 Tx Thevenin equivalent voltage of the Transmitter model

Tp12 Tx Test point for the output of the Tx Emphasis block (if on)

The Test Point and Bandwidth Manager is reached by pressing any test point on the Main Menu. Use this to configure the individual output

waveforms, to save test point filters, to set the Global BW limit or to create a custom BW limit filter

if Dual Input is selected on the Main Menu. (If Single Input is selected, the Select Tp Mode column will not appear.) Scroll down for

descriptions of each feature.

. You can also select test point modes

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 32

Page 33

Tp On/Off

Test points

Controls which of the six (4 math and 2 reference) active test point waveforms are on or of

available Math functions or a Ref memory waveform in the oscilloscope. If the button is off, then the waveform on the oscilloscope screen

is turned off. If the button is on, then the waveform on the oscilloscope screen is turned on.

f. Each radio button lists the name of one of the

Map Tp to Math

This drop-down menu allows a specific test point to be assigned to a math function of Math1, Math2, Math3, or Math4. The same test point

may be assigned to more than one math slot.

Note: SDLA only processes and creates test point filters for the enabled test points. An enabled test point is a Tp that has been

mapped to a Math or Ref waveform, and the corresponding Math or Ref is turned on.

Select Tp Mode

This column is only visible when Dual Input has been selected on the Main Menu.

This system maintains full 4-port modeling. Therefore, the test points are dif

(test point modes) to view. The options are:

• A: the waveform on the upper line of the test point

• B: the waveform on the lower line

• A – B: the differential waveform and

• (A + B )/2: the common mode waveform.

ferential, and each contains a set of four possible waveforms

Label

A label for the test point waveform can be entered into this box. It will appear on the oscilloscope screen along with the waveform.

Save Filters

You can save each test point filter into the file folder you specify by pressing the Save button next to the test point label. For more

information, see, Saving Test Points.

Filter Scaling Factor

Filter Scaling Factor is located at the bottom of the configuration menu in the single input case only. It scales the test point filter coefficient

according to the value.

The small square check box is used to enable or disable the Scaling Factor. The Scaling Factor value is not effected whether the check

box is on or not.

After the scaling factor is enabled and the main menu Apply is finished, the scaled filter coef

scaling factor is between 20% to 200%. The default is 90%.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 33

ficient value can be saved. The range of the

Page 34

Test points

Plotting Test Points

o plot test point transfer functions, return to the Main Menu and press Plot. Magnitude, Phase, Impulse and Step graphs are available.

T

It is useful to always check these plots AFTER the Apply button on the Main Menu has been pressed, in order to verify that the results

appear as expected. This helps ensure that no errors were made in setting up the configuration of the S-parameter blocks throughout the

system.

For cases where the auto bandwidth limit setting has been used (see below), the plot will reveal whether or not the auto bandwidth limit

is sufficient. If not, you may select Custom bandwidth and specify a more appropriate bandwidth limit filter. Then press Apply once more,

and re-check the plots.

Global Bandwidth Limit

This allows you to set up how the global BW limit filter will be applied to all test point waveforms. Under the Global Bandwidth Limit label,

three options are available, including the option to create a custom filter

• None. No bandwidth limit filter will be applied to test points.

• Auto. All test point transfer functions will be checked. The one that crosses the -14 dB point at the lowest frequency will be determined.

The bandwidth limit filter cutoff frequency will be set to that value.

• Custom. Allows you to create a bandwidth limit filter. The Custom option is most useful when the Auto bandwidth filter is not

appropriate for your input data, or your test has specific bandwidth requirements. For more information, see Creating a Custom

Bandwidth Filter.

.

Delay

This allows you to control how SDLA Visualizer handles absolute and relative delay for the test points. By default, the absolute delay is

removed.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 34

Page 35

Test points

Keep Delay: The absolute delay between all test point waveforms is maintained.

Remove Delay: This is the default setting. The absolute delay of the test point filters is removed, so that the test point waveforms all have

the same events close to being aligned in time.

Adjust Delay: This button is only visible when the Remove Delay radio button is selected. Pressing that will bring up the T

Delay Slider.

est Point Filter

Test Point Filter Delay Sliders

The Delay Slider menu allows the relative delay of each test point filter applied to Math to be adjusted over a range of -1 ns to +1 ns.

There are four delay sliders, one for each math waveform on the oscilloscope display.

There are several ways to control the relative delay using a slider:

enter a number in the text edit box next to the slider

•

• drag the slider button with a mouse

• fine position by pressing or holding down the arrow buttons

• course position by pressing or holding down on the space between the arrow button and the slider button.

Sliders that are assigned to the same test point will operate together, with their delays set to the same value.

As the delay is adjusted, the test point filters will be recalculated and will update live on the oscilloscope display. Hint: to obtain a more

lively interaction, you can make the record length shorter temporarily while setting up delay.

SEE ALSO:

• Understanding Test Points

• Creating a Custom Bandwidth Limit Filter

• Saving Test Point Filters (Transfer Function)

Saving test points

There is a separate Save button on the Test Point and Bandwidth Manager that is associated with each of the four possible test points that

may be active. Simply press on Save next to the test point you are interested in.

In order to save a test point that was not enabled before Applying the model, you must return to the Main Menu and press Apply to

recompute the test point filters.

est point filters are intended to work on oscilloscopes that have a 64-bit processor. However, if you wish to export these

Note: T

filters for use with a scope that has a 32-bit processor, then you’ll need to edit the file to make it compatible. For more information,

see Exporting filters for use with a 32-bit oscilloscope. You can also press ? on the Test Point and Bandwidth Manager.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 35

Page 36

Test points

Pressing any Save button in the T

specify a new folder:

est Point and Bandwidth Manager will open up a folder browser. You may then either select a folder or

Dual Input Mode (RT only)

If you have selected Dual Input on the Main Menu, then SDLA V

each contain one of the test point filters. One of the files will contain all eight of the filters. If using math as the input source, make sure the

test point is output to a different math.

The test point filter filename convention for Dual Input mode is:

isualizer will save 9 files into the specified folder. Eight of the files will

<foldername>_Tp<X><mode><source>.flt. File details.

<Foldername>: entered by user

<X>: test point number

<mode>: either A, B, Diff, or Cm

<source>: either Src1 or Src2, where Src1 relates to src1 on the Main Menu, and Src2 relates to src2.

A test point single file contains ASCII characters. The first character is “#” to identify a comment line. Numerous comments can be

included. Variables and parameters can be included in comment lines of these forms:

# TpX differential test point filters

# [ DELAY ] 1e-09 is the delay parameter same as current arbflt format.

# [ SAMPLERATE ] 50e9

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 36

Page 37

Eight lines contain the coefficients for the 8 filters, i.e.:

Line 1: TpXASrc1

Line 2: TpXASrc2

Line 3: TpXBSrc1

Line 4: TpXBSrc2

Test points

Line 5: TpXDif

Line 6: TpXDiffSrc2

Line 7: TpXCMSrc1

Line 8: TpXCMSrc2

fSrc1

Note: For future releases of scope firmware it is planned that this file may be loaded into a new math function that can apply the

filters according to the selected mode and sources.

Single Input Mode

For Single Input mode, only one filter file is saved for each test point when you press Save on the T

is for mode A-B, differential. You may save test point filters to a file with the following name format: <filename>.flt.

The ASCII file format contains comment lines that start with a “#”. A line with [DELAY] <value> may be present in the file. The filter line

contains a sample rate number followed by a “;” and the coefficients separated by commas.

SEE ALSO:

• Exporting Filters to Use with a 32-bit Oscilloscope

• Test Point and Bandwidth Manager

• Understanding Test Points

est Point and Bandwidth Manager. This

Exporting filters for use with a 32-bit sampling oscilloscope

Test point filters are saved to an arbflt ASCII file format, in order to allow them to be loaded into the oscilloscope’s arbflt function in the

math menu. There is a slight difference between filters used by RT (64-bit) scopes and filters used by sampling (32-bit) scopes. SDLA

automatically selects the appropriate type of filter based on whether the Source selection on the main menu specifies Sampling.

However, if you later wish to use filters created for a RT scope on a sampling scope you’ll need to edit the file to make it compatible.

The file format contains lines with comments preceded by the # symbol.

Next, there is a line that contains the sample rate value for the first entry, followed by “;” followed by the filter coefficients for the remaining

entries separated by commas. (For further information on the filter file format, see Understanding Test Points.)

Note: If the radio button is selected on the T

sample period.

To edit the file:

1. Open it up using Windows Notepad.

2. Add a comment line at the top of the file in order to document what sample rate the filter was designed to operate at. Enter # <sample

rate value> where the sample rate value is the first element of the filter coef

3. Next, on the filter coefficient line, edit the first sample rate number to be an @ symbol. The @ symbol indicates that the filter will

operate at all sample rates with the same set of coefficients.

Make sure that if you use this filter on a 32-bit scope, that the oscilloscope is set to the sample rate specified in the comment line

above. The arbflt math function was designed to run only at the sample rate in the coefficient line and will normally blank out the waveform

est Point and Bandwidth Manager, then the waveform timing may be off by one

ficient line.

SDLA Visualizer Serial Data Link Analysis Visualizer Software Application Help 37

Page 38

Test points

if the oscilloscope sample rate is changed to some other value. However, when the @ symbol is present, then the filter will run at all

sample rates, but its response will be normalized to the sample rate. In other words, the filter will only work as desired when the scope is

set to the sample rate the filter was designed for

For example:

# Tp1 filter

# sample rate 50GS/s

@ <coeff1>, <coeff2>, <coeff3>, ... <coeffn>

.

CAUTION: Note that if you are using this filter with a scope with a 32-bit processor

(interpolated sample rate), then the sample rate readout on the screen is not actually the interpolated sample rate, but rather is

the base sample rate before the interpolation. The filter would be operating at the interpolated sample rate.

In order for the filter with an @ as the sample rate to operate with the correct response, the interpolated sample rate must be set

to the rate for which the filter was designed. The user must manually do this when exporting to a scope using a 32-bit processor.

You may determine the IT sample rate by computing 1 divided by the sample interval readout in seconds per point on the scope

display.

, and the scope is operated in IT mode

Save test point filters for multiple sample rates (RT only)

On real-time scopes, there may be a need to save a single T

Filter for one sample rate. The following steps can be used to combine multiple Test Point Filters for each sample rate to a single Test Point

Filter that covers all the sample rates that are needed.

To cover m number of sample rates SR1, SR2, …., SRm:

1. Set the sample rate of SDLA input to SR1, run SDLA to create the Test Point Filter for Tp<x>. Rename it to sdlaTpxxxx.flt.

2. Set the sample rate of SDLA input to SR2, run SDLA to create the Test Point Filter for Tp<x>. Copy the sample rate and coefficient part

of sdlaTp<x>.flt and paste it to the end of sdlaTpxxxx.flt.