Page 1

Service Manual

1740A Series, 1750A Series, & 1760 Series

Waveform/Vector Monitors

S/N B020000 and Above

070-8469-03

This document applies to firmware version 2.00

and above.

Warning

The servicing instructions are for use by qualified

personnel only. To avoid personal injury, do not

perform any servicing unless you are qualified to

do so. Refer to all safety summaries prior to

performing service.

www.tektronix.com

Page 2

Copyright © Tektronix, Inc. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes

that in all previously published material. Specifications and price change privileges reserved.

Tektronix, Inc., P.O. Box 500, Beaverton, OR 97077

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

Page 3

WARRANTY

Tektronix warrants that the products that it manufactures and sells will be free from defects in materials and

workmanship for a period of three (3) years from the date of shipment. If a product proves defective during this

warranty period, Tektronix, at its option, either will repair the defective product without charge for parts and labor,

or will provide a replacement in exchange for the defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration

of the warranty period and make suitable a rrangements for the performance of service. Customer shall be

responsible for packaging and shipping the defective product to the service center designated by Tektronix, with

shipping charges prepaid. Tektronix shall pay for the return of the product to Customer if the shipment is to a

location within the country in which the Tektronix service center is located. Customer shall be responsible for

paying all shipping charges, duties, taxes, and any other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or ina dequate

maintenance and care. Tektronix shall not be obligated to furnish service under this warra nty a) to repair damage

resulting from attempts by personnel other than Tektronix representatives to install, repair or servic e the product;

b) to repair damage resulting from improper use or connection to incompatible equipment; c) to repair any

damage or malfunction caused by the use of non-Tektronix supplies; or d) to service a product that has been

modified or integrated with other products when the effect of such modification or inte g ration increases the time

or difficulty of servicing the product.

THIS W ARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS

OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX’

RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND

EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS W ARRANTY.

TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL,

INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR

THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Page 4

Page 5

Table of Contents

Specifications

General Safety Summary ix...................................

Service Safety Summary xi....................................

Preface xiii...................................................

Contacting Tektronix xiv.............................................

Product Description 1--1..............................................

Input Format 1--13....................................................

Installation 2--1.....................................................

Standard Accessories 2--1.............................................

Mechanical Installation 2--2...........................................

Electrical Installation 2--8.............................................

Rear Panel Connectors 2--9............................................

Remote Connector 2--10...............................................

Remote Connector Converter 2--12.......................................

RS232 Connector 2--13................................................

Installing Software 2--14...............................................

Loading Software 2--16................................................

Calibrating New Features 2--20..........................................

Special Recovery for Power Loss During the Execution of UPGRADE 2--20.....

Operating Information

Theory of Operation

Getting Started 2--23..................................................

Operating Instructions 2--24............................................

General Menu Information 2--25.........................................

Functional Overview 2--27.............................................

Displaying a Signal 2--29...............................................

Block Diagram Description 3--1..................................

Block Diagram 1: Input and Waveform Monitor 3--1........................

Block Diagram 2: Vector -- SCH -- Component 3--3.........................

Block Diagram 3: Microprocessor and Line Rate Controller 3--5..............

Circuit Theory 3--7............................................

Diagrams <1> and <2> Channel A and Channel B Inputs 3--7...............

Diagram <3> Vertical Input 3--8........................................

Diagram <4> Vertical Output 3--10.......................................

Diagram <5> Horizontal 3--11..........................................

Diagram <6> Microprocessor 3--12......................................

Diagram <7> Dynamic Control 3--14.....................................

Diagram <8> Readout 3--15............................................

Diagram <9> DACS & Serial 3--16......................................

Diagram <10> Remote & 1760 Series / XROM Bus Connectors 3--16...........

1740A Series, 1750A Series, & 1760 Series Service Manual

i

Page 6

Table of Contents

Diagram <11> Z-Axis & Control 3--17....................................

Diagram <12> Front Panel 3--18.........................................

Diagram <13> DACs & Digital Control 3--18..............................

Diagram <14> Subcarrier Regenerator 3--19...............................

Diagram <15> Phase Shifter 3--21.......................................

Diagram <16> Demodulator 3--22.......................................

Diagram <17> Internal SCH 3--23.......................................

Diagram <18> Reference SCH 3--26.....................................

Diagram <19> Component Inputs, Transcoders, & RGB Outputs 3--28..........

Diagram <20> Component Control and Switching (1760 Series Only) 3--30......

Diagram <21> Low Voltage Power Supply 3--32............................

Diagram <22> High Volts Power Supply 3--35..............................

Performance Verification

Recommended Equipment List 4--1.....................................

Performance Check Procedure Short-Form Reference 4--6...................

Performance Check Procedure 4--19......................................

Adjustments

Maintenance

Required Equipment 5--1..............................................

Initial Setup 5--9....................................................

Functional Description of PC Display 5--10................................

Circuit Board Adjustment Locations 5--12.................................

Waveform Illustrations 5--15............................................

Preventing ESD 6--1.................................................

Preventive Maintenance 6--1...........................................

Performance Checks and Adjustments 6--2................................

Inspection and Cleaning 6--2...........................................

Replacing the Line Fuse 6--5...........................................

Troubleshooting 6--5.................................................

Corrective Maintenance 6--12....................................

Circuit Boards 6--12...................................................

Mechanical Disassembly/Assembly 6--13..................................

Removing the Bezel 6--13..........................................

Replacing the Graticule Light 6--14...................................

Removing the CRT 6--16...........................................

Removing the Rear Panel 6--19......................................

Removing the Front Panel and the Front Panel Circuit Board 6--21..........

Removing the Main Board 6--22.....................................

Removing the Power Supply Board 6--24..............................

Removing the Vector Board 6--25....................................

Removing the SCH Board

(1750A Series & 1760 Series Option SC only) 6--26..............

Removing the Component Board

(1760 Series only) 6--26.....................................

Repackaging 6--27....................................................

ii

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 7

Options and Accessories

Options 7--1........................................................

Standard Accessories 7--1.............................................

Optional Accessories 7--2.............................................

Replaceable Electrical Parts

Parts Ordering Information 8--1.........................................

Using the Replaceable Electrical Parts List 8--1............................

Diagrams/Circuit Board Illustrations

Replaceable Mechanical Parts

Parts Ordering Information 10--1.........................................

Using the Replaceable Mechanical Parts List 10--1..........................

Table of Contents

Glossary

Index

1740A Series, 1750A Series, & 1760 Series Service Manual

iii

Page 8

Table of Contents

List of Figures

Figure 2--1: Dimensions of the 1700F00 plain cabinet 2--2............

Figure 2--2: 1700F02 portable cabinet 2--3.........................

Figure 2--3: Rear view showing the securing screws 2--4.............

Figure 2-- 4: The WFM7F05 side-by-side rack adapter 2-- 5...........

Figure 2--5: A WFM7F05 with a blank front panel (1700F06) 2--5.....

Figure 2--6: WFM7F05 rack mount cabinet with a 1700F07 utility

drawer 2-- 6...............................................

Figure 2--7: Custom installation of an instrument 2--7...............

Figure 2--8: Rear panel connectors 2--9............................

Figure 2--9: Rear panel REMOTE connector. 2--10...................

Figure 2--10: Replacement adapter for 1740/1750 2--12...............

Figure 2--11: Rear panel RS232 connector 2--13.....................

Figure 2-- 12: Standard and alternate hookups for the 9-pin

connector 2--16.............................................

Figure 2-- 13: Standard and alternate hookups for 25-Pin PC

Connector 2--17.............................................

Figure 2--14: 1760 front panel 2--24................................

Figure 2--15: The CRT menu, with the bezel controls and buttons 2--25.

Figure 3--1: NTSC line count (U24) & color frame 1 SCH field pulse 3--26

Figure 3--2: PAL line count (U24) & color frame 1 SCH field pulse 3--27

Figure 3--3: Pinout of the CRT socket 3--35.........................

Figure 4--1: External Horizontal or RGB/YRGB Cable Adapter 4--4...

Figure 4--2: Remote Sync Cable Adapter 4--5......................

Figure 4-- 3: Audio and Timecode Cable Adapter 4-- 5................

Figure 4--4: Timing Cursor Check 4--16............................

Figure 4--5: Fast DC Restorer Response 4--24.......................

Figure 4--6: R--Y Display 4--27....................................

Figure 4-- 7: Audio Display 4-- 33..................................

Figure 4-- 8: Option Blanking Pulse 4-- 36...........................

Figure 4--9: Bowtie Common Mode Rejection Ratio 4--38.............

Figure 5--1: External horizontal/RGB and YRGB cable adapter 5--5...

Figure 5--2: Remote sync cable adapter 5--5........................

Figure 5-- 3: Audio and Timecode Cable Adapter 5-- 6................

iv

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 9

Table of Contents

Figure 5--4: RS232 cable standard and alternate connections for

9-pin PC connector 5--7.....................................

Figure 5-- 5: RS232 cable standard and alternate hookups for

25-pin PC connector 5--8....................................

Figure 5--6: Typical adjustment procedures PC screen display 5--10....

Figure 5-- 7: A1 Power Supply board 5-- 12..........................

Figure 5--8: A3 Main board 5--12..................................

Figure 5--9: A5 Vector board 5--13.................................

Figure 5--10: A6 SCH board 5--13.................................

Figure 5--11: A7 Component board 5--14...........................

Figure 5--12: Adjusting for thinnest luminance step 5--15.............

Figure 5--13: Matching flat and luminance filter responses 5--15.......

Figure 5--14: Adjusting the NTSC SCH on the oscilloscope 5--16.......

Figure 5-- 15: Matching the SCH dot flipping points 5--16.............

Figure 5-- 16: Adjusting the option blanking pulse 5-- 17...............

Figure 5--17: Adjusting for minimum Bowtie amplitude 5--17..........

Figure 5-- 18: Adjusting Diamond display phase 5--18.................

Figure 6-- 1: Instrument etched circuit board assemblies 6--12..........

Figure 6--2: Removing the CRT bezel 6--13.........................

Figure 6-- 3: Replacing graticule light bulbs 6-- 15....................

Figure 6--4: Removing the CRT 6--17..............................

Figure 6-- 5: Removing the rear panel and Input/BNC assembly 6-- 20...

Figure 6-- 6: Disassembling Input/BNC assembly A4/A4--A1 6-- 20.......

Figure 6-- 7: Removing the front--panel assembly 6-- 21................

Figure 6--8: Front Panel circuit board assembly 6--22.................

Figure 6--9: Screws holding the Main circuit board in place 6--23.......

Figure 6-- 10: Securing screws for the Power Supply circuit 6--24.......

Figure 6--11: Mounting h ardware for the Vector and SCH circuit

boards 6-- 25................................................

Figure 6--12: Component circuit board mounting hardware 6--26......

Figure 6--13: Repackaging a 1740A, 1750A, or 1760 Series

instrument 6--27............................................

Figure 10--1: Exploded View 10--11.................................

1740A Series, 1750A Series, & 1760 Series Service Manual

v

Page 10

Table of Contents

List of Tables

Table 1--1: Waveform vertical deflection 1--3......................

Table 1--2: External reference 1--6..............................

T able 1--3: Waveform horizontal deflection 1--6...................

T able 1--4: Measurement cursors 1--7............................

Table 1--5: RGB/YRGB 1--7....................................

T a b l e 1 -- 6 : C a l i b r a t o r 1 -- 8.....................................

Table 1--7: Vector mode 1--8....................................

Table 1--8: Audio mode 1--9.....................................

Table 1--9: Time code 1--10......................................

Table 1--10: SCH Phase mode (1750 Series and

1760 Option SC Only) 1--10..................................

Table 1--11: Component vector mode (1760 Series Only) 1--12.........

Table 1--12: Lightning mode (1760 Series only) 1--12.................

Table 1--13: Bowtie mode (1760 Series only) 1--13...................

Table 1--14: Transcoded GBR outputs 1--13........................

Table 1--15: CRT display 1--14...................................

Table 1--16: Power source 1--14...................................

T able 1--17: Environmental characteristics 1--14....................

Table 1--18: Physical characteristics 1--15..........................

Table 1--19: Certifications and compliances 1--16....................

T able 2--1: Remote connector 2--1 1................................

Table 2--2: The available display modes 2--27.......................

Table 3--1: Transcoder signal mixing 3--28.........................

Table 3--2: Component display output switching 3--29...............

Table 4--1: Short-Form Performance Check 4--6....................

Table 4--2: Vector cursor readout values 4--17......................

Table 4--3: Audio and Timecode Values 4-- 32.......................

T able 6--1: External inspection check list 6--3......................

Table 6--2: Power supply fault symptoms 6-- 6......................

Table 6--3: Low volts supply voltages 6--6.........................

Table 6--4: Control Circuit Test Points 6--8........................

Table 6--5: Shut down logic levels 6-- 9............................

vi

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 11

Table of Contents

Table 6--6: High Volts Supply Fault Symptoms 6--10.................

Table 6--7: High voltage oscillator test points 6--11..................

Table 6--8: Main Board Plug Connections 6--22.....................

Table 7--1: Power cord identification 7--2.........................

1740A Series, 1750A Series, & 1760 Series Service Manual

vii

Page 12

Table of Contents

viii

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 13

General Safety Summary

Review the following safety precautions to avoid injury and prevent damage to

this product or any products connected to it. To avoid potential hazards, use this

product only as specified.

Only qualified personnel should perform service procedures.

ToAvoidFireor

Personal Injury

Use Proper Power Cord. Use only the power cord specified for this product and

certified for the country of use.

Ground the Product. This product is grounded through the grounding conductor

of the power cord. To avoid electric shock, the grounding conductor must be

connected to earth ground. Before making connections to the input or output

terminals of the product, ensure that the product is properly grounded.

Observe All Terminal Ratings. To avoid fire or shock hazard, observe all ratings

and markings on the product. Consult the product manual for further ratings

information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal, that

exceeds the maximum rating of that terminal.

Do Not Operate Without Covers. Do not operate this product with covers or panels

removed.

Use Proper Fuse. Use only the fuse type and rating specified for this product.

Avoid Exposed Circuitry. Do not touch exposed connections and components

when power is present.

Do Not Operate With Suspected Failures. If you suspect there is damage to this

product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

Provide Proper Ventilation. Refer to the manual’s installation instructions for

details on installing the product so it has proper ventilation.

Symbols and Terms

1740A Series, 1750A Series, & 1760 Series Service Manual

Terms in this Manual. These terms may appear in this manual:

WARNING. Warning statements identify conditions or practices that could result

in injury or loss of life.

ix

Page 14

General Safety Summary

CAUTION. Caution statements identify conditions or practices that could result in

damage to this product or other property.

Terms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the

marking.

WARNING indicates an injury hazard not immediately accessible as you read the

marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

CAUTION

Refer to Manual

WARNING

High Voltage

Protective Ground

(Earth) Terminal

x

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 15

Service Safety Summary

Only qualified personnel should perform service procedures. Read this Service

Safety Summary and the General Safety Summary before performing any service

procedures.

Do Not Service Alone. Do not perform internal service or adjustments of this

product unless another person capable of rendering first aid and resuscitation is

present.

Disconnect Power. To avoid electric shock, switch off the instrument power, then

disconnect the power cord from the mains power.

Use Caution When Servicing the CRT. To avoid electric shock or injury, use

extreme caution when handling the CRT. Only qualified personnel familiar with

CRT servicing procedures and precautions should remove or install the CRT.

CRTs retain hazardous voltages for long periods of time after power is turned off.

Before attempting any servicing, discharge the CRT by shorting the anode to

chassis ground. When discharging the CRT, connect the discharge path to ground

and then the anode. Rough handling may cause the CRT to implode. Do not nick

or scratch the glass or subject it to undue pressure when removing or installing it.

When handling the CRT, wear safety goggles and heavy gloves for protection.

Use Care When Servicing With Power On. Dangerous voltages or currents may

exist in this product. Disconnect power, remove battery (if applicable), and

disconnect test leads before removing protective panels, soldering, or replacing

components.

To avoid electric shock, do not touch exposed connections.

X-Radiation. To avoid x-radiation exposure, do not modify or otherwise alter the

high-voltage circuitry or the CRT enclosure. X-ray emissions generated within

this product have been sufficiently shielded.

1740A Series, 1750A Series, & 1760 Series Service Manual

xi

Page 16

Service Safety Summary

xii

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 17

Preface

Servicing Information

This manual provides servicing information for the 1740A/1750A/1760--Series

of instruments. The 1750A is identical to the 1740A, except that the 1750A--Series makes SCH Phase measurements. The 1760-Series adds component analog

measurement capability to the basic 1740A-Series, and the 1760-Series Option

SC adds the same component analog measurement capability to a 1750A-Series

instrument.

This manual supports both module level (for module exchange) and component

level servicing. Module level servicing uses the block diagram and its descriptions to isolate a problem to the circuits on a particular circuit board. Component

level servicing also uses the theory of operation, schematic diagrams and circuit

board parts locating illustration and cross reference indexes (part location charts).

Specific procedures for troubleshooting and disassembly in this manual should

only be attempted by competent service technicians. Be sure to read and follow

all Warnings and Cautions when performing maintenance.

The last sections of this manual contain the Replaceable Parts Lists, Circuit

Board Illustrations, and Schematic Diagrams needed to isolate and replace faulty

components. Replacement part ordering information can be found in the

Maintenance section of this manual.

Performance Verification

These instruments are designed to be returned to operation within stated

specifications through a PC-based adjustment procedure. The disk holder for this

manual contains two computer disks: 1. A software disk containing instruments

operating software (Version 2.2 or greater). 2. A calibration software disk.

An IBM compatible personal computer (PC) with a DOS 3.3 or higher operating

system, and a 3

readjustment procedure or reload the operating software.

The spare software disk is provided in case the Main circuit board, which

contains the software, requires replacement. In all cases, the operating software

must be Version 2.2 or above to perform the Readjustment Procedure.

The specifications contained in the Specification section of this manual contain

Performance Verification step numbers.

1

/2inch high density floppy drive is required to perform the

1740A Series, 1750A Series, & 1760 Series Service Manual

xiii

Page 18

Preface

Contacting Tektronix

Phone 1-800-833-9200*

Address Tektronix, Inc.

Department or name (if known)

14200 SW Karl Braun Drive

P.O. Box 500

Beaverton, OR 97077

USA

Web site www.tektronix.com

Sales support 1-800-833-9200, select option 1*

Service support 1-800-833-9200, select option 2*

Technical support Email: techsupport@tektronix.com

1-800-833-9200, select option 3*

6:00 a.m. -- 5:00 p.m. Pacific time

* This phone number is toll free in North America. After office hours, please leave a

voice mail message.

Outside North America, contact a Tektronix sales office or distributor; see the

Tektronix web site for a list of offices.

xiv

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 19

Specifications

The tables in this chapter list the specifications for the 1740A, 1750A, and 1760

Series waveform monitors. Items listed in the Performance Requirement column

are generally quantitative, and can be tested by the Performance Verification

procedure in the service manual. Items listed in the Reference Information

column are useful operating parameters that have typical values; information in

this column is not guaranteed.

The second column of the two column format contains all of the descriptive

material about the listed characteristic. The performance verification procedure

step number, used to verify the characteristic, is also in this column. This series

of instruments is designed to operate on both PAL and NTSC standards, so some

of the tolerances are defined in millivolts and IREs; in these dual value tolerances, P AL values appear in parentheses.

Performance Requirements (Req) . Items with this designation are critical to

instrument performance. In most cases, a tolerance and a performance verification step number are listed. However, there are a few areas where instrument

operation verifies that the performance requirement is met.

Product Description

Reference Information (RI). This information about the instrument operation may

have a tolerance listed, but these should be considered as typical, not absolute.

Performance Verification Step. This item identifies the location of the test method

in the Performance Verification procedure.

The specifications listed in the Electrical Specifications portion of these tables

apply over an ambient temperature range of +0 _ Cto+40_C. The rated

accuracies are valid when the instrument is calibrated in an ambient temperature

range of +20 _Cto+30_C.

The 1740A/1750A/1760 Series is a half-rack width by three-rack-unit high

instrument. It is a versatile waveform monitor/vectorscope for composite and

component television signals. Most circuitry and the mechanical components are

shared throughout the series. In addition to NTSC and PAL standard versions, a

dual standard (NTSC/PAL) version is available.

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 1

Page 20

Specifications

These instruments employ a bright, post accelerated CRT with lighted internal

graticule. The parallax free internal graticule structure contains targets and

markings for both the vector and waveform functions. The “Lightning” graticule,

for the 1760 Series, is electronic, in order to keep from complicating the

waveform/vector graticule. Option 74, which uses a white phosphor (P4) CRT, is

available for all three instrument series.

These monitors are microprocessor controlled to provide greater versatility.

Switch settings, affecting the operation of the instrument, are continuously

polled by the processor, with any change in status acted upon immediately.

Current operating conditions are preserved in Non-Volatile Random Access

Memory (NOVRAM), which returns the front panel settings to the current

settings, in the event of power interruption (either accidental or routine power

down).

Many operational measurements are performed on a repetitive basis, and these

instruments provide a method of repeating common measurements by simply

selecting stored measurement settings from a CRT menu list. The common

measurement front panel settings can be stored and named by the user. Measurement specific, front-panel settings can be recalled by pushing the front-panel

Preset Menu button and selecting the desired preset by name or number.

Many functions that were formerly selected by changing internal jumpers and/or

wire straps are now accessible through on screen menu selections. Menus are

selected by pushing the appropriate front panel Menu selection. Menu items are

then selected by pushing one or more of the assignable switches and/or rotating

the assigned front-panel control. Once selected these menu choices are retained

until changed by subsequent reconfiguration.

The front panel provides both assignable switches (located next to the CRT) and

controls (located beneath the CRT), that operate with CRT readout to increase

functionality without cluttering the limited front panel area. Function of these

switches and controls is dictated by the front-panel Display and initial Menu

choices.

The 1740A Series is a full capability waveform/vector monitor that also provides

audio and time code measurements. The 1750A Series has all of the capabilities

of the 1740A Series, with the addition of SCH phase measurements.

The 1760 Series combines component measurements with the composite

capabilities of the 1740A/1750A Series. It incorporates all of the measurements

of the 1740A Series with a full set of component analog measurements. The

assignable cursors, along with the CRT readout can be used for time, voltage,

and phase measurements. The system of Menus and CRT readout simplifies the

configuration of this monitor for measurement or monitoring of signal characteristics.

1- 2

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 21

Specifications

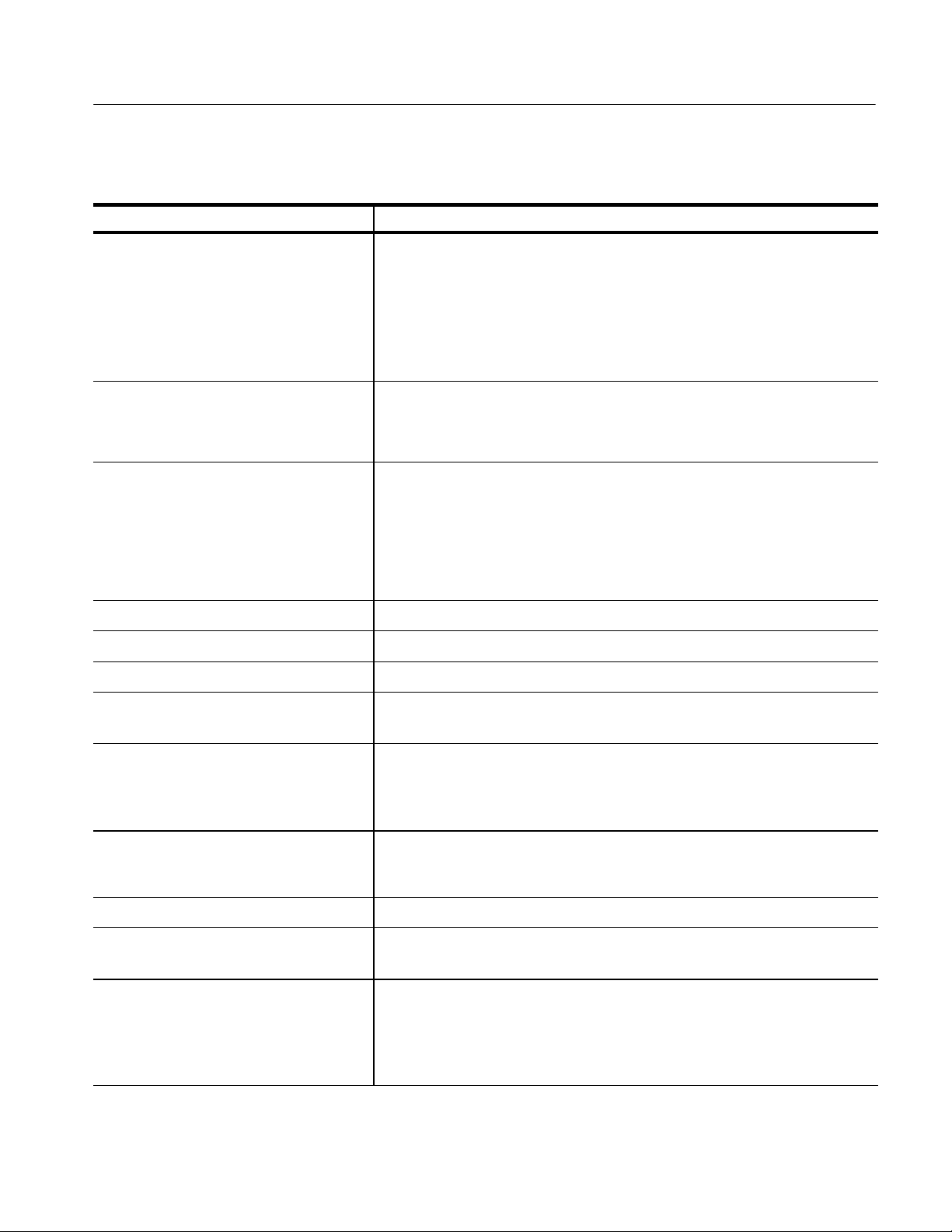

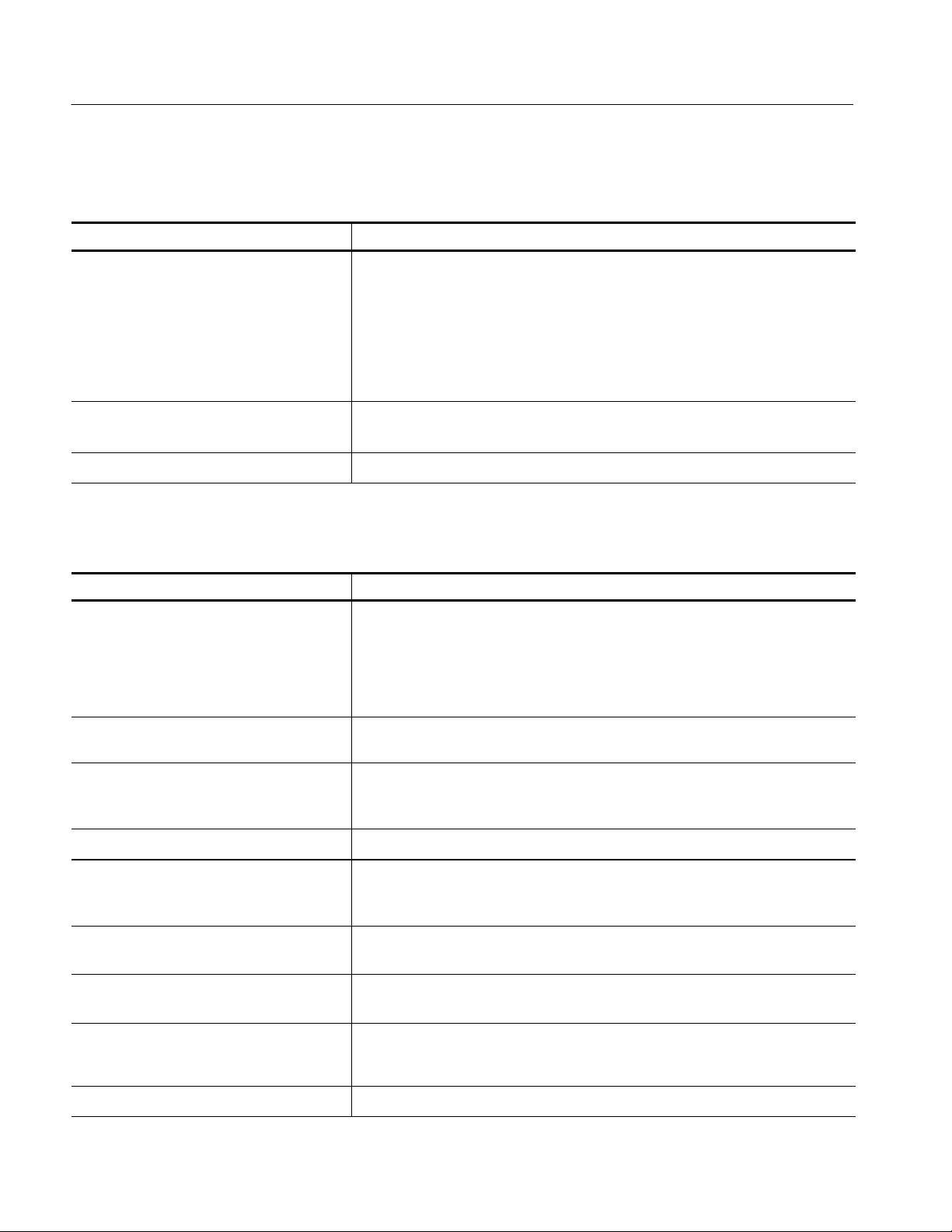

Table 1- 1: Waveform vertical deflection

Characteristic Performance requirement

Deflection Factor Req: 1 V full scale (X1): 1 volt input displayed within 1% of 140 IRE (1.00 VPAL)

X5 Gain: 0.2 volt input displayed within1% of 140 IRE (1.00 VPAL)

X10 Gain: 0.1 volt input displayed within 1% of 140 IRE (1.00 VPAL)

RI: Any one of the 8 inputs

Performance Verification Procedure Step

RI:

1 V , 0.2 V, and 0.1 V from accurate source (VAC) can be made full scale.

V ariable Gain Range Req: 0.2X to 1.4X

Performance Verification Procedure Step

RI:

VAC of 1 V and 0.2 V can be displayed as full scale with appropriate Gain

settings.

:9

:9

Overscan Req: ≤1% variation in baseline of chroma when positioned anywhere between sync tip

and 100% white

RI: X1, X5, or X10 with any variable gain setting

Performance Verification Procedure Step

RI: 1 V peak to peak Modulated Sin

: 16

2

composite video signal.

Frequency and Transient response performance requirements (PR), with any gain

setting, override any overscan specification.

Video Maximum Operating Input Voltage RI: --1.8 V to +2.2 V, (all inputs, A -- B3) DC+peak AC

Absolute Video Input Voltage RI: --8.5 V to +8.5 V ( DC+peak AC)

Video Input DC Impedance RI: ≥20k Ω

Video Input Return Loss RI: Typically ≥40 dB to 6 MHz

RI: Loop through terminated in 75 Ω. Power on or off.

Video Input DC Offset Between Channels Req: ≤1IRE(7mVPAL)

RI: Typically ≤1mV

Performance Verification Procedure Step

RI: Inputs terminated in 75 Ω.

: 4

Video Input Offset Range RI: CHA2, A3, B2, & B3 can be offset from CHA1 or CHB1 by ±350 mV

RI: No signal applied, terminated in 75 Ω and rotate Variable Gain between

minimum and maximum.

Video Input Loop-Through Isolation RI: Typically ≥70 dB

Video Input Crosstalk Between Channels RI: Typically ≥60 dB

RI: All inputs terminated in 75 Ω.

Frequency Response (Flat)

Req: ±2% to 10 MHz (X1 Gain)

±4% to 10 MHz (X5 and X10 Gain), on screen signal (0.2 V or 0.1 V)

RI: Leveled Sinewave Generator

RI: All inputs AC or DC coupling

Performance Verification Procedure Step

1740A Series, 1750A Series, & 1760 Series Service Manual

: 12

1- 3

Page 22

Specifications

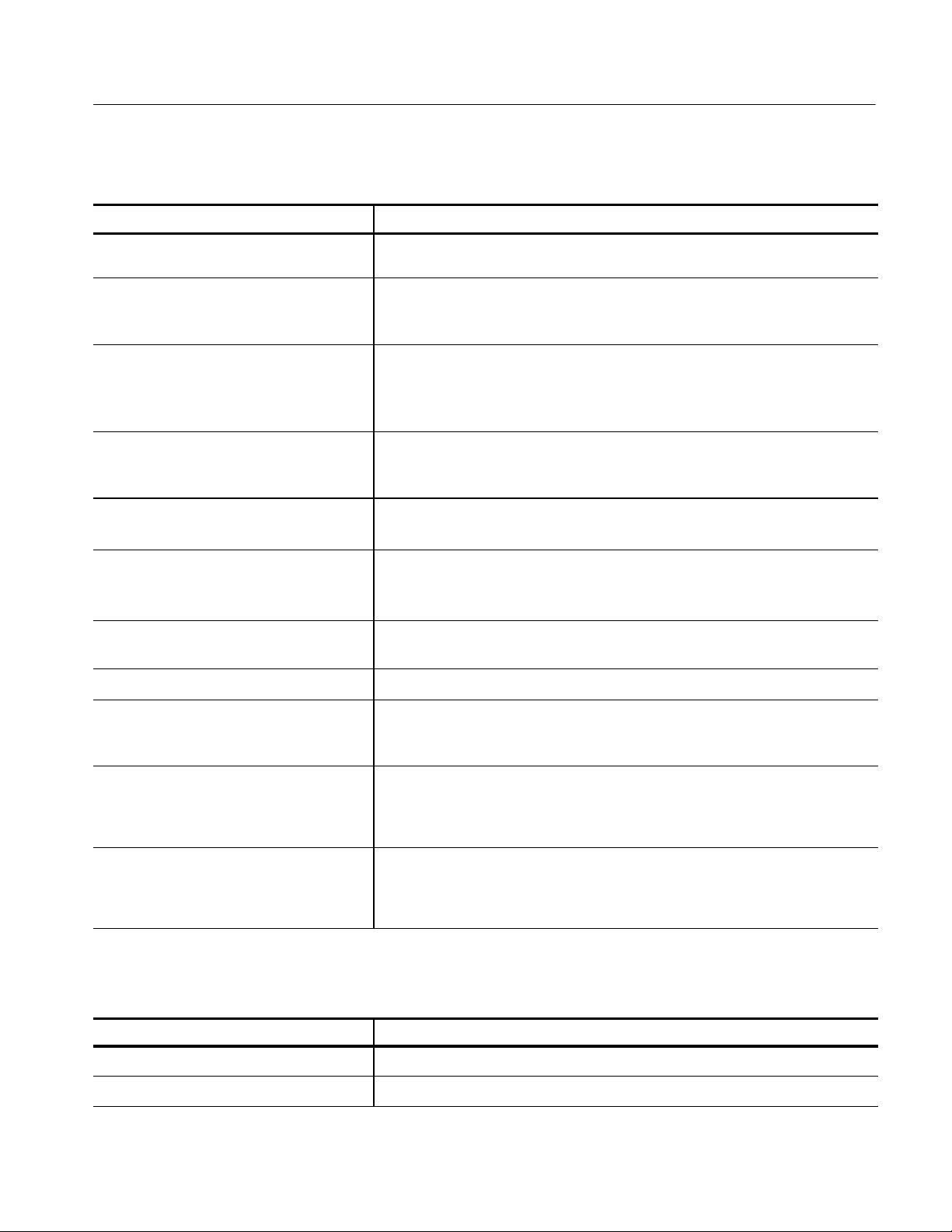

Table 1- 1: Waveform vertical deflection ( Cont.)

Characteristic Performance requirement

Luminance Filter Gain Req: 1 ±1%

RI: Reference is FLAT at 50 kHz

Performance Verification Procedure Step

RI: Leveled Sinewave Generator.

Luminance and chrominance filter offset is typically 1mV.

: 13

Luminance Filter Response Req: ≤3 dB attenuation at 1 MHz

≥40 dB attenuation at F

SC

Performance Verification Procedure Step: 13

RI: Leveled Sinewave Generator.

Luminance Filter Chrominance Rejection

(1745A--1755A-- 1765 only)

Req: ≥34 dB

RI: Leveled Sinewave Generator.

Chrominance Filter Gain Req: 1 ±1%

RI: Ref. is flat at F

(3.58 or 4.43 MHz)

SC

Performance Verification Procedure Step

RI: Leveled Sinewave Generator.

Luminance and chrominance filter offset is typically 1mV.

Chrominance Filter Bandwidth Req: 1.5 MHz ±0.3 MHz

Chrominance Filter Attenuation at 2X F

SC

Differentiated Step Filter Attenuation at 2X F

SC

RI: Centered at F

RI: Leveled Sinewave Generator

RI: ≥25 dB

RI: ≥40 dB

. Passband is typically FSC+ and -- 750 kHz

SC

Transient Response Req: Pulse-to-Bar Ratio 0.99:1 to 1.01:1

RI: Preshoot ≤1%

RI: Overshoot ≤1%

RI: Ringing ≤1%

RI: 2T pulse and bar, any gain setting.

Field-Rate Tilt ≤1%

Req:

RI: Field rate square wave or vertical window signal.

Req: Line-Rate Tilt ≤1%

RI: 25 sbar.

RI: Differential Gain ≤1%

Performance Verification Procedure Step

: 14

: 17

Pix Out Gain Req: 1±3%

RI: Leveled Sinewave Generator and Peak-to-Peak Detector.

Pix Out Frequency Response Req: ±3%to6MHz

RI: A leveled sinewave generator with the output terminated in 75 Ω.

Pix Out Differential Gain RI: ≤1%

1- 4

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 23

Table 1- 1: Waveform vertical deflection ( Cont.)

Characteristic Performance requirement

Pix Out Differential Phase RI: ≤1°

Pix Out Output Impedance RI: 75 Ω

Pix Out Return Loss Req: Typically ≥ 30 dB to 6 MHz

RI: Power on.

Specifications

Pix Out Line Select Strobe RI: (AUD) A DC offset is added to output in line select to bright up the selected

line or lines.

RI: Checked in both 15--line and 1 line.

DC Restorer 60 Hz (50 Hz) Attenuation Req: Slow Mode ≤10%

Fast Mode ≥95%

RI: Back porch or sync tip clamp point is selected through menu.

Performance Verification Procedure Step

RI: 60 Hz (50 Hz) sinewave generator.

: 18

DC Restorer Offset Error Req: ≤1IRE(7 mVPAL)

RI: Typically 3 mV

Performance Verification Procedure Step

RI: No signal applied, terminated in 75 Ω. Rotate Variable Gain between mini-

: 4

mum and maximum.

Fast Settling Time RI: (AUD) ≤6 video lines

Blanking Shift with 10 to 90% APL Change Req: ≤1IRE(7mVPAL)

Blanking Shift with Presence and Absence of

Burst

Performance Verification Procedure Step

RI: APL Bounce signal.

Req: ≤1IRE(7mVPAL)

Performance Verification Procedure Step

RI: Typically 3 mV

RI: Burst on test signal turned off and on.

: 19

: 19

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 5

Page 24

Specifications

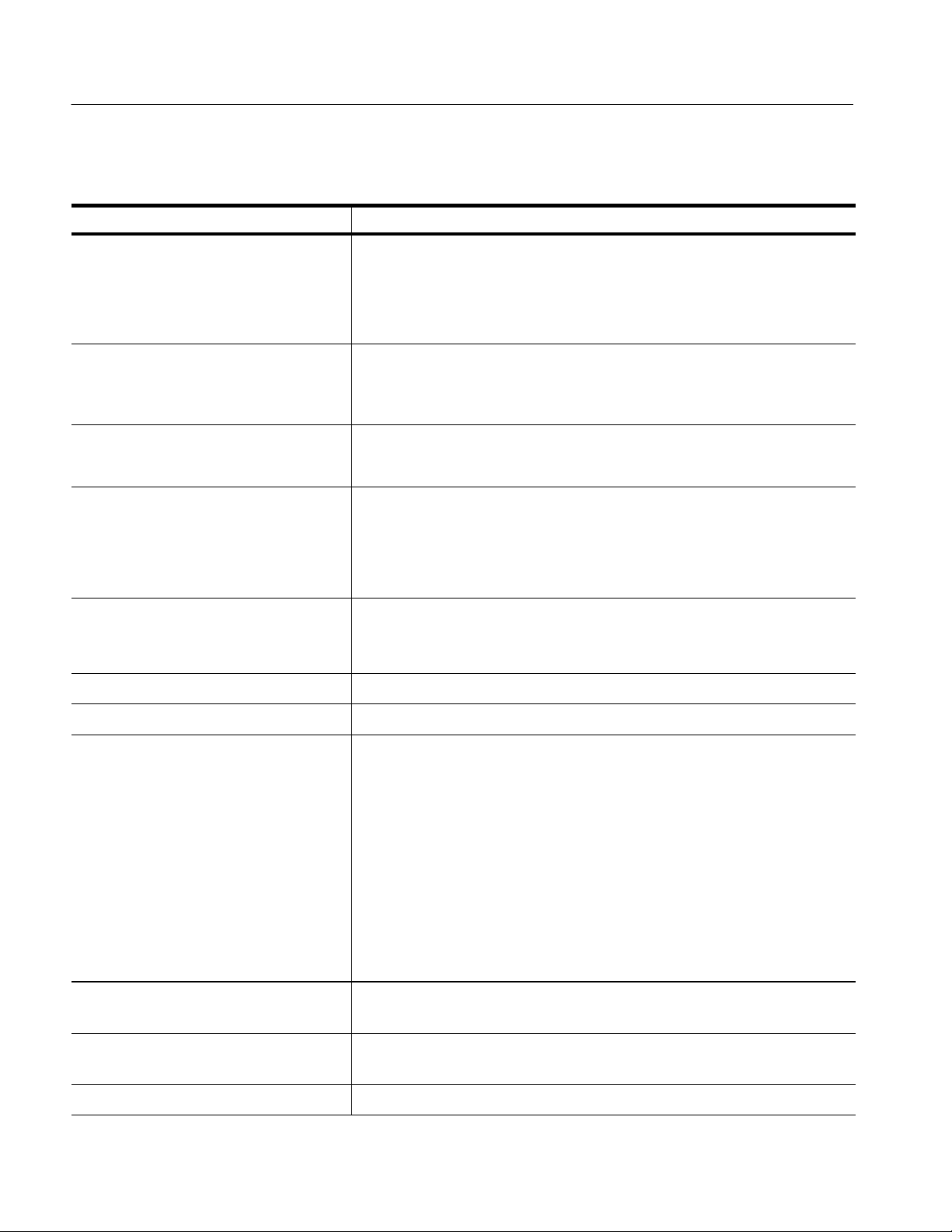

Table 1- 2: External reference

Characteristic Description

Input RI: Composite video or black burst

Maximum Operating Input Voltage RI: --1.8 V to +2.2 V , DC + peak AC

Absolute Maximum Input Voltage RI: --8.5 V to +8.5 V, DC + peak AC

DC Input Impedance RI: ≥20 k Ω

Return Loss RI: Typically ≥40 dB to 6 MHz

Performance Verification Procedure Step

RI: Loop-through terminated in 75 Ω. Power on or off.

Table 1- 3: Waveform horizontal deflection

Characteristic Description

: NO TAG

Sweep Req: Synchronization: Sweep triggered by horizontal and vertical sync pulses

RI: Sweep Length: ≈12 divisions

RI: Sweep freeruns without input

Performance Verification Procedure Step

: 8

Sweep Timing Accuracy Req: 1 Line: 5 s/division ±1%

2 Line: 10 s/division ±1%

RI: Checked over the center 10 div. of sweep.

RI: 1 Field: displays one full field, including field rate sync

2 Field: displays two full fields and the field rate sync between them

Performance Verification Procedure Step

: 7

Sweep Linearity Req: 1 line: ±1%

2 line: ±1%

Performance Verification Procedure Step

RI:

0.5 minor division. Checked over the center 10 divisions of sweep.

:7

Magnified Sweep Accuracy Req: 1 Line: 0.2 s/division ±1%

2 Line: 1.0 s/division ±1%

RI: Checked over the center 10 div. of unmagnified sweep, excluding the first

and last 2 div. of magnified display.

Performance Verification Procedure Step

: 7

Magnified Sweep Linearity Req: 1 line: ±1%

2 line: ±1%

Performance Verification Procedure Step

RI: Checked over the center 10 div. of unmagnified sweep, excluding the first

: 7

and last 2 div. of magnified display.

Horizontal Position Range Req: Any portion of the synchronized sweep can be positioned on screen in all sweep

modes.

: 5

1- 6

Performance Verification Procedure Step

RI:

Color bar signal from serial digital generator in magnified 2--line sweep.

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 25

Table 1- 3: Waveform horizontal deflection ( Cont.)

Characteristic Description

External Horizontal Input Req: 2 divisions/volt, ±2%

RI: Menu is selected and enabled by REMOTE connector ground closure.

Performance Verification Procedure Step

RI: 5 V = 10 divisions

Remote Sync RI: Input Amplitude: TTL level

RI: Frequency: 25 Hz to 100 Hz positive edge-triggered sweep

RI: Enabling Signal: TTL low or ground closure

Performance Verification Procedure Step

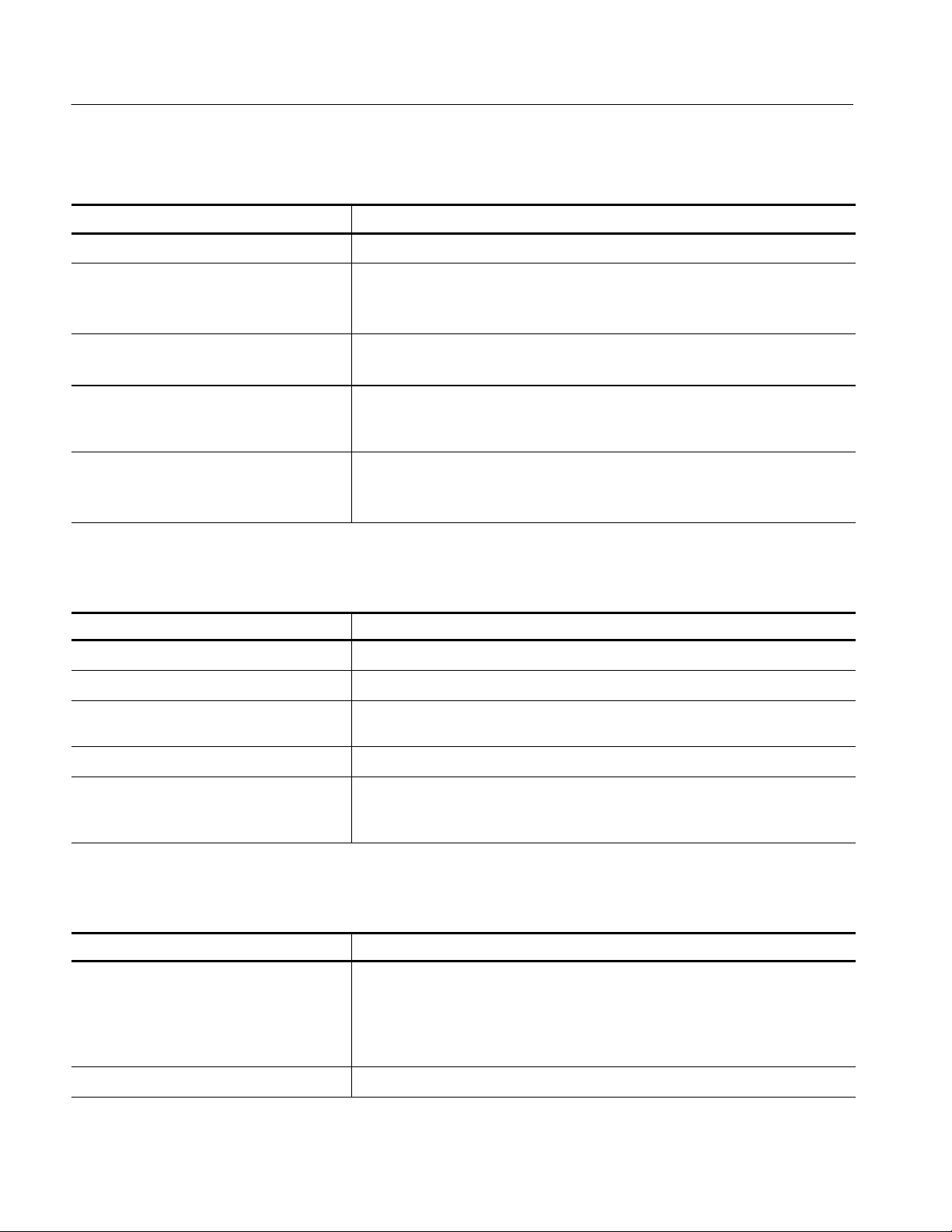

Table 1- 4: Measurement cursors

Characteristic Description

Specifications

: 29

: 33

Waveform Accuracy(P-SPEC-CD) Req: Voltage: 0.5%

Timing: 0.5%, for line rate sweeps

RI: Typically 0.5% for field rate sweeps

Performance Verification Procedure Step

RI: Cursors are calibrated against the VAC.

: 9 & 6

V ector Accuracy(P - SPEC - CD) Req: Gain: ±1.5%

Phase: ±1°

RI: Measured with respect to the Color Bar signal

Performance Verification Procedure Step

: 10

Table 1- 5: RGB/YRGB

Characteristic Description

RGB/YRGB Req: RGB Staircase input gain: 0.8 V/division ±10%

RI: RGB Sweep Length:

1 Field ≈30% of normal

1Line≈ 30% of normal

RI: (AUD) YRGB Sweep Length:

1 Field ≈ 25% of normal

1Line≈ 25% of normal

RI: 2 kHz, 10 V square wave through REMOTE connector RGB Input.

RI: Maximum staircase operating signal: DC signal plus peakAC not to exceed

--12 V to+12 V. Line or field rate sweep.

RI: Peak-to-peak ACsignal not to exceed 12 V .

RI: Sweep Repetition Rate: Field or line rate of displayed video or external

sync signal as selected by the front-panel sweep selection

Performance Verification Procedure Step

: 30

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 7

Page 26

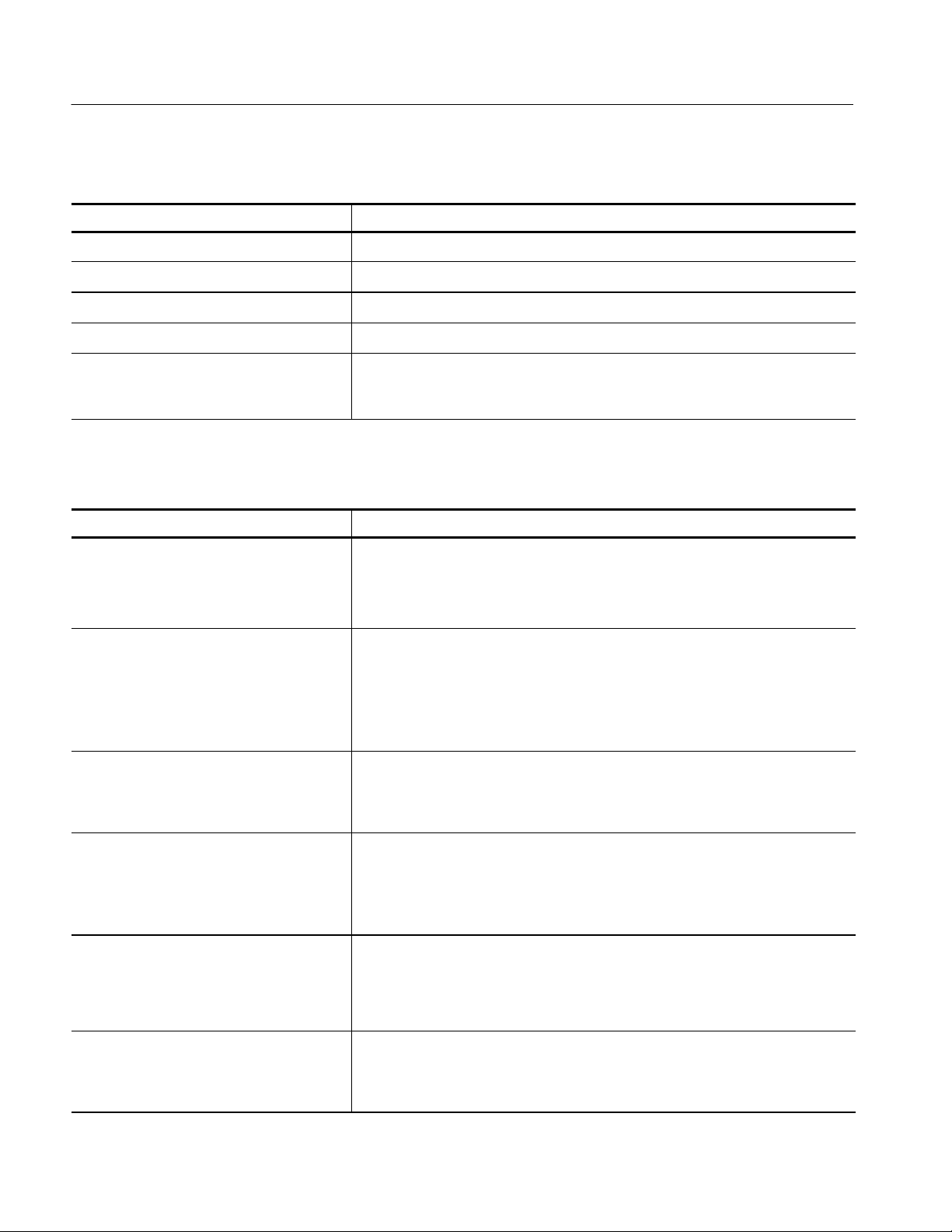

Specifications

Table 1- 6: Calibrator

Characteristic Description

Waveform Square Wave Req: Amplitude: 1.0 V ±0.5%

Performance Verification Procedure Step

RI: Calibrated against the VAC.

Frequency: 100 kHz ±0.1%

Req:

RI: Frequency counter.

RI: Crystal controlled 10 s square wave

Performance Verification Procedure Step

: 9

: 6

Waveform Sine Wave Req: Amplitude: 1.0V

RI: Measured against the VAC.

p-p

, ±1%

V ector Circle RI: Circle that approximates the graticule compass rose

Table 1- 7: Vector mode

Characteristic Description

Input Requirements Req: 1 V peak--peak ±6dB

RI: Black burst or composite video.

RI: Instrument freeruns with no input

RI: External Reference: Black burst or composite video

V ector input range is ±12 dB.

Nominal Subcarrier Frequency (FSC) RI: NTSC 3.579545 MHz

Chrominance Processing Bandwidth (--3 dB) Req: 1MHz±200 kHz

PAL +V RI: V Axis is inverted at 1/2 video line rate

PAL 4.43361875 MHz

Performance Verification Procedure Step

RI:

Leveled sinewave generator.

: 15

Display Phase Accuracy Error Req: ≤1.25°

Performance Verification Procedure Step

RI: Color bar generator

Display Gain Accuracy Error Req: ≤2.5% with 75% amplitude color bars

Performance Verification Procedure Step

Quadrature Phasing Error Req: ≤0.5° (RI: Bursts set to targets)

Performance Verification Procedure Step

Subcarrier Regenerator Pull-in Range Req: (AUD) NTSC : ±50 Hz

PAL: ±10 Hz

Performance Verification Procedure Step

Subcarrier Regenerator Pull-in Time RI: ≤2 seconds

1- 8

1740A Series, 1750A Series, & 1760 Series Service Manual

: 23

: 23

: 22

: 24

Page 27

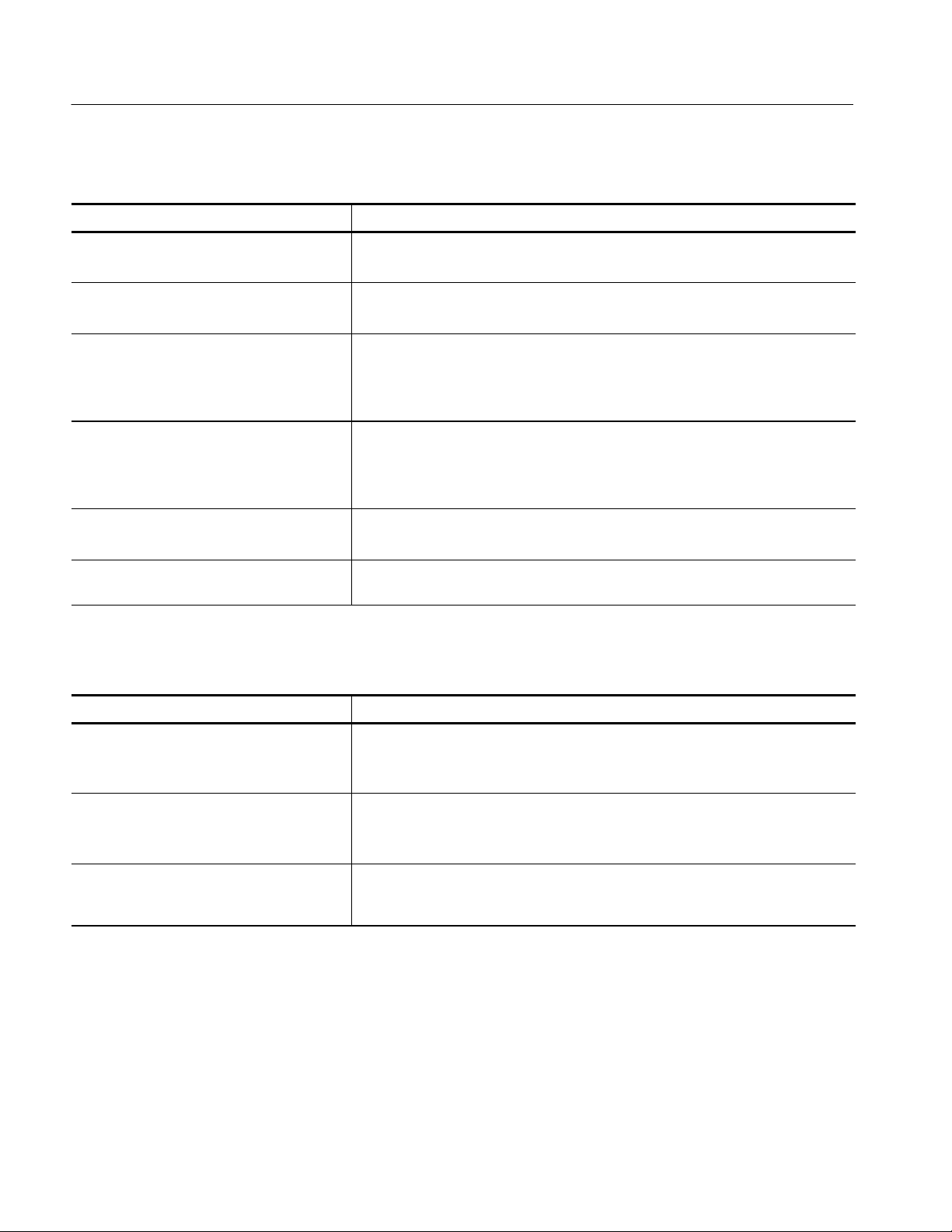

Table 1- 7: Vector mode (Cont.)

Characteristic Description

Specifications

Phase Shift with FSCChange Req: NTSC: ≤2° (FSCto FSC±50 Hz)

Phase Shift with Burst Amplitude Change of

±6dB

PAL: ≤2° (F

Req: ≤ 2°

Performance Verification Procedure Step

RI: Color bar generator.

to FSC±10 Hz)

SC

Phase Shift With Video Input Channel Change Req: ≤1°

RI: With external reference selected.

Typically ≤0.5°

Performance Verification Procedure Step

Phase Shift With Variable Gain Control +3 dB

to --6 dB

Req: ≤0.5°

Performance Verification Procedure Step

RI: Color bar generator.

Burst Jitter RI: ≤0.5° rms

RI: 140 IRE (1 V) composite video input.

Clamp Stability Req: ≤1/64 inch (0.4 mm)

RI: Center spot movement with rotation of the phase control

Performance Verification Procedure Step

Phase Control Range RI: 360° continuous rotation

Performance Verification Procedure Step

Phase Control Quantization RI: ≤0.2°

: 25

: 27

: 26

: 28

: 28

Position Control Range Req: ≥0.236 inch (6 mm) from center

Performance Verification Procedure Step

RI: Color bar generator.

Differential Phase Req: ≤1°

Performance Verification Procedure Step

RI: Measured with 140 IRE (1 Volt) linearity signal (5--step, 10-- step, or ramp)

with 40 IRE (300 mV) subcarrier.

Differential Gain Req: ≤1%

Performance Verification Procedure Step

RI: Measured with 140 IRE (1 V) linearity signal (5--step, 10--step, or ramp)

with 40 IRE (300 mV) subcarrier.

Table 1- 8: Audio mode

Characteristic Description

Input RI: DC coupled, differential input

Input Impedance RI: 20 k Ω

: 28

: 21

: 21

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 9

Page 28

Specifications

Table 1- 8: Audio mode (Cont.)

Characteristic Description

Full Scale Selection RI: 0, 4, 8, & 12 dBm full scale. Menu selected

Full Scale Accuracy Req: ±0.5 dB

RI: Measured at 1 kHz

Performance Verification Procedure Step

Maximum Input Voltage RI: ±8 V peak

RI: Measured to chassis ground

Bandwidth (--3 dB) Req: -- 3 d B ≥200.0 kHz

Performance Verification Procedure Step

RI:

Leveled sinewave generator.

X & Y Input Phase Matching Req: ≤1°

RI: Measured at 20 kHz

Performance Verification Procedure Step

: 31

: 32

: 33

Table 1- 9: Time code

Characteristic Description

Input RI: Longitudinal Time Code. DC coupled, differential input

Input Impedance RI: 20 k Ω.

Input Amplitude RI: 0, 4, 8, & 12 dBm full scale. Menu

Maximum Input Voltage RI: --10 V to +10 V peak

Bandwidth (--3 dB) Req: ≥200.0 kHz

selectable for 140 IRE (1.0 V) deflection

Performance Verification Procedure Step

RI:

Leveled sinewave generator.

: 32

Table 1- 10: SCH Phase mode (1750 Series and 1760 Option SC Only)

Characteristic Description

Absolute Accuracy Req: ≤5°

RI: Applies over a temperature range of 0 -- 50° C

RI: Calibrated at 25°C. ±3 dB input amplitude.

Typically ≤5° with±6 dB input amplitude

Performance Verification Procedure Step

: 34

Relative Accuracy RI: 2°

1- 10

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 29

Table 1- 10: SCH Phase mode (1750 Series and 1760 Option SC Only) (Cont.)

Characteristic Description

Acquisition Time RI: ≤1 Second

Specifications

Displayed Phase Error Caused by CRT

Geometry Variations

Input Timing RI: Stable display with Video to External Reference timing

Color Frame Range RI: ±70° (Color frame correctly identified when applied external reference

RI: ±1.25°

signal is ≤70° of 0° SCH.)

Performance Verification Procedure Step

: 34

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 11

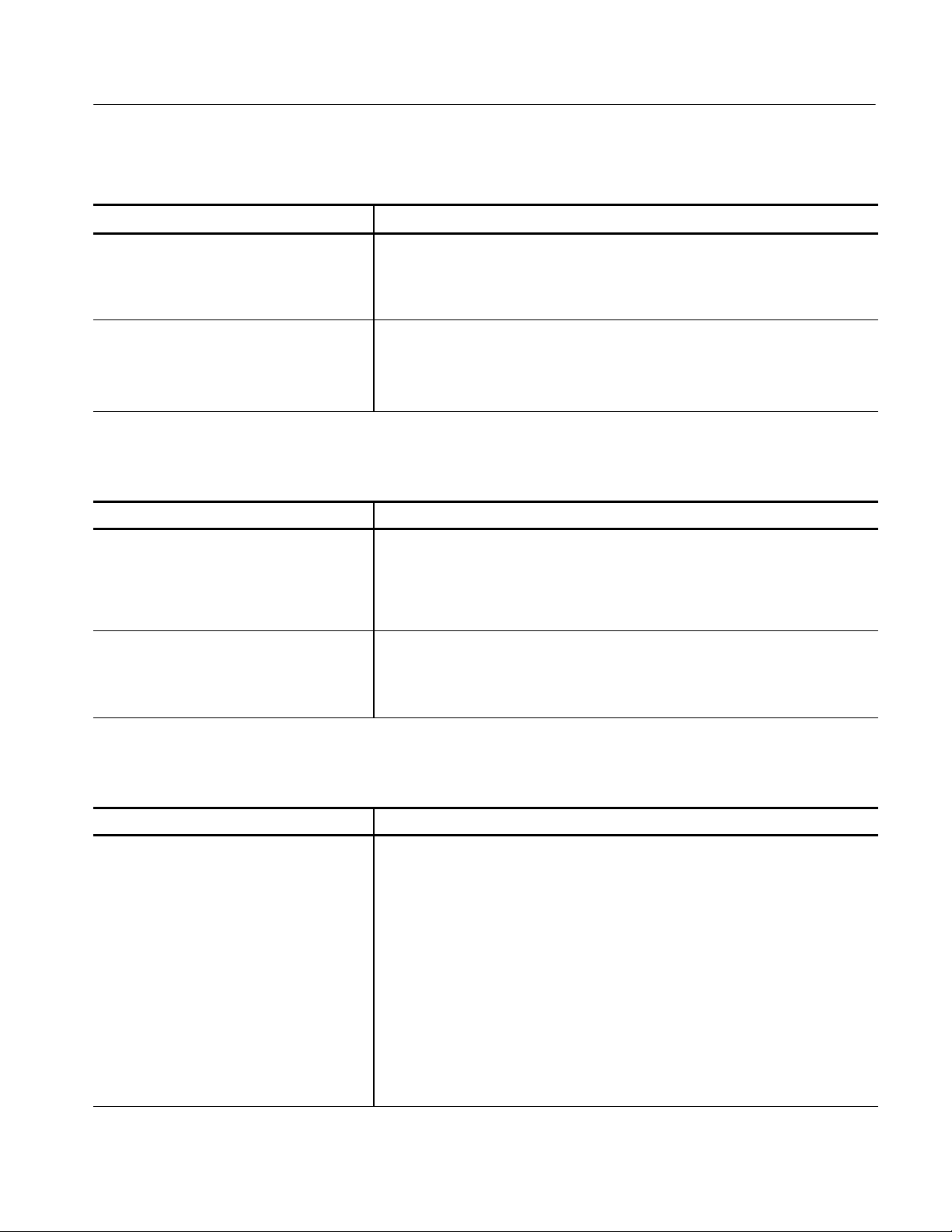

Page 30

Specifications

Table 1- 11: Component vector mode (1760 Series Only)

Characteristic Description

V ertical Bandwidth Req: --3dBat≥1.0 MHz

RI: Multiburst signal from TSG300.

Horizontal to Vertical Bandwidth Matching Req: No eye opening at 500 kHz or 2 MHz

RI: Trace-width opening with Y, P

V ertical Gain Accuracy Req: ±2.5%.

RI: With respect to graticule

Performance Verification Procedure Step

Specification will apply to the electronic graticule when it becomes available.

Horizontal Gain Accuracy Req: ±2.5%

RI: With respect to graticule

Performance Verification Procedure Step

Specification will apply to the electronic graticule when it becomes available.

Display to Graticule Registration Req: ≤0.25 box with the color bar black display dot centered in target

RI: Component signal generator.

signal applied.

R,PB

: 35

: 35

V ector Display RI: Ch A2 or B2 is displayed on the horizontal axis and Ch A3 or B3 is dis-

played on the vertical axis.

Table 1- 12: Lightning mode (1760 Series only)

Characteristic Description

V ertical Gain Accuracy Req: ±2%

RI: With respect to electronic graticule

Performance Verification Procedure Step

Horizontal Gain Accuracy Req: ±2%

RI: With respect to electronic graticule

Performance Verification Procedure Step

Electronic Graticule Display RI: Ch A1 or B1 is displayed vertically.

Ch A2 or B2 is displayed horizontally on top half of display.

Ch A3 or B3 is displayed horizontally on bottom half of display.

: 36

: 36

1- 12

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 31

Table 1- 13: Bowtie mode (1760 Series only)

Characteristic Description

Common Mode Rejection Ratio Req: ≥34 dB at 3 MHz

RI: Timing error contributed by the specification limit will be less than 0.6 ns.

Performance Verification Procedure Step

RI:

Checked with a multi burst signal. Right side display should be 400 mV.

Left side display should be 8 mV.

Specifications

: 39

Electronic Graticule Display RI: Y minus PB(CH1-- CH2) is displayed on the left half of the display.

Y minus P

(CH1-- CH3) is displayed on the right half of the display.

R

Table 1- 14: Transcoded GBR outputs

Characteristic Description

Input Format

Accuracy Req: 1 ±3%

GBR Output Impedance RI: Nominally 75 Ω . Back porch clamped to 0V

RI: GBR, SMPTE, MII, or Betacam format. Selectable from a menu

RI: Typically <1%

RI: Use lightning mode of another monitor to check GBR outputs. Color bar

dots should be inside targets.

Alternate Method:

tor.

RI: No line select strobe on GBR outputs

Performance Verification Procedure Step

Component generator used to measure transcoder accuracy must have an accuracy of

≤±1%.

Measure GBR output amplitudes with a waveform moni-

: 42

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 13

Page 32

Specifications

Table 1- 15: CRT display

Characteristic Description

CRT Viewing Area RI: 80 X 100 mm

Horizontal: 12.5 divisions

V ertical: 170 IRE (1.19 V)

Scan Sensitivity: Vertical: 34.5 to 43.7 V for 80 mm.

Horizontal: 91.5 to 118.5 V for 100 mm.

Accelerating Potential RI: Nominally 13.5 kV

Trace Rotation Range Req: <+and--1° from horizontal

RI: Free-running sweep.

RI: Total adjustment range is typically ≥8°.

Performance Verification Procedure Step

Graticule RI: Internal with variable illumination

Table 1- 16: Power source

Characteristic Description

Mains Voltage Range Req: 90 --250 V

RI: Check with variable auto transformer and step-up transformer.

RI: Continuous range from 90 to 250 V AC

Performance Verification Procedure Step

: 3

: 2

Mains Frequency RI: 50 or 60 Hz.

Power Consumption RI: 110 VA (67 watts) maximum; 102 VA (60 watts) typical

Table 1- 17: Environmental characteristics

Characteristic Description

Operating Temperature Req: 0° to 50° C(+32° to 122° F)

Storage Temperature Req: -- 4 0 ° to 75° C(--40° to 158° F)

Operating Altitude Req: To 15,000 feet (4572 meters)

Storage Altitude Req: T o 50,000 feet (15,240 meters)

Vibration Req: 5 minutes at 5 -- 15 Hz with 0.060 inch displacement

Mechanical Shock Req: Non Operating: 50 g’s 1/2 sine, 11 ms duration 3 shocks per surface (18 total)

5 minutes at 15 -- 25 Hz with 0.040 inch displacement

5 minutes at 25 -- 55 Hz with 0.020 inch displacement

Military Specification: Mil-- T--28800D, Paragraph 1.2.2, Class 3

1- 14

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 33

Table 1- 17: Environmental characteristics (Cont.)

Characteristic Description

Transportation Req: Qualified under NSTA Test Procedure 1A, Category II (24 inch drop)

Specifications

Humidity Req: Will operate at 95% relative humidity for up to five days. Do not operate with

visible moisture on the circuit boards.

Table 1- 18: Physical characteristics

Characteristic Description

Dimensions Req: Height: 5 1/4 inches (133.4 millimeters)

Weight Req: Net: 8 pounds (3.8 kilograms)

Width: 8 1/2 inches (215.9 millimeters)

Depth: 18 1/8 inches (460.4 millimeters)

Shipping: 15.7 pounds (7.2 kilograms) approximate

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 15

Page 34

Specifications

EMC

LowVoltag

e

y

g

Table 1- 19: Certifications and compliances

Category Standards or description

EC Declaration of Conformity --

1

EMC

Meets the intent of Directive 89/336/EEC for Electromagnetic Compatibility. Compliance was demonstrated to the following specifications as list ed in the Official Journal of the European Communities:

EN 55103 Product family standard for audio, video, audio-visual and entertainment lighting

control apparatus for professional use.

2

Environment E2 -- commercial and light industrial

Part 1 Emission

EN 55022 Class B radiated and conducted emissions

EN 55103--1, Annex A Radiated magnetic field emissions

EN 55103--1, Annex B Inrush current; I peak = 2.5 amps

EN-55103--1, Annex E Conducted emissions, signal/control ports

Part 2 Immunity

IEC 61000--4--2 Electrostatic discharge immunity

IEC 61000--4--3 RF electromagnetic field immunity

IEC 61000--4--4 Electrical fast transient / burst immunity

IEC 61000--4--5 Power line surge immunity

IEC 61000--4--6 Conducted RF Immunity

IEC 61000--4--11 Voltage dips and interruptions immunity

EN 55103--2, Annex A Radiated magnetic field immunity

EN 55103--2, Annex B Balanced ports common mode immunity

Australia / New Zealand

Declaration of Conformity-EMC

Complies with EMC provision of Radiocommunications Act per the following standard(s):

AS/NZS 2064.1/2 Industrial, Scientific, and Medical Equipment: 1992

FCC Compliance Emissions comply with FCC Code of Federal Regulations 47, Part 15, Subpart B, Class A Limits.

EC Declaration of Conformity -Low Voltage

Compliance was demonstrated to the following specification as listed in the Official Journal of t he

European Communities:

Low Voltage Directive 73/23/EEC, amended by 93/68/EEC

EN 61010-1:1993/A2:1995 Safety requirements for electrical equipment for measurement control

and laboratory use.

U.S. Nationally Recognized UL3111-1 Standard for electrical measuring and test equipment.

Testing Laboratory Listing

Canadian Certification CAN/CSA C22.2 No. 1010.1 Safety requirements for electrical equipment for measurement, control,

and laboratory use.

1

This product complies when installed into any of the following Tektronix instrument enclosures:

1700F00 Standard Cabinet

1700F02 Portable Cabinet

WFM7F05 Rack Adapter

2

Use only high-quality shielded cables.

1- 16

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 35

Specifications

CategoryDescription

s

Table 1- 19: Certifications and compliances (cont.)

Category Standards or description

Additional Compliance IEC61010-1 Safety requirements for electrical equipment for measurement, control, and

laboratory use.

ISA S82.02.01:1999 Safety standard for electrical and electronic test, measuring, controlling, and

related equipment.

Installation (Overvoltage)

Category Descriptions

Pollution Degree Descriptions A measure of the contaminates that could occur in the environment around and within a product.

Equipment type Test and Measurement

Safety Class Class I

Overvoltage Category CAT II

Pollution Degree Pollution Degree 2

Terminals on this product may have different installation (overvoltage) category designations.

The installation categories are:

CAT III Distribution-level mains (usually permanently connected). Equipment at this level is

typically in a fixed industrial location.

CAT II Local-level mains (wall sockets). Equipment at this level includes appliances, portable

tools, and similar products. Equipment is usually cord-connected.

CAT I Secondary (signal level) or battery operated circuits of electronic equipment.

Typically the internal environment inside a product is considered to be t he same as the external.

Products should be used only in the environment for which they are rated.

Pollution Degree 1 No pollution or only dry, nonconductive pollution occurs. Products in this

category are generally encapsulated, hermetically sealed, or located in c lean

rooms.

Pollution Degree 2 Normally only dry, nonconductive pollution occurs. Occasionally a temporary

conductivity that is caused by condensation must be expected. This location is

a typical office/home environment. Temporary condensation occurs only when

the product is out of service.

Pollution Degree 3 Conductive pollution, or dry, nonconductive pollution that becomes conductive

due to condensation. These are sheltered locations where neither temperature

nor humidity is controlled. The area is protected from direct sunshine, rain, or

direct wind.

Pollution Degree 4 Pollution that generates persistent conductivity through conductive dust, rain,

or snow. Typical outdoor locations.

1740A Series, 1750A Series, & 1760 Series Service Manual

1- 17

Page 36

Specifications

1- 18

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 37

Installation

Standard Accessories

The information contained here deals with the installation and operation of the

1740A/1750A/1760--Series instrument. If the instrument is to be removed from

its installed position for servicing, this will provide the information needed to

remove it or reinstall it. Note that the repackaging information is located at the

end of the Maintenance section.

This instrument is shipped with a set of standard accessories. These are the items

necessary to place the instrument in service, such as the power cord. When the

box for the instrument is opened, it should contain:

H One User Manual.

H Power cord assembly (See Options)

H One cartridge fuse.

H Three replacement graticule light bulbs.

H Three replacement air filters

Two 3.5-inch high density disks are included with this manual. The disks run on

an IBM compatible PC with a DOS 3.3 or higher operating system and a

3.5-inch high-density disk drive.

One disk contains the current operating software for the instrument. To determine the level of software loaded in an instrument, perform the following steps:

1. Power up the 1740A/1750A/1760--Series.

2. Push the CONFIG menu button.

3. Select the REMOTE submenu.

4. Read the software version number from the lower right corner of the CRT.

The other disk contains the procedure needed to return the instrument operation

to its specified levels. This procedure works in conjunction with the Adjustment

Procedures section of this manual. Version 2.2 or higher software must be loaded

in the instrument to use the Adjustment procedures.

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 1

Page 38

Installation

Mechanical Installation

8.250

6.8750.688

Cabinets

Rear

0.156 Diameter (4)

12.725

1.060

5.105

6.130

16.180

Bottom Side

Figure 2- 1: Dimensions of the 1700F00 plain cabinet

The cabinets available for this instrument provide necessary shielding and

protection against accidental electrical shock, and also protect internal circuitry

against build up of dust. A supply of filtered, cooling air is provided from the

rear panel and exits through the cabinet vent holes. Operation in air flow

restricted environments may lead to excessive heat build up.

2- 2

All qualification testing for the 1740A/1750A/1760--Series instruments was

performed in a 1700F00 cabinet. To guarantee compliance with specifications,

the instrument should be operated in a cabinet. The plain cabinet, 1700F00, is

shown in Figure 2--1.

Also available are the 1700F02 Portable carrying case and the WFM7F05

side-by-side rack mount assembly. All of these cabinets are available from

Tektronix. If you need one of these cabinets, contact your nearest Tektronix field

office or representative for assistance in ordering.

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 39

8.250

6.8750.688

Installation

5.105

5.0001.625

16.180

Bottom Side

Rear

0.141 Diameter (4)

9.435

3.310

Figure 2- 2: 1700F02 portable cabinet

The portable cabinet, 1700F02, is shown in Figure 2--2. The 1700F02 has a

handle, four feet, a flip-up stand. The mounting hole sizes and spacing are

different from those of the 1700F00.

The 1700F00, 1700F02, and WFM7F05 cabinets, which are available from

Tektronix as optional accessories, provide the proper electrical environment for

the instrument. They supply adequate shielding, minimize handling damage, and

reduce dust accumulation within the instrument.

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 3

Page 40

Installation

Installing the Cabinet

CAUTION. Do not attempt to carry an instrument in the cabinet without installing

the mounting screws. Without the mounting screws, there is nothing to hold the

instrument in the cabinet if it is tipped forward.

The instrument is secured to the cabinet by two 6-32 Pozidriver screws, located

in the upper corners of the rear panel. See Figure 2-- 3.

Cabinet securing screws

Rack Adapter

Figure 2- 3: Rear view showing the secur ing screws

The optional WFM7F05 side-by-side rack adapter, shown in Figure 2--4, consists

of two attached cabinets. It can be used to mount the 1740A/1750A/1760--Series

and another half-rack width instrument in a standard 19-inch rack.

CAUTION. Be sure to read and follow the instructions that are shipped with the

rack adapter.

Use the correct sleeve for your product. The ventilation holes and EMI shielding

on the sleeves are specially designed to meet the requirements of the instruments

for which they were intended. If you use the wrong sleeve, it could damage the

instrument and cause overheating problems.

When working with instruments that are not enclosed in a chassis, you must

observe static precautions. You must also be careful not to damage circuit board

mounted components or interconnection wiring when sliding a sleeve over these

products.

2- 4

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 41

18.970

Installation

5.250

Mounting

holes

6.875

Rear view

17.270

Controls front panel

to rack alignment

Figure 2- 4: The WFM7F05 side -by-side rack adapter

The rack adapter is adjustable, so the instrument can be more closely aligned

with other equipment in the rack. See Figure 2--4.

WFM7F05

1700F06

Figure 2- 5: A W FM7F05 with a blank front panel (1700F06)

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 5

Page 42

Installation

If only one side of the rack adapter is used, a 1700F06 Blank Panel can be

inserted in the unused section. See Figure 2--5. The rack adapter and panel are

available through your local Tektronix field office or representative.

When only one instrument is mounted in the side-by-side adapter, an accessory

drawer (1700F07) can be installed in the blank side of the cabinet. See

Figure 2--6.

WFM7F05

1700F07

Figure 2- 6: WFM7F05 rack mount cabinet with a 1700F07 utility drawer

2- 6

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 43

Installation

Custom Installation

For applications such as consoles, the instrument can be mounted with front

molding flush or protruding from the console. In both cases, allow approximately 3 inches of rear clearance for BNC and power-cord connections.

To mount the instrument safely, attach it to a shelf strong enough to hold its

weight. Install the mounting screws through the four 0.156-inch diameter holes

in the bottom of the 1700F00 cabinet. See Figure 2--7.

For flush front panel: Cut hole the

same size as the monitor front molding

to allow the monitor front panel to align

with the custom panel surface.

Requires four 0.156” holes below

the 1700F00 cabinet to secure

the instrument to the shelf.

For protruding front molding:

Cut hole in panel the same size as the

opening in the monitor cabinet to allow

the front panel molding to cover the hole.

Figure 2- 7: Custom installation of an instrument

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 7

Page 44

Installation

Electrical Installation

Power Source

Mains Frequency and

Voltage Range

Power Cord Options

Operational Changes

These monitors are designed to operate from a single-phase power source having

one of its current-carrying conductors at or near earth ground (the neutral

conductor). Only the line conductor is fused for over-current protection Systems

that have both current-carrying conductors live with respect to ground (such as

phase-to-phase on multiphase systems) are not recommended as power sources.

A protective ground connection by way of the grounding conductor in the power

cord is essential for safe operation.

WARNING. When power is supplied, line voltage will be present in the instrument, even if the

The 1740A/1750A/1760--Series monitors operate at 50 and 60 Hz, over the range

of 90--250 Volts, without operator adjustment.

These instruments ship with a standard North America power cord, unless a

power cord option was ordered. Table 7--1 in the Options section shows the

available options.

No operational modifications are made to this monitor through internal jumper

settings.

POWER switch is set to STANDBY.

2- 8

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 45

Rear Panel Connectors

Installation

Signals into and out of the instrument are connected via the rear panel. Video

signals are input/output through the BNC connectors, except for the RGB

staircase signal which is input through the REMOTE connector. General

information about the rear panel connectors is provided in the following

paragraphs. Figure 2--8 shows the rear panel configuration for a 1760--Series

instrument. The only difference between the 1760--Series rear panel and the other

instrument rear panels is the presence of the GBR outputs.

PIX

OUT

G

B

EXT

REF

R

75 OHM LOOP-THROUGH COMP E NSATED

A3 A2 A1 A

75 Ω Loop-Through

Video Inputs

External Reference

(EXT REF)

B3 B2 B1 B

51 13 1

96

RS232

25 14

REMOTE

Figure 2- 8: Rear panel connect ors

There are a total of eight 75 Ω compensated loop-through video input BNC

connectors. These inputs are not internally terminated; inputs require 75 Ω

external termination to provide accurate measurement capabilities. Inputs A and

B are dedicated composite inputs regardless of instrument type. Inputs

A1--A2--A3 and B1--B2--B3 can also be used as composite inputs, but if

component signals are to be displayed, they become the component inputs.

Maximum operating input voltage for all inputs is --1.8 V to +2.2 V DC plus

peak AC. Absolute maximum input voltage is --8.5 V to +8.5 V DC plus

peak AC.

The external reference input provides both external synchronizing signals and

external subcarrier input to these instruments. Input is either black burst or

composite video. It is a 75 Ω compensated loop-through input, requiring external

termination.

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 9

Page 46

Installation

Picture Monitor Out

(PIX OUT)

GBR Output

Remote Connector

The PIX OUT is a 75 Ω, nonfiltered output designed to drive a picture monitor.

A bright-up strobe is added when the instrument is operated in the line select

mode. Strobe will either be the line in the selected field, the line in all fields or

of 15 lines duration in the selected field or all fields. In the 15-line mode, the

bright up starts with the selected line.

1760--Series Only. These three 75 Ω outputs are from the color difference-to-

GBR transcoder. When the input is RGB, the transcoder is bypassed. The G

(green) output contains sync.

The rear-panel REMOTE connector is a 25-pin, D-type connector. It provides the

input for stereo L and R audio. TTL signal or ground closure to designated pins

are the enables. Eight front-panel setups can also be stored and recalled through

the Remote connector. Table 2--1 shows pin assignments and Figure 2--9 shows

the connector.

13

1

1425

REMOTE

!

Figure 2- 9: Rear panel REMOTE connector.

2- 10

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 47

Table 2- 1: Remote connector

Pin number Function Signal requirement Miscellaneous information

Installation

1 RGB/YRGB Staircase Input

External Horiz. Input

2 Ground

3 Staircase/Ext. Horiz. Enable Ground (TTL low) Grounding enables the function. (Staircase or external horizontal

4 External Blanking Input Negative-going signal Enabled by menu selection.

5 Remote Sync Input TTLlevel square wave

6 Remote Sync Enable Ground (TTL low) Grounding enables the function.

7 Ground

8 +Y Audio Input Max. Input ±8 V peak. Left in phase. Measured to Chassis Ground.

9 --Y Audio Input Max. Input ±8 V peak. Left out of phase. Measured to Chassi s Ground.

10 +X Audio Input Max. Input ±8 V peak. Right in phase. Measured to Chassis Ground.

11 --X Audio Input Max. Input ±8 V peak. Right out of phase. Measured to Chassis Ground.

12 + Time Code Input --10 -- +10 V peak. Longitudinal Time Code, differential.

13 -- Time Code Input --10 -- +10 V peak. Longitudinal Time Code, differential.

14 Ground

+10 V for RGB/YRGB

0 -- +5 V Sawtooth

triggers 2-field sweep.

≈9 divisions of sweep. (Staircase/external horizontal and

RGB/YRGB selected through the menu.)

10 divisions of horizontal deflection.

selected through the menu.)

30/90 Hz for NTSC

25/100 Hz for PAL

15 & 16 Not used

17 Preset 1 Ground (TTL low) Ground pin 17 to recall front-panel setup from preset 1. Ground

pins 17 and 25 to store current front-panel setup at preset 1.

18 Preset 2 Ground (TTL low) Ground pin 18 to recall front-panel setup from preset 2. Ground

pins 18 and 25 to store current front-panel setup at preset 2.

19 Preset 3 Ground (TTL low) Ground pin 19 to recall setup from preset 3. Ground pins 19 and

25 to store current setup at preset 3.

20 Preset 4 Ground (TTL low) Ground pin 20 to recall setup from preset 4. Ground pins 20 and

25 to store current setup at preset 4.

21 Preset 5 Ground (TTL low) Ground pin 21 to recall setup from preset 5. Ground pins 21 and

25 to store current setup at preset 5.

22 Preset 6 Ground (TTL low) Ground pin 22 to recall setup from preset 6. Ground pins 22 and

25 to select preset 6 as storage location for current setup.

23 Preset 7 Ground (TTL low) Ground pin 23 to recall setup from preset 7. Ground pins 23 and

25 to select preset 7 as storage location for current setup.

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 11

Page 48

Installation

Table 2- 1: Remote connector (Cont.)

Pin number Miscellaneous informationSignal requirementFunction

24 Preset 8 Ground (TTL low) Ground pin 24 to recall setup from preset 8. Ground pins 24 and

25 to select preset 8 as storage location for current setup.

25 Store Ground (TTL low) Ground this pin along with one of the Preset pins to store the

current front-panel setup at the selected Preset location.

Remote Connector Converter

If the 1740A/1750A/1760--Series replaces a 1740/1750--Series instrument, rewire

the remote cable or provide an adapter as shown in Figure 2--10

If the 1740A/1750A/1760--Series replaces an Option 16 instrument, construct the

adapter in the same manner, omitting the pin 3-to-pin-25 connection.

1740A/1750A/1760--Series

rear-panel REMOTE connector

1

14

3

5

6

7

25

13

*(Do not connect when replacing Option 16 instruments.)

RGB INPUT

RGB

ENABLE*

REMOTE SYNC IN

GROUND

REMOTE SYNC ENABLE

Figure 2- 10: Replacement adapter for 1740/1750

Remote plug

1

14

19

8

9

10

25

13

2- 12

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 49

RS232 Connector

Installation

This 9-pin subminiature D-type connector provides a serial interface for remote

control. It has a driver built in for RS232 serial binary data interchange. The

operational mode is full duplex. Data rate = 9600 baud; data type is asynchronous. Figure 2-- 11 shows pin assignments and connector orientation.

54321

9876

RS232

1 DCD

2 Receive Data (RxD)

3 Transmit Data (TxD)

4 Data Terminal Ready (DTR)

5 Signal Ground (GND)

Figure 2- 11: Rear panel RS232 connector

6 Data Set Ready (DSR)

7 Request to Send (RTS)

8 Clear to Send (CTS)

9 No connection

1740A Series, 1750A Series, & 1760 Series Service Manual

2- 13

Page 50

Installation

Installing Software

These versatile monitors can be upgraded to perform additional measurements or

to revise operations. Software code is contained in Flash EPROM that can be

written over when upgrades become available.

If you replace the Flash EPROM, you must reinstall the software from the

software disk accompanying this manual.

To find the current version of software, go to the CONFIG menu and then to the

REMOTE submenu. The version number, preceded by the letter V, is displayed

in the lower right corner of the screen.

Software Disk

Required Equipment

The software disk is a 3.5” (1.44MB) high-density disk. It contains all programs

necessary to upgrade or reload the operating software in the Tektronix

1740A/1750A/1760--Series instruments. If a disk drive other than 3.5” is to be

used, copy the contents of the disk to the desired size disk or to a hard disk

directory. The disk contents are:

NVSAVE.EXE. Saves calibration constants and user presets.

CONVERT.EXE.Updates format of calibration and preset data.

UPGRADE.EXE. Performs software upgrade.

NVRESTOR.EXE. Restores calibration constants and user presets.

NEW_CAL.EXE. Used to calibrate new features.

SOFTWARE.BIN. Data file used by UPGRADE.EXE.

IBM Compatible PC with the following

H DOS 3.3 or Higher.

H 640 K Bytes Random-Access Memory (RAM).

H High Density Floppy Drive (3.5”/1.44 MB).

2- 14

H Available RS232 Port (COM 1, 2, 3, or 4).

H RS232 Cable to connect PC to the 1740A/1750A/1760--Series R S232

connector.

1740A Series, 1750A Series, & 1760 Series Service Manual

Page 51

Installation

Instrument Reset

Certain conditions, such as removing the power source while a program is

running, may cause the 1740A/1750A/1760--Series instrument front-panel

controls to become locked.

Reset as

Turn off instrument power, then depress CLEAR MENU and WAVEFORM,

holding in both buttons until you have turned instrument power on again and the

instrument has returned to its normal operating state.

CAUTION. Loading new software will result in the loss of instrument calibration

constants and user presets. Therefore, the program NVSAVE must be run before

executing UPGRADE.

If a disk is used to upgrade more than one instrument, finish one upgrade,

including the NVRESTOR program, before running NVSAVE on the next

instrument. NVSAVE will overwrite the temporary files on the disk every time it