Technical Reference Manual

TLA 700 Series

TLA 7QS QuickStart Training Board

070-9716-00

There are no current European directives that

apply to this product. This product provides cable

and test lead connections to a test object of

electronic measuring and test equipment.

This document supports firmware version 1.00

and above.

Warning

The servicing instructions are for use by qualified

personnel only. To avoid personal injury, do not

perform any servicing unless you are qualified to

do so. Refer to all safety summaries prior to

performing service.

Copyright T ektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and

are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the

Rights in T echnical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the

Commercial Computer Software – Restricted Rights clause at F AR 52.227-19, as applicable.

T ektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes

that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

T ektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070–1000

TEKTRONIX and TEK are registered trademarks of T ektronix, Inc.

MagniVu is a registered trademark of T ektronix, Inc.

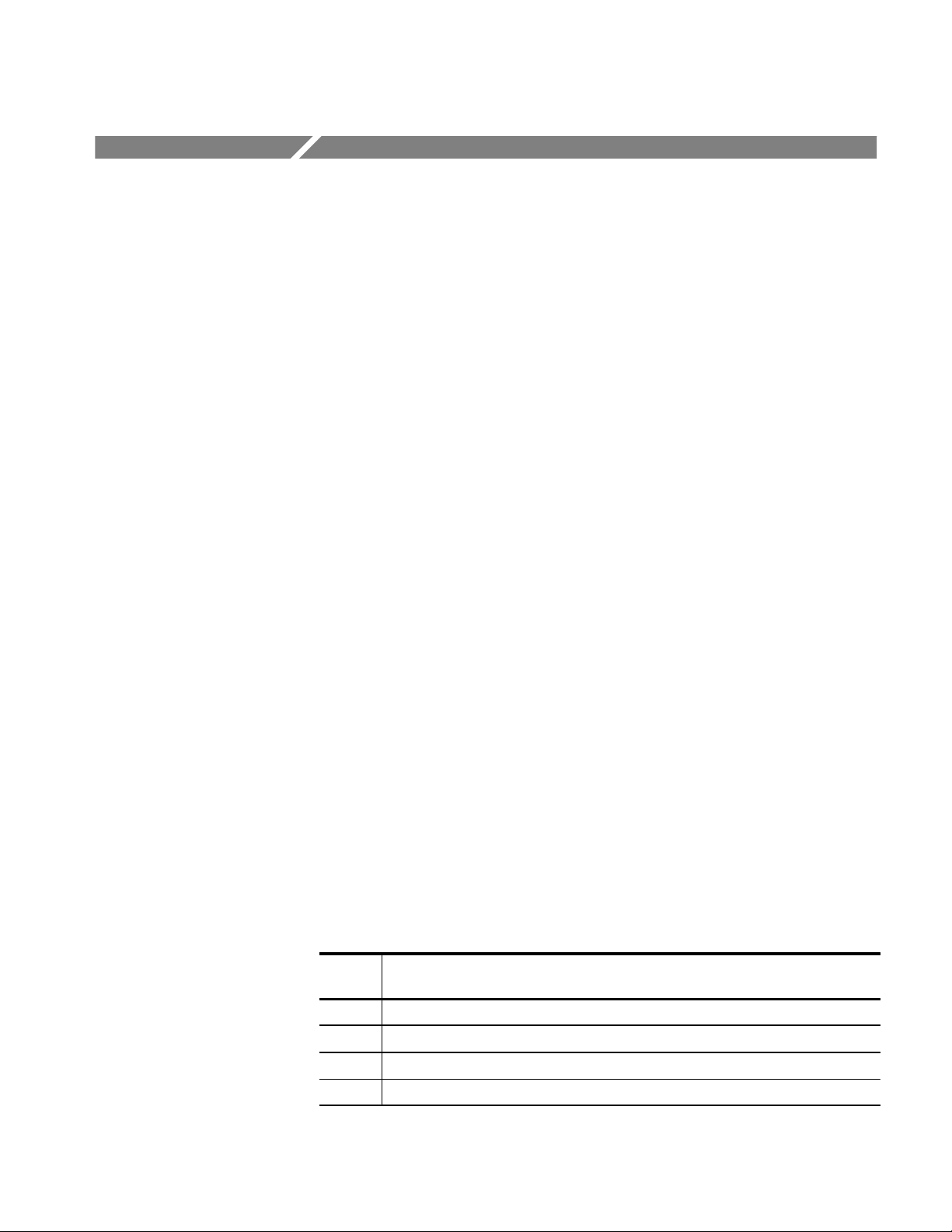

Table of Contents

Getting Started

Reference

General Safety Summary vii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Service Safety Summary ix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Preface xiii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

How to Use This Document xi. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Related Documentation xii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Manual Conventions xii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Contacting T ektronix xii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Product Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Accessories 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Configuration 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Check 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Hardware Features 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Board Modules 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Microprocessor Module 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Sources Module 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Interface Module 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input and Output Connectors 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Port Requirements 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Software Features 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Modes 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stand-Alone Mode 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Host-Controlled Mode 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Debug Mode 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Main Software Routine 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Embedded Programs 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LITES 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STOP LITES 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STRINGS 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

COUNTER 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PATTERN GEN 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SHOW CYCLES 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

WAIT STATE 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

INT LATENCY 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PGM DELAY 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AUTO DELAY 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PULSE 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SETUP/HOLD 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PGM FLASH 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LAPOR T ENABLE 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TRIG ENABLE 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIAGS 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLA QuickStart Technical Reference Manual

i

Table of Contents

MONITOR 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interrupt Service Routines 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LCD User Interface 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UP and DN Buttons 2–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RUN Button 2–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

STOP Button 2–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RS-232 Interface 2–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diagnostics 2–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LCD T est 2–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Port Tests 2–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ROM T est 2–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RAM T est 2–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Maps 2–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Mapped Input and Output 2–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LCD Display 2–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LED Displays 2–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input Control Bits Register 2–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Control Bits Register 2–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Programmable Delay Setup and Hold Violation Circuit 2–21. . . . . . . . . . . . . . . .

Read-Write Setup and Hold Violation Memory 2–21. . . . . . . . . . . . . . . . . . . . . .

Low Counter Pattern Generator Data 2–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

High Counter Pattern Generator Data 2–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memory Maps 2–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Creating Programs for the Training Board 2–29. . . . . . . . . . . . . . . . . . . . .

Preparation 2–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Software Development Systems T ools 2–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

T ektronix Software Tools 2–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Writing the Program 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Create the Menu Entry 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Include the User Header File 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Create a Dummy Function 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Write the Code 2–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Compiling and Linking Code 2–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Compile the Code 2–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Link the Code 2–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Writing an Image to the Flash Memory 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Running the Program 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Specifications

Theory of Operation

ii

Circuit Board Modules 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Microprocessor Module 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Sources Module 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User Interface Module 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply Module 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input and Output Connectors 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Ports 4–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Logic Analyzer Control Port 4–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Trigger BNC Connectors 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Background Debug Mode Connector 4–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLA QuickStart Technical Reference Manual

Functional Verification

Maintenance

Table of Contents

JTAG Port 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Input Connectors 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bus Interface Connector 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Probe Interfaces 4–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Equipment Required 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Microprocessor Circuitry Check 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Counter-Pattern Generator Circuitry Check 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital and Analog Circuitry Check 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Runt Pulse and Missing Pulse Check 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Narrow Pulse Check 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Burst Pulse Check 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fast Edge Signal Check 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Metastable Glitch Signal Check 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Staircase Signal Check 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Preventing ESD 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Service Strategy 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Warranty Repair Service 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Repair or Calibration Service 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Self Service 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Inspection and Cleaning 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Troubleshooting Procedures 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diagnostics 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Signal Tracing 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Repackaging Instructions 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Replaceable Parts

Schematics

Parts Ordering Information 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using the Replaceable Electrical Parts List 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Abbreviations 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Component Number 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Assemblies 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chassis Parts 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mfr. Code to Manufacturer Cross Index 7–2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

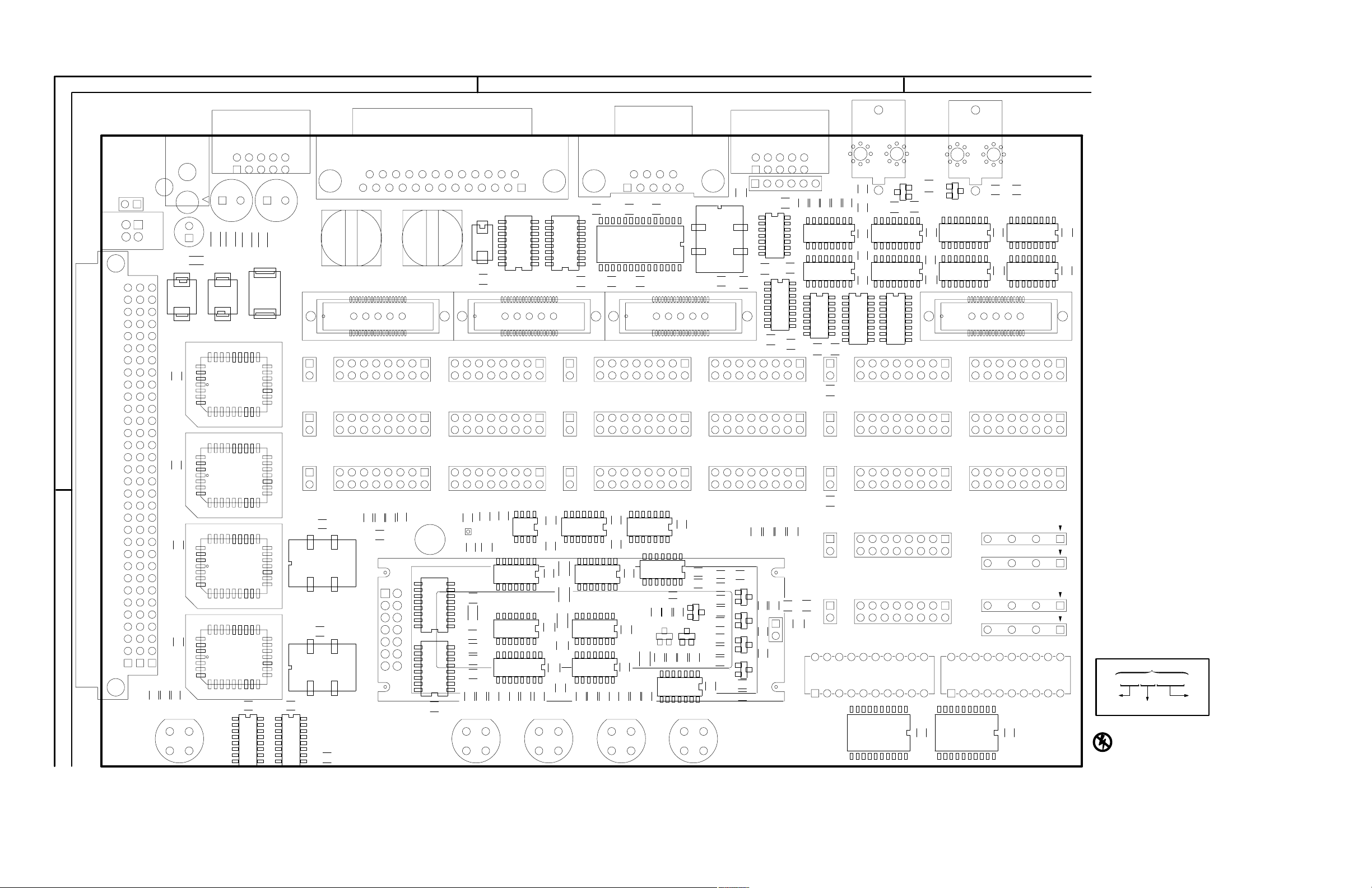

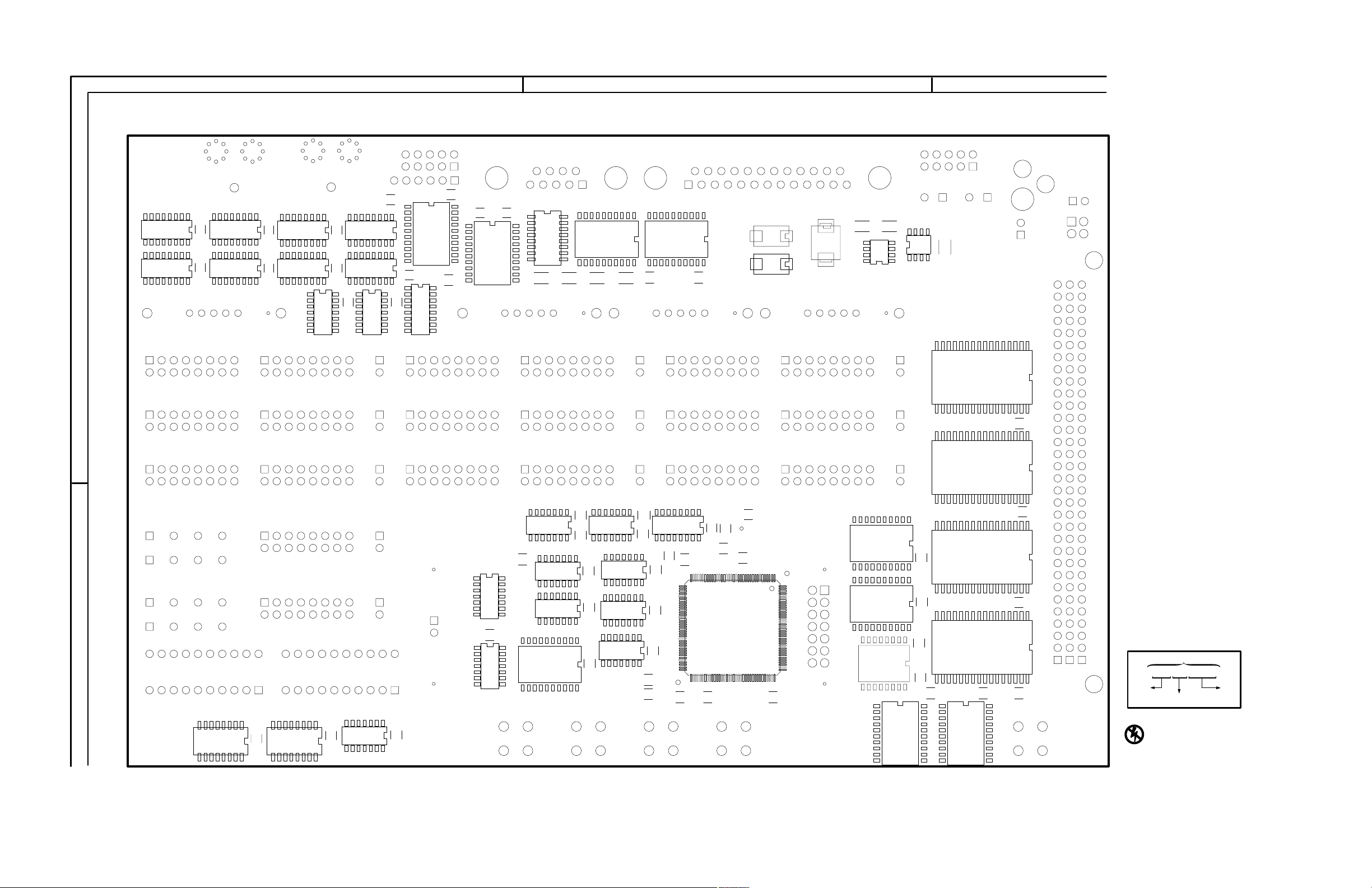

Diagrams and Circuit Board Illustrations 7–1. . . . . . . . . . . . . . . . . . . . . .

Symbols 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Component Values 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Graphic Items and Special Symbols Used in This Manual 7–1. . . . . . . . . . . . . . . . .

Component Locator Diagrams 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLA QuickStart Technical Reference Manual

iii

Table of Contents

Replaceable Mechanical Parts

Parts Ordering Information 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Using the Replaceable Mechanical Parts List 8–1. . . . . . . . . . . . . . . . . . . . . . . . . . .

Abbreviations 8–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Chassis Parts 8–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mfr. Code to Manufacturer Cross Index 8–2. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendices

Appendix A: Source Code A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Source Code Files A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sample programs A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

User.c A–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

build.bat A–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

combine.spc A–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

TLA QuickStart Technical Reference Manual

List of Figures

Table of Contents

Figure 2–1: Programmable delayed read memory block diagram 2–3. . .

Figure 2–2: Null modem connections 2–7. . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–3: Remote menu 2–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–4: Full Memory Map 2–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–5: System and user static RAM 2–24. . . . . . . . . . . . . . . . . . . . . . .

Figure 2–6: User EEPROM and Flash 2–25. . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–7: Input and output 2–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 2–8: System EEPROM and Flash 2–27. . . . . . . . . . . . . . . . . . . . . . .

Figure 4–1: Setup and hold violation counter block diagram 4–5. . . . . . .

Figure 4–2: Input and output connector locations 4–10. . . . . . . . . . . . . . . .

Figure 5–1: Sample Activity Monitor 5–3. . . . . . . . . . . . . . . . . . . . . . . . . .

Figure 8–1: Exploded view 8–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TLA QuickStart Technical Reference Manual

v

Table of Contents

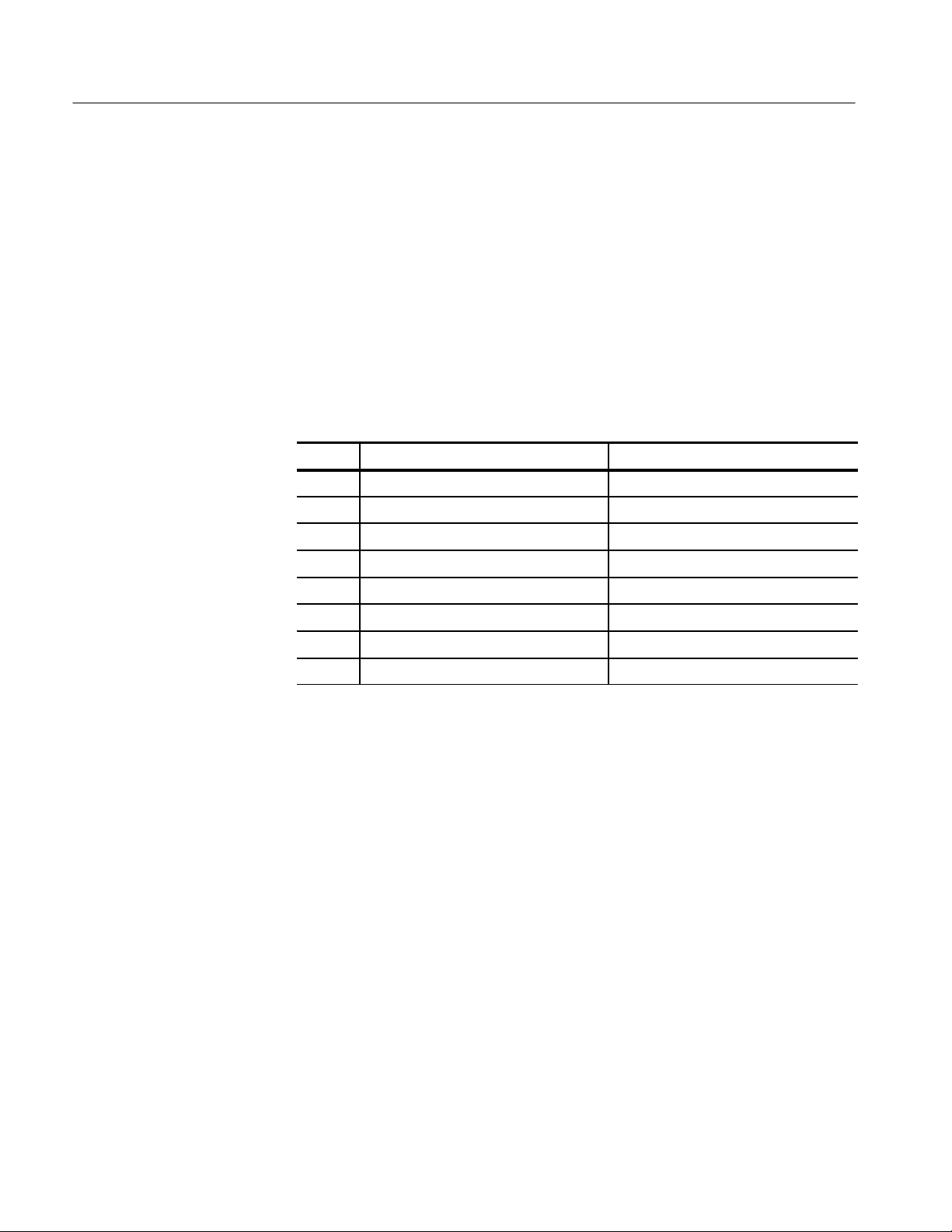

List of Tables

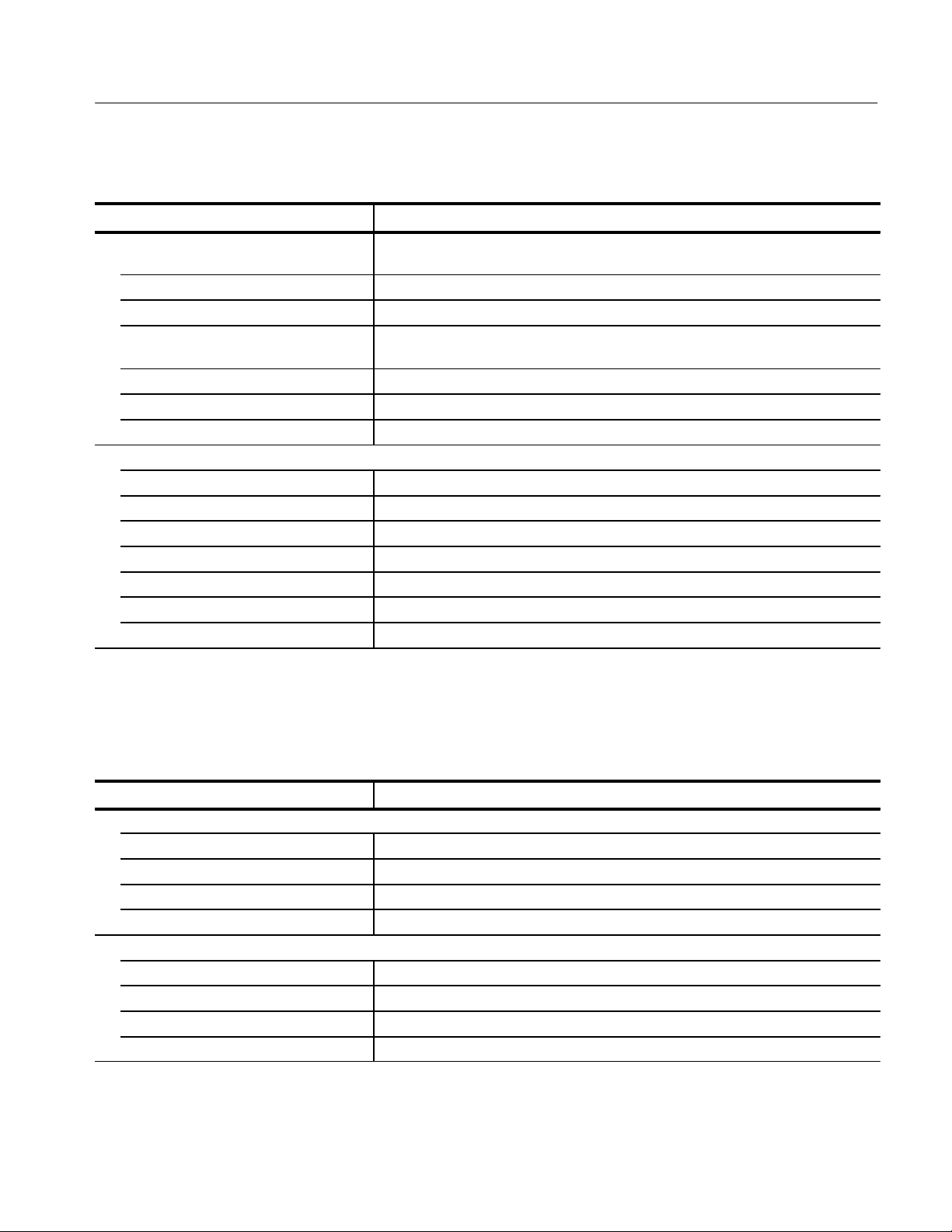

Table 2–1: Microprocessor chip select lines 2–1. . . . . . . . . . . . . . . . . . . . .

Table 2–2: PORTA signals 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–3: RS-232 connector pinouts 2–7. . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–4: Input and output device addresses 2–19. . . . . . . . . . . . . . . . . . .

Table 2–5: Input control bits 2–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 2–6: Output control bits 2–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

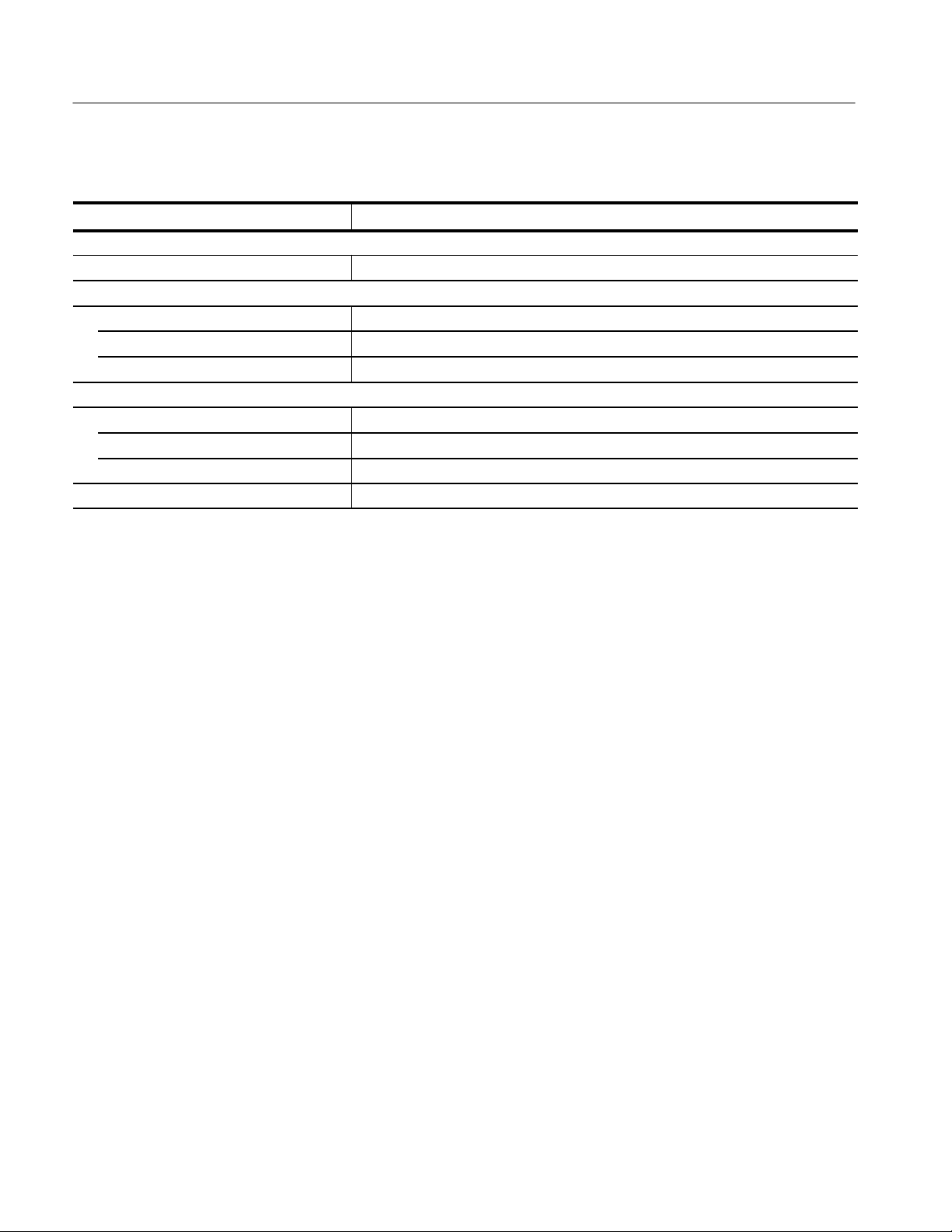

Table 3–1: Microprocessor signal characteristics 3–1. . . . . . . . . . . . . . . .

Table 3–2: Signal source characteristics 3–3. . . . . . . . . . . . . . . . . . . . . . . .

Table 3–3: Hardware characteristics 3–4. . . . . . . . . . . . . . . . . . . . . . . . . .

Table 3–4: Power distribution characteristics 3–5. . . . . . . . . . . . . . . . . .

Table 3–5: Mechanical characteristics 3–6. . . . . . . . . . . . . . . . . . . . . . . . .

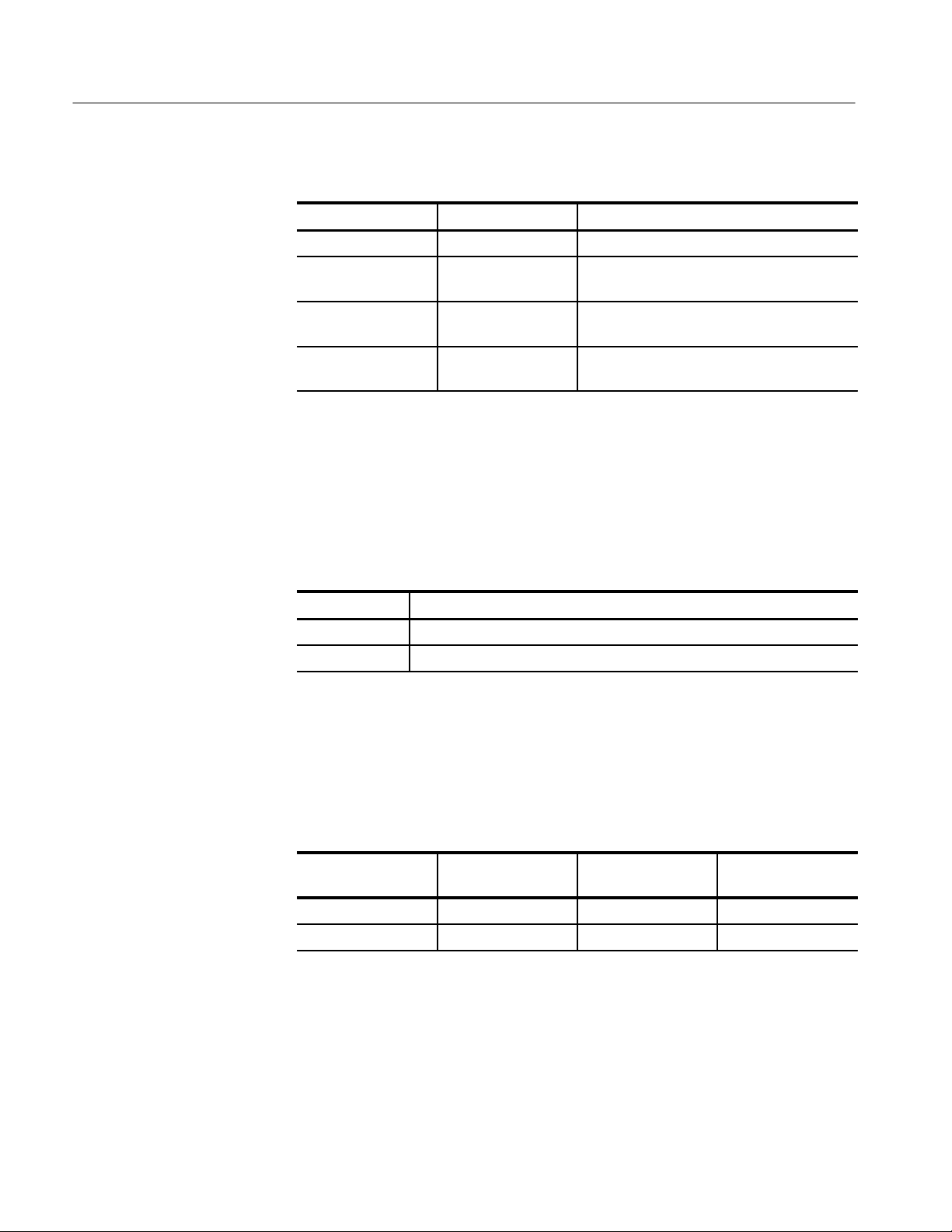

Table 4–1: Output control bits 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 4–2: Pattern generator clock select truth table 4–4. . . . . . . . . . . . .

Table 4–3: Sigclk2 selections 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 4–4: Counter-pattern generator addresses 4–4. . . . . . . . . . . . . . . .

Table 4–5: LOCNTRSEL bit operation 4–6. . . . . . . . . . . . . . . . . . . . . . . .

Table 4–6: PATCLKSEL0 and PATCLKSEL1 bit operation 4–6. . . . . .

Table 4–7: Serial Port B pinout (J500) 4–11. . . . . . . . . . . . . . . . . . . . . . . . .

Table 4–8: Serial Port A pinout (J600) 4–11. . . . . . . . . . . . . . . . . . . . . . . . .

Table 4–9: Logic analyzer control port signals (J400) 4–12. . . . . . . . . . . .

Table 4–10: BDM mode connector(J200) 4–13. . . . . . . . . . . . . . . . . . . . . . .

Table 4–11: JTAG port (J601) 4–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table 4–12: Bus interface connector (J180) 4–15. . . . . . . . . . . . . . . . . . . . .

Table 5–1: Test equipment 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Table A–1: TLA 7QS System software files A–1. . . . . . . . . . . . . . . . . . . . .

vi

TLA QuickStart Technical Reference Manual

General Safety Summary

Review the following safety precautions to avoid injury and prevent damage to

this product or any products connected to it. To avoid potential hazards, use this

product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read

the General Safety Summary in other system manuals for warnings and cautions

related to operating the system.

To Avoid Fire or

Personal Injury

Connect and Disconnect Properly . Do not connect or disconnect probes or test

leads while they are connected to a voltage source.

Observe All Terminal Ratings. To avoid fire or shock hazard, observe all ratings

and marking on the product. Consult the product manual for further ratings

information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal, that

exceeds the maximum rating of that terminal.

Use Proper AC Adapter. Use only the AC adapter specified for this product.

Do Not Operate Without Covers. Do not operate this product with covers or panels

removed.

Use Proper Fuse. Use only the fuse type and rating specified for this product.

Avoid Exposed Circuitry. Do not touch exposed connections and components

when power is present.

Do Not Operate With Suspected Failures. If you suspect there is damage to this

product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry .

Provide Proper Ventilation. Refer to the manual’s installation instructions for

details on installing the product so it has proper ventilation.

TLA QuickStart Technical Reference Manual

vii

General Safety Summary

Symbols and Terms

T erms in this Manual. These terms may appear in this manual:

WARNING. Warning statements identify conditions or practices that could result

in injury or loss of life.

CAUTION. Caution statements identify conditions or practices that could result in

damage to this product or other property.

T erms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the

marking.

WARNING indicates an injury hazard not immediately accessible as you read the

marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

WARNING

High Voltage

Protective Ground

(Earth) T erminal

CAUTION

Refer to Manual

Double

Insulated

viii

TLA QuickStart Technical Reference Manual

Service Safety Summary

Only qualified personnel should perform service procedures. Read this Service

Safety Summary and the General Safety Summary before performing any service

procedures.

Do Not Service Alone. Do not perform internal service or adjustments of this

product unless another person capable of rendering first aid and resuscitation is

present.

Disconnect Power. To avoid electric shock, disconnect the main power by means

of the power cord or, if provided, the power switch.

Use Care When Servicing With Power On. Dangerous voltages or currents may

exist in this product. Disconnect power, remove battery (if applicable), and

disconnect test leads before removing protective panels, soldering, or replacing

components.

To avoid electric shock, do not touch exposed connections.

TLA QuickStart Technical Reference Manual

ix

Preface

The TLA 7QS Technical Reference Manual is an optional accessory to the TLA

7QS package. It is intended to provide technical and service information for the

TLA 7QS training board.

How to Use This Document

The manual is made up of the following sections:

The Getting Started chapter provides a brief overview of the product.

The Reference chapter consists of basic reference information on the training

The Specifications chapter lists specifications and various characteristics of

The Theory of Operation chapter describes the basic operation of the

board. It consists of subsections describing the hardware features, software

features, memory maps, and programming information for using the training

board.

the training board.

electronic circuitry on the training board. This chapter can be used in

conjunction with the schematics to provide an overall understanding of the

operation and capabilities of the training board.

The Functional Verification Procedures chapter provides information for

verifying functional operation beyond the power-on diagnostics.

The Maintenance chapter provides information on the basic service strategy,

static handling procedures, inspection and cleaning procedures, simple

troubleshooting procedures, and repackaging instructions.

The Replaceable Electrical Parts chapter lists the electronic components on

the training board.

The Schematics chapter provides individual schematics for the circuitry on

the training board.

The Replaceable Mechanical Parts chapter lists the mechanical replaceable

parts and accessories for the training board.

Appendix A: Source Code provides information on the program code used

with the training board software. It also provides examples of code that can

be used to create programs and to download them to the training board.

TLA QuickStart Technical Reference Manual

xi

Preface

Related Documentation

Manual Conventions

Several other pieces of documentation are available to use with the TLA 700

Series Logic Analyzers. The information consists of both online documentation

and paper copies.

The TLA 700 Series Logic Analyzer User Manual provides basic user

information for the TLA 700 Series Logic Analyzers.

Use the online help in the TLA 700 Series logic analyzer to obtain operating

information and for specific information on windows, menus, and fields

within the application.

The TLA 7QS QuickStart Training Manual provides examples of exercises to

demonstrate the capabilities of the TLA 700 Series logic analyzers.

The following manual conventions are found in this document:

Contacting Tektronix

Active low signals are identified by an asterisk (*) after the signal name.

The term training board represents the TLA 7QS QuickStart training board.

Product

Support

Service

Support

For other

information

To write us Tektronix, Inc.

For application-oriented questions about a Tektronix measurement product, call toll free in North America:

1-800-TEK-WIDE (1-800-835-9433 ext. 2400)

6:00 a.m. – 5:00 p.m. Pacific time

Or contact us by e-mail:

tm_app_supp@tek.com

For product support outside of North America, contact your

local Tektronix distributor or sales office.

Contact your local Tektronix distributor or sales office. Or visit

our web site for a listing of worldwide service locations.

http://www.tek.com

In North America:

1-800-TEK-WIDE (1-800-835-9433)

An operator will direct your call.

P.O. Box 1000

Wilsonville, OR 97070-1000

xii

TLA QuickStart Technical Reference Manual

Getting Started

Product Description

This document provides technical reference information for the TLA 7QS

training board. The manual provides information for running the embedded

programs, downloading user-defined programs from a host, specifications,

schematics, parts lists, and miscellaneous service information.

The TLA 7QS training board is used to demonstrate the Tektronix logic analyzer

products. It consists of an electronic circuit board with rubber feet standoff and a

digital display. The circuit board has a built-in M68340 microcontroller with

supporting electronic circuitry, and several connectors.

The training board has several embedded programs accessible by the user

interface or by a remote host connection. The embedded programs are designed

to send digital and analog signals to the various connectors on the training board.

These signals can be used to demonstrate the capabilities of the TLA 700 Series

Logic Analyzers.

The training board is used with the TLA 7QS Training Manual. The training

manual provides examples of using the training board to demonstrate the

capabilities of the TLA 700 Series Logic Analyzers.

Accessories

The training board is available with the following standard accessories:

TLA 7QS Training Manual

TLA 7QS Software

Wall mount power adapter (power dependent on country)

The TLA 7QS Technical Reference Manual is available as an optional accessory

and comes with the TLA 7QS. development software.

Configuration

The default training board has no configurations. The training board can be set

up, however, to download user specific programs. The programs reside in the

flash memory.

TLA QuickStart Technical Reference Manual

1–1

Getting Started

Functional Check

The basic operation of the TLA 7QS training board is verified by the power-up

diagnostics. The power-up diagnostics run at power-on or when the RESET

signal is asserted by pressing the RESET button.

To perform a more detailed functional verification of the training board, refer to

the Functional Verification Procedures beginning on page 5–1.

1–2

TLA QuickStart Technical Reference Manual

Hardware Features

This section describes the hardware features of the TLA 7QS training board. It

provides information on using the hardware to demonstrate features of logic

analyzers and oscilloscopes. Detailed information on individual circuits is

provided in the Theory of Operation beginning on page 4–1.

Circuit Board Modules

The training board can be divided into the following circuit board modules:

Microprocessor module

Signal sources module

User interface module

Input/output module

Power supply module

Microprocessor Module

The microprocessor module consists of a Motorola M68340 microcontroller in a

TQFP package and the associated static RAM and flash memory. The flash

memory is divided into a user flash and system flash. The user flash area is

intended for use with additional applications; it can be modified with the proper

software development tools. The system Flash is initially programmed at the

factory and can be updated by field service upgrade kits (when they become

necessary).

Microprocessor Chip Selects. Four programmable chip select lines are used on

the training board. Table 2–1 lists the chip select lines and how they are used.

For information on the memory mapping, refer to Memory Maps beginning on

page 2–22.

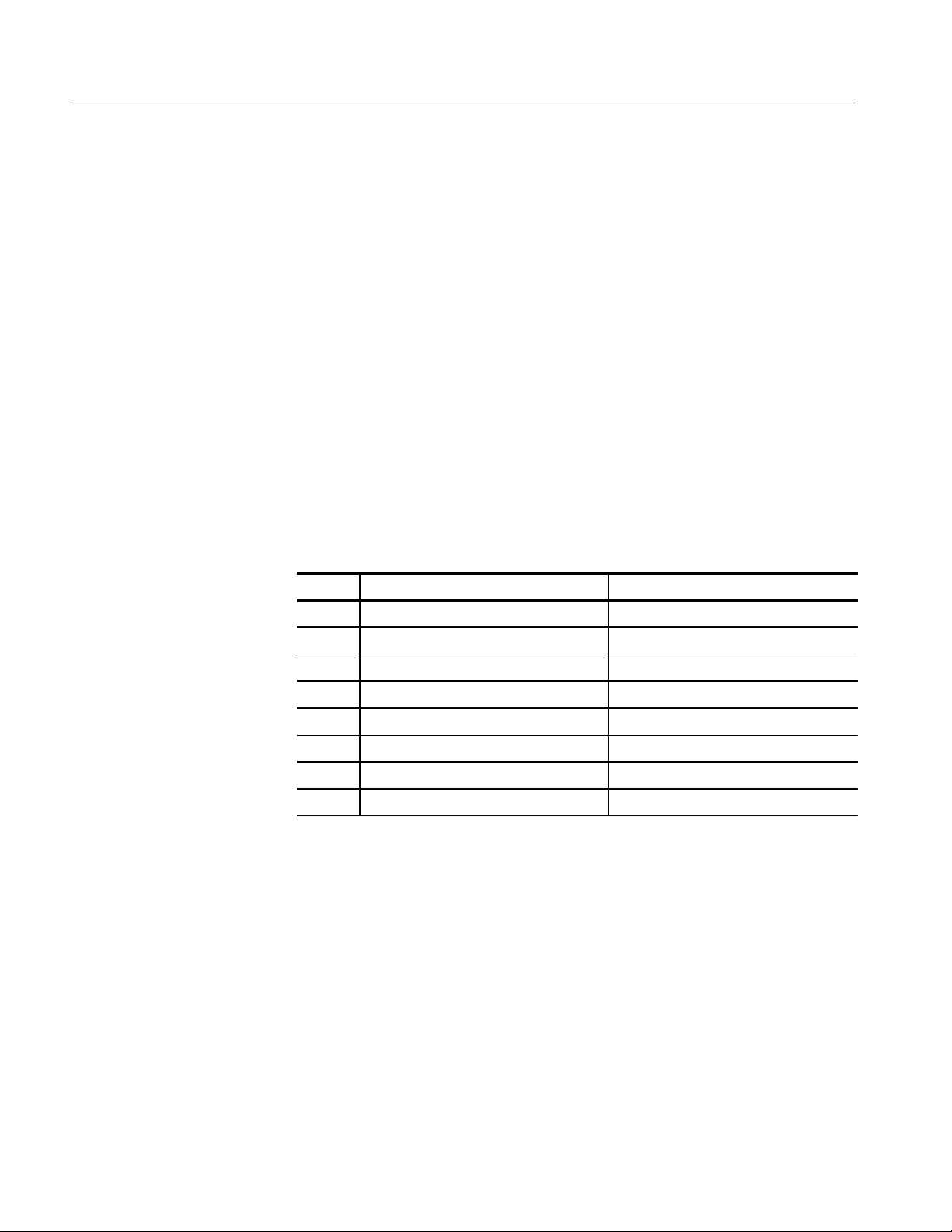

T able 2–1: Microprocessor chip select lines

Chip

select

CS0* Boot and system Flash ROM

CS1* User and system RAM

CS2* User and application ROM

CS3* Memory mapped input and output

Memory space usage

TLA QuickStart Technical Reference Manual

2–1

Hardware Features

Microprocessor Interrupts. Four external interrupts are used on the training board:

IRQ3*, IRQ5*, IRQ6*, and IRQ7*. You can assert the signals through the push

buttons on the training board or through the parallel control port.

Microprocessor Parallel Input/Output Port. The microprocessor has a general

purpose parallel input/output port (PORTA) that uses the upper eight address

lines. The port is used for general purpose (application defined) input and output

bits, serial clock bits, and serial data bits. Table 2–2 shows the bits of the port

and the corresponding signals. The PORTA signals are accessible on bus

interface connector (J180).

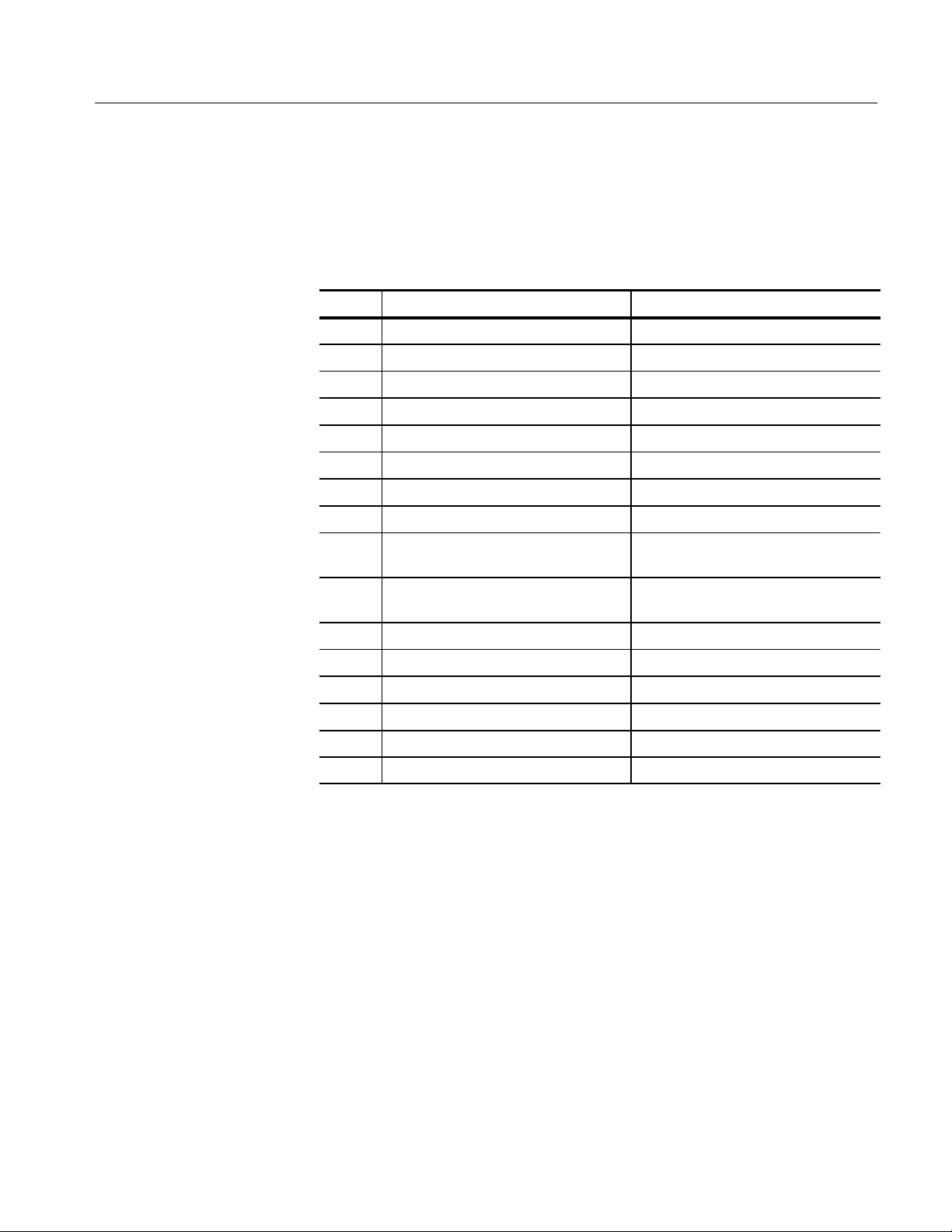

T able 2–2: PORTA signals

Bit Signal name Function

0 SCL Serial clock bit

1 SDA Serial data bit

2 CNTLIN1 Application defined input control bit

3 CNTLIN2 Application defined input control bit

4 CNTLIN3 Application defined input control bit

5 CNTLOUT1 Application defined output control bit

6 CNTLOUT2 Application defined output control bit

7 CNTLOUT3 Application defined output control bit

Microprocessor Output Bits. The microprocessor has an output port that shares

the signal lines with the signal lines of the dedicated serial ports (A and B). Two

of the bits have specific uses. The OP4 bit generates the clears the external

trigger input. The OP6 bit generates the trigger output signal (EXTRIGOUT).

Both signals are active low signals.

Delay Line Memory. The delay line memory is a 16-bit read and write register to

demonstrate setup and hold timing violations during read operations. Data can be

written and then read from the same memory location; the data read should equal

the written data. When you program the delay line with a small delay, a setup

violation occurs during the read operation and the data read back will be different

than the written data. When you program the delay line with a large delay, a hold

violation occurs during the read operation and the returned data will be different

than the written data.

2–2

TLA QuickStart Technical Reference Manual

Clockout

Dlyclksel0

Dlyclksel1

Data<0..15>

Delayed

read strobe

gen logic

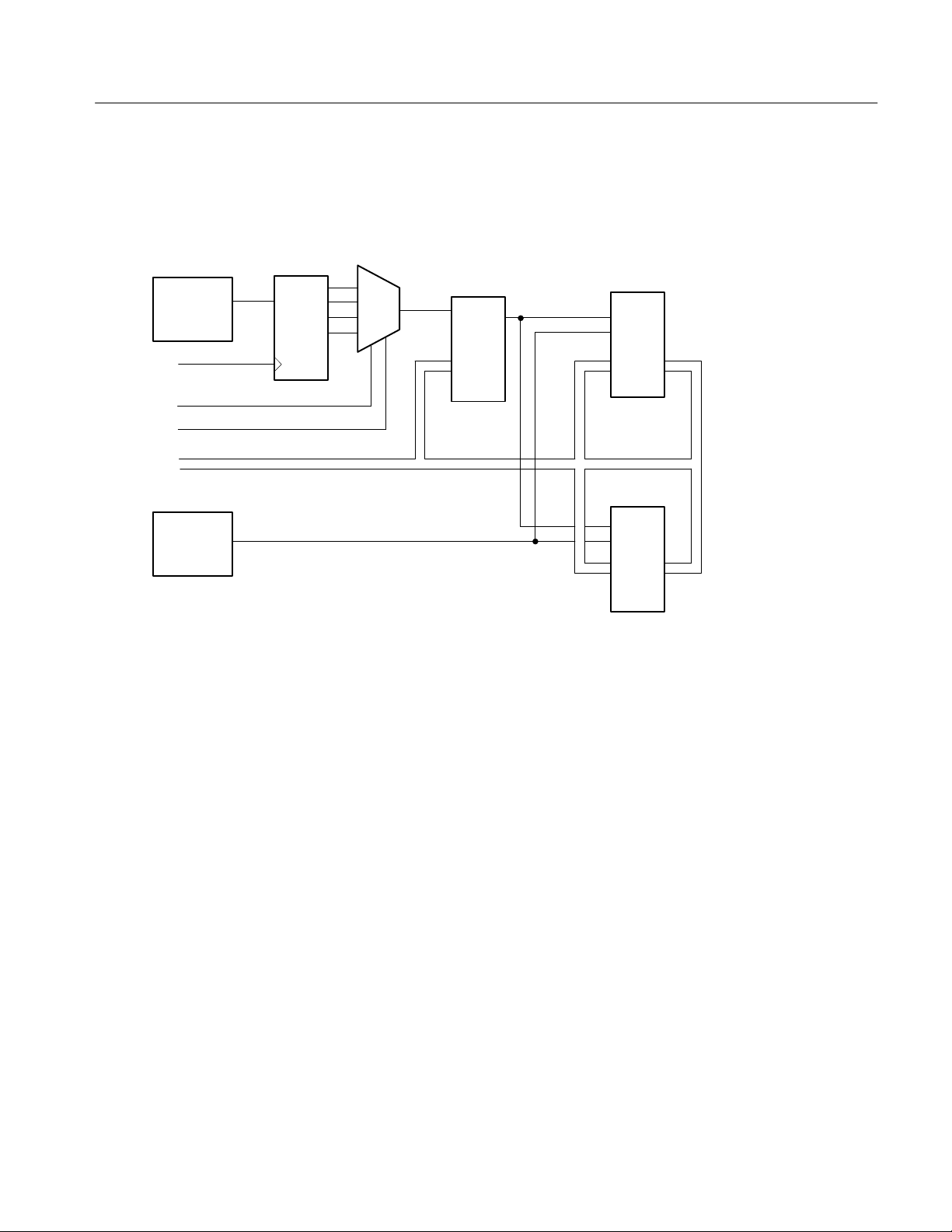

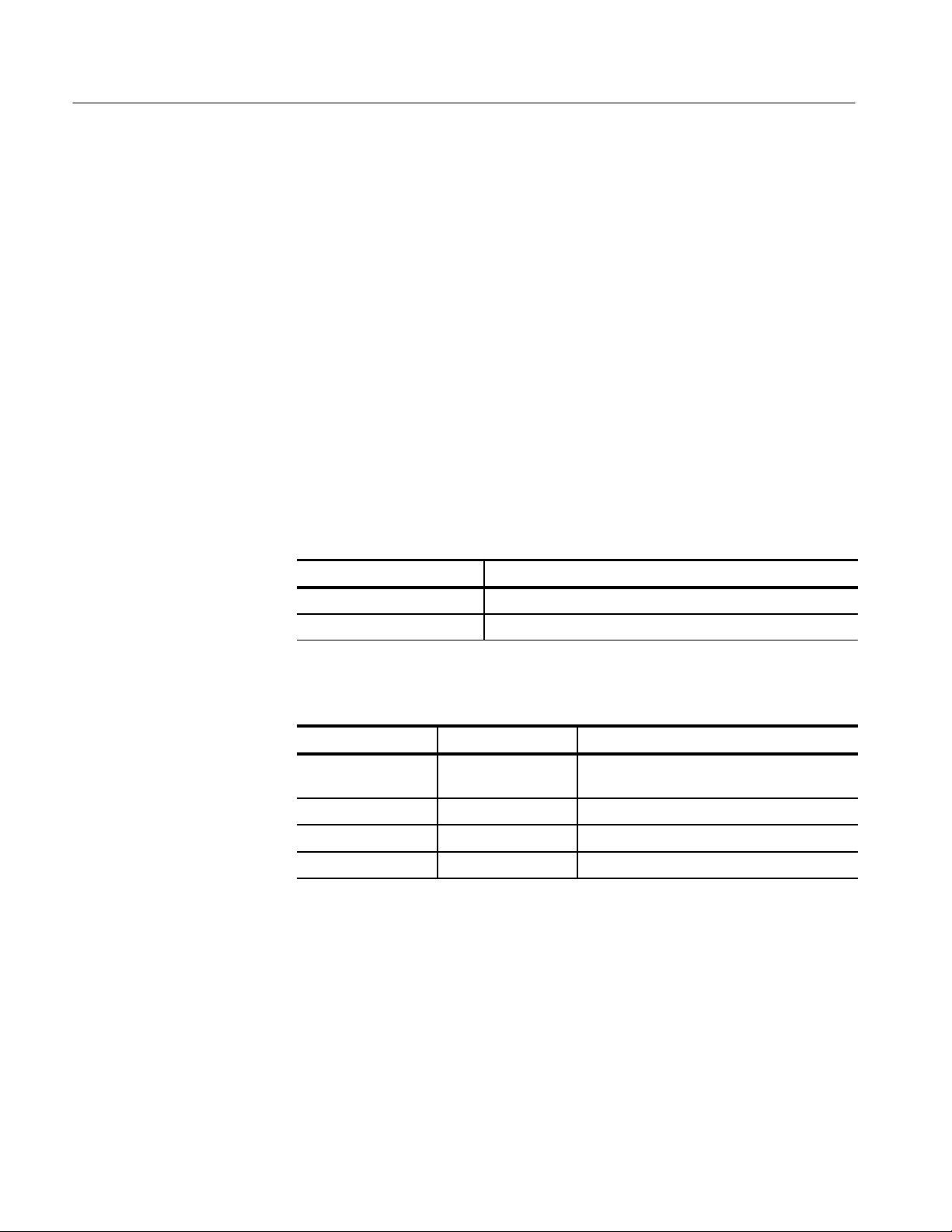

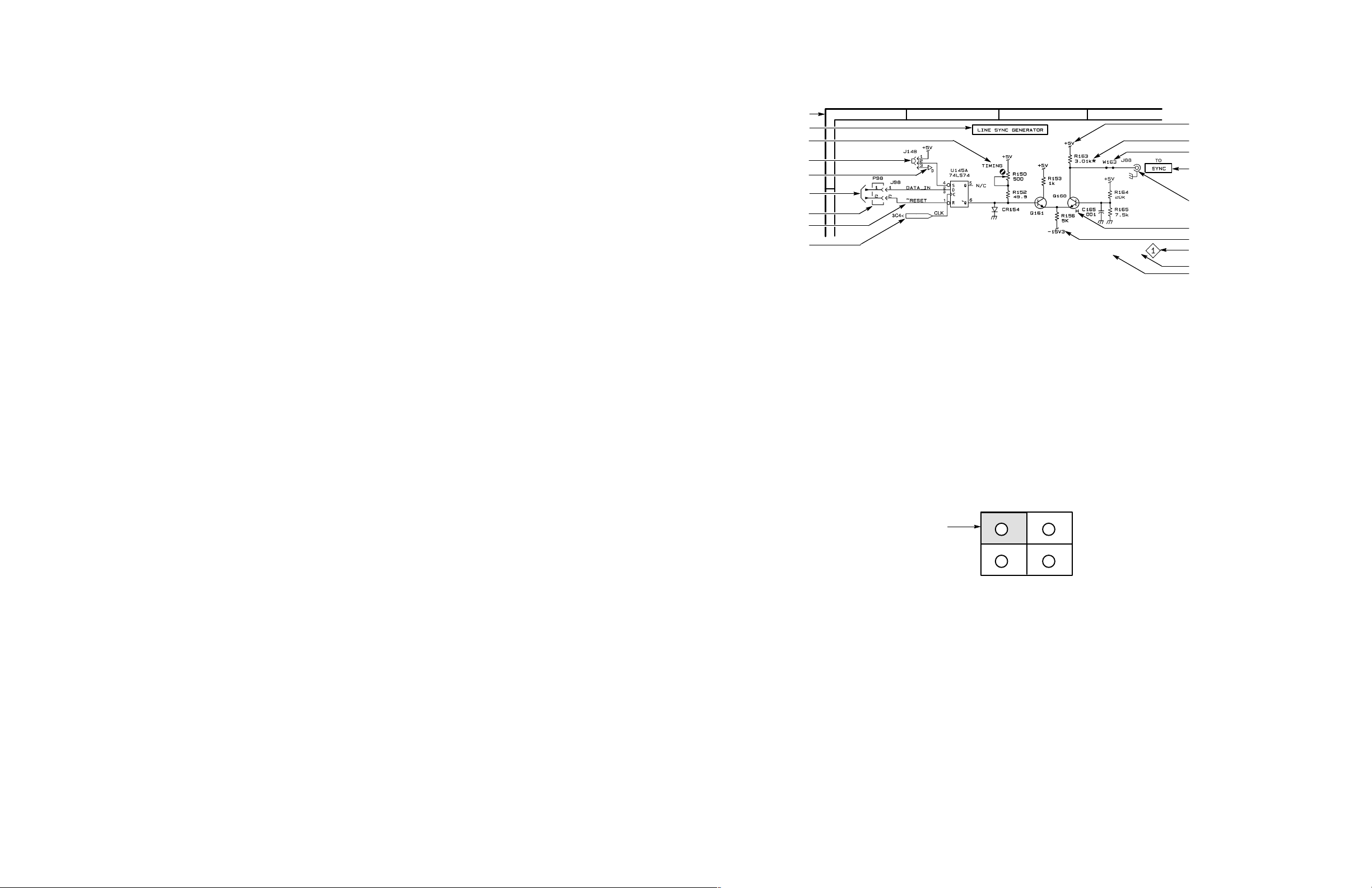

Figure 2–1 shows a block diagram of the programmable delayed read memory.

Read strobe delay

shift register

62 ns/Step

Shift

register

Mux

0–125 ns

programmable

delay

In

Out

Prog.

delay

line

Hardware Features

Upper byte

memory

OE

CLK

Data<8..15>

Lower byte

memory

Read/Write

logic

Figure 2–1: Programmable delayed read memory block diagram

Programmable Delay Clock Select. The programmable delay clock select consists

of a serial shift register clocked by the microprocessor system clock. The input to

the shift register is the delayed shift register read strobe which is delayed in

multiples of the clock period. The input read strobe and three output bits of the

shift register are routed to a four-bit input multiplexer. The multiplexer selects

one of the four read strobes.

Programmable Delay Line. The programmable setup and hold delay line is an

eight-bit register with 256 programmable delay settings. The delay line delays

the read strobe to the delay line memory to demonstrate setup and hold timing

violations. Each delay count increment is a 0.5 ns time delay. The minimum

delay is 00 and the maximum is FF.

OE

CLK

Data<0..7>

TLA QuickStart Technical Reference Manual

2–3

Hardware Features

Signal Sources Module

The signal sources module consists of the following groups of signals that can be

used to demonstrate logic analyzer and oscilloscope features:

Counter and pattern generator signals

Setup & Hold and trigger signals

Tapped delay line

Burst signal

Glitch signal

Metastable data and clock signals

Step signal

Runt pulse and missing pulse signal

Single-shot and narrow pulse signal

Staircase signal

Counter and Pattern Generator Signals. You can use the two 16-bit (or one 32-bit)

counter and pattern generators to demonstrate multiple logic analyzer and logic

scope capabilities. Both counter and pattern generators can be configured by

software. The counters can be programmed to count up or down. They can be

clocked by the 50 MHz oscillator or through an external trigger input.

Setup and Hold Trigger Signals. Use the setup and hold trigger signals to

demonstrate how logic analyzers can measure or trigger on setup and hold

signals. The setup and hold signals are generated by a four-bit counter. The

counter can be controlled by software to demonstrate setup violations or hold

violations.

T apped Delay Line. Use the tapped delay line as basic pattern generator to show

signal skew, timing resolution, and sampling rates.

Burst Signal. Use the burst signal to demonstrate logic analyzer transitional

timing.

Glitch Signal. Use the glitch signal to demonstrate logic analyzer and oscilloscope

triggering.

Metastable Data and Clock Signals. Use the metastable data and clock signals to

demonstrate logic analyzer and oscilloscope setup and hold triggering.

2–4

TLA QuickStart Technical Reference Manual

Hardware Features

Step Signal. Use the step signal to demonstrate analog bandwidth and triggering

of oscilloscopes and logic analyzers.

Runt Pulse and Missing Pulse Signal. Use the runt pulse and missing pulse signal

to demonstrate oscilloscope pulse triggering features. You can also use it to

demonstrate logic analyzer 4 ns counter/timers and time-qualified triggers.

Single-Shot Narrow Pulse Signal. Use the single-shot narrow pulse signal to

demonstrate analog bandwidths of oscilloscopes and logic analyzers. You can

also use this signal to demonstrate real-time sampling capabilities of the

oscilloscopes and logic analyzers.

Staircase Signal. Use the staircase signal to demonstrate the oscilloscope

acquisition modes and glitch detection.

User Interface Module

The user interface module consists of the following elements:

A two-line by 16-character LCD display

Four push-button switches

A reset switch

Two 10-segment LED indicators

LCD Display . The main display device is a two line by 16 character LCD display.

The readout is controlled by software and by the four push-button switches.

The microprocessor communicates with the display by placing the upper eight

bits on the data bus. The LCD display has a register select (RS) bit. When the

RS bit is low, it selects the instruction register; when the bit is high, it selects the

data register.

Push-button Switches. The four push-button switches connect to the four external

interrupt lines of the microcontroller. The switches select and control the

programs in the training board. The LCD readout displays the push-button

switch functions. The right-most switch halts the program and asserts a

nonmaskable interrupt (NMI) signal to IRQ7.

Reset Switch. The Reset switch is a momentary push-button switch that provides

a system reset to the microcontroller.

TLA QuickStart Technical Reference Manual

2–5

Hardware Features

LED Indicators. Two 10-segment LED indicators display bit patterns for various

software and hardware demonstrations. The first sixteen LED segments (labeled

0 through 15) represent data bits. Bits 16 and 17 represent the LAPort input and

output enable status. Bit 18 indicates whether the external trigger input is

enabled. Bit 19 shows the status of the Halt signal line.

Input and Output Connectors

The TLA 7QS Training Board has the following input and output port connectors:

Two serial ports

A logic analyzer control port

Two trigger BNC connectors

A background debug mode connector

A JTAG connector (pins not installed on board)

Power input connectors

Bus interface connector

These connectors and their pin information are described in the Theory of

Operation chapter beginning on page 4–9.

Serial Port Requirements

Serial Port B is the main serial port for connecting the training board to an

external host. It is also used to monitor programs and to download and execute

firmware. The serial port uses hardware handshaking to control communications

between the host and the training board.

In addition to the minimum RS-232 signals (RX, TX, and GND) for serial

communications, the handshaking signals (CTS and RTS) are required for

connection between a terminal (or computer) and the training board.

Serial Port B on the training board is designed as a DTE (data terminal equipment) device. Most terminals and personal computers with serial ports are also

configured as DTE devices. Therefore, the signal connections between the

terminal and Serial Port B on the training board may require an null modem

connection.

2–6

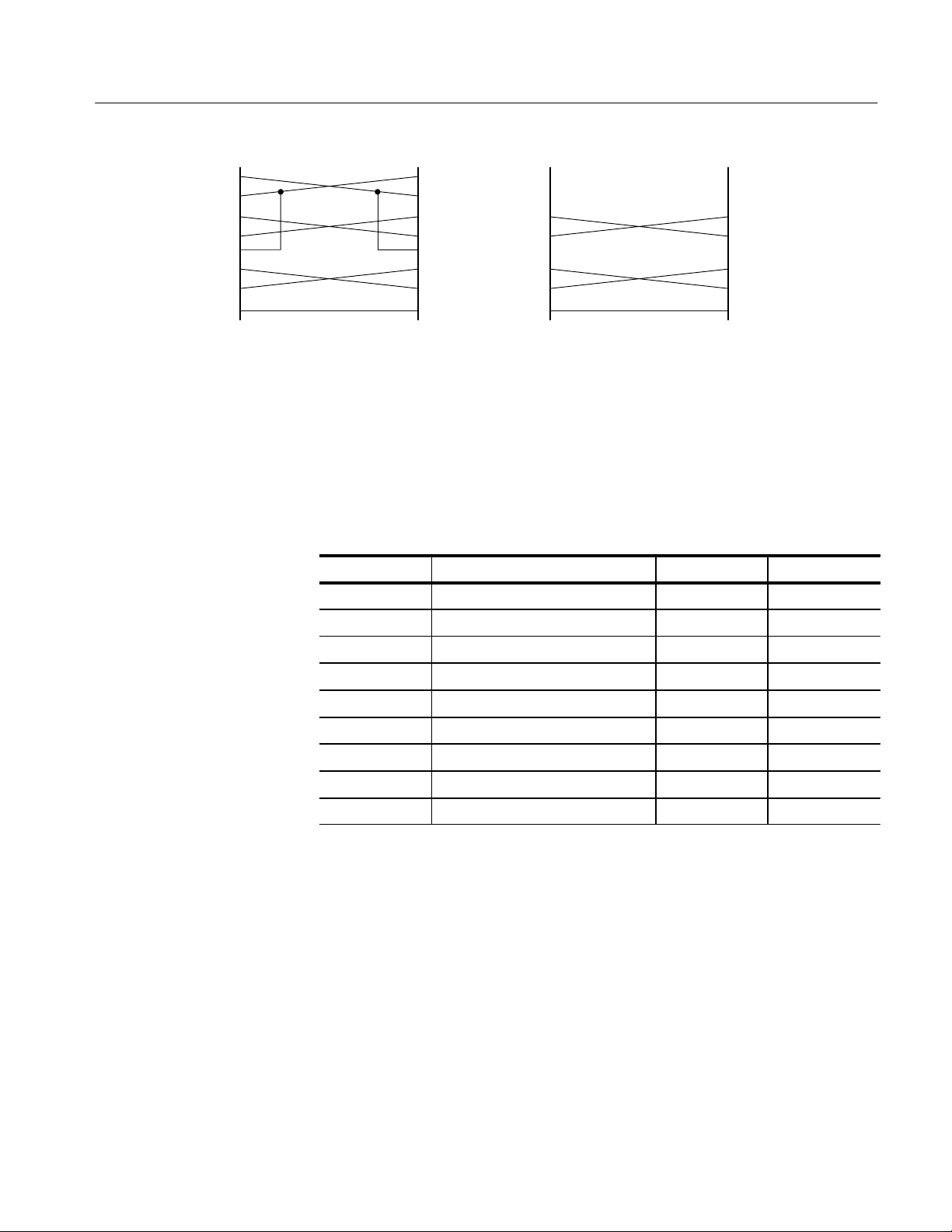

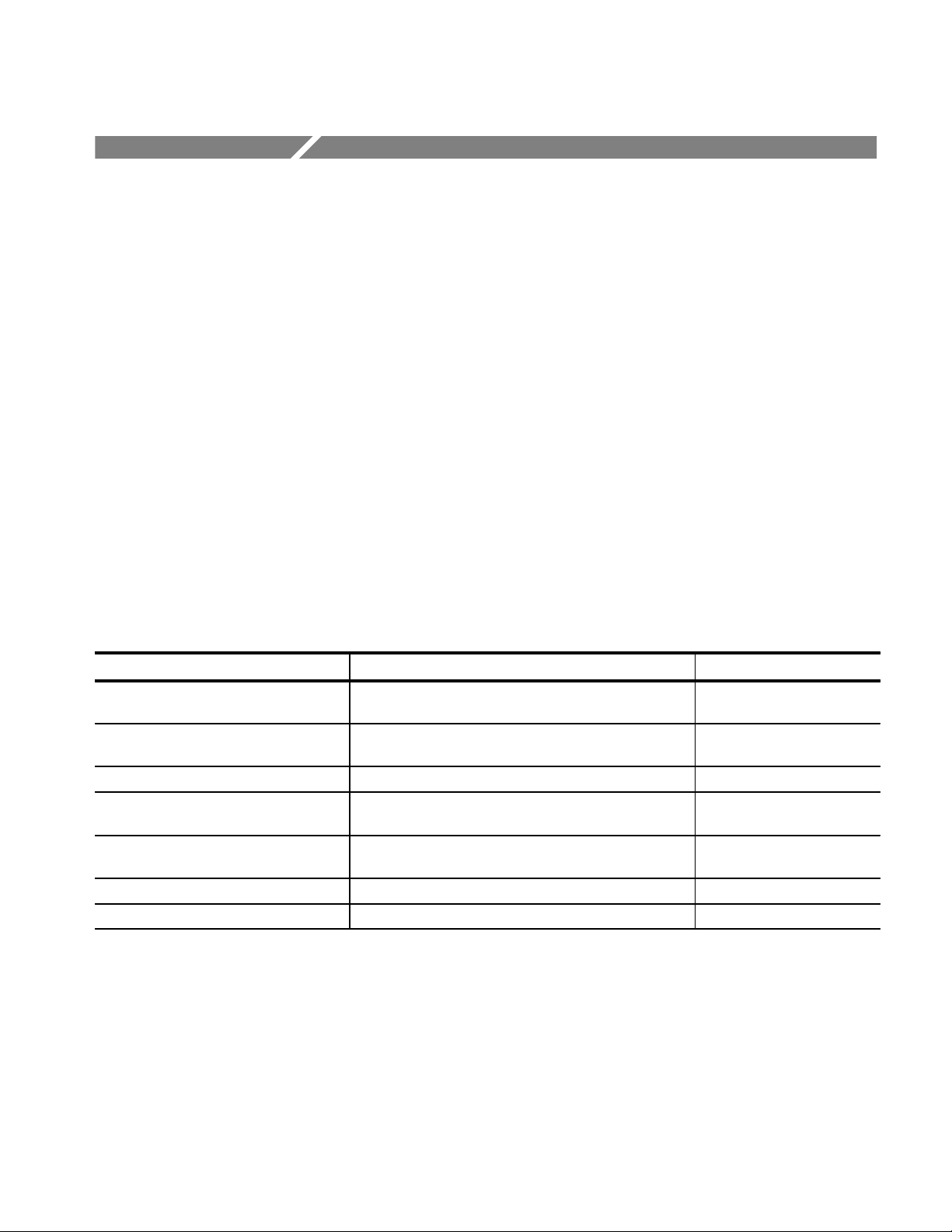

The left side of Figure 2–2 shows the standard full null modem connection. The

minimum null modem connection required for the training board is shown on the

right side of Figure 2–2.

TLA QuickStart Technical Reference Manual

Hardware Features

DTR

DSR

RTS

CTS

DCD

TXD

RXD

GND

Standard null modem connection Minimum null modem connection

DTR

DSR

RTS

CTS

DCD

TXD

RXD

GND

DTR

DSR

RTS

CTS

DCD

TXD

RXD

GND

required for the training board

Figure 2–2: Null modem connections

Table 2–3 shows the connector pinouts for the DB9 and DB25 serial port

connectors.

T able 2–3: RS-232 connector pinouts

Signal Name DB9 pins DB25 pins

DCD Data carrier detect 1 8

RXD Receive data 2 3

DTR

DSR

RTS

CTS

DCD

TXD

RXD

GND

TXD Transmit data 3 2

DTR Data terminal ready 4 20

GND Signal ground 5 7

DSR Data set ready 6 6

RTS Request to send 7 4

CTS Clear to send 8 5

RI Ring indicator 9 22

For more information on the serial ports on the training board refer to the Serial

Ports on page 4–11.

TLA QuickStart Technical Reference Manual

2–7

Software Features

This section describes software operation, embedded programs, and diagnostics

available with the TLA 7QS Training Board.

When you first apply power to the the training board, or when you press the

Reset button, the training board initializes the 68340 registers, runs the power-on

diagnostics, and then starts the normal operation.

Operating Modes

There are three modes of normal operation for the training board:

Stand-alone mode

Host-controlled mode

Debug mode

The software routines are available in both stand-alone operation and host

controlled mode (unless specified otherwise).

Stand-Alone Mode

Host-Controlled Mode

In the stand-alone mode, operation of the training board is controlled by the

button interface. All program information is sent to the liquid crystal display

(LCD). Menu selections are displayed on the LCD as well as the current function

of the four buttons mounted directly below the display.

You can scroll through the menu selection by pressing the UP or DN (down)

buttons. Pressing the RUN button starts the selected software routine. Pressing

the STOP button halts the selected routine. The display on the LCD may change

depending on the selected software routine. Refer to LCD User Interface on page

2–15 for more detailed information on controlling the training board in the

stand-alone mode.

In the host-controlled mode, the operation of the training board is controlled

through Serial Port B. You can connect the training board to a host (such as a PC

running an RS-232 application such as HyperTerminal). The menu selections are

the same as in the stand-alone mode; however, because of the larger display,

more verbose descriptions are possible.

TLA QuickStart Technical Reference Manual

2–9

Software Features

NOTE. You may need to use a null modem to connect the training board to your

PC. For information on using a null modem, refer to Serial Port Requirements

on page 2–6.

Additional menu choices are available that are not used in the stand-alone mode.

These choices include downloading an S-record file to user flash memory and

starting the SDS (Software Development Systems) target monitor program. A

list of embedded programs and routines is described in detail under Embedded

Programs beginning on page 2–10.

While the training board is connected to host, the training board operation can

still be controlled from the buttons and data will be displayed on the LCD as

well as on the remote menu.

Debug Mode

Main Software Routine

Embedded Programs

The debug mode is intended to be used during program development. While in

the debug mode, the training board runs a target monitor (a ROM resident

program) that communicates with the SDS SingleStep development software.

The debug mode lets you develop, download, and test programs before you

commit them to flash memory. The debug mode also provides direct access to

the hardware on the training board.

The main software routine is a message processor that runs in an endless loop.

User and instrument actions, such as pressing a button, generate messages which

are posted to a message stack. The routine continuously checks the stack for

messages and sends new messages to the appropriate action routine.

Most messages are generated by an interrupt service routine. The buttons,

timers, and RS-232 circuitry have individual interrupt service routines. When an

interrupt is serviced, the interrupt service routine posts the appropriate message

to the message stack and then returns control to the processor.

2–10

This section describes the embedded programs that are available with the current

version of the training board. The programs, routines, or tests described in this

subsection are available at product introduction. Others can be added by the user

as necessary.

The programs use several subroutines to provide logic analyzers a means of

demonstrating performance analysis. All initialized variables are mapped into

SRAM so values can be changed. The variables return to the default values at

power-on or when the training board is reset.

TLA QuickStart Technical Reference Manual

Software Features

LITES

STOP LITES

STRINGS

COUNTER

The Lites program strobes the LED segments from right to left and then left to

right. The program also writes the phrase “Making It Happen” to Serial Port B.

The Stop Lites program lights specific LEDs in a predetermined sequence. The

LEDs are lighted in a sequence to emulate two traffic lights (hence the name

Stop Lites). One set of lights change from green to amber to red. After the light

is red, a second set of lights cycles from green to amber to red. The sequence

continues until interrupted by the user.

The Strings program continuously sends the string “The quick brown fox jumped

over the lazy dog” to Serial Port B.

The Counter program controls the counter-pattern generator circuitry on the

training board (J840, J940, J830, and J930). Push the RUN button to start the

program and to display the current settings. To change any of the settings, push

the F1, F2, or F3 buttons. You can change the program settings by pushing the

appropriate buttons as described below:

Push the F1 button to select the counter size, 16 bits or 32 bits.

Push the F2 button to select the counter direction, up or down.

PATTERN GEN

SHOW CYCLES

Push the F3 button to select the counter clock source, internal or external.

Push the F4 button to accept the changes.

The Pattern Gen program controls the counter-pattern generator circuitry on the

training board (J840, J940, J830, and J930). Push the RUN button to start the

program and to display the current settings. To change any of the settings, Push

the F1, F2, or F3 buttons. You can change the program settings by pushing the

appropriate buttons as described below:

Push the F1 button to select the data pattern, A5 or F0.

Push the F2 button to select the clock speed, normal, divide-by-four,

divide-by-sixteen, or SIM timer module 2.

Push the F4 button to accept the changes.

The Show Cycle program routes the M68340 internal bus cycles to the external

bus. The logic analyzer can be set up to capture and analyze these bus cycles.

TLA QuickStart Technical Reference Manual

2–11

Software Features

WAIT STATE

INT LATENCY

PGM DELAY

The Wait State program varies the M68340 wait states from zero to three on CS2

and CS3. After starting the program, push the F1 button to select the number of

wait states. You can then use a logic analyzer to capture and analyze the impact

of the wait states on system performance.

The INT Latency program generates an interrupt at random intervals of time.

This program provides a means for logic analyzers to measure the time between

an INT assertion and an INT acknowledge. The LEDs strobe across the LED

display while the program runs.

The PGM Delay program controls the Setup and Hold circuitry on the training

board (J850). You can use the buttons to select the clock speed and to specify a

delay from 00 Hex to FF Hex.

When the program runs, it sends a value of 5555 Hex to a register and is then

read back. The read select line is delayed by the programmed amount. The

resulting value is displayed by the LED bank. If the displayed value is not

5555 Hex, then you know that an error occurred.

Push the RUN button to start the program and to display the current settings. To

change any of the settings, push the F1, F2, or F3 buttons. You can change the

program settings by pushing the appropriate buttons as described below:

AUTO DELAY

PULSE

Push the F1 button to select the clock, normal, divide-by-two, divide-by-

four, or divide-by-eight.

Push the F2 button to change the most-significant byte of the delay value.

Push the F3 button to change the least-significant byte of the delay value.

Push the F4 button to accept the changes.

The Auto Delay program is similar to the PGM Delay program except that the

clock and delay times are automatically sequenced through all possible values.

The Pulse program generates a monostable pulse when you press the F1 button.

The pulse is generated by SIM timer module 1. The 1 V pulse is sent to the

PULSE pins (J971-3 and J870-5, 6) in the Analog Signals section of the training

board. A TTL-level pulse is available on the C0-4 section (T1) of the microprocessor signals section on J750-5.

2–12

TLA QuickStart Technical Reference Manual

Software Features

SETUP/HOLD

PGM FLASH

The Setup/Hold program controls the Setup and Hold circuitry on the training

board (J850). The program sends a four bit count pattern to DATA pins 0–3

(J850-1 though J850-4). The same pattern is sent to the QOUT pins 0–3 (J850-5

through J850-8). However, the count data at the QOUT pins is skewed by a

specified amount of time.

Push the RUN button to start the program and to display the current settings. To

change any of the settings, Push the F1, F2, or F3 buttons. You can change the

program settings by pushing the appropriate buttons as described below:

Push the F1 button to select the clock, normal, Setup (CLK 2), or Hold

(CLK 1).

Push the F2 button to enable (YES) or disable (NO) a toggle feature. The

feature toggles the clock between Normal and Hold or between Setup and

Hold when a count of 0A H is reached.

Push the F4 button to accept the changes.

The PGM flash program provides a means for loading user programs into the

User area of the flash ROM. You can also use the program to bulk-erase the user

flash ROM. Any new user programs will be added to the menu display and can

be selected in the same manner as any other program. To use this program, you

must be operating in the host-controlled mode. Instructions for creating a new

user program are described in Creating Programs for the Training Board

beginning on page 2–29.

LAPORT ENABLE

CAUTION. Exiting or interrupting the program prematurely can corrupt the user

flash memory. Do not execute this program if you are not operating in the

host-controlled mode.

If you start the program from the training board, you will be asked to verify your

intentions (select YES to continue, NO to exit the program). You can only exit or

interrupt the program by pushing the Reset button on the training board.

The LAPort Enable program controls the LAPort functions of the training board.

The LAPort is normally enabled during reset or when you apply power to the

training board. This program allows you to enable or disable the port.

Push the RUN button to start the program and to display the current settings. To

change any of the settings, push the F1 button. You can change the program

settings by pushing the appropriate buttons as described below:

Push the F1 button to enable or disable the port.

Push the F2 button to count up to select the port lines.

TLA QuickStart Technical Reference Manual

2–13

Software Features

Push the F3 button to count down to select the port lines.

Push the F4 button to accept the changes.

The three LAPort lines are selected by binary values from the F2 or F3 buttons.

The value written to the output is displayed on the LCD as a binary number. For

example, to set the LAPort output line 1 high and others low, select the binary

value 010.

TRIG ENABLE

DIAGS

MONITOR

The Trig Enable program enables or disables the Trigger In or Trigger Out

features on the training board. When enabled, a Trigger In signal will generate an

IRQ7 interrupt and a Trigger Out signal will generate an IRQ6 interrupt.

When disabled, the Trigger In signal functions as an external clock for the

counters. The Trigger Out circuitry functions normally but does not assert an

IRQ6 interrupt.

Push the RUN button to start the program and to display the current settings.

Push the F2 button to enable or disable the Trigger In and Trigger Out feature.

Push the F1 button to manually generate a Trigger Out pulse; the training board

responds by displaying an asterisk on the LCD.

The Diags program executes the extended diagnostics. For more information on

diagnostics, see Diagnostics on page 2–16.

The Monitor program starts the SDS Target Monitor routine in preparation for

running the SDS SingleStep debugger. This selection is only useful if you have a

copy of the SDS SingleStep program running on a host computer. You will be

prompted to verify your intention to run this program. To exit this program, push

the Reset button.

Interrupt Service Routines

Interrupts 3, 5, 6, and 7 have individual handlers. Each handler posts a global

message that will be read by the main function. Timer 1, Timer 2, and RS-232

can also generate interrupts that will have their own interrupt service routines.

2–14

TLA QuickStart Technical Reference Manual

LCD User Interface

Software Features

The LCD Interface consists of the liquid crystal display and four buttons on the

training board. The UP, DN, RUN, and STOP images on the LCD correspond to

the buttons located directly below the display.

UP and DN Buttons

RUN Button

STOP Button

RS-232 Interface

Pushing either button causes interrupts. The interrupts post messages to the main

routine. Push the UP button to scroll backward through a list of programs. Push

the DN button to scroll forward through a list of programs.

Push the RUN button to start a program. While a program runs, the UP, DN, and

RUN images on the display are replaced by the prompt “RUNNING.” Other

buttons are ignored, except when the program prompts you to push a button.

Push the STOP button to halt a program. Pushing the STOP button while no

tests are running has no effect.

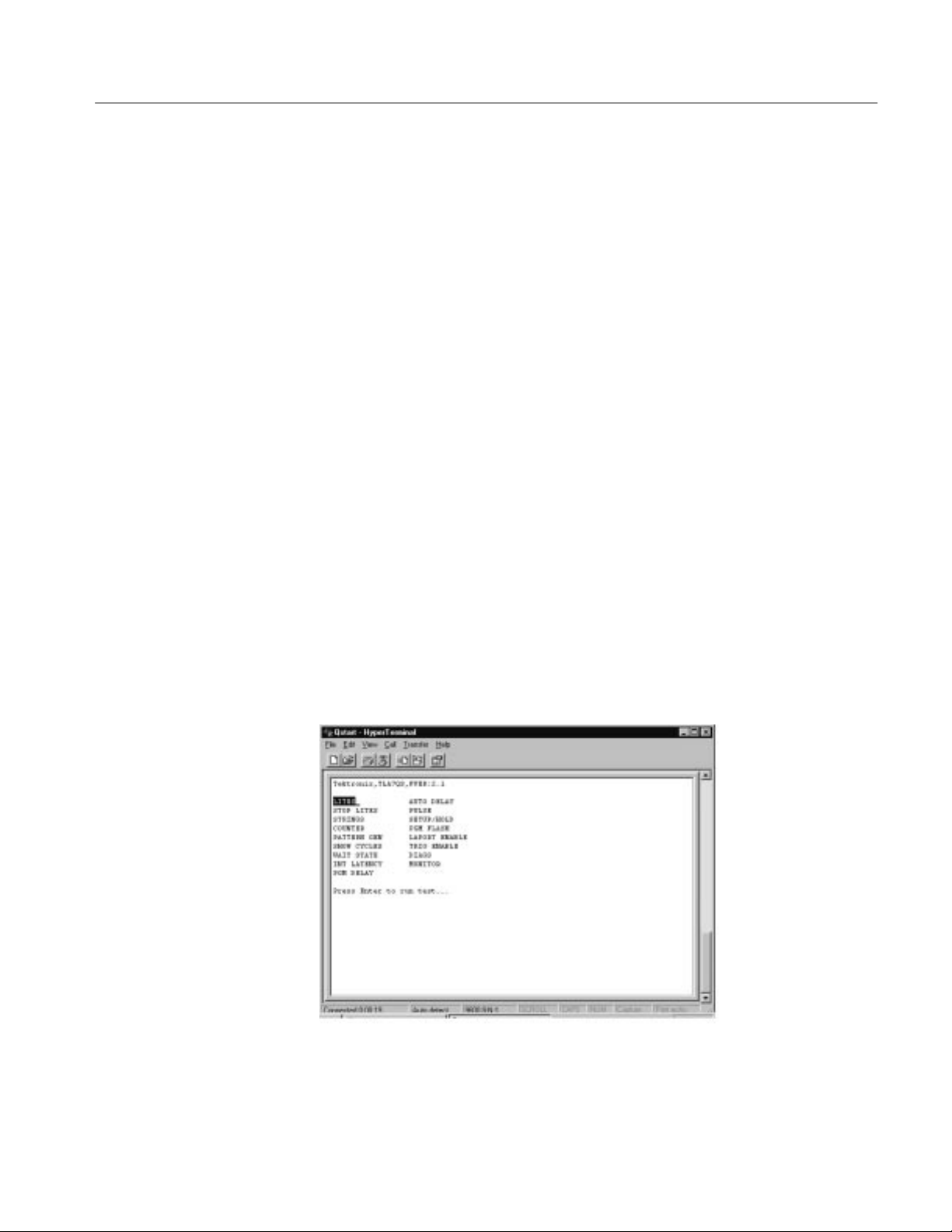

The RS-232 interface provides a means of controlling the training board from a

host. The host connects to the training board through RS-232 Serial Port B. The

interface displays a menu (see Figure 2–3) containing all of the tests programmed in the training board.

Figure 2–3: Remote menu

TLA QuickStart Technical Reference Manual

2–15

Software Features

Diagnostics

The interface runs at a baud rate of 9600 with hardware flow control. You should

use a terminal emulation program on a PC such as HyperTerminal.

The ANSI escape codes provide cursor control. Press an arrow key on the

terminal keyboard to move between highlight selections in the menu. If the

terminal does not have any arrow keys, press the J or K keys to change selections.

Press the Enter or Return key to start a program or test. The terminal displays the

following message:

Press any key to stop a test. The terminal returns control to the menu selections.

The diagnostics test the basic operation of the training board. The power-up

diagnostics run when power is applied to the training board or when the RESET

is asserted. Some of the extended diagnostics require human interaction.

LCD Test

Serial Port Tests

To start the extended diagnostics, select DIAGS on the display. Push the run

button to start the extended diagnostics. The diagnostics run automatically and

only require user interaction when connecting the RS-232 cables. The extended

diagnostics test the following areas of the training board:

LCD

Serial ports

ROM

RAM

Upon completing the diagnostics, the test results are temporarily listed on the

display.

The LCD is tested by displaying a pattern that illuminates all bits on the display.

Visually verify that all bits are illuminated.

The serial port test consists of two kinds of tests. The first test is an internal

loopback test. The test places the serial ports into the loopback mode. A

character is transmitted to the port, received, and compared. The test passes

when the received character matches the transmitted character.

2–16

TLA QuickStart Technical Reference Manual

Software Features

The second test requires connecting a terminal to Serial Port A (9-pin subminiture D connector). The test pauses until you connect the cable and then push the

Run button to continue. The test string, “Testing serial port A,” is transmitted

through the port. The test passes when when you see the test string is on the

terminal screen.

The test is repeated for Serial Port B using a two by five shrouded square-pin

connector (see Table 4–8 on page 4–11 for pinout information).

ROM Test

RAM Test

The ROM test checks the read-only memory. The ROM is checked by reading a

specific location for a confidence word. If the returned value matches the

confidence word, the ROM is assumed to be good. A Pass/Fail condition is

displayed on the LCD at the completion of the tests.

The RAM is tested by writing a value and then reading the value. If the returned

value matches the written value, the test passes. A Pass/Fail condition is

displayed on the LCD at the completion of the tests.

TLA QuickStart Technical Reference Manual

2–17

Memory Maps

This section provides information on the memory maps for the TLA 7QS

Training board. The first part of this section provides information on the memory

mapped input and output. The rest of this section lists the actual memory maps.

Memory Mapped Input and Output

The training board has 2 Mbytes of memory mapped input and output. The

memory is divided into eight equal segments. Table 2–4 lists the names and

addresses of the memory mapped input and output devices.

T able 2–4: Input and output device addresses

Device Address Input/output type Memory depth and width

LCD display $40 0000 Read/write 1 X 8

LED display $44 0000 Write only 1 X 16

Input control bits $48 0000 Read only 1 X 8

Output control bits $4C 0000 Write only 1 X 16

Setup and hold delay line $50 0000 Write only 1 X 8

Setup and hold memory $54 0000 Read/write 1 X 16

Low counter /pattern generator $58 0000 Write only 1 X 16

High counter/pattern generator $5C 0000 Write only 1 X 16

LCD Display

LED Displays

TLA QuickStart Technical Reference Manual

The liquid crystal display has two eight-bit registers selected by the register

select (RS) bit. When the RS bit is low, it selects the instruction register, when it

is high it selects the data register.

The training board has two 10-segment LED displays. The segments are used as

follows:

The first 16 segments connect directly to the 16-bit data lines and are used

for general purpose applications. Bit 0 is the right-most segment on DS880.

Bit 16 represents the LAPort input enable status. The input circuit uses a

flip-flop to clock in data by an external computer. The enable control bit

connects to the output enable of the flip-flop. When the LED is on (low

signal) the input is enabled and input signals are connected to the training

board.

2–19

Memory Maps

Bit 17 represents the LAPort output enable status. The output circuit uses a

transparent latch. When the LED is on (low signal), the output is enabled and

signal changes on the training board are sent to the output port. When the

LED is off, the output data is latched to last transmitted value (unknown at

power-on). The bit is inverted for proper polarity to the latch.

Bit 18 represents the external trigger input and output interrupt enable status.

When the LED is on, an external input or output trigger causes interrupts

IRQ7 and IRQ6 respectively.

The last bit represents the status of the Halt* signal. When the LED is on,

the Halt* line is asserted.

Input Control Bits

Register

The input control bits register is a general purpose register that monitors signals.

Table 2–5 lists the input control bits and the associated signals. The signals are

intended for diagnostic read-back purposes. See Figure 2–7 on 2–26 page for

memory mapping information.

T able 2–5: Input control bits

Bit Signal name Function

0 LAPORTIN* Control bit readback

1 LAPORTOUT* Control bit readback

2 TRIGGERIN Control bit readback

3 CNTRDIAG Control bit readback from Mux

4 SIGCLK1 Microprocessor timer 1 readback

5 SIGCLK2 Microprocessor timer 1 readback

6 SCL Serial clock (PortA bit 0) readback

7 SDA Serial clock (PortA bit 1) readback

2–20

TLA QuickStart Technical Reference Manual

Memory Maps

Output Control Bits

Register

The output control bits register is a 16-bit input register used to assert signals.

Table 2–6 lists the output control bits and the associated signals. See Figure 2–7

on 2–26 page for memory mapping information.

T able 2–6: Output control bits

Bit Signal name Function

0 LCDRS LCD register select

1 DL YCLKSEL0 Delay generator clock select Mux bit 0

2 DL YCLKSEL1 Delay generator clock select Mux bit 1

3 LAPORTIN* LAPort input enable

4 LAPORTOUT* LAPort output enable

5 TRIGGERIN* External trigger input enable

6 EXTCLKEN External counter clock enable

7 CNTR16BIT* 16-bit or 32-bit counter select

8 PATCLKSEL0 Pattern generator clock selector Mux

bit 0

9 PATCLKSEL1 Pattern generator clock selector Mux

bit 1

Programmable Delay

Setup and Hold Violation

Circuit

Read-Write Setup and

Hold Violation Memory

10 LOCNTREN* Low counter count enable

11 LOCNTRSEL* Low counter or pattern select

12 LOCNTRUP* Low counter count up/down select

13 HICNTREN* High counter count enable

14 HICNTRSEL* High counter or pattern select

15 HICNTRUP* High counter count up/down select

The programmable setup and hold delay line is an eight-bit register with 256

programmable delay settings. The delay line delays the read strobe to the delay

line memory to demonstrate setup and hold timing violations. Each delay count

increment is a 0.5 ns time delay. The minimum delay is 00 and the maximum

is FF.

The delay line memory is a 16-bit read and write register to demonstrate setup

and hold timing violations during read operations. Data can be written and then

read from the same memory location; the data read should equal the written data.

When you program the delay line with a small delay, a setup violation occurs

during the read operation and the data read back will be different than the written

data. When you program the delay line with a large delay, a hold violation occurs

during the read operation and the data will be different than the written data.

TLA QuickStart Technical Reference Manual

2–21

Memory Maps

Low Counter Pattern

Generator Data

High Counter Pattern

Generator Data

Memory Maps

The low counter pattern generator data register is a 16-bit write-only register that

stores a data value in the low counter pattern generator.

The high counter pattern generator data register is a 16-bit write-only register

that stores a data value in the high counter pattern generator.

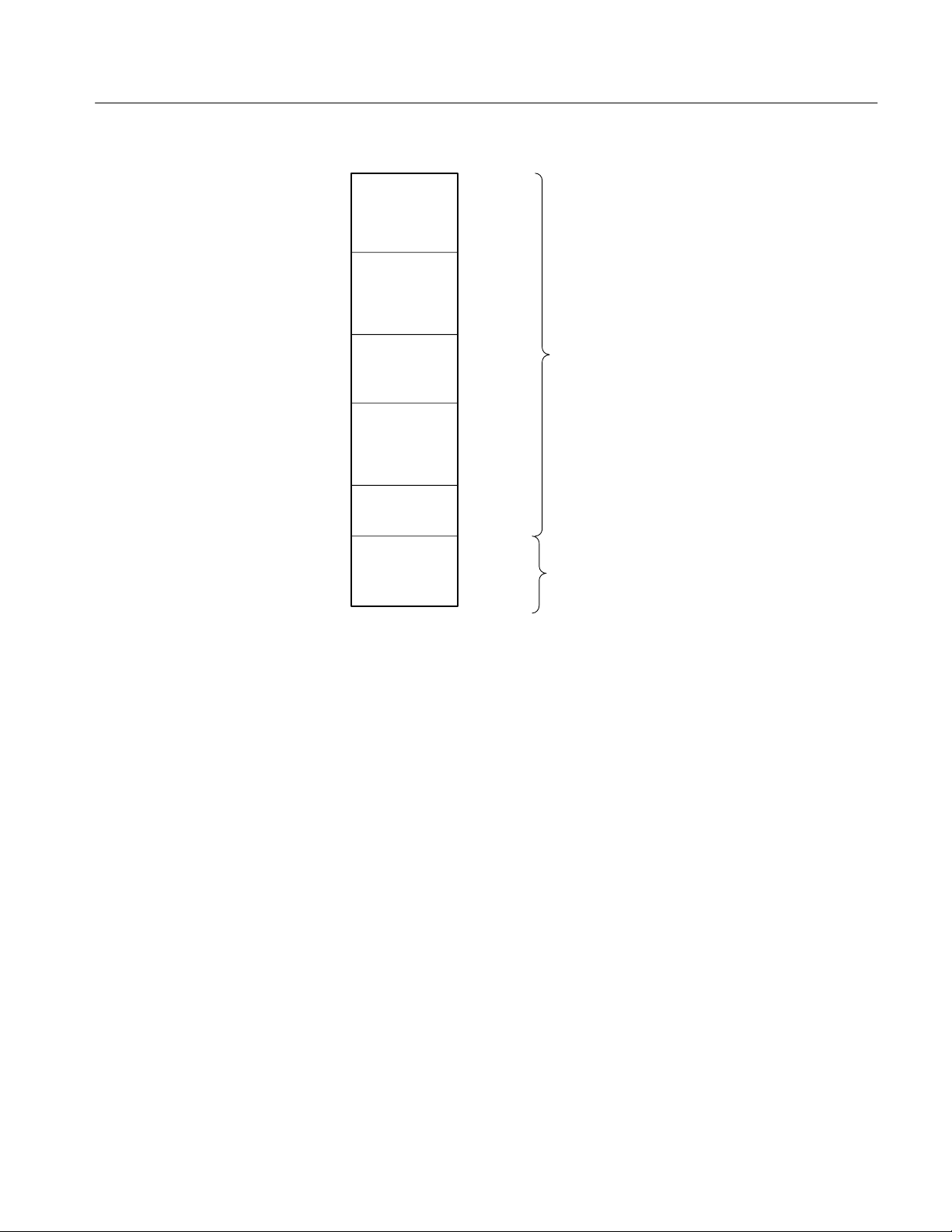

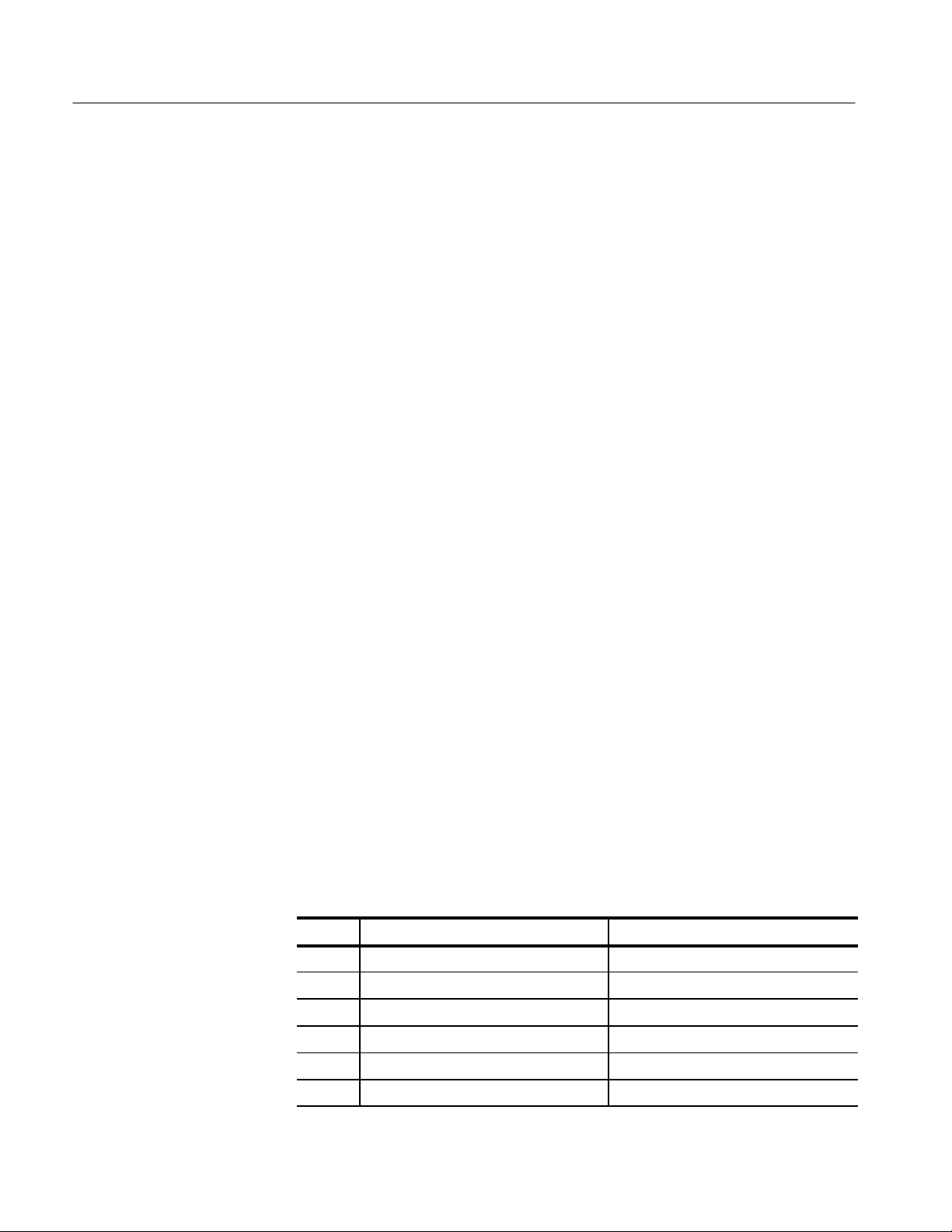

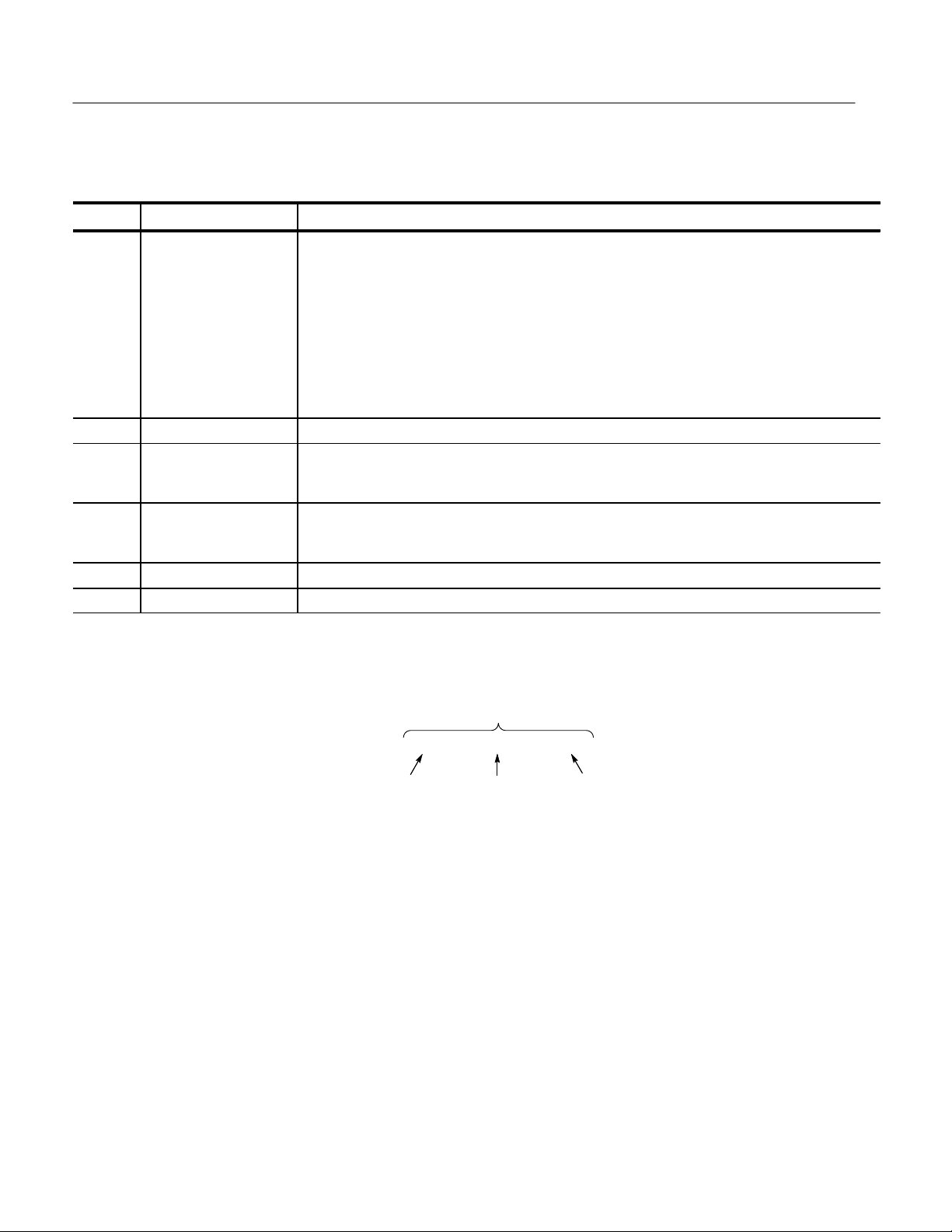

Figures 2–4 through 2–8 show the following memory maps for the TLA 7QS

Training board:

A full memory map

System and user static RAM

User EEPROM and flash

Input and output

System EEPROM and flash

2–22

TLA QuickStart Technical Reference Manual

Memory Maps

CS1

CS2

CS3

CS0

2 MB

User/System

SRAM

Space

2 MB

User

EEPROM/Flash

Space

2 MB

Input/Output

Space

2 MB

System

EEPROM/Flash

Space

8 MB

UNUSED

4 GB

Available on

Extender Bus

00 0000

$20 0000

$40 0000

$60 0000

$80 0000

$FF FFFF

$FFFF FFFF

On Board Memory Space

16 MB Address Space

24 Address Lines (A0—A23)

Extended Memory Space

4 GB Address Space

Available on Extender Bus using the upper

eight Address Lines (A24—A31)

Figure 2–4: Full Memory Map

TLA QuickStart Technical Reference Manual

2–23

Memory Maps

256K

256K

512K

512K

512K

128 K X 16 K

SRAM

128 K X 16 K

SRAM

Unused

Unused

Unused

$00 0000

$04 0000

$08 0000

$10 0000

$18 0000

1K

15K

16K

32K

196K

496K

Exception

Vectors

Monitor

Supervisor

Space

Supervisor

Stack Pointer

Space

User

Stack Pointer

Space

User

Program

Space

User

Program

Space

$00 0000

$00 03FF

$00 3FFF

$00 7FFF

$01 0000

$04 0000

$07 FFFF

$1F FFFF

Figure 2–5: System and user static RAM

2–24

TLA QuickStart Technical Reference Manual

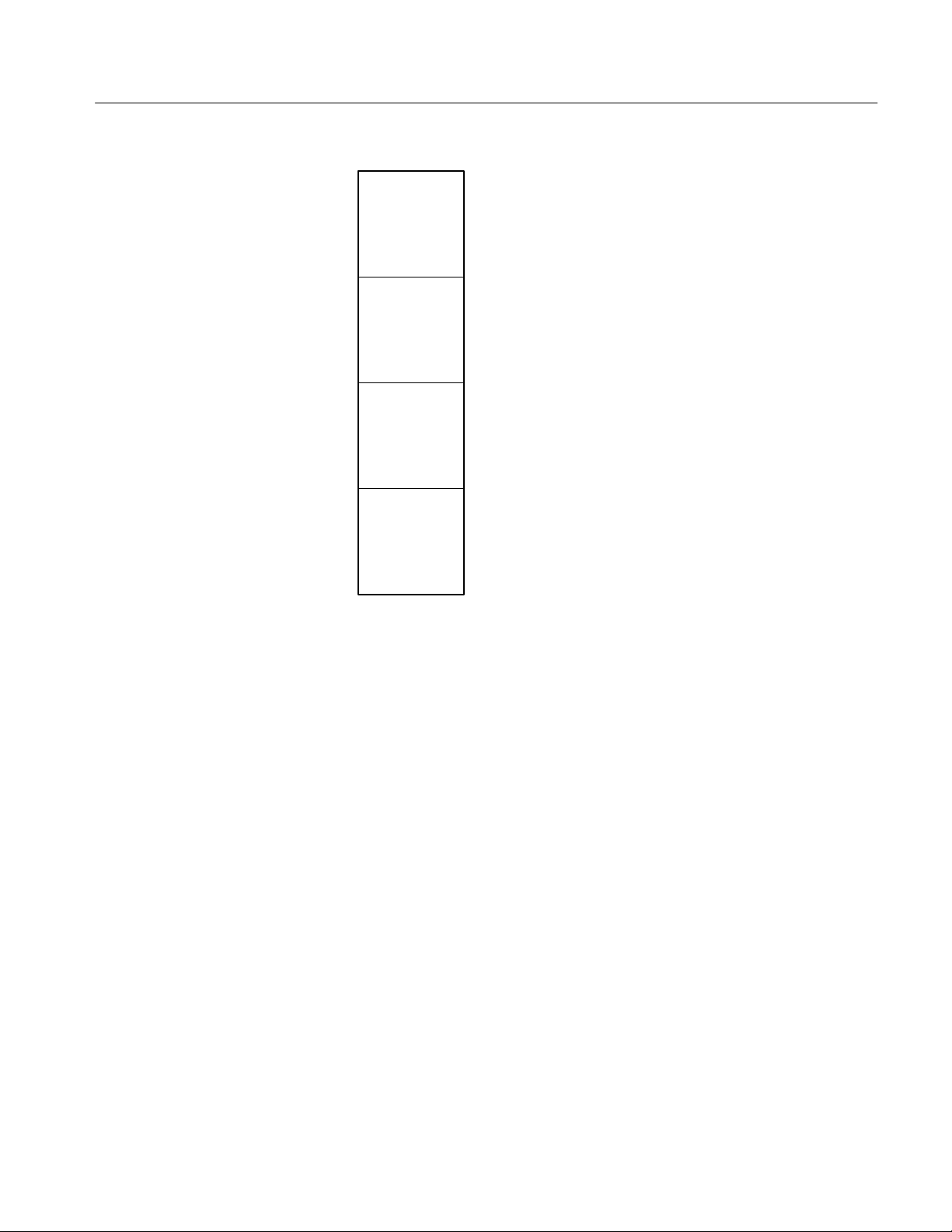

$20 0000

Memory Maps

512K

512K

512K

512K

256K X 16

EEPROM/Flash

$28 0000

Unused

$30 0000

Unused

$38 0000

Unused

$3F FFFF

Figure 2–6: User EEPROM and Flash

TLA QuickStart Technical Reference Manual

2–25

Memory Maps

256K

256K

Input Control Bits

256K

Output Control Bits

256K

Programmable

256K

Delay Line Memory

256K

Pattern Generator

256K

Pattern Generator

256K

LCD Display

Output

Read/Write

LED Display

Output

Write Only

Read Only

Write Only

Delay Line

Write Only

Read/Write

Data

Write Only

Control

Write Only

$40 0000

$44 0000

$48 0000

$4C 0000

$50 0000

$54 0000

$58 0000

$5C 0000

$5F FFFF

Figure 2–7: Input and output

2–26

TLA QuickStart Technical Reference Manual

$60 0000

Memory Maps

512K

512K

512K

512K

256K X 16

EEPROM/Flash

$68 0000

Unused

$70 0000

Unused

$78 0000

Unused

$7F FFFF

Figure 2–8: System EEPROM and Flash

TLA QuickStart Technical Reference Manual

2–27

Creating Programs for the Training Board

This section provides information on creating programs for use with the training

board. Information is provided under the following subsections:

Preparation

Writing the program

Compiling and linking code

Writing an image to the flash memory

Rebooting and running the program

Preparation

To create programs for the training board you will need the SDS CrossCode

C 68K software package from Software Development Systems (the C++ option

is not required) and some software tools from Tektronix. You will use these

packages to write the code and to download the programs to the training board.

Software Development

Systems Tools

Tektronix Software Tools

The SDS CrossCode C/C++ 68K package includes the C compiler, assembler,

linker, and other utilities necessary to convert your source code into 68K code.

Although not required, the SDS SingleStep debugger package may also prove to

be helpful.

The software packages come in several versions which vary mainly in the

connections to the target. The OnChip debugger connects to the background

Debug Mode (BDM) port on the training board through a cable adapter from the

PC printer port. The Target Monitor version connects through a standard serial

COM port to the SDS monitor program which is resident on the training board.

The Target Monitor version is easier to connect, but it is also slower than the

BDM version. The BDM version was used to develop the training board.

In addition to the software packages from Software Development Systems, you

will also need the object file (mongoose.obj) and the linker specification file

(combine.spc). If you intend to reuse some of the code already present on the

training board (such as the code to display strings on the LCD), you will also

need the include files for the training board.

Appendix A: Source Code contains examples of the combine.spc file and a list of

the Tektronix supplied software available with this technical reference manual.

TLA QuickStart Technical Reference Manual

2–29

Creating Programs for the Training Board

Writing the Program

The following procedures provide information on writing the program code for

the training board. You may want to refer to Appendix A: Source Code for a

sample program. The procedures consist of the following steps:

Create the menu entry

Include the user header file

Create a dummy function

Write the code

Create the Menu Entry

Include the User Header

File

The menu for the training board is a linked list structure. The menu structure is

defined in the include file, menu.h. The file is type defined as MENU. You need

to define the following information in the structure:

The menu text to be displayed

The row location of the remote menu text

The column location of the remoter menu text

A pointer to the function to be executed

The following example shows how a sample menu entry with all of the

definitions provided.

MENU myItem = {

My Text", /*text that will be displayed on the menu */

3, /*row location of the remote menu item */

35, /*column location of the remote menu item */

mytestfunction /*pointer to the function to be executed */

};

You must include the user header file, user.h. This file declares a constant that is

located in a specific place in the user memory on the training board. The constant

is checked every time the training board is reset. If the header file finds the

constant, the software will look for menu entries to be added to the menu list.

Create a Dummy Function

2–30

You must include a dummy function to create the proper code and C frame. Do

not include any code in the function, the function must remain empty. The

dummy function is required to allow your code to be appended to the software

on the training board.

TLA QuickStart Technical Reference Manual

Creating Programs for the Training Board

Write the Code

Write your code using normal C or assembly language. You can use any of the

functions for the training board, or create your own functions. Refer to Appen-

dix A: Source Code for a sample program. You may also want to refer to the code

supplied on the floppy disk accompanying this manual.

Compiling and Linking Code

The following procedure shows how to compile and link the code using the

CrossCode 68K application.

Compile the Code

Link the Code

Compile the code using commands and flags as shown below:

Although you may want to use other combinations of compiler flags, not all

combinations have been tested. However, the flags used in the above example

should work for your application.

After compiling the code, you must link the code. To link the code into an object

file, you will need the following items:

An object file (the output file from the compile operation)

The firmware object file (mongoose.obj)

A linker specification file (combine.spc)

The firmware object file is necessary because a successful link requires the

symbol table from the TLA 7QS software that is programmed in the system flash

ROM. For the symbol table to be valid, the firmware object file must be the

same revision as the firmware on the training board.

The linker specification file tells the linker file where to locate some specific

regions, such as your code, data, and constants. For more information about the

linker, regions, and partitions, refer to the SDS documentation on the linker

program.

Refer to Appendix A: Source Code for examples of the C program that will add a

menu item to the main menu on the training board. The program will display the

string “Time to Switch” on the display. The appendix also includes the linker

specification file and a batch file to compile, link, and convert the output to a

Motorola S-record file.

TLA QuickStart Technical Reference Manual

2–31

Creating Programs for the Training Board

Writing an Image to the Flash Memory

Prepare to download the code into flash memory on the training board using a

downloader utility. The downloader utility will extract code bytes and convert

them into a Motorola S-record file. Make sure that you use the proper flags to

avoid ending up with an extremely large file.

Connect the training board to a PC running a terminal program such as HyperTerminal. Open up a session with the baud rate set to 9600 and with hardware

control flow. If you are unsure of the HyperTerminal settings, check the

configuration settings on the Property sheet under the File menu.

Complete the following steps to load the program in the flash memory:

1. Power on the training board and select PGM FLASH.

2. Start the PGM FLASH program and select YES when you are asked to

confirm your actions.

3. Select PGM from the menu to prepare to download the program.

Running the Program

4. When you see the prompt “Start file transfer now,” start the file transfer by

selecting Send Text File from the Transfer menu.

5. Enter the file name of the file created by the downloader program.