Page 1

®

SUPER

X7DA3+

USER’S MANUAL

Revision 1.0a

Page 2

The information in this User’s Manual has been carefully reviewed and is believed to be accurate.

The vendor assumes no responsibility for any inaccuracies that may be contained in this document,

makes no commitment to update or to keep current the information in this manual, or to notify any

person or organization of the updates. Please Note: For the most up-to-date version of this

manual, please see our web site at www.supermicro.com.

Super Micro Computer, Inc. ("Supermicro") reserves the right to make changes to the product

described in this manual at any time and without notice. This product, including software, if any,

and documentation may not, in whole or in part, be copied, photocopied, reproduced, translated or

reduced to any medium or machine without prior written consent.

IN NO EVENT WILL SUPERMICRO BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL,

SPECULATIVE OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO

USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF

SUCH DAMAGES. IN PARTICULAR, SUPERMICRO SHALL NOT HAVE LIABILITY FOR ANY

HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE

COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH

HARDWARE, SOFTWARE, OR DATA.

Any disputes arising between manufacturer and customer shall be governed by the laws of Santa

Clara County in the State of California, USA. The State of California, County of Santa Clara shall

be the exclusive venue for the resolution of any such disputes. Supermicro's total liability for all

claims will not exceed the price paid for the hardware product.

FCC Statement: This equipment has been tested and found to comply with the limits for a Class B

digital device pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable

protection against harmful interference in a residential installation. This equipment generates,

uses, and can radiate radio frequency energy and, if not installed and used in accordance with the

manufacturer’s instruction manual, may cause interference with radio communications. However,

there is no guarantee that interference will not occur in a particular installation. If this equipment

does cause harmful interference to radio or television reception, which can be determined by turning

the equipment off and on, you are encouraged to try to correct the interference by one or more

of the following measures: Reorient or relocate the receiving antenna. Increase the separation

between the equipment and the receiver. Connect the equipment into an outlet on a circuit different

from that to which the receiver is connected. Consult the dealer or an experienced radio/television

technician for help.

California Best Management Practices Regulations for Perchlorate Materials: This Perchlorate

warning applies only to products containing CR (Manganese Dioxide) Lithium coin cells. “Perchlorate

Material-special handling may apply. See www.dtsc.ca.gov/hazardouswaste/perchlorate”

WARNING: Handling of lead solder materials used

in this product may expose you to lead, a chemical

known to the State of California to cause birth defects

and other reproductive harm.

Manual Revision: Rev. 1.0a

Release Date: April 4, 2008

Unless you request and receive written permission from Super Micro Computer, Inc., you may not

copy any part of this document.

Information in this document is subject to change without notice. Other products and companies

referred to herein are trademarks or registered trademarks of their respective companies or mark

holders.

Copyright © 2008 by Super Micro Computer, Inc.

All rights reserved.

Printed in the United States of America

Page 3

Preface

About This Manual

This manual is written for system integrators, PC technicians and knowledge-

able PC users. It provides information for the installation and use of the

X7DA3+ motherboard. The

Dual-Core processors with a front side bus speed of 1.333 GHz/1.066 GHz/667

MHz. With two 64-bit Quad-Core and Dual-Core processors built-in, the X7DA3+

offers substantial functionality enhancements to the motherboards based on the

Intel Quad-Core/Dual-Core architecture while remaining compatible with the IA-32

software. The features include the Intel Virtualization Technology, Hyper Pipelined

Technology, Execution Trace Cache, Thermal Monitor 1/2 (TM1/TM2), Enhanced

Intel SpeedStep technology, Advanced Dynamic Execution, Advanced Transfer

Cache, Streaming SIMD Extensions 3 (SSE3) and Extended Memory 64 Technol-

ogy (EM64T). These features allow the motherboard to operate at much higher

speeds with better power management in much safer thermal environments than the

traditional motherboards. The X7DA3+ is ideal for high performance quad processor

or dual processor workstation and enterprise server environments. Refer to our web

site (http://www.supermicro.com/products/) for updates on supported processors.

This product is intended to be professionally installed.

X7DA3+ supports dual Intel Quad-Core and

Preface

Manual Organization

Chapter 1 describes the features, specifi cations and performance of the mother-

board and provides detailed information about the chipset.

Chapter 2 provides hardware installation instructions. Read this chapter when

installing the processor, memory modules and other hardware components into

the system. If you encounter any problems, see Chapter 3, which describes

troubleshooting procedures for the video, the memory and the system setup stored

in CMOS.

Chapter 4 includes an introduction to BIOS and provides detailed information on

running the CMOS Setup utility.

Appendix A and Appendix B provide BIOS POST Messages and POST Codes.

Appendix C, Appendix D and Appendix E list HostRAID, Windows OS and Other

Software Program Installation Instructions.

Conventions Used in the Manual

Special attention should be given to the following symbols for proper installation and

to prevent damage done to the components or injury to yourself:

Danger/Caution: Instructions to be strictly followed to prevent

catastrophic system failure or to avoid bodily injury.

Warning: Important information given to ensure proper system installation

or to prevent damage to the components.

Note: Additional Information given to differentiate various models or to ensure cor-

rect system setup.

iii

Page 4

X7DA3+ User's Manual

Table of Contents

Preface

About This Manual ...................................................................................................... iii

Manual Organization ................................................................................................... iii

Conventions Used in the Manual .................................................................................. iii

Chapter 1: Introduction

1-1 Overview ......................................................................................................... 1-1

Checklist ................................................................................................... 1-1

Contacting Supermicro ............................................................................. 1-2

X7DA3+ Image ........................................................................... 1-3

X7DA3+ Layout .......................................................................... 1-4

Quick Reference ...................................................................................... 1-5

Motherboard Features ................................................................................ 1-6

Intel 5000X (Greencreek) Chipset: System Block Diagram .................... 1-8

1-2 Chipset Overview ........................................................................................... 1-9

1--3 Special Features ........................................................................................... 1-10

1-4 PC Health Monitoring .................................................................................... 1-10

1-5 ACPI Features .............................................................................................. 1-11

1-6 Power Supply ............................................................................................... 1-12

1-7 Super I/O ........................................................................................................ 1-12

Chapter 2: Installation

2-1 Static-Sensitive Devices ................................................................................. 2-1

Precautions ................................................................................................ 2-1

Unpacking ................................................................................................ 2-1

2-2 Motherboard Installation ................................................................................. 2-1

2-3 Processor and Heatsink Installation ............................................................... 2-2

2-4 Installing DIMMs ............................................................................................. 2-6

2-5 Control Panel Connectors and IO Ports ......................................................... 2-8

A. Back Panel Connectors/IO Ports .............................................................. 2-8

B. Front Control Panel ................................................................................... 2-9

C. Front Control Panel Pin Defi nitions ........................................................ 2-10

NMI Button ............................................................................................. 2-10

Power LED ............................................................................................. 2-10

HDD LED .............................................................................................. 2-11

NIC1/NIC2 LED Indicators ..................................................................... 2-11

Overheat/Fan Fail LED ......................................................................... 2-12

Power Fail LED ........................................................................................ 2-12

iv

Page 5

Table of Contents

Reset Button ......................................................................................... 2-13

Power Button .......................................................................................... 2-13

2-6 Connectors and Headers ............................................................................... 2-14

ATX Power Connector .......................................................................... 2-14

Processor Power Connector ................................................................. 2-14

Universal Serial Bus (USB) ..................................................................... 2-15

Chassis Intrusion .................................................................................... 2-15

Fan Headers .......................................................................................... 2-16

ATX PS/2 Keyboard and Mouse Ports ..................................................... 2-17

Serial Port .............................................................................................. 2-17

Wake-On-Ring .......................................................................................... 2-18

Wake-On-LAN .......................................................................................... 2-18

GLAN 1/2 (Ethernet) Ports ....................................................................... 2-19

Speaker/Power LED Header .................................................................. 2-19

Power Fault .............................................................................................. 2-20

Overheat/Fan Fail LED ............................................................................ 2-20

SMB Connector ........................................................................................ 2-21

Power SMB Connector ............................................................................. 2-21

Compact Flash Card PWR Connector ..................................................... 2-22

SGPIO Headers ....................................................................................... 2-22

High Defi nition Audio ................................................................................ 2-23

CD Connector ........................................................................................... 2-23

2-7 Jumper Settings ............................................................................................ 2-24

Explanation of Jumpers ......................................................................... 2-24

GLAN Enable/Disable ............................................................................ 2-24

CMOS Clear ............................................................................................ 2-25

Watch Dog ................................................................................................ 2-25

3rd PWR Supply PWR Fault .................................................................... 2-26

SAS Controller Enable ............................................................................. 2-26

Compact Flash Master/Slave Enable/Disable .......................................... 2-27

Alarm Reset .............................................................................................. 2-27

SMB to PCI-X/PCI-E Slots ....................................................................... 2-28

2-8 Onboard Indicators ....................................................................................... 2-29

GLAN LEDs .............................................................................................. 2-29

Onboard Power LED ................................................................................ 2-29

Onboard SAS Activity LED Indicators ...................................................... 2-30

2-9 Parallel Port, Floppy, SIMLP IPMI, Hard Disk Drive and SAS Connections 2-31

Parallel Port Connector ........................................................................... 2-31

Floppy Connector .................................................................................... 2-32

v

Page 6

X7DA3+ User's Manual

SIMLP IPMI Slot ...................................................................................... 2-32

IDE Connectors ........................................................................................ 2-33

SAS Connectors ....................................................................................... 2-34

Chapter 3: Troubleshooting

3-1 Troubleshooting Procedures ........................................................................... 3-1

Before Power On ....................................................................................... 3-1

No Power ................................................................................................... 3-1

No Video .................................................................................................. 3-1

Losing the System’s Setup Confi guration ................................................ 3-2

Memory Errors ........................................................................................... 3-2

3-2 Technical Support Procedures ....................................................................... 3-2

3-3 Frequently Asked Questions .......................................................................... 3-3

3-4 Returning Merchandise for Service ................................................................. 3-4

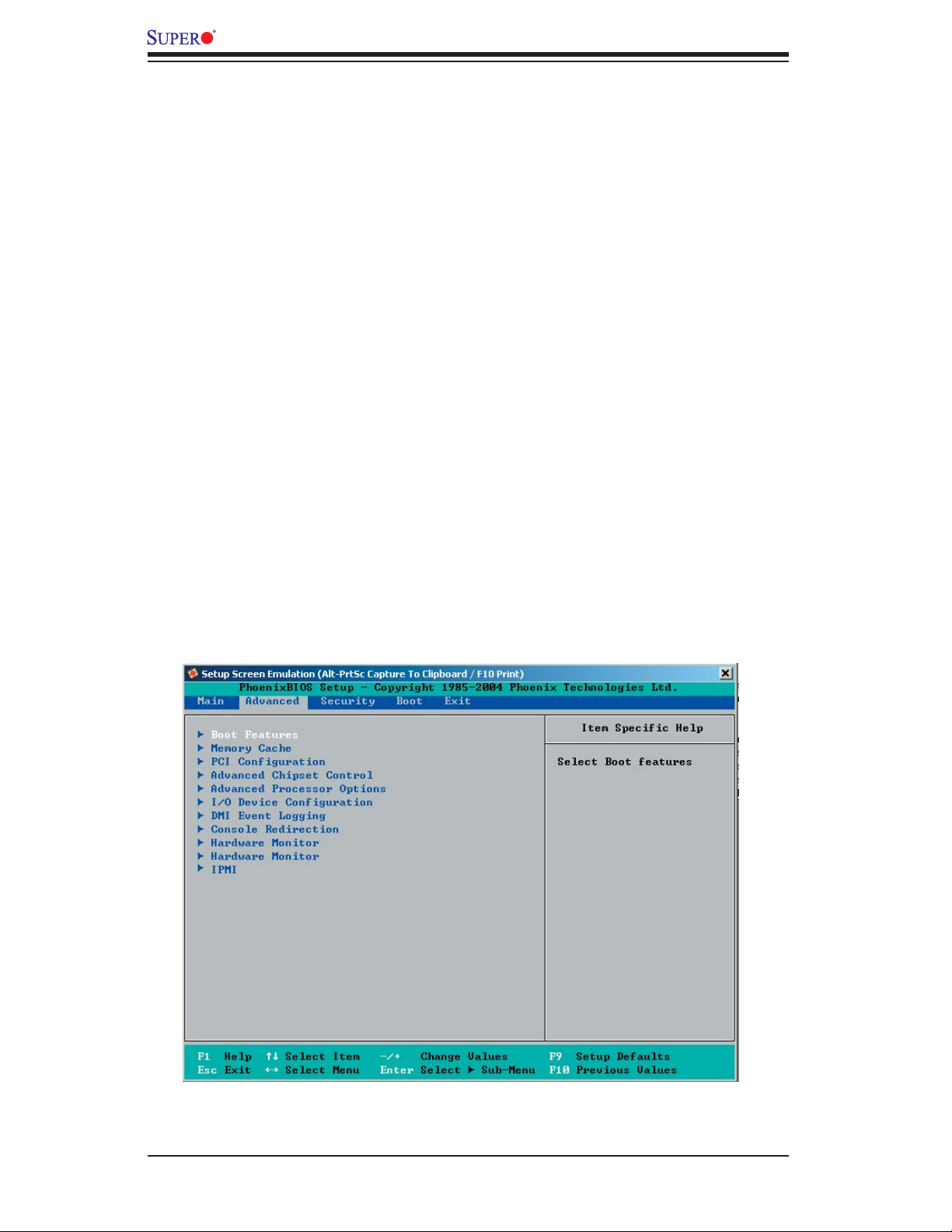

Chapter 4: BIOS

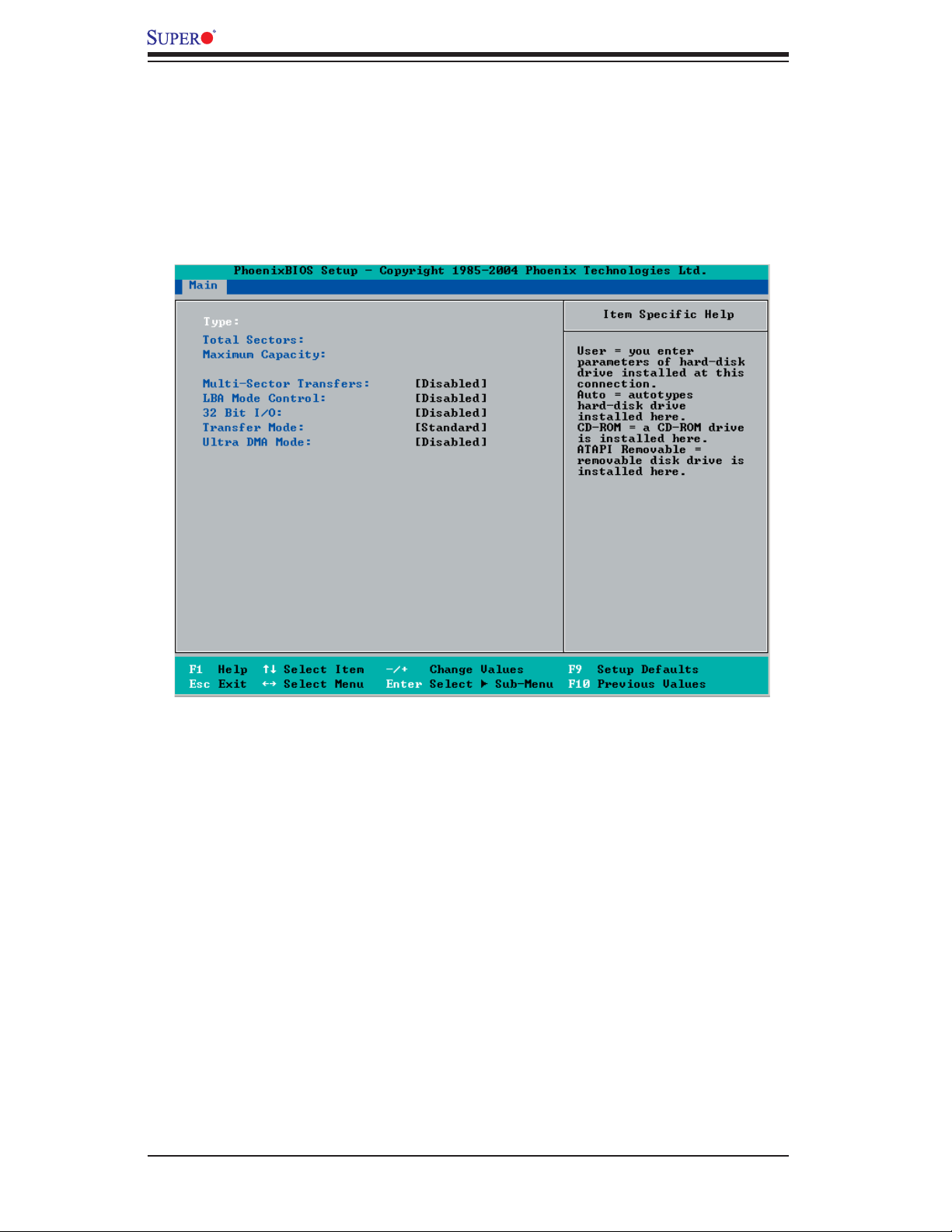

4-1 Introduction ....................................................................................................... 4-1

4-2 Running Setup ................................................................................................. 4-2

4-3 Main BIOS Setup ............................................................................................. 4-2

4-4 Advanced Setup ............................................................................................... 4-6

4-5 Security Setup ............................................................................................... 4-23

4-6 Boot Setup ...................................................................................................... 4-24

4-7 Exit .................................................................................................................. 4-25

Appendices:

Appendix A: BIOS POST Messages .......................................................................... A-1

Appendix B: BIOS POST Codes ................................................................................B-1

Appendix C: Installing the Adaptec HostRAID Utility and the Windows OS ............C-1

Appendix D: Intel HostRAID and the Windows OS Setup Guidelines ......................D-1

Appendix E: Installing Other Software Programs and Drivers .................................. E-1

vi

Page 7

Chapter 1: Introduction

Chapter 1

Introduction

1-1 Overview

Checklist

Congratulations on purchasing your computer motherboard from an acknowledged

leader in the industry. Supermicro boards are designed with the utmost attention to

detail to provide you with the highest standards in quality and performance. Check

that the following items have all been included with your motherboard. If anything

listed here is damaged or missing, contact your retailer.

All the items are included in the retail box.

One (1) Supermicro Mainboard

One (1) ribbon cable for IDE devices (CBL-0036L-02)

One (1) fl oppy ribbon cable (CBL-0022L)

Four (4) SATA cables (CBL-0044L)

Two (2) I-Pass-to-4 SATA Straight Through Cables (CBL-0097L-02)

One (1) I/O backpanel shield (MCP-260-74301-0N)

One (1) Supermicro CD containing drivers and utilities

One (1) User's/BIOS Manual

1-1

Page 8

X7DA3+ User's Manual

Contacting Supermicro

Headquarters

Address: Super Micro Computer, Inc.

980 Rock Ave.

San Jose, CA 95131 U.S.A.

Tel: +1 (408) 503-8000

Fax: +1 (408) 503-8008

Email: marketing@supermicro.com (General Information)

support@supermicro.com (Technical Support)

Web Site: www.supermicro.com

Europe

Address: Super Micro Computer B.V.

Het Sterrenbeeld 28, 5215 ML

's-Hertogenbosch, The Netherlands

Tel: +31 (0) 73-6400390

Fax: +31 (0) 73-6416525

Email: sales@supermicro.nl (General Information)

support@supermicro.nl (Technical Support)

rma@supermicro.nl (Customer Support)

Asia-Pacifi c

Address: Super Micro Computer, Inc.

4F, No. 232-1, Liancheng Rd.

Chung-Ho 235, Taipei County

Taiwan, R.O.C.

Tel: +886-(2) 8226-3990

Fax: +886-(2) 8226-3991

Web Site: www.supermicro.com.tw

Technical Support:

Email: support@supermicro.com.tw

Tel: 886-2-8228-1366, ext.132 or 139

1-2

Page 9

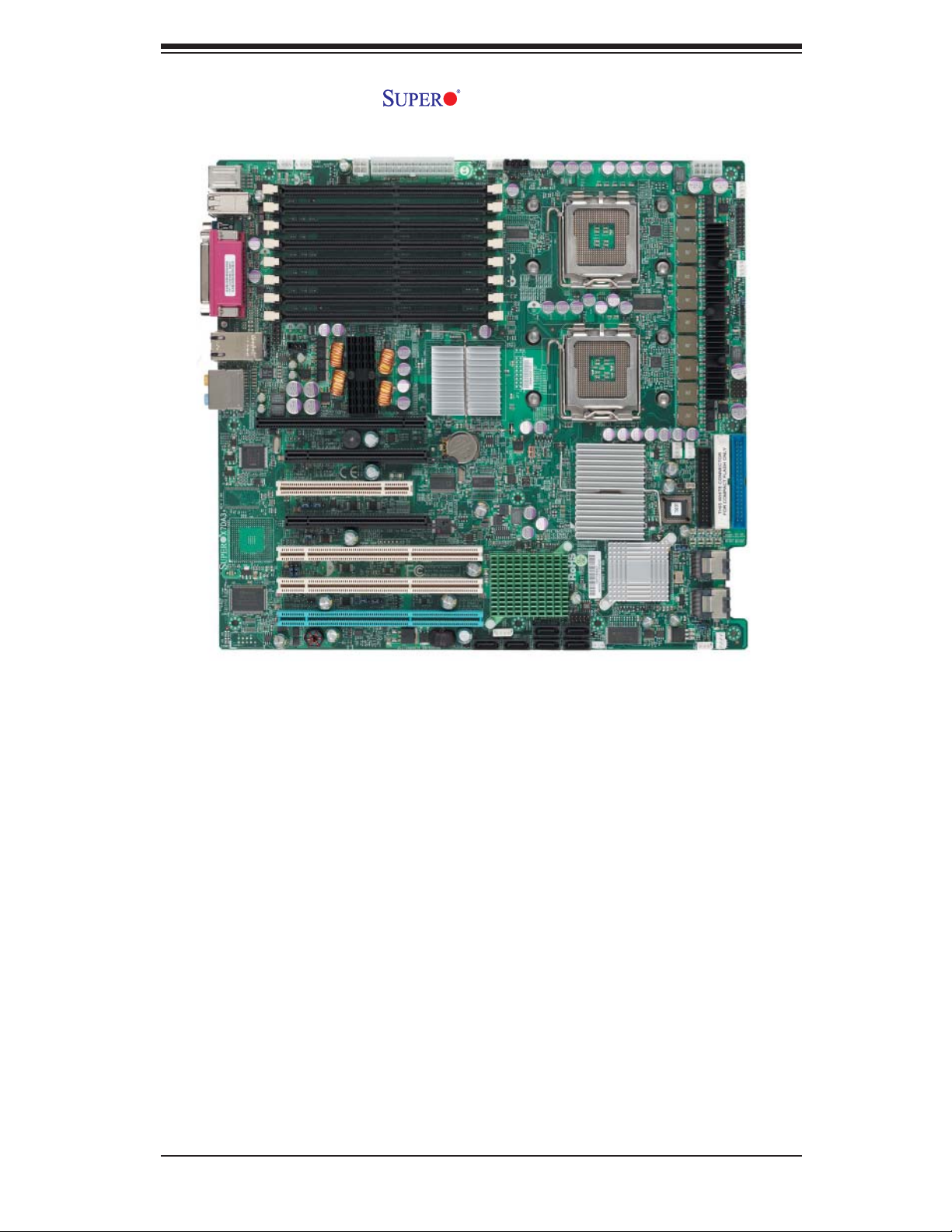

X7DA3+ Image

Chapter 1: Introduction

Note: The drawings and pictures shown in this manual were based on the latest

PCB Revision available at the time of publishing of the manual. The motherboard

you’ve received may or may not look exactly the same as the graphics shown in

the manual.

1-3

Page 10

X7DA3+ User's Manual

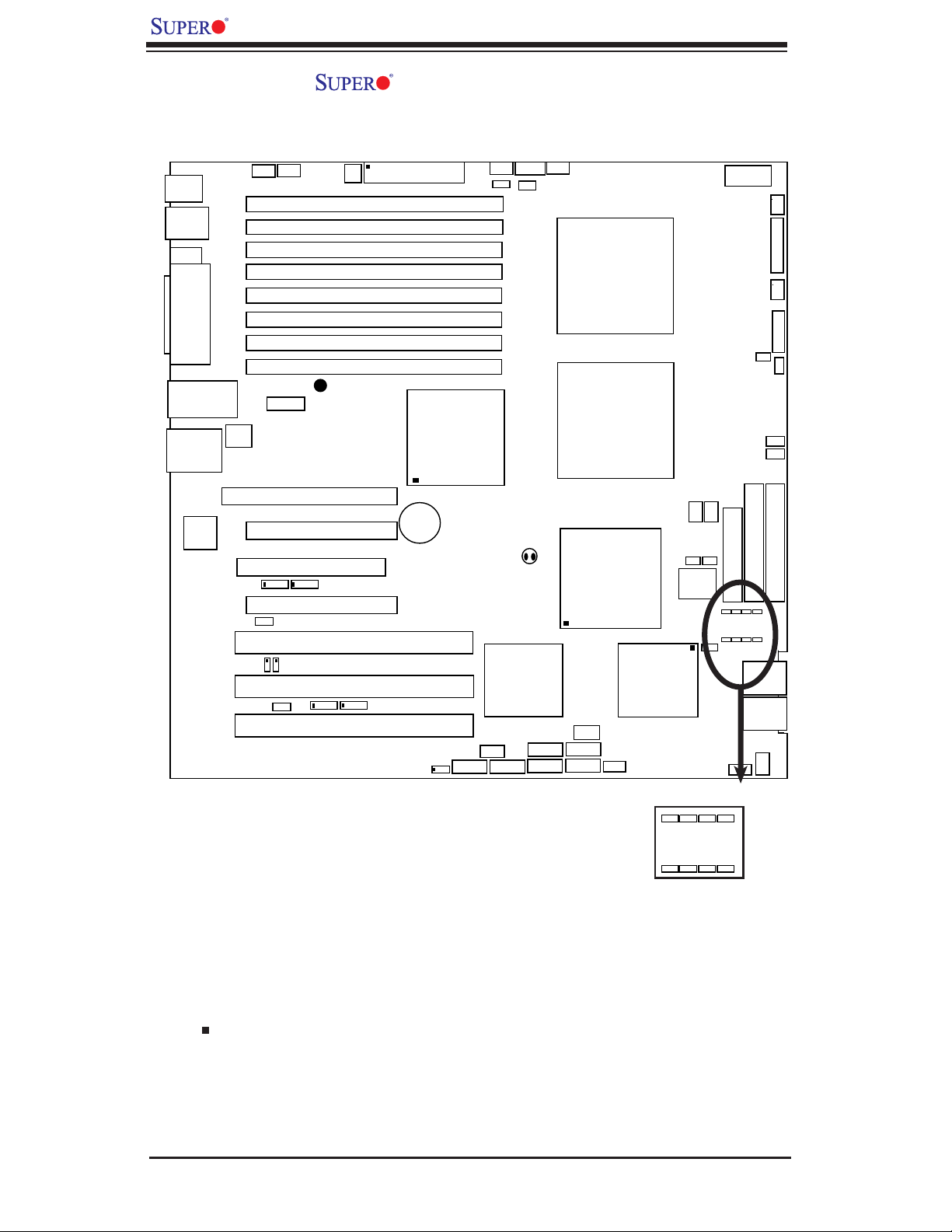

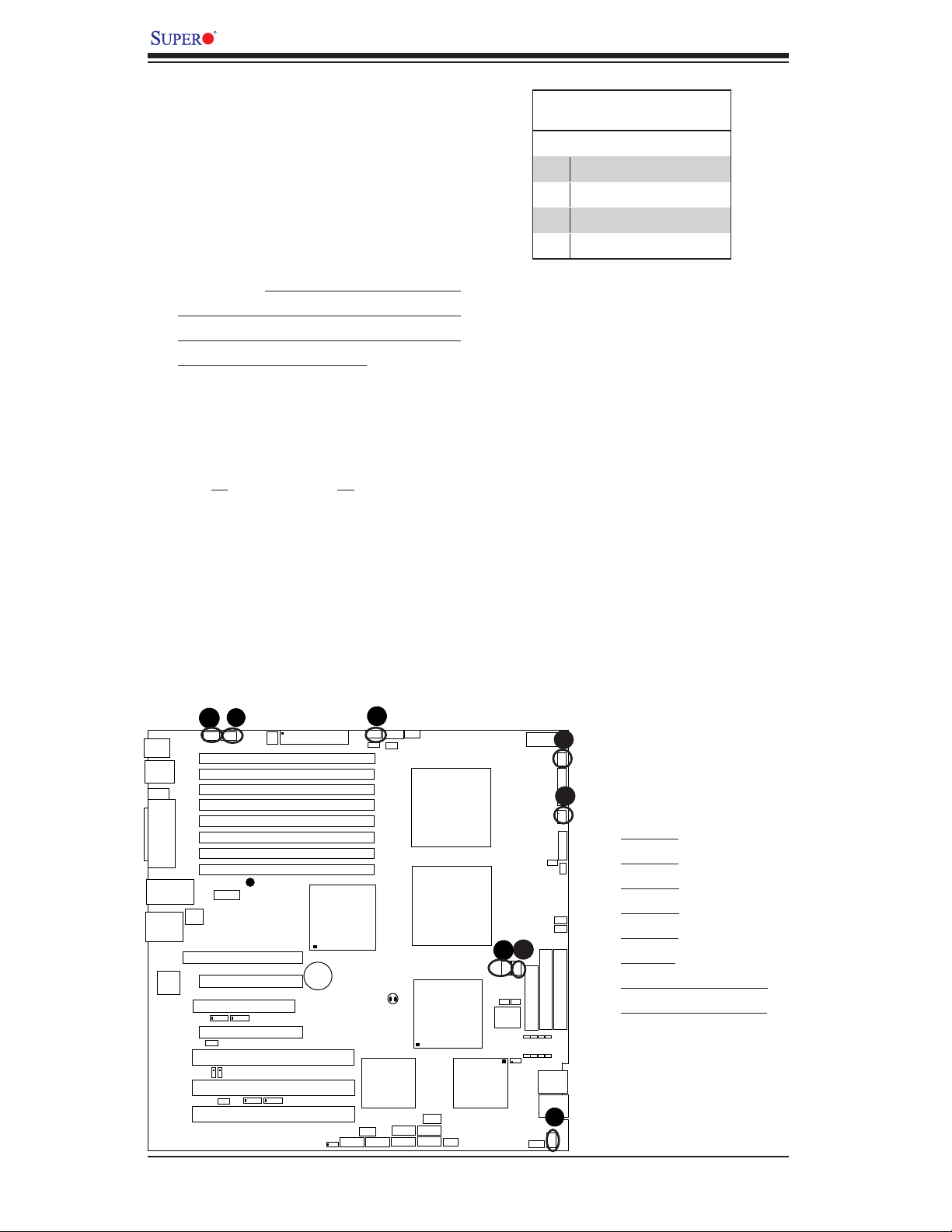

X7DA3+ Motherboard Layout

(not drawn to scale)

KB/

Mouse

JKM1

US

1/2/3

JUSB1

OM1

C

LAN1/2

HD

Audio

/

0

B

J

Parrallel

Port

JLAN1

J21

JC1

GLAN

R

CTL

COM1

JLA

Slot

Fan6

J9B2

1

J9B

J8B3

2

J8B

J8B1

B3

J7

7B2

J

J7B1

UPER X7DA3+

S

N

1

Audio

CTRL

7

SIM LP IPMI

6

Slot

PCI-Exp x16

Slot5

PCI-33MHz

2

C

JI

lot4

S

P

JWD

Slot3

PCI-X 133

JPL1

2

Slot

PCI-X 133

WOR

J

1

Slot

PCI

PWR

DIMM 4B (Bank 4)

DIMM 4A (Bank 4)

D

DIMM 3A (Bank 3)

D

DIMM 2A (Bank 2)

DIMM 1B

DIMM 1A (Bank 1)

CD1

2

C4

JI

3

4

x

p

CI-Ex

MHz

2

JPL

MHz

2

JI

00 MH

-X 1

4-Pin

Fan5

24-Pin

JPW2

IMM 3B (Bank

IMM 2B (Bank

(Ban

®

2

C2

I

J

C1

reen

ZCR (G

z

ATX PWR

3

2

k 1)

Battery

Slot)

JPW1

)

)

reencree

G

North Bridge

JL

1

SATA0

CPU

Fan 1

JS

k

SMB

1

Fan7

J3P

JBT1

PX

SATA1

JS2

J17

JAR

H

USB4/5

SATA4

JS5

SATA2

J

PSF

S

8-pin PWR

JPW3

1

Fan

JF1

Floppy

T

4-7

0-3

SAS4-7

SAS0-3

SPK

PW LED

LE1

SGPIO1

J29

J30

SGPIO2

Compact Flash

JIDE2

JSM2

JSM1

Fan4

FP Control

Fan2

JD1

JOH1

DE1

I

IDE1

J

CPU1

CPU2

CPU

Fan2

Fan3

Fan8

F1

JW

JCF1

South

Bridge

SAS

Controller

JUSB2

A5

T

SA

JS6

A3

T

SA

WOL

J

JS4

3

IOS

B

22

J

AC

ACT

JPS1

S10

J

SAS ACT4-7 LEDs

SAS ACT0-3 LEDs

Notes:

1. Jumpers not indicated are for test purposes only.

2. See Chapter 2 for detailed information on jumpers, I/O ports and JF1 front panel

connections.

3. " " indicates the location of Pin 1.

4. Please install the ZCR card on the green slot for it to work properly.

5. The drawings and pictures shown in this manual were based on the latest

PCB Revision available at the time of publishing of the manual. The motherboard

you’ve received may or may not look exactly the same as the graphics shown in

the manual.

1-4

Page 11

Chapter 1: Introduction

Quick Reference (X7DA3+)

Jumper Description Default Setting

J3P 3rd PWR Failure Detect

JAR Alarm Reset Off (Disabled)

JBT1 CMOS Clear See Chapter 2

JCF1 Compact Card Master/Slave Select On (Master)

JI2C1/JI2C2 SMB to PCI-X Slots Pins 2-3 (Disabled)

JI2C3/JI2C4 SMB to PCI-E Slots Pins 2-3 (Disabled)

JPS1 SAS Controller Enable Pins 1-2 (Enabled)

JPL1/ JPL2 GLAN1/GLAN2 Enable Pins 1-2 (Enabled)

JWD Watch Dog Pins 1-2 (Reset)

Connector Description

ATX PWR (JPW1) Primary 24-Pin ATX PWR Connector

Aux. PWR/CPU PWR +12V 4-pin PWR (JWP2)/+12V 8-pin PWR(JPW3)

HD Audio (JC1) High Defi nition Audio Connector (JC1)

Chassis Intrusion (JL1) Chassis Intrusion Header

COM1 (JCOM1) COM1 Serial Port Connector

Compact PWR (JWF1) Compact Card PWR Connector

DIMM#1A-DIMM#4B Memory DDRII Fully Buffered DIMM Slots

FAN 1-8 Fans 1-8 (Fan7: CPU Fan1, Fan8: CPU Fan2)

Floppy (J22) Floppy Disk Drive Connector

FP Control (JF1) Front Control Panel Connector

GLAN 1/2 (JLAN1) G-bit Ethernet Ports

IDE1/IDE2(Note 1 Below)IDE1 Hard Drive (JIDE1)/Compact Flash Card (JIDE2)

LE1 LED (Note 2 Below) 5V Standby PWR LED Indicator

OH LED (JOH1) Overheat LED

Parallel (J21) Parallel (Printer) Port

PWR LED/SPKR (JD1) PWR LED(pins1-3)/SpeakerHeader (pins 4-7)

PWR SMB (J17) Power System Management (I

PSF Power Supply Failure (See Chapter 2)

SAS#0-#3,#4-#7(JSM1/2) SAS (Serial Attached SCSI) Connectors #0-#3, #4-#7

SATA#0-#5(JS1-JS6) Serial ATA Connectors #0-5

SGPIO 1/2(J29,J30) Serial General Purpose Input/Output Headers

SMB (J18) System Management Bus Header

Slot 7 SIM Low Profi le IPMI Connector

USB 0/1/2/3 (JUSB1) Back Panel USB 0/1/2/3(JUSB1)

USB 4/5 (JUSB2) Front Panel USB4/5 (JUSB2)

WOL (JWOL) Wake-on-LAN Header

WOR (JWOR) Wake-on-Ring Header

Notes: 1.JIDE2 is for Compact Card Use only. JCF1 is used to confi gure the com-

pact fl ash card as a master or a slave drive. Be sure to connect JWF1 to a power

supply to provide power to the compact fl ash card. 2. When LE1 is on, the Standby

Power is on. Unplug the PWR cables before changing components.

Off (Disabled)

2

C) Header

1-5

Page 12

X7DA3+ User's Manual

Motherboard Features

CPU

• Dual Intel

®

64-bit LGA 771 Quad-Core/Dual-Core Xeon 5300/5100/5000 Series

processors at a front side bus speed of 1.333 GHz/1.066 GHz/667 MHz

Memory

• Eight 240-pin DIMM sockets with support up to 32 GB ECC DDR2 FBD 667/533

Memory (See Section 2-3 in Chapter 2 for DIMM Slot Population.)

Chipset

• Intel 5000X (Greencreek) chipset, including: the 5000X (Greencreek) Memory

Control Hub (MCH), the Enterprise South Bridge 2 (ESB2), and the I/O subsys-

tem (PXH-V).

Expansion Slots

Two PCI-E slots (one x16 signal on x16 slot, one x4 signal on x16 slot)

Three 64-bit PCI-X slots (two: PCI-X-133 slots, one PCI-X-100 ZCR Slot)

One PCI-33 MHz slot

One Low Profi le IPMI slot

BIOS

• 8 Mb Phoenix

®

Flash ROM

• DMI 2.1, PCI 2.2, ACPI 1.0, Plug and Play (PnP), SMBIOS 2.3, PCI-X 1.0

PC Health Monitoring

• Onboard voltage monitors for CPU cores, chipset voltage, 1.8V, 3.3V, +5V,

+12V, −12V, 3.3V standby and 5V standby

• Fan status monitor with fi rmware speed control

• CPU/chassis temperature monitors

• Platform Environment Control Interface (PECI)

• CPU slow-down on temperature overheat

• CPU thermal trip support for processor protection

• Power-up mode control for recovery from AC power loss

• Auto-switching voltage regulator for CPU core

• System overheat LED and control

• Chassis intrusion detection

• System resource alert

ACPI Features

• Slow blinking LED for suspend state indicator

• Main switch override mechanism

1-6

Page 13

Chapter 1: Introduction

Onboard I/O

• Adaptec AIC-9410W SAS Controller w/HostRAID support (RAID 0, 1,10)

• Intel ESB-2 South Bridge supports 6 SATA connectors (w/RAID 0, 1, 5,10) (For

the Windows OS only)

• One SIM Low Profi le IPMI slot

• Intel 82563EB Gigabit Dual-Port Ethernet controller

• 1 EIDE Ultra DMA/100 bus master interfaces w/2 devices supported

• 1 fl oppy port interface

• 1 serial port

• 1 EPP/ECP Parallel Port

• 7.1+2 Channel High Defi nition Audio Connection

• Super I/O: Winbond W83627HG w/Hardware Monitor support: W83793G

• PS/2 mouse and PS/2 keyboard ports

• Up to 6 USB 2.0 (Universal Serial Bus) (4 ports, 2 Headers)

• Super I/O

Other

• External modem ring-on

• Wake-on-LAN (WOL)

• Wake-on-Ring (WOR)

• Console redirection

• Onboard Fan Speed Control by Thermal Management via BIOS

CD/Diskette Utilities

• BIOS fl ash upgrade utility and device drivers

Dimensions

• Ext. ATX 12.08" x 13.05" (306.8 mmx 331.5 mm)

1-7

Page 14

X7DA3+ User's Manual

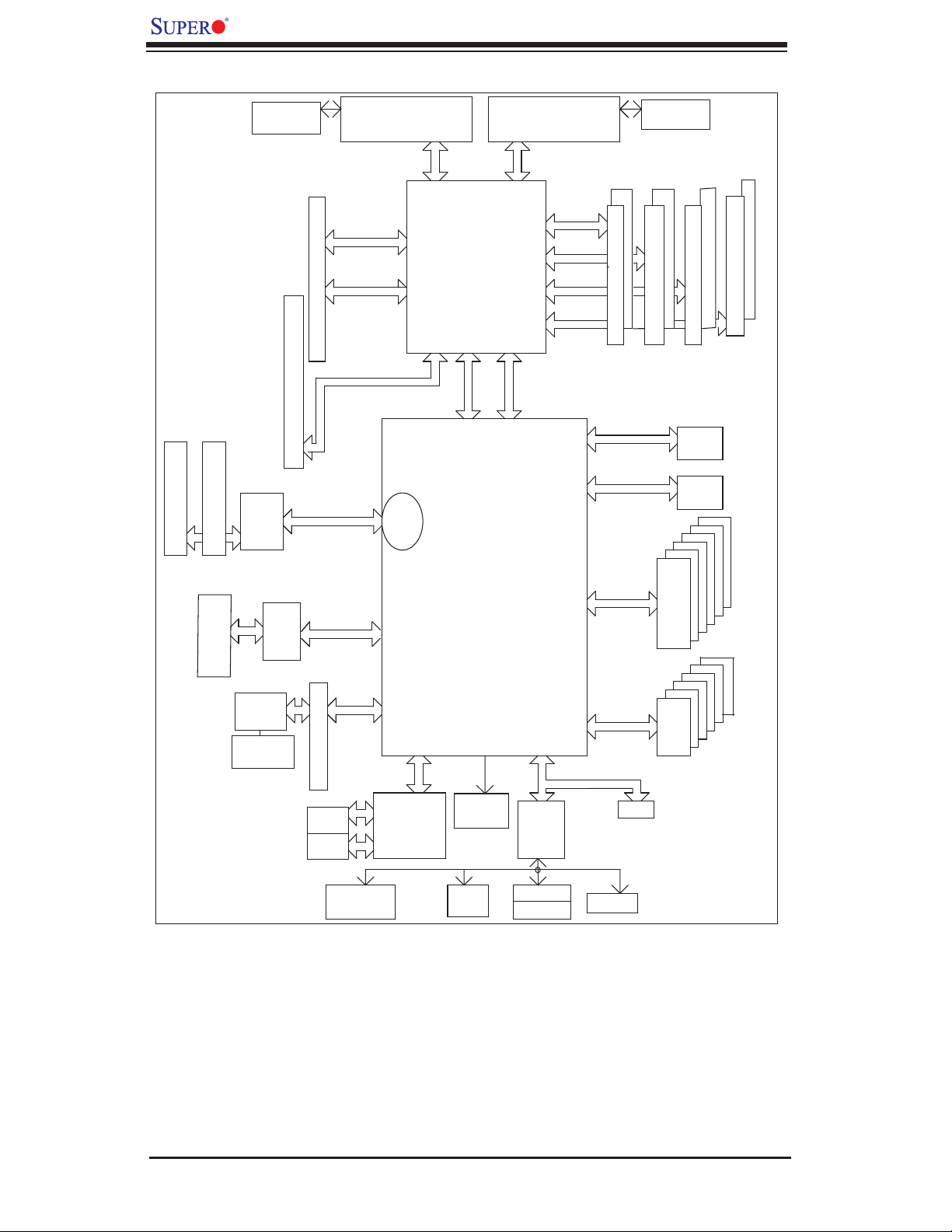

J13

#2

PCI-X SLOT

J14

#3

J12

#1

PCI-X SLOT

PXH-V

VRM

J5

#6

J9

#4

PCI-EXP_X4_in_X16_SLOT

PCI-EXP X8

SAS

PCI-X 133

9410

PROCESSOR#2

PCI-EXP X8

PCI-EXP X8

PCI-EX_X16_SLOT

PCI-EXP X4

667/1067/

1333 MHz

Port

#1,2

Port

#4,5

Port

#6,7

Port

1B

FBD DIMM

EXP.

BUS

VRM

2B

2A 3A

FBD DIMM

IDE

CONN

EBUS

CONN

#3

#2

#1

#0

#4

3B

FBD DIMM

#5

4B

4A

FBD DIMM

PROCESSOR#1

667/1067/

1333 MHz

FBD

CHNL0

MCH

5000X

Port

Port

#0

#3

#2

PCIE X4

Port

Port

#4

#3

FBD

CHNL1

FBD

CHNL2

FBD

CHNL3

PCIE X4

1A

ATA100

ESB2

3.0 Gb/S

SATA

PCI-X SLOT

zcr

FRONT

PANEL

SIMLP-IPMI

CONN

J6

PCI 32/

33MMZ

#5

PCI32_SLOT

RJ45

RJ45

PARALLEL

PORT

GB LAN

GILGAL

HD Audio

FDD

SIO

W83627

EHF

MS

KB

USB 2.0

LPC

FWH

COM1

#5

#4

#3

#2

#1

#0

USB

Block Diagram of the 5000X (Greencreek) Chipset

Note: This is a general block diagram. Please see the previous Motherboard Features

pages for details on the features of each motherboard.

1-8

Page 15

Chapter 1: Introduction

1-2 Chipset Overview

Built upon the functionality and the capability of the 5000X (Greencreek) chipset,

the X7DA3+ motherboard provides the performance and feature set required for

dual processor-based workstations with confi guration options optimized for com-

munications, presentation, storage, computation or database applications. The

5000X (Greencreek) chipset supports single or dual Xeon 64-bit dual core processor

with front side bus speeds of up to 1.333 GHz. The chipset consists of the 5000X

(Greencreek) Memory Controller Hub (MCH), the Enterprise South Bridge 2 (ESB2),

and the I/O subsystem (PXH-V).

The 5000X (Greencreek) MCH chipset is designed for symmetric multiprocessing

across two independent front side bus interfaces. Each front side bus uses a 64-bit

wide, 1.333 GHz data bus that transfers data at 10.7 GB/sec. The MCH chipset con-

nects up to 8 Fully Buffered DIMM modules, providing a total of 32.0 GB/s for DDR2

667/533 memory. The MCH chipset also provides one x8 PCI-Express and one x4

ESI interface to the ESB2. In addition, the 5000X (Greencreek) chipset offers a wide

range of RAS features, including memory interface ECC, x4/x8 Single Device Data

Correction, CRC, parity protection, memory mirroring and memory sparing.

Xeon Dual Core Processor Features

Designed to be used with conjunction of the 5000X (Greencreek) chipset, the Xeon

Dual Core Processors provide a feature set as follows:

The Xeon Dual Core Processors

L1 Cache Size: Instruction Cache (32KB/16KB), Data Cache (32KB/24KB)

L2 Cache Size: 2MB (per core)

Data Bus Transfer Rate: 8.5 GB/s

Package: FC-LGA6/FC-LGA4, 771 Lands

1-9

Page 16

X7DA3+ User's Manual

1-3 Special Features

Recovery from AC Power Loss

BIOS provides a setting for you to determine how the system will respond when AC

power is lost and then restored to the system. You can choose for the system to

remain powered off (in which case you must hit the power switch to turn it back on)

or for it to automatically return to a power- on state. See the Power Lost Control

setting in the Advanced BIOS Setup section (Boot Features) to change this setting.

The default setting is Last State.

1-4 PC Health Monitoring

This section describes the PC health monitoring features of the X7DA3+. All have

an onboard System Hardware Monitor chip that supports PC health monitoring.

Onboard Voltage Monitoring

An onboard voltage monitor will scan these voltages continuously: CPU Cores,

Chipset Voltage, +3.3V, +5V, +12V, -12V, +3.3V Standby, +5V Standby and Vbat.

Once a voltage becomes unstable, a warning is given or an error message

is sent to the screen. Users can adjust the voltage thresholds to defi ne the

sensitivity of the voltage monitor.

Fan Status Monitor with Firmware Control

The PC health monitor can check the RPM status of the cooling fans. The onboard

CPU and chassis fans are controlled by Thermal Management via BIOS (under

Hardware Monitoring in the Advanced Setting).

Environmental Temperature Control

The thermal control sensor monitors the CPU temperature in real time and will turn

on the thermal control fan whenever the CPU temperature exceeds a user-defi ned

threshold. The overheat circuitry runs independently from the CPU. Once it detects

that the CPU temperature is too high, it will automatically turn on the thermal fan

control to prevent any overheat damage to the CPU. The onboard chassis thermal

circuitry can monitor the overall system temperature and alert users when the chas-

sis temperature is too high.

CPU Fan Auto-Off in Sleep Mode

The CPU fan activates when the power is turned on. It continues to operate when

the system enters Standby mode. When in sleep mode, the CPU will not run at full

power, thereby generating less heat.

1-10

Page 17

Chapter 1: Introduction

CPU Overheat LED and Control

This feature is available when the user enables the CPU overheat warning function

in the BIOS. This allows the user to defi ne an overheat temperature. When this tem-

perature is exceeded, both the overheat fan and the warning LED are triggered.

System Resource Alert

This feature is available when used with Supero Doctor III in the Windows OS

environment or used with Supero Doctor II in Linux. Supero Doctor is used to

notify the user of certain system events. For example, if the system is running

low on virtual memory and there is insuffi cient hard drive space for saving the

data, you can be alerted of the potential problem. You can also confi gure Supero

Doctor to provide you with warnings when the system temperature goes beyond

a pre-defi ned range.

1-5 ACPI Features

ACPI stands for Advanced Confi guration and Power Interface. The ACPI specifi ca-

tion defi nes a fl exible and abstract hardware interface that provides a standard

way to integrate power management features throughout a PC system, including

its hardware, operating system and application software. This enables the system

to automatically turn on and off peripherals such as CD-ROMs, network cards, hard

disk drives and printers. This also includes consumer devices connected to the PC

such as VCRs, TVs, telephones and stereos.

In addition to enabling operating system-directed power management, ACPI

provides a generic system event mechanism for Plug and Play and an operating

system-independent interface for confi guration control. ACPI leverages the Plug

and Play BIOS data structures while providing a processor architecture-independent

implementation that is compatible with Windows 2000, Windows XP and Windows

2003 Server.

Slow Blinking LED for Suspend-State Indicator

When the CPU goes into a suspend state, the chassis power LED will start blinking

to indicate that the CPU is in suspend mode. When the user presses any key, the

CPU will wake-up and the LED will automatically stop blinking and remain on.

Main Switch Override Mechanism

When an ATX power supply is used, the power button can function as a system

suspend button to make the system enter a SoftOff state. The monitor will be sus-

pended and the hard drive will spin down. Pressing the power button again will

cause the whole system to wake-up. During the SoftOff state, the ATX power

1-11

Page 18

X7DA3+ User's Manual

supply provides power to keep the required circuitry in the system alive. In case

the system malfunctions and you want to turn off the power, just press and hold

the power button for 4 seconds. This option can be set in the Power section of

the BIOS Setup routine.

External Wake-On-LAN

Wake-On-LAN is defi ned as the ability of a management application to remotely

power up a computer that is powered off. Remote PC setup, up-dates and asset

tracking can occur after hours and on weekends so that daily LAN traffi c is kept to

a minimum and users are not interrupted. The motherboard has a 3-pin header

(WOL) to connect to the 3-pin header on a Network Interface Card (NIC) that has

WOL capability. In addition, an onboard LAN controller can also support WOL

without any connection to the WOL header. The 3-pin WOL header is to be used

with a LAN add-on card only.

Note: Wake-On-LAN requires an ATX 2.01 (or above) compliant power supply.

1-6 Power Supply

As with all computer products, a stable power source is necessary for proper and

reliable operation. It is even more important for processors that have high CPU

clock rates.

The X7DA3+ can only accommodate 24-pin ATX power supply. Although most

power supplies generally meet the specifi cations required by the motherboard, some

are inadequate. You should use one that will supply at least 400W of power. In

addition, the 12V 8-pin and the 4-pin are also required for adequate power supply

to the system. Also your power supply must supply 1.5A for the Ethernet ports.

It is strongly recommended that you use a high quality power supply that meets ATX

power supply Specifi cation 2.01 or above. It must also be SSI compliant (For more

information, please refer to the website at http://www.ssiforum.org/). Additionally, in

areas where noisy power transmission is present, you may choose to install a line

fi lter to shield the computer from noise. It is recommended that you also install a

power surge protector to help avoid problems caused by power surges.

1-7 Super I/O

The disk drive adapter functions of the Super I/O chip include a fl oppy disk drive

controller that is compatible with industry standard 82077/765, a data separator,

write pre-compensation circuitry, decode logic, data rate selection, a clock genera-

tor, drive interface control logic and interrupt and DMA logic. The wide range of

1-12

Page 19

Chapter 1: Introduction

functions integrated onto the Super I/O greatly reduces the number of components

required for interfacing with fl oppy disk drives. The Super I/O supports 360 K, 720

K, 1.2 M, 1.44 M or 2.88 M disk drives and data transfer rates of 250 Kb/s, 500 Kb/s

or 1 Mb/s. It also provides two high-speed, 16550 compatible serial communication

ports (UARTs). Each UART includes a 16-byte send/receive FIFO, a programmable

baud rate generator, complete modem control capability and a processor interrupt

system. Both UARTs provide legacy speed with baud rate of up to 115.2 Kbps

as well as an advanced speed with baud rates of 250 K, 500 K, or 1 Mb/s, which

support higher speed modems.

The Super I/O supports one PC-compatible printer port (SPP), Bi-directional Printer

Port (BPP) , Enhanced Parallel Port (EPP) or Extended Capabilities Port (ECP).

The Super I/O provides functions that comply with ACPI (Advanced Confi guration

and Power Interface), which includes support of legacy and ACPI power manage-

ment through an SMI or SCI function pin. It also features auto power management

to reduce power consumption.

1-13

Page 20

X7DA3+ User's Manual

Notes

1-14

Page 21

Chapter 2: Installation

Chapter 2

Installation

2-1 Static-Sensitive Devices

Electro-Static-Discharge (ESD) can damage electronic com ponents. To prevent

damage to your system board, it is important to handle it very carefully. The following

measures are generally suffi cient to protect your equipment from ESD.

Precautions

• Use a grounded wrist strap designed to prevent static discharge.

• Touch a grounded metal object before removing the board from the antistatic

bag.

• Handle the board by its edges only; do not touch its components, peripheral

chips, memory modules or gold contacts.

• When handling chips or modules, avoid touching their pins.

• Put the motherboard and peripherals back into their antistatic bags when not in

use.

• For grounding purposes, make sure your computer chassis provides excellent

conductivity between the power supply, the case, the mounting fasteners and

the motherboard.

Unpacking

The motherboard is shipped in antistatic packaging to avoid static damage. When

unpacking the board, make sure the person handling it is static protected.

2-2 Motherboard Installation

(Note: Be sure to mount the motherboard into the chassis before you

install the CPU onto the motherboard.)

All motherboards have standard mounting holes to fi t different types of chassis.

Make sure that the locations of all the mounting holes for both motherboard and

chassis match. Make sure that the metal standoffs click in or are screwed in

tightly. Then, use a screwdriver to secure the motherboard onto the motherboard

tray. (Note: some components are very close to the mounting holes. Please

take precautionary measures to prevent damage done to these components

when you install the motherboard into the chassis.)

2-1

Page 22

X7DA3+ User's Manual

!

2-3 Processor and Heatsink Installation

When handling the processor package, avoid placing

direct pressure on the label area of the fan.

Notes: 1. Always connect the power cord last and always remove it before adding,

removing or changing any hardware components. Make sure that you install the

processor into the CPU socket before you install the CPU heatsink.

2. Intel's boxed Xeon CPU package contains the CPU fan and heatsink assembly.

If you buy a CPU separately, make sure that you use only Intel-certifi ed multi-di-

rectional heatsink and fan.

3. The Intel Xeon LGA 771 heatsink and fan comes with a push-pin design and no

tool is needed for installation.

4. Make sure to install the motherboard into the chassis before you install the CPU

heatsink and fan.

5. When purchasing an LGA 771 CPU or when receiving a motherboard with an LGA

771 CPU pre-installed, make sure that the CPU plastic cap is in place and none of

the CPU pins are bent; otherwise, contact the retailer immediately.

6. Refer to the MB Features Section for more details on CPU support.

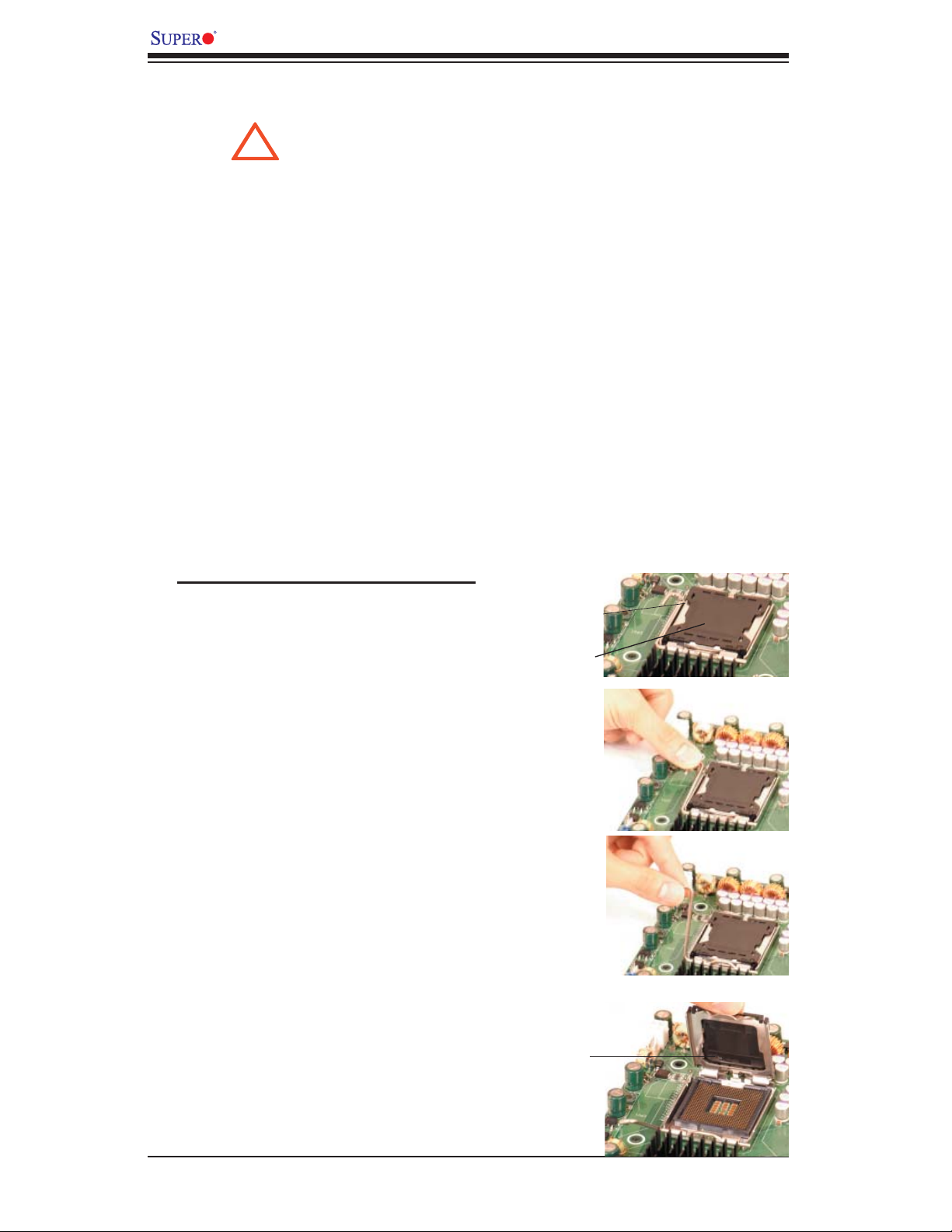

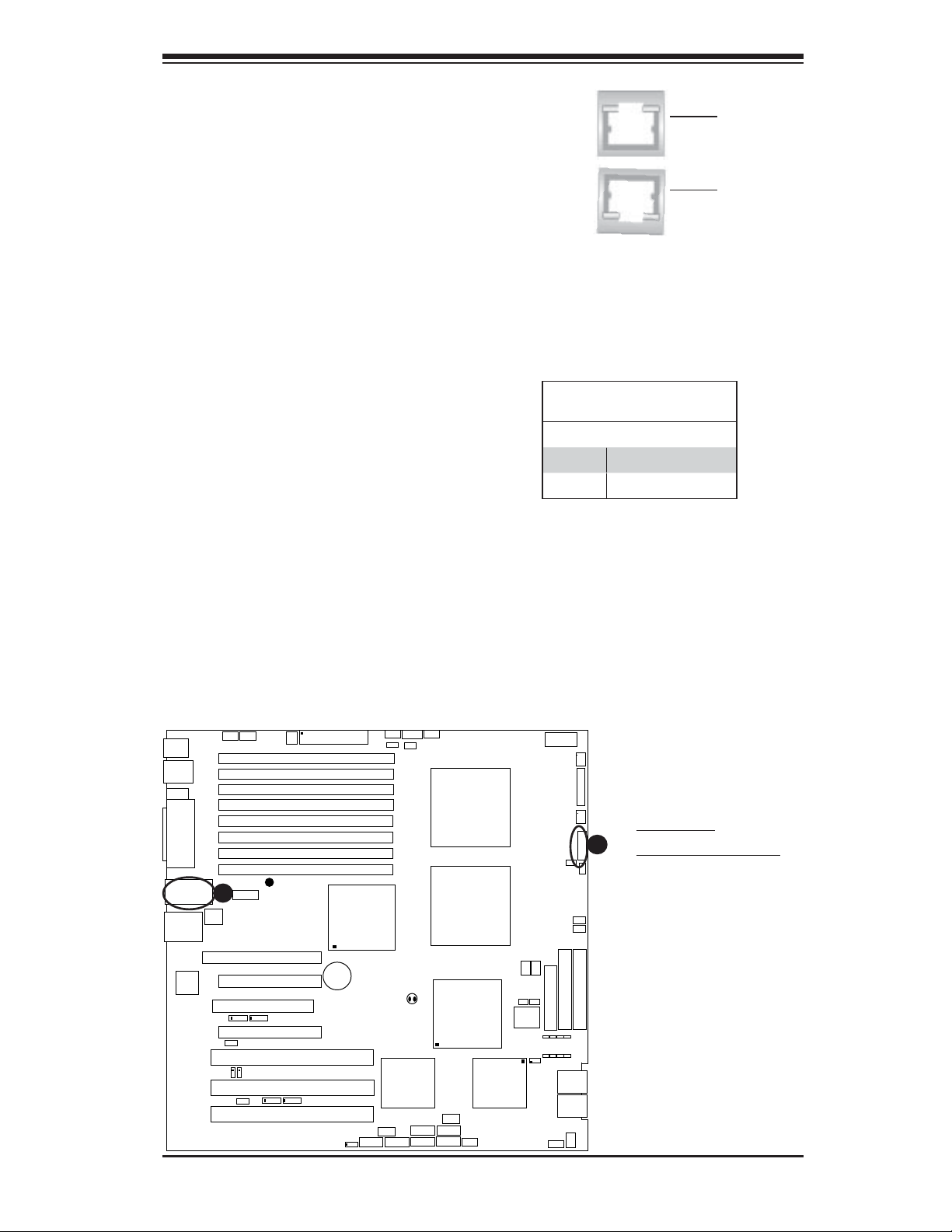

Installing the LGA771 Processor

Load Lever

PnP Cap on

top of the

1. Press the load lever to release

the load plate, which covers the CPU

socket, from its locking position.

2. Gently lift the load lever to open the

load plate.

Load Plate

Load Plate

(with PnP Cap

attached)

2-2

Page 23

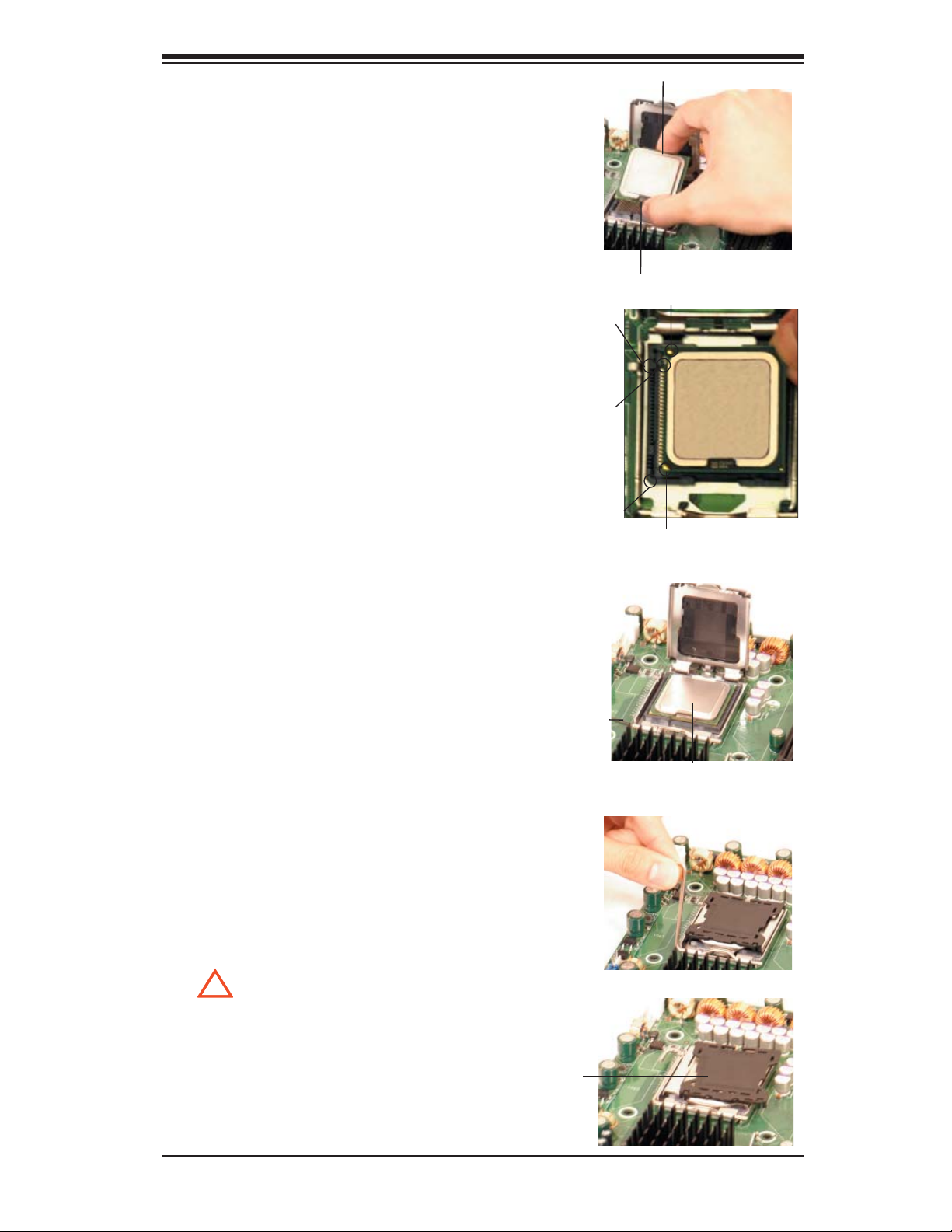

3. Use your thumb and your index

!

fi nger to hold the CPU at the North

Center Edge and the South Center

Edge of the CPU.

4. Align CPU Pin1 (the CPU corner

marked with a triangle) against the

socket corner that is marked with a

triangle cutout.

5. Align the CPU key that is the semi-

circle cutout below a gold dot against

the socket key, the Notch on the

same side of the triangle cutout on

the socket.

6. Once aligned, carefully lower the

CPU straight down to the socket.

(Do not drop the CPU on the socket.

Do not move the CPU horizontally or

vertically. Do not rub the CPU against

the surface or against any pins of the

socket to avoid damage to the CPU

or the socket.)

Socket Key

(Socket Notch)

CPU Key (semi-

circle cutout) be-

low the circle.

Corner with a

triangle cutout

Chapter 2: Installation

North Center Edge

South Center Edge

gold dot

CPU Pin1

7. With the CPU inside the socket,

inspect the four corners of the CPU

to make sure that the CPU is properly

installed.

8. Use your thumb to gently push the

load lever down to the lever lock.

9. If the CPU is properly installed into

the socket, the plastic PnP cap will be

automatically released from the load

plate when the load lever is pushed

in the lever lock. Remove the PnP cap

from the motherboard.

(Warning: Please save the plas-

tic PnP cap. The motherboard must

be shipped with the PnP cap properly

installed to protect the CPU socket

pins. Shipment without the PnP cap

properly installed will cause damage

to the socket pins.)

Load Lever

CPU in the CPU socket

Plastic cap

is released

from the

load plate

if CPU

properly

installed.

2-3

Page 24

X7DA3+ User's Manual

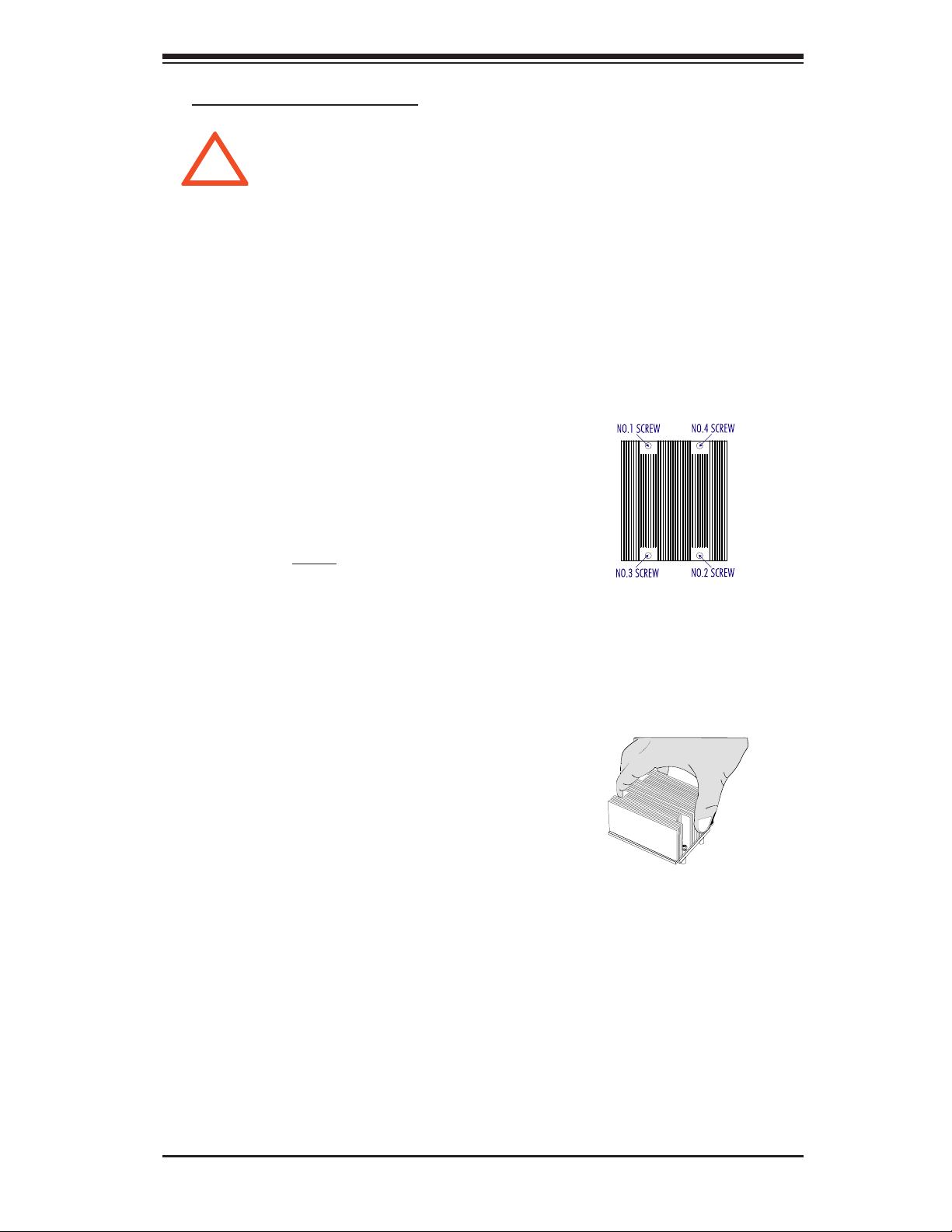

Installing the Heatsink

CEK Heatsink Installation

1. Do not apply any thermal grease to

the heatsink or the CPU die-the required

amount has already been applied.

2. Place the heatsink on top of the CPU so

that the four mounting holes are aligned with

those on the retention mechanism.

3. Screw in two diagonal screws (ie the #1

and the #2 screws) until just snug (-do not

fully tighten the screws to avoid possible

damage to the CPU.)

CEK Passive Heatsink

Screw#1

Screw#1

Screw#2

4. Finish the installation by fully tightening

all four screws.

Screw#2

2-4

Page 25

Uninstalling the Heatsink

!

(Warning: We do not recommend

that the CPU or the heatsink be

removed. However, if you do need

to remove the heatsink, please

follow the instructions below to

uninstall the heatsink to prevent

damage done to the CPU or the

CPU socket.)

1. Unscrew and remove the heatsink screws

from the motherboard in the sequence as

shown in the picture on the right.

Chapter 2: Installation

2. Hold the heatsink as shown in the picture

on the right and gently wriggle the heatsink to

loosen it from the CPU. (Do not use excessive

force when wriggling the heatsink!!)

3. Once the CPU is loosened, remove the

heatsink from the CPU socket.

4. Clean the surface of the CPU and the

heatsink to get rid of the old thermal grease.

Reapply the proper amount of thermal grease

on the surface before you re-install the CPU

and the heatsink.

2-5

Page 26

X7DA3+ User's Manual

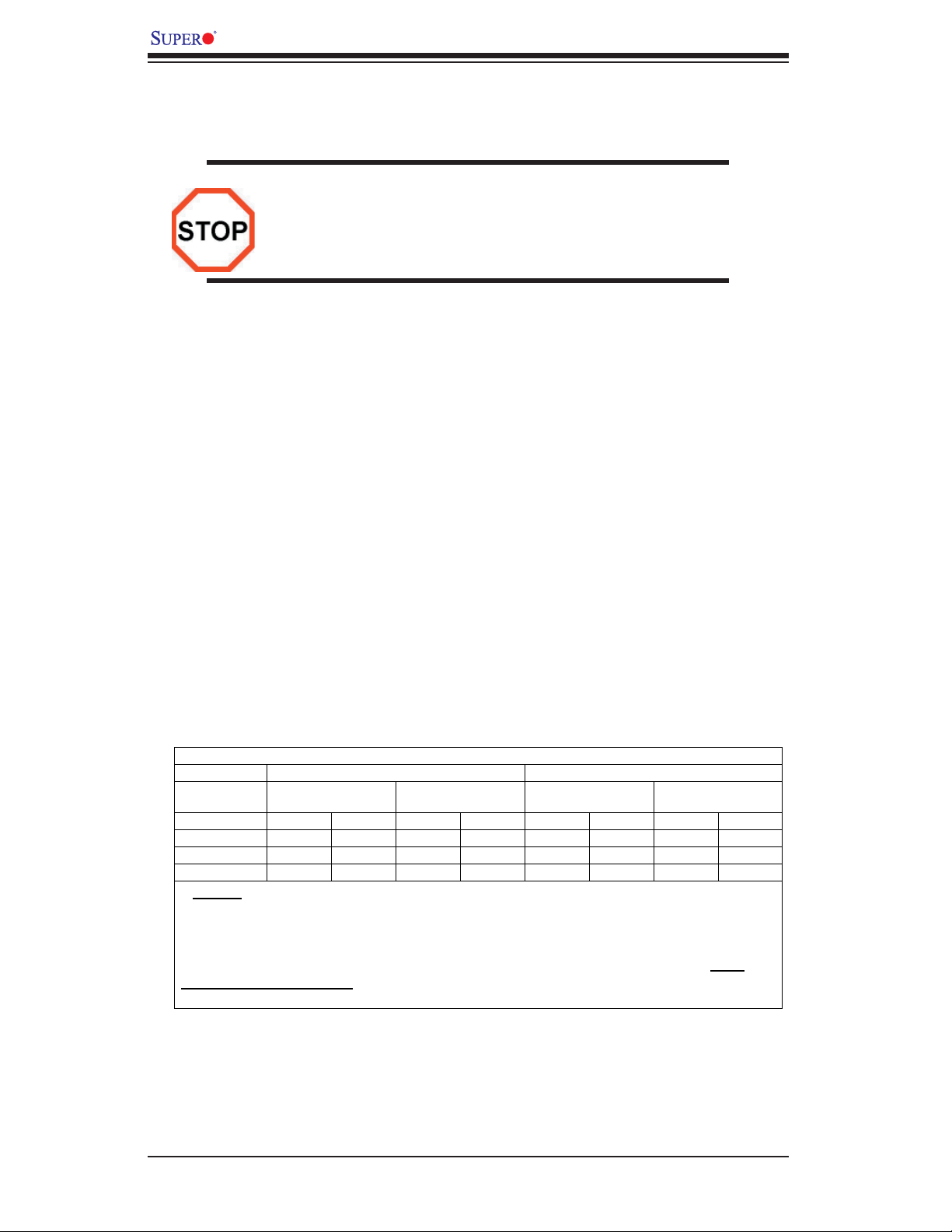

2-4 Installing DIMMs

Note: Check the Supermicro web site for recommended memory modules.

CAUTION

Exercise extreme care when installing or removing DIMM

modules to prevent any possible damage. Also note that the

memory is interleaved to improve performance (see step 1).

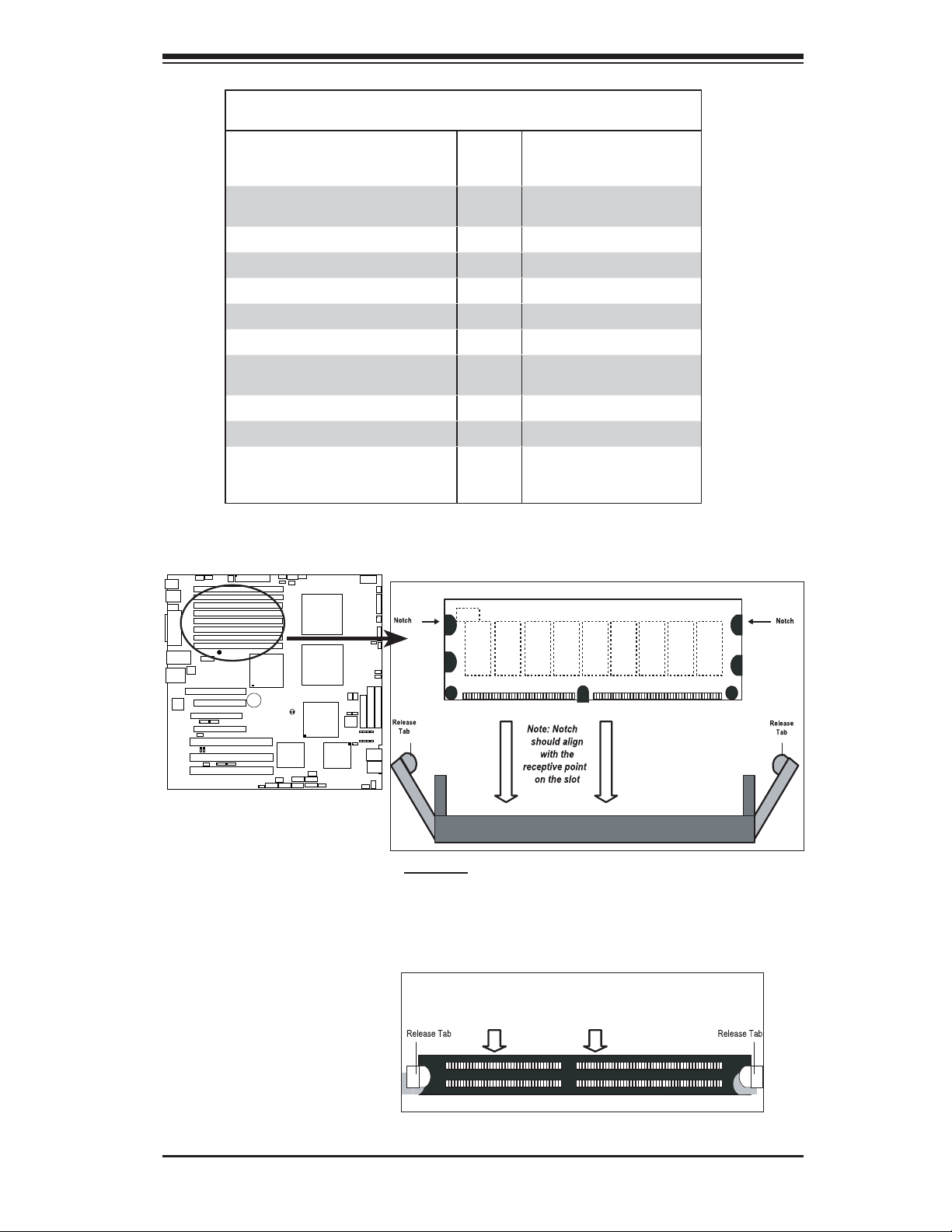

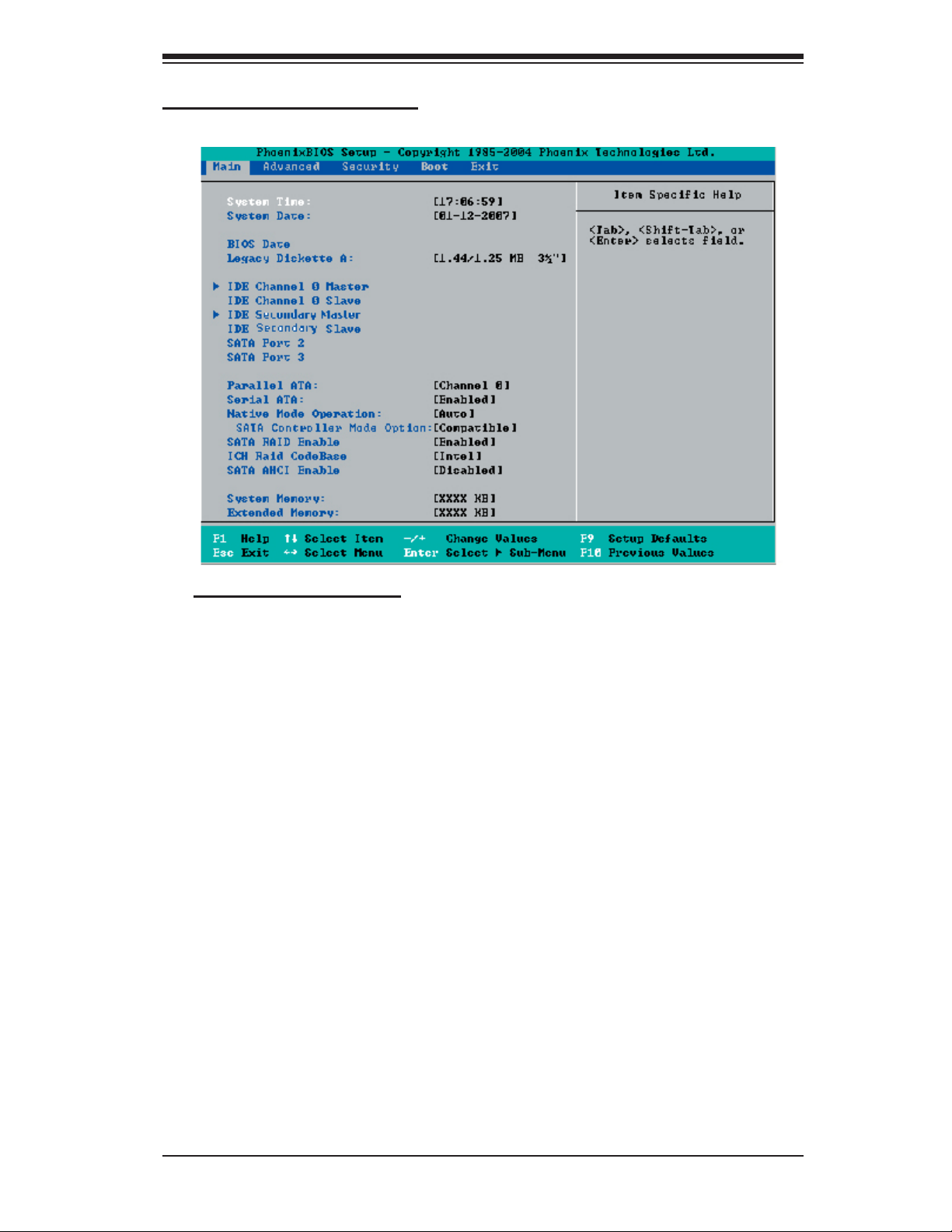

DIMM Installation (See Figure 2-2)

1. Insert the desired number of DIMMs into the memory slots, starting with Bank

1. (For optimal memory performance, please install four modules at a time.

Please refer to the table below.)

2. Insert each DIMM module vertically into its slot. Pay attention to the notch along

the bottom of the module to prevent inserting the DIMM module incorrectly.

3. Gently press down on the DIMM module until it snaps into place in the slot.

Repeat for all modules (see step 1 above).

Memory Support

The X7DA3+ supports up to 32 GB fully buffered (FBD) ECC DDR2 533/667 in 8

DIMMs. Populating DIMM modules with a pair (or pairs) of memory modules that

are of the same size and of the same type in Bank1, Bank2, Bank3 and Bank4 will

result in interleaving memory.

Note 1: Due to the OS limitations, some operating systems may not show more

than 4 GB of memory.

Optimized DIMM Population Configurations

Branch0 Branch1

Number of

DIMMs

2 DIMMs 1A ------ 2A ------ ------ ------ ------ -----4 DIMMs 1A ------ 2A ------ 3A ------ 4A -----6 DIMMs 1A 1B 2A 2B 3A ------ 4A -----8 DIMMs 1A 1B 2A 2B 3A 3B 4A 4B

(*Notes: i. DIMM slot# specified: DIMM slot to be populated; “---“: DIMM slot not to

be populated. ii. Both FBD 533 MHz and 667MHz DIMMs are supported; however,

you need to use the memory modules of the same speed and of the same type on a

motherboard. iii. Interleaved memory is supported when pairs of DIMM modules are

installed. To optimize memory performance, please install pairs of DIMMs in both

Branch 0 and Branch 1. iv. For memory to work properly, you need to follow the

restrictions listed above. )

Bank 1

(Channel 0)

Bank 2

(Channel 1)

Bank 3

(Channel 2)

Bank 4

(Channel 3)

Note 2: Due to memory allocation to system devices, memory remaining available

for operational use will be reduced when 4 GB of RAM is used. The reduction in

memory availability is disproportional. (Refer to the following Memory Availability

Table for details.)

2-6

Page 27

DDR2 FBD DIMM

Possible System Memory Allocation & Availability

Chapter 2: Installation

System Device Size Physical Memory

Remaining (-Available)

(4 GB Total System Memory)

Firmware Hub fl ash memory (System

1 MB 3.99

BIOS)

Local APIC 4 KB 3.99

Area Reserved for the chipset 2 MB 3.99

I/O APIC (4 Kbytes) 4 KB 3.99

PCI Enumeration Area 1 256 MB 3.76

PCI Express (256 MB) 256 MB 3.51

PCI Enumeration Area 2 (if needed)

512 MB 3.01

-Aligned on 256-MB boundary-

VGA Memory 16 MB 2.85

TSEG 1 MB 2.84

Memory available to OS and other ap-

2.84

plications

Installing and Removing DIMMs

JLAN1

®

3+

A

X7D

R

PE

U

S

To Remove:

Use your thumbs

to gently push

the release tabs

near both ends of

the module. This

should release it

from the slot.

DDR2 FBD

To Install: Insert module vertically and press down until it

snaps into place. Pay attention to the alignment notch at

the bottom.

Top View of DDR2 FBD Slot

Top View of DDR2 FBD

2-7

Page 28

X7DA3+ User's Manual

1

2

3

4

5

6

789

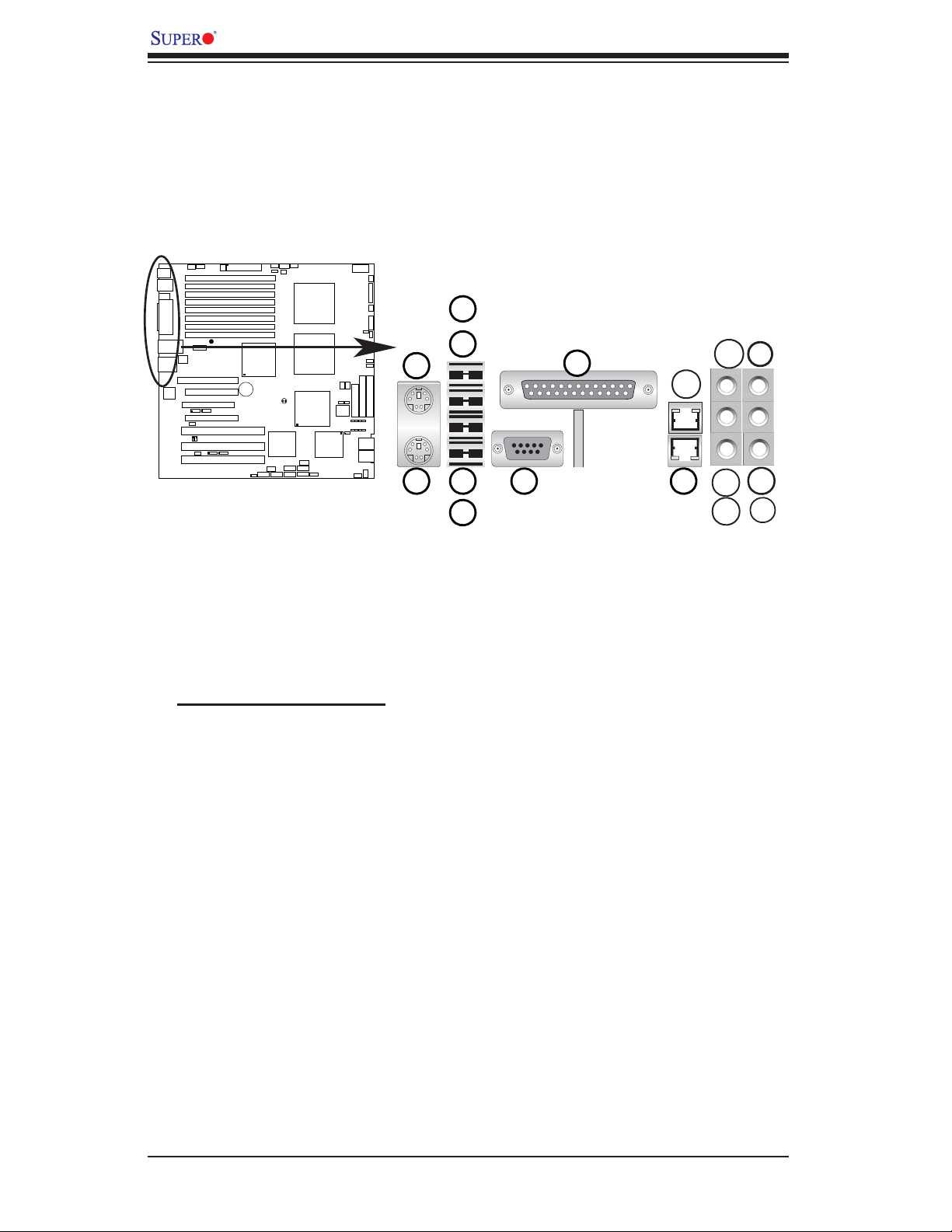

2-5 Control Panel Connectors/IO Ports

The I/O ports are color coded in conformance with the PC 99 specifi cation. See

Figure 2-3 below for the colors and locations of the various I/O ports.

Back Panel Connectors/IO Ports

JLAN1

®

3+

A

X7D

R

PE

U

S

13

10

12

16

15

Back Panel I/O Port Locations and Defi nitions

Back Panel Connectors

1. Keyboard (Purple)

2. PS/2 Mouse (Green)

3. Back Panel USB Port 0

4. Back Panel USB Port 1

5. Back Panel USB Port 2

6. Back Panel USB Port 3

7. COM Port 1 (Turquoise)

8. Parallel Port (Printer)

9. Gigabit LAN 2

10. Gigabit LAN 1

11. Side_Surround (Grey)

12. Back_Surround (Black)

13. CEN/LFE (Orange)

14. Microphone-In (Pink)

15. Front (Green)

16. Line-In (Blue)

(See Section 2-5 for details.)

11

14

2-8

Page 29

Chapter 2: Installation

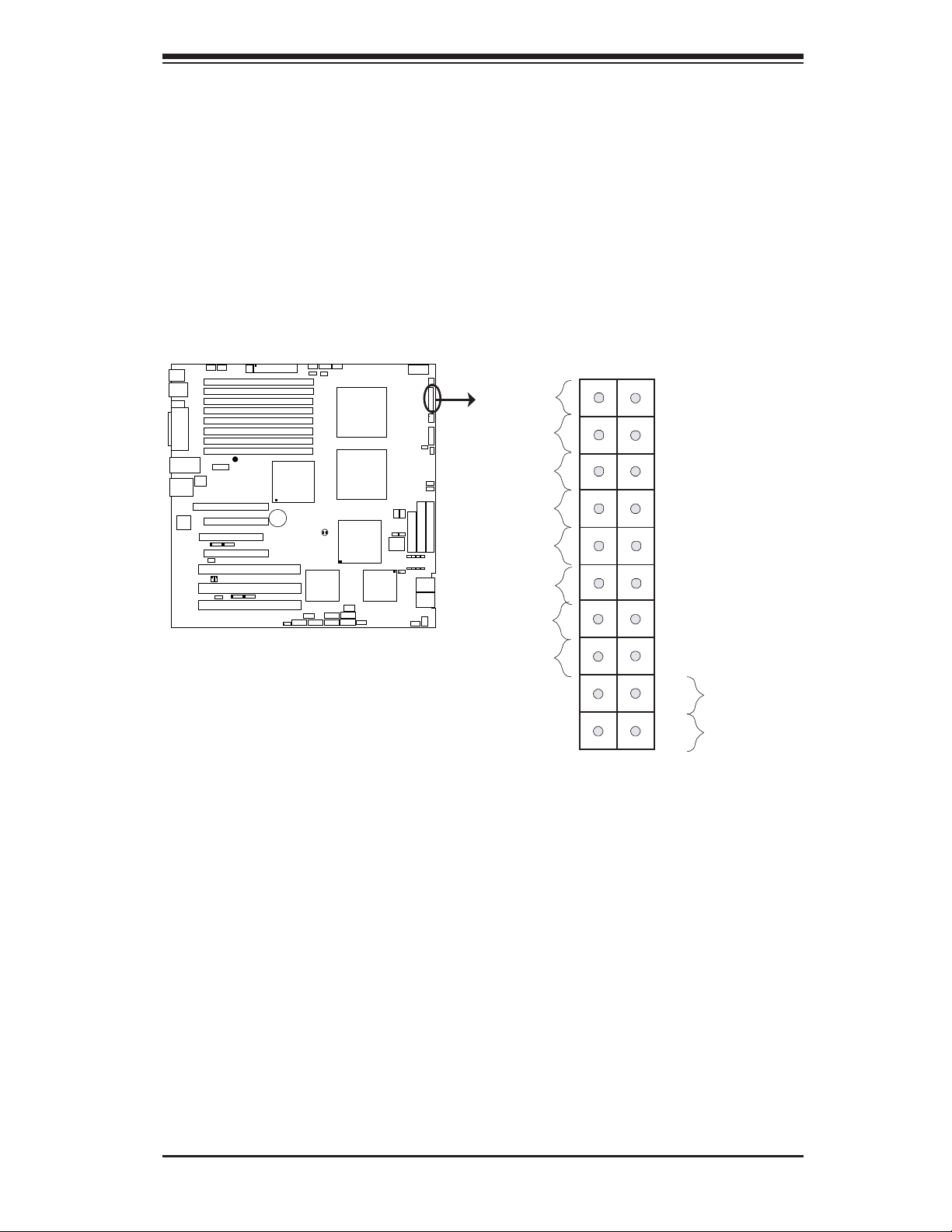

Front Control Panel

JF1 contains header pins for various buttons and indicators that are normally located

on a control panel at the front of the chassis. These connectors are designed specifi -

cally for use with Supermicro server chassis. See Figure 2-4 for the descriptions of

the various control panel buttons and LED indicators. Refer to the following section

for descriptions and pin defi nitions.

JF1 Header Pins

1920

Ground

NMI

JLAN1

®

UPER X7DA3+

S

X

Power LED

HDD LED

NIC1 LED

NIC2 LED

OH/Fan Fail LED

PWR Fail LED

Ground

Ground

X

Vcc

Vcc

Vcc

Vcc

Vcc

Vcc

Reset

PWR

2

1

Reset Button

Power Button

2-9

Page 30

X7DA3+ User's Manual

Front Control Panel Pin Defi nitions

NMI Button

The non-maskable interrupt button

header is located on pins 19 and 20

of JF1. Refer to the table on the right

for pin defi nitions.

Power LED

NMI Button

Pin Defi nitions (JF1)

Pin# Defi nition

19 Control

20 Ground

The Power LED connection is located

on pins 15 and 16 of JF1. Refer to the

table on the right for pin defi nitions.

A. NMI

B. PWR LED

KB/

Mouse

USB 0/

/2/3

1

COM1

LAN1/2

HD

Audio

Parrallel

Port

JLAN1

LAN

G

TLR

C

S

Audio

CTRL

ank

CPU

PWR

X

T

A

Fan 1

JPW1

k

4)

4

)

k

3)

3

)

1)

Greencreek

ridg

B

h

Nort

attery

B

lot)

S

JL1

SATA

4-Pin

4-Pin

2

5

Fan

6

Fan

WR

P

JPW2

DIMM

4B (Ban

DIMM

4

A (

Bank

DIMM

3B (Ban

DIMM

3

A (

Bank

DIMM

2B (Bank 2)

DIMM

2A (Bank 2)

DIMM 1

B (B

DI

MM

1A (Bank 1)

®

A3+

D

X7

R

UPE

S

CD1

7

lot

SIM LP IPMI

lot6

S

PCI-Exp x16

5

Slot

PCI-33MHz

2

2

C4

I

J

3

C

I

J

4

Slot

4

x

p

x

-E

CI

P

WD

J

3

Slot

Slot

JW

Slot

z

H

M

33

1

X

-

CI

P

JPL2

JPL1

2

z

H

M

33

1

X

-

CI

P

2

2

C2

I

J

1

C

I

J

OR

1

-

CI

P

reen

G

(

CR

Z

z

MH

00

1

X

PSF

7

Fan

J17

J3P

JAR

e

JBT1

PXH

MB

S

0

SATA

South

Bridge

/5

4

B

S

U

5

A

T

4

SA

SATA

3

2

SATA

1

SATA

Power LED

Pin Defi nitions (JF1)

Pin# Defi nition

15 +5V

16 Ground

8-pin PWR

JPW3

1

Fan

Ground

JF1

L

E1

SGP

SGP

FP Control

Fan2

SPK

PW LED

JOH1

I

O1

I

O

2

B

Power LED

HDD LED

NIC1 LED

X

1

U

P

C

2

PU

C

NIC2 LED

CPU

Fan2

Fan8

Fan3

ct Flash

IDE1

1

AC

ACT0-3

JS10

Floppy

T4

ompa

C

-7

SAS4-7

SAS0-3

Fan4

OH/Fan Fail LED

PWR Fail LED

Ground

Ground

WF

J

F1

JC

S

O

I

B

J

PS1

SAS

Controller

OL

W

J

1920

NMI

A

X

Vcc

Vcc

Vcc

Vcc

Vcc

Vcc

Reset

Reset Button

Power Button

PWR

2

1

2-10

Page 31

HDD LED

The HDD LED connection is located

on pins 13 and 14 of JF1. Attach the

hard drive LED cable here to display

disk activity (for any hard drives on

the system, including SAS, Serial ATA

and IDE). See the table on the right

for pin defi nitions.

NIC1/NIC2 LED Indicators

The NIC (Network Interface Control-

ler) LED connection for GLAN port1 is

located on pins 11 and 12 of JF1 and

the LED connection for GLAN Port2

is on Pins 9 and 10. Attach the NIC

LED cables to display network activity.

Refer to the table on the right for pin

defi nitions.

Chapter 2: Installation

HDD LED

Pin Defi nitions (JF1)

Pin# Defi nition

13 +5V

14 HD Active

GLAN1/2 LED

Pin Defi nitions (JF1)

Pin# Defi nition

9/11 Vcc

10/12 Ground

A. HDD LED

B. NIC1 LED

C. NIC2 LED

USB 0/

/2/3

1

COM1

LAN1/2

Parrallel

HD

Audio

G

C

Port

JLAN1

LAN

TLR

S

Audio

CTRL

lot

Fan

S

7

lot

S

5

Slot

Slot

3

Slot

2

Slot

OR

JW

1

Slot

KB/

Mouse

Fan

6

UPER

CD1

SIM LP IPMI

6

PCI-Exp x16

PCI-33MHz

2

3

C

I

J

4

-E

CI

P

WD

J

X

-

CI

P

JPL2

JPL1

X

-

CI

P

X

-

CI

P

CPU

4-Pin

4-Pin

2

PWR

X

T

WR

P

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM 1

DI

MM

®

4

z

H

M

z

H

M

2

1

C

I

z

JPW2

4B (Ban

4

A (

3B (Ban

3

A (

2B (Bank 2)

2A (Bank 2)

B (B

1A (Bank 1)

A3+

D

2

C2

I

J

reen

G

(

CR

Z

Bank

Bank

ank

A

JPW1

k

4)

4

)

k

3)

3)

1)

Greencreek

ridg

B

h

Nort

attery

B

lot)

S

JL1

SATA

5

X7

2

C4

I

J

x

p

x

33

1

33

1

J

MH

00

1

PSF

7

Fan

J17

Fan 1

J3P

JAR

1

U

P

C

2

U

P

e

JBT1

PXH

MB

S

0

SATA

C

South

Bridge

SAS

Controller

/5

4

B

S

U

5

A

T

4

SA

SATA

3

2

SATA

1

SATA

OL

W

J

8-pin PWR

JPW3

Fan1

JF1

FP Control

Fan2

SPK

PW LED

L

E1

JOH1

SGP

I

O1

SGP

I

O

2

CPU

Fan2

Fan8

Fan3

y

ct Flash

IDE1

1

WF

J

F1

JC

Flopp

ompa

C

ACT0

AC

T4

-7

-3

SAS4-7

SAS0-3

JS10

Fan4

OH/Fan Fail LED

S

O

I

B

J

PS1

Ground

Power LED

HDD LED

A

B

NIC1 LED

NIC2 LED

C

PWR Fail LED

X

Ground

Ground

1920

NMI

X

Vcc

Vcc

Vcc

Vcc

Vcc

Vcc

Reset

Reset Button

Power Button

PWR

2

1

2-11

Page 32

X7DA3+ User's Manual

Overheat/Fan Fail LED (OH)

Connect an LED to the OH/Fan Fail

connection on pins 7 and 8 of JF1 to

provide advanced warning of chassis

overheating or fan failure. Refer to the

table on the right for pin defi nitions.

Power Fail LED

The Power Fail LED connection is

located on pins 5 and 6 of JF1. Re-

fer to the table on the right for pin

defi nitions.

OH/Fan Fail LED

Pin Defi nitions (JF1)

Pin# Defi nition

7 Vcc

8 Ground

OH/Fan Fail Indicator

Status

State Defi nition

Off Normal

On Overheat

Flash-

Fan Fail

ing

PWR Fail LED

Pin Defi nitions (JF1)

Pin# Defi nition

5 Vcc

6 Ground

A. OH/Fan Fail LED

B. PWR Supply Fail

4-Pin

5

Fan

6

USB 0/

/2/3

1

COM1

LAN1/2

HD

Audio

Parrallel

Port

JLAN1

LA

G

TLR

C

S

Audio

CTRL

7

Slot

N

Slot

Slot

Slot

lot

S

Slot

JW

Slot

Fan

WR

P

DIMM 4

DIMM

DIMM 3B (

DIMM

DIMM 2

DIMM

DIMM 1B (Bank 1)

DIMM 1A (

®

PER X7DA3+

U

CD1

SIM LP IPMI

6

PCI-Exp x16

5

PCI-33MHz

2

2

4

C

I

J

3

C

I

J

4

4

x

p

x

E

-

CI

P

WD

J

3

z

H

M

33

1

X

CI-

P

JPL2

JPL1

2

z

H

M

33

1

X

CI-

P

2

1

C

I

J

OR

1

Z

z

H

M

00

1

X

-

CI

P

KB/

Mouse

24

JPW2

B

(

Bank

4A (Bank 4)

Bank 3

3A (Bank 3)

B (B

2A (Bank 2)

2

2

C

I

J

reen S

G

(

CR

-Pin

B

A

ank

ank 1)

lot)

T

B

attery

PWR

X

4)

2)

JPW1

)

Greencree

North Brid

JL1

CPU

PSF

7

Fan

J17

Fan 1

J3P

JAR

1

PU

C

k

e

g

JBT1

XH

P

SA

MB

S

0

1

SA

A

A

T

T

SA

SA

2

U

P

C

South

ge

Brid

SAS

Controller

/5

4

B

S

U

5

4

SATA

A

T

3

A

T

2

SA

A

T

L

O

W

J

8-pin PWR

JPW3

1

Fan

Ground

JF1

FP Control

2

Fan

SPK

Power LED

PW LED

L

E1

JOH1

HDD LED

SGP

I

O1

NIC1 LED

SGP

I

O

2

h

CPU

Fan2

Fan3

Fan8

1

DE

I

1

WF

J

1

F

JC

I

B

Floppy

S

O

ACT4

AC

T0-3

J

PS1

SAS

0

JS1

OH/Fan Fail LED

ompact Flas

C

PWR Fail LED

-7

-7

4

SAS0-3

Fan4

X

NIC2 LED

A

B

Ground

Ground

1920

NMI

X

Vcc

Vcc

Vcc

Vcc

Vcc

Vcc

Reset

Reset Button

Power Button

PWR

2

1

2-12

Page 33

Chapter 2: Installation

Reset Button

The Reset Button connection is located

on pins 3 and 4 of JF1. Attach it to the

hardware reset switch on the computer

case. Refer to the table on the right for

pin defi nitions.

Power Button

The Power Button connection is located

on pins 1 and 2 of JF1. Momentarily

contacting both pins will power on/off

the system. This button can also be con-

fi gured to function as a suspend button

(with a setting in BIOS - see Chapter 4).

To turn off the power when set to suspend

mode, press the button for at least 4

seconds. Refer to the table on the right

for pin defi nitions.

Reset Button

Pin Defi nitions (JF1)

Pin# Defi nition

3 Reset

4 Ground

Power Button

Pin Defi nitions (JF1)

Pin# Defi nition

1 Signal

2 +3V Standby

A. Reset Button

B. PWR Button

6

USB 0/

/2

1

C

LAN1/2

/

OM1

Parrallel

HD

Audio

3

G

C

Port

JLAN1

LAN

TLR

Fan

UPER X7DA3+

S

Audio

CTRL

7

Slot

6

Slot

5

Slot

2

I

J

4

Slot

P

3

Slot

P

JPL1

2

Slot

P

OR

JW

1

lot

S

P

KB/

Mouse

5

Fan

CD1

SIM LP IPMI

PCI-Exp x16

PCI-33MHz

2

C

I

J

C3

p

x

-E

CI

WD

J

33

1

X

CI-

JPL2

33

1

X

-

CI

00

1

X

-

CI

4

4

x

M

M

J

M

4-Pin

24-Pin

A

WR

P

JPW2

DIMM

4B (Bank 4)

DIMM 4A (Bank 4)

DIMM

3B (Bank 3)

DIMM

3A (Bank 3)

D

I

MM 2B (Bank 2)

DIMM

2

A

(Bank 2

DIMM

1B (Bank 1)

DIMM

1A (Bank 1)

®

B

z

H

z

H

2

2

2

C

I

J

1

C

I

lot

reen S

G

(

CR

Z

z

H

PWR

X

T

)

atter

)

JPW1

Greencreek

North Bridg

y

JL

1

SATA

CPU

PSF

7

Fan

J17

Fan 1

J3P

JAR

1

PU

C

2

U

P

SATA

SATA

C

South

Bridge

SAS

Controller

/5

4

B

S

U

5

4

SATA

3

2

SATA

WOL

J

e

T1

JB

PXH

MB

S

0

1

SATA

8-pin PWR

JPW3

1

Fan

Ground

JF1

FP Control

Fan2

SPK

Power LED

PW LED

L

E1

JOH1

SGP

I

O1

SGP

CPU

Fan2

Fan8

Fan3

ct Flash

1

WF

J

F1

JC

Floppy

ompa

C

S

O

I

B

AC

T4-7

ACT0

-

3

J

PS

1

SAS4-7

SAS0-3

JS10

NIC1 LED

I

O

2

IDE1

OH/Fan Fail LED

PWR Fail LED

Fan4

X

HDD LED

NIC2 LED

Ground

Ground

1920

NMI

X

Vcc

Vcc

Vcc

Vcc

Vcc

Vcc

Reset

Reset Button

A

Power Button

PWR

2

1

B

2-13

Page 34

X7DA3+ User's Manual

2-6 Connectors and Headers

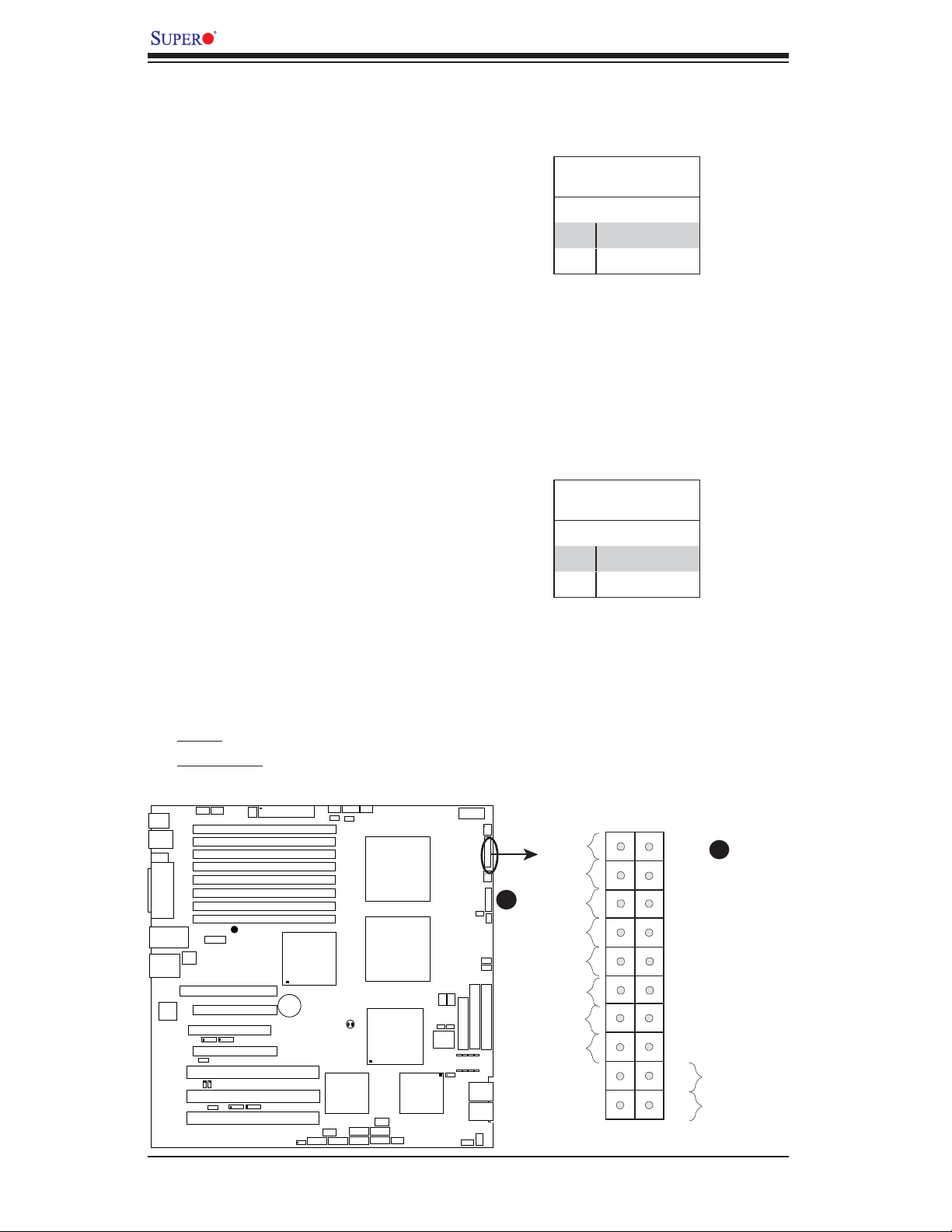

ATX Power Connector

There are a 24-pin main power supply

connector(JPW1) and an 8-pin CPU

PWR connector (JPW3) on the moth-

erboard. These power connectors

meet the SSI EPS 12V specifi cation.

The 4-pin 12V PWR supply located at

JPW2 is also required to provide ad-

equate power to the system. See the

table on the right for pin defi nitions.

For the 8-pin PWR (JPW3), please

refer to the item listed below.

Processor Power Connector

In addition to the Primary ATX power

connector (above), the 12V 8-pin CPU

PWR connector at JPW3 must also

be connected to your power supply.

See the table on the right for pin

defi nitions.

ATX Power 24-pin Connector

Pin Defi nitions

Pin# Defi nition Pin # Defi nition

13 +3.3V 1 +3.3V

14 -12V 2 +3.3V

15 COM 3 COM

16 PS_ON 4 +5V

17 COM 5 COM

18 COM 6 +5V

19 COM 7 COM

20 Res (NC) 8 PWR_OK

21 +5V 9 5VSB

22 +5V 10 +12V

23 +5V 11 +12V

24 COM 12 +3.3V

Required Connection

12V 4-pin Power

Connector

Pin Defi nitions

Pins Defi nition

1 and 2 Ground

3 and 4 +12V

12V 8-pin Power Con-

Pins Defi nition

1 through 4 Ground

5 through 8 +12V

Required Connection

nector

Pin Defi nitions

KB/

M

USB

1/2/3

ouse

COM1

0

Parrallel

LAN1/2

HD

Audio

G

C

/

Port

JLAN1

AN

L

TLR

5

Fan

6

Fan

UPER X7DA3+

S

CD1

Audio

CTRL

7

Slot

SIM LP IPMI

6

Slot

PCI-Exp x16

5

Slot

PCI-33MHz

2

2

C4

I

J

C3

I

J

4

Slot

Exp x

PCI-

JWD

3

Slot

133 M

CI-X

P

JPL2

JPL1

2

Slot

133

-X

CI

P

WOR

J

1

Slot

100 M

CI-X

P

C

-Pin

-Pin

4

4

2

WR

P

JPW2

D

I

MM

4B

(B

D

IMM 4

A

(B

DIMM 3B (Bank

D

IMM 3A

(B

DIMM

2B

(Bank

D

IMM 2A

(B

D

IMM

1B (Ban

D

I

MM

1

A

(B

®

4

Hz

Hz

M

2

2

C2

I

J

C1

I

J

(Green

CR

Hz Z

T

A

ank

ank 4)

an

k

an

k 2

k

an

k 1

B

lot)

S

A

X PWR

4)

3)

3)

2)

1)

atter

)

)

G

North

y

JL

JPW1

reencree

Brid

1

SA

CPU

Fan 1

TA

J17

J3P

JAR

CPU1

k

e

g

JBT1

H

X

P

SATA4

SMB

0

1

SATA2

TA

SA

USB4/

SATA5

SA

2

U

CP

South

ge

rid

B

SAS

Controller

5

TA3

WOL

J

CPU

8-pin PWR

JPW3

Fan1

F1

J

FP Control

2

Fan

SPK

PW LED

LE1

JOH1

SG

P

IO1

SG

P

IO2

Fan2

Fan3

Fan8

Flash

y

ct

DE1

JWF1

F1

C

J

OS

I

B

JP

I

Flopp

ompa

C

ACT4-

7

AC

T

0-3

S

1

7

-

4

SAS

SAS0-3

0

S1

J

Fan4

A. 24-pin ATX PWR

B. 8-pin Processor PWR

C. 4-pin PWR

PSF

B

7

Fan

2-14

Page 35

Chapter 2: Installation

Universal Serial Bus (USB)

There are six USB 2.0 (Universal Se-

rial Bus) ports/headers on the mother-

board. Four of them are Back Panel

USB ports (USB#0/1/2/3: JUSB1),

and the other two are Front Panel

USB headers (USB#4/5:JUSB2).

See the tables on the right for pin

defi nitions.

Chassis Intrusion

A Chassis Intrusion header is located

at JL1 on the motherboard. Attach the

appropriate cable from the chassis to

inform you of a chassis intrusion when

the chassis is opened.

Back Panel USB

(USB0/1/2/3)

Pin# Defi nitions

1 +5V

2 PO-

3PO+

4 Ground

5N/A

Front Panel USB

Pin Defi nitions (USB4)

USB4

Pin # Defi nition

USB5

Pin # Defi nition

1 +5V 1 +5V

2 PO- 2 PO-

3PO+ 3PO+

4 Ground 4 Ground

5 Key 5 No connection

Chassis Intrusion

Pin Defi nitions (JL1)

Pin# Defi nition

1 Intrusion Input

2 Ground

KB/

M

USB

1/2/3

ouse

COM1

LAN1/2

HD

Audio

/

0

Parrallel

Port

JLAN1

AN

L

G

TLR

C

5

Fan

6

Fan

A

UPER X7DA3+

S

CD1

Audio

CTRL

7

Slot

SIM LP IPMI

6

Slot

PCI-Exp x16

5

Slot

PCI-33MHz

2

2

C4

I

J

C3

I

J

4

Slot

Exp x

PCI-

JWD

3

Slot

133 M

CI-X

P

JPL2

JPL1

2

Slot

133

-X

CI

P

WOR

J

1

Slot

100 M

CI-X

P

-Pin

-Pin

4

4

2

WR

P

JPW2

D

I

MM

4B

(B

D

IMM 4

A

(B

DIMM 3B (Bank

D

IMM 3A

(B

DIMM

2B

(Bank

D

IMM 2A

(B

D

IMM

1B (Ban

D

I

MM

1

A

(B

®

4

Hz

Hz

M

2

2

C2

I

J

C1

I

J

(Green S

CR

Hz Z

A

ank

ank 4)

an

k

an

k 2

k

an

k 1

B

lot)

X PWR

T

4)

3)

3)

2)

1)

atter

C

)

)

G

North

y

JL

JPW1

reencree

Brid

1

SA

CPU

Fan 1

TA

PSF

7

Fan

J17

J3P

JAR

CPU1

k

e

g

JBT1

H

X

P

SATA4

SMB

0

1

SATA2

TA

SA

B

USB4/

SATA5

SA

2

U

CP

South

ge

rid

B

SAS

Controller

5

TA3

WOL

J

CPU

8-pin PWR

JPW3

Fan1

1

F

J

FP Control

2

Fan

SPK

PW LED

LE1

JOH1

SG

P

IO1

SG

P

IO2

Fan2

Fan3

Fan8

Flash

ct

JWF1

F1

C

J

OS

I

B

JP

IDE1

Floppy

ompa

C

ACT4-

7

AC

T

0-3

S

1

7

-

4

SAS

SAS0-3

0

S1

J

Fan4

A. Back panel USB Ports

01/2/3

B. Front Panel USB 4/5

C. Chassis Intrusion

2-15

Page 36

X7DA3+ User's Manual

G

F

E

D

H

Fan Headers

The X7DA3+ has eight chassis/system

fan headers (Fan1 to Fan8), including

two CPU Fans (Fans 7/8). (Note: Pins

1-3 of 4-pin fan headers are backward

compatible with the traditional 3-pin

fans). See the table on the right for pin

defi nitions. (The onboard fan speeds

are controlled by Thermal Manage-

ment via BIOS Hardware Monitor

in the Advanced Setting

Manufacturer Default is set to Dis-

abled to allow the fans to constantly

run at the full speed. When using

Thermal Management setting, please

use all 3-pin fans or all 4-pin fans on

the motherboard.)

. Note: The

Fan Header

Pin Defi nitions (Fan1-8)

Pin# Defi nition

1 Ground

2 +12V

3 Tachometer

4 Pulse Width Modulation

KB/

M

USB

1/2/3

ouse

COM1

Parrallel

LAN1/2

HD

Audio

0

Port

JLAN1

L

G

TLR

C

Fan

/

S

Audio

CTRL

7

Slot

AN

Slot

5

Slot

Slot

3

Slot

2

Slot

WOR

J

1

Slot

-Pin

-Pin

4

4

WR

P

D

D

JPW2

I