SUMMIT SMP9212G, SMP9212S, SMP9210G, SMP9210S, SMP9211G Datasheet

...

1

Characteristics subject to change without notice 2048 3.3 10/03/01

SMP9210, -11, -12

SUMMIT

MICROELECTRONICS, Inc.

©SUMMIT MICROELECTRONICS, Inc., 2001 • 300 Orchard City Dr., Suite 131 • Campbell, CA 95008 • Phone 408-378-6461 • FAX 408-378-6586 • www.summitmicro.com

Preliminary

!!

!!

! Two 10-Bit Nonvolatile DACs

""

""

" INL ±1LSB

""

""

" DNL ±1LSB

!!

!!

! Programmable Configuration

!!

!!

! Programmable Power On Reset Options

""

""

" Recall Full Scale Value

""

""

" Recall Zero Scale Value

""

""

" Recall Mid-Scale Value

""

""

" Recall NV Register Value

Dual 10-Bit Nonvolatile DAC

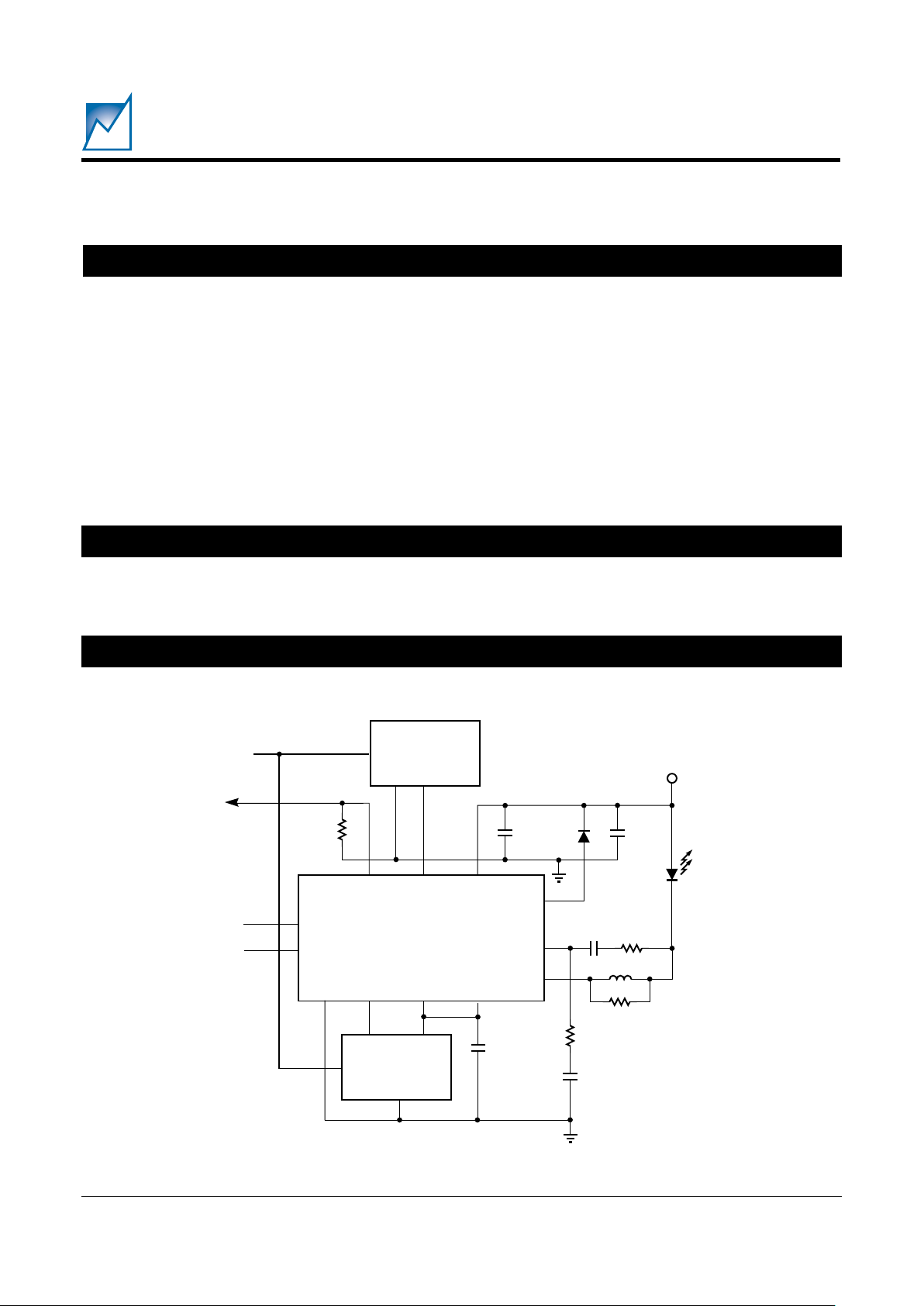

SIMPLIFIED APPLICATION DRAWING

FEATURES

C

APC

1nF

IN+

IN–

APCSET

MODMON

MD

IMOD

Laser Driver

IBIAS

GND

MODSET

BIASSET

V

CC

APC

MONITOR

DIODE

R

FILT

R

DAMP

LASER

DIODE

3.3V

SMP9210

SMP9210

VOUT1

VOUT1

VOUT2

I2C

2048 SAD

APPLICATIONS

!!

!!

! ATE Set and Forget Calibration

!!

!!

! Laser Biasing

!!

!!

! Tandem or Independent Operation of DACs

!!

!!

! Programmable Power Down Mode (Short VOUT

to GND or Float VOUT)

!!

!!

! I2C Interface

!!

!!

! Low Noise Outputs

!!

!!

! 2.7V to 5.5V Operation

!!

!!

! –40ºC to 85ºC Temperature Range

!!

!!

! RFPA Biasing

2

SMP9210, SMP9211, SMP9212

2048 3.3 10/03/01

SUMMIT MICROELECTRONICS, Inc.

Preliminary

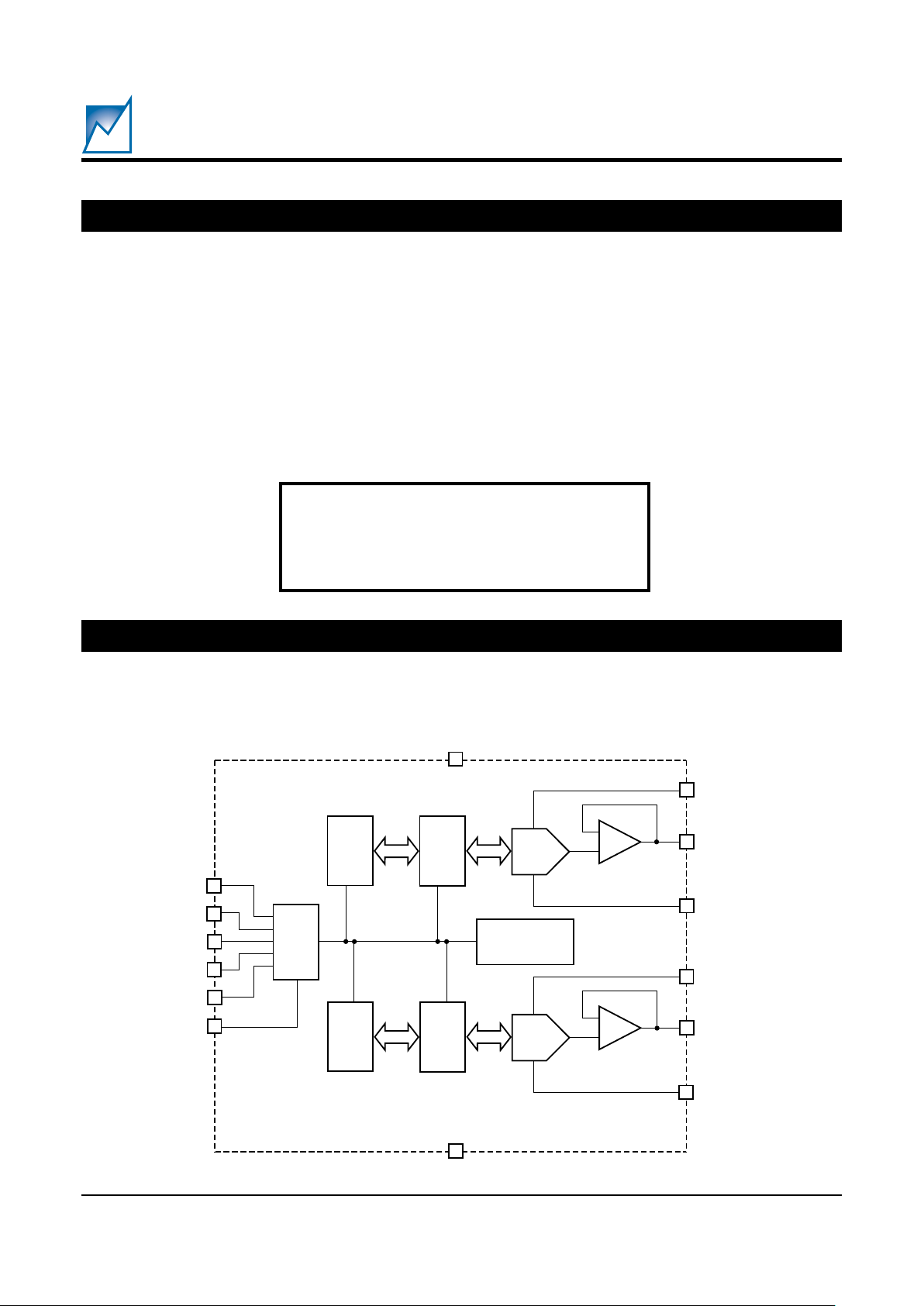

GND

V

DD

13

7

6

V

OUT

2

9

SCL

12

CS

8

2048 BD10 2.2

CONFIGURATION

REGISTER

INTERFACE

& CONTROL

LOGIC

A0

3

A1

2

A2

1

SDA

14

VOLATILE

CONTROL

REGISTER

10-BIT

DAC

NON-

VOLATILE

REGISTER

VOLATILE

CONTROL

REGISTER

10-BIT

DAC

NON-

VOLATILE

REGISTER

V

REF

H2

4

5

11

10

V

REF

H1

V

REF

L2

V

REF

L1

V

OUT

1

SMP9210

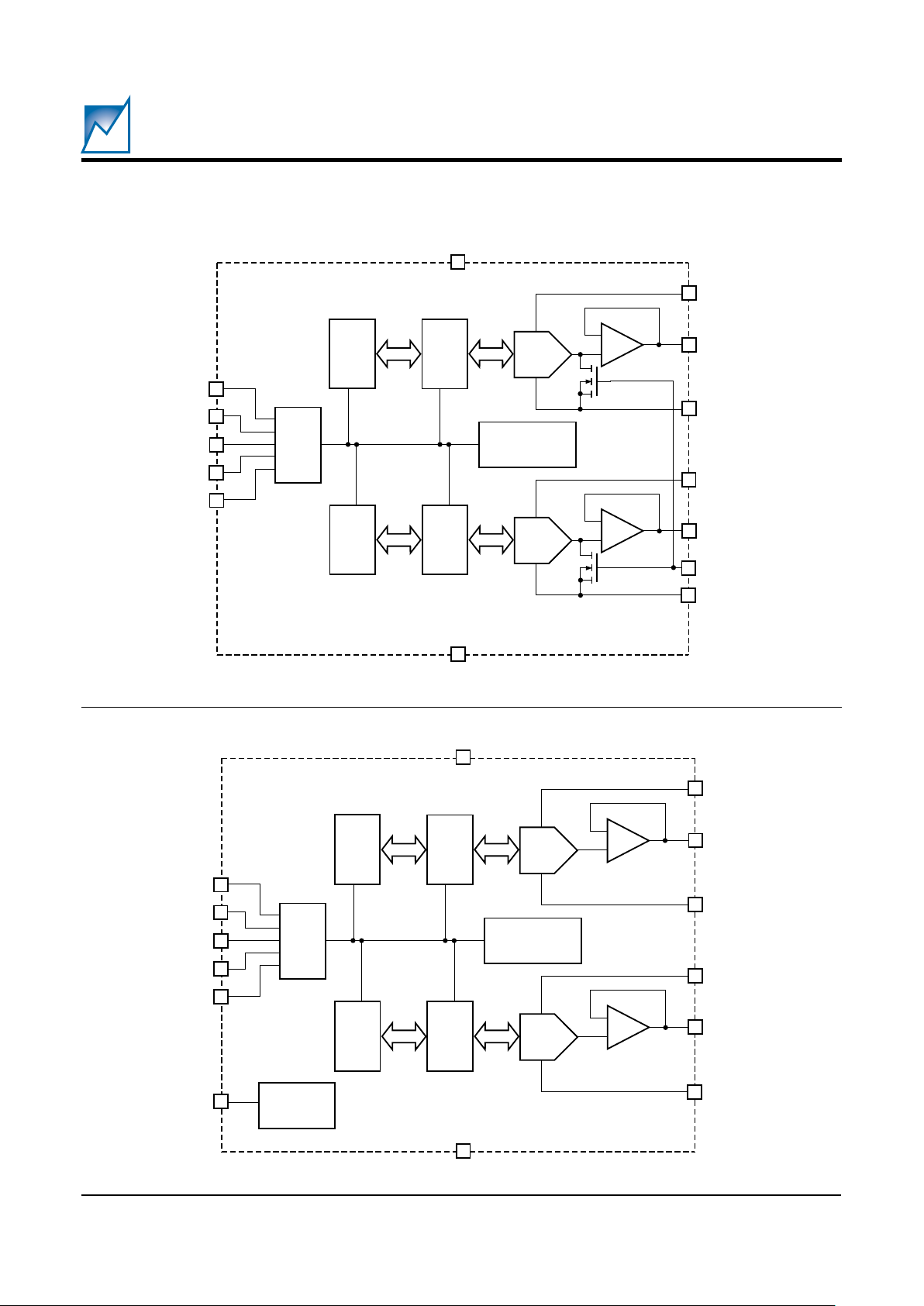

FUNCTIONAL BLOCK DIAGRAMS

Note: Pinouts for these three drawings reflect the 14 pin SOIC package.

INTRODUCTION

The SMP9210, -11, -12 trio are serial input, voltage

output, dual 10-Bit digital to analog converters. They can

operate from a single 2.7V to 5.5V supply. Internal

precision buffers swing rail-to-rail with an input reference

range from ground to the positive supply.

They integrate two 10-Bit DACs and their associated

circuits: an enhanced unity gain operational amplifier

output, a 10-Bit volatile data latch, a 10-bit nonvolatile

data register and an industry standard 2-wire serial

interface.

Programming of configuration, control and calibration

values by the user can be simplified with the interface

adapter and Windows GUI software obtainable from

Summit Microelectronics.

RECOMMENDED OPERATING CONDITIONS

Temperature –40ºC to 85ºC.

Voltage 2.7V to 5.5V

3

2048 3.3 10/03/01

SMP9210, SMP9211, SMP9212

SUMMIT MICROELECTRONICS, Inc.

Preliminary

GND

V

DD

13

7

6

V

OUT

2

9

SCL

12

2048 BD11 2.2

CONFIGURATION

REGISTER

INTERFACE

& CONTROL

LOGIC

A0

3

A1

2

A2

1

SDA

14

VOLATILE

CONTROL

REGISTER

10-BIT

DAC

NON-

VOLATILE

REGISTER

VOLATILE

CONTROL

REGISTER

10-BIT

DAC

NON-

VOLATILE

REGISTER

V

REF

H2

4

5

11

10

V

REF

H1

V

REF

L2

V

REF

L1

V

OUT

1

SMP9211

MUTE#

8

GND

V

DD

13

7

6

V

OUT

2

9

SCL

12

V

REF

8

2048 BD12 3.0

CONFIGURATION

REGISTER

INTERFACE

& CONTROL

LOGIC

A0

3

A1

2

A2

1

SDA

14

VOLATILE

CONTROL

REGISTER

10-BIT

DAC

NON-

VOLATILE

REGISTER

VOLATILE

CONTROL

REGISTER

10-BIT

DAC

NON-

VOLATILE

REGISTER

V

REF

H2

4

5

11

10

V

REF

H1

V

REF

L2

V

REF

L1

V

OUT

1

PRECISION

REFERENCE

SMP9212

4

SMP9210, SMP9211, SMP9212

2048 3.3 10/03/01

SUMMIT MICROELECTRONICS, Inc.

Preliminary

V

DD

Power supply input.

GND

Power supply return.

V

OUT1, VOUT

2

The voltage output of the DACs. It is buffered by a unitygain follower that can slew up to 1V/µs.

V

REF

L1, V

REF

L2

The lower of the voltage reference inputs. V

REF

L must be

equal to or greater than ground and less than V

REF

H.

V

REF

H1, V

REF

H2

The higher of the voltage reference inputs. V

REF

H must be

equal to or less than VCC and greater than V

REF

L.

A0, A1, A2

The address inputs for the serial interface logic. Biasing the address inputs will determine the device’s bus

address that is contained within the serial data stream

when communicating over the serial bus.

PIN DESCRIPTIONS

SCL

The serial interface clock. It is used to clock the data in and

out. When writing to the device data must remain stable

while SCL is high. When reading from the device data is

clocked out on the falling edge of SCL.

SDA

The bidirectional pin used to transfer data in and out of

the device.

CS

Chip Select input (VIH = selected) in the 9210. See the

Block Diagrams.

MUTE#

Mute input (VIL = mute) in the 9211. See the Block

Diagrams.

V

REF

V

REF

output (1.25V) in the 9212. See the Block Diagrams.

Note: NC pins are not connected.

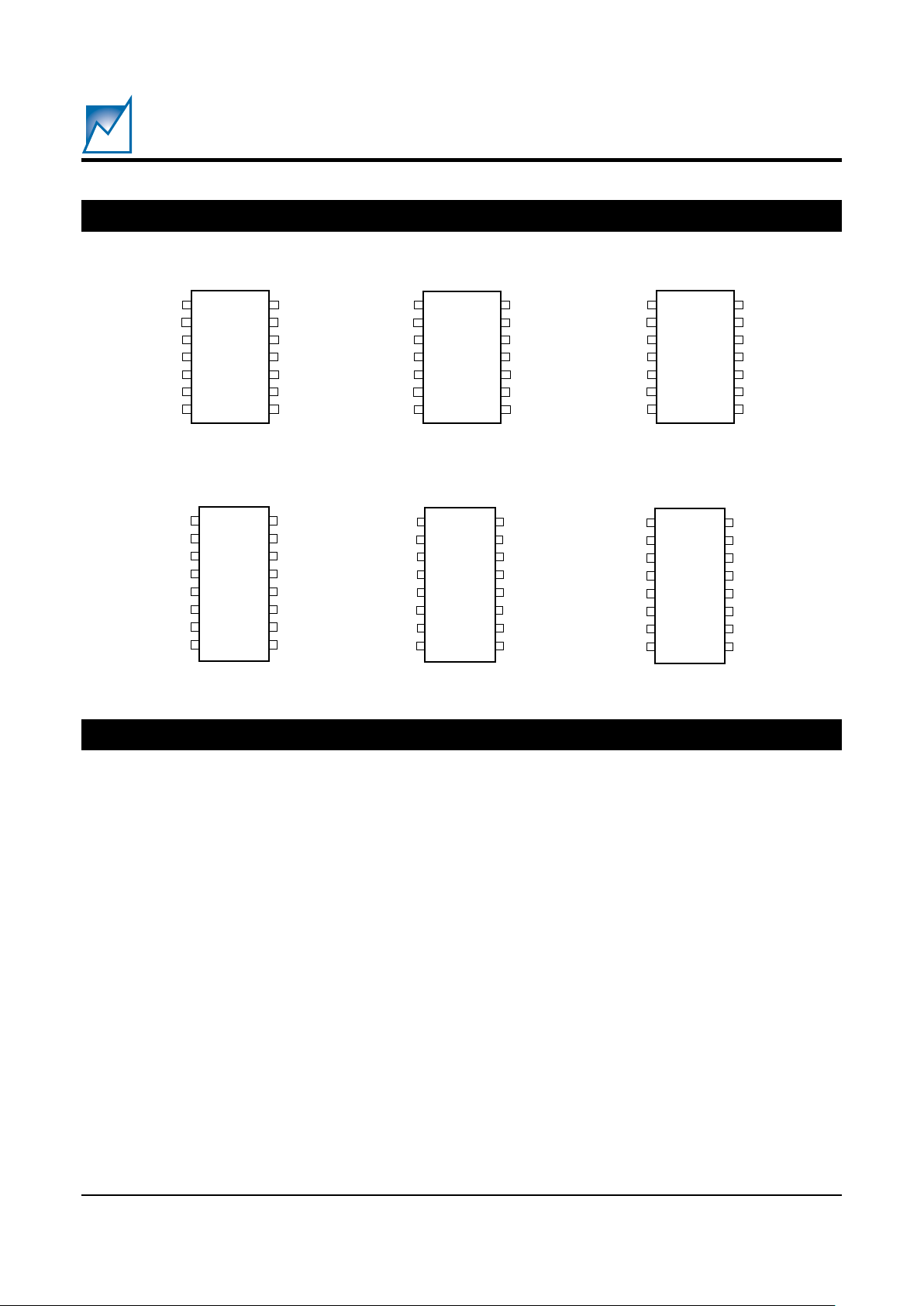

PIN CONFIGURATIONS

A2

A1

A0

V

REF

H2

V

REF

L2

V

OUT

2

GND

SDA

V

DD

SCL

V

REF

H1

V

REF

L1

V

OUT

1

MUTE#

14-Pin SOIC

2048 14-PCon

1

2

3

4

5

6

7

14

13

12

11

10

9

8

A2

A1

A0

V

REF

H2

V

REF

L2

V

OUT

2

GND

SDA

V

DD

SCL

V

REF

H1

V

REF

L1

V

OUT

1

CS

1

2

3

4

5

6

7

14

13

12

11

10

9

8

A2

A1

A0

V

REF

H2

V

REF

L2

V

OUT

2

GND

SDA

V

DD

SCL

V

REF

H1

V

REF

L1

V

OUT

1

V

REF

1

2

3

4

5

6

7

14

13

12

11

10

9

8

SMP9210

SMP9211

SMP9212

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

2048 16-PCon

16-Pin SSOP

A2

NC

A1

A0

V

REF

H2

V

REF

L2

V

OUT

2

GND

SDA

NC

V

DD

SCL

V

REF

H1

V

REF

L1

V

OUT

1

MUTE#

SMP9210

SMP9211

SMP9212

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

A2

NC

A1

A0

V

REF

H2

V

REF

L2

V

OUT

2

GND

SDA

NC

V

DD

SCL

V

REF

H1

V

REF

L1

V

OUT

1

CS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

A2

NC

A1

A0

V

REF

H2

V

REF

L2

V

OUT

2

GND

SDA

NC

V

DD

SCL

V

REF

H1

V

REF

L1

V

OUT

1

V

REF

Loading...

Loading...