SUMMIT SMH4803AS Datasheet

SUMMIT

MICROELECTRONICS, Inc.

SMH4803A

Distributed Power Hot Swap Controller

FEATURES

l Soft Starts Main Power Supply on Card Insertion

or System Power Up

l Senses Card Insertion via Short Pins or Ejector

Switches

l Master Enable to Allow System Control of Power

Up or Down

w Can be used as a Temperature Sense Input

l Programmable Independent Controls of 3 DC/DC

Converters

w Not Enabled until Host Supply Fully Soft

Started

w Programmable Time Delay Between each

Enable Signal

w Available Input to hold off Dependant Enables

until Conditions are Satisfied

l Highly Programmable Circuit Breaker

w Programmable Quick-TripTM Values

w Programmable Current Limiting

Preliminary

w Programmable Circuit Breaker Mode:

Latched (Volatile or Nonvolatile)

w Programmable Duty Cycle Times

w Programmable Over-current Filter

l Programmable Host Voltage Fault Monitoring

w Programmable Under- voltage Hysteresis

w Programmable UV/OV Voltage Filter

w Programmable Fault Mode: Latched or Duty

Cycle

l Nonvolatile Programming to Customize Features

w Available Pre-programmed from Summit

l 2.5V and 5.0V Reference Outputs

w Eliminates the Need or Other Primary Volt-

ages

w Easy Expansion of External Monitor Func-

tions

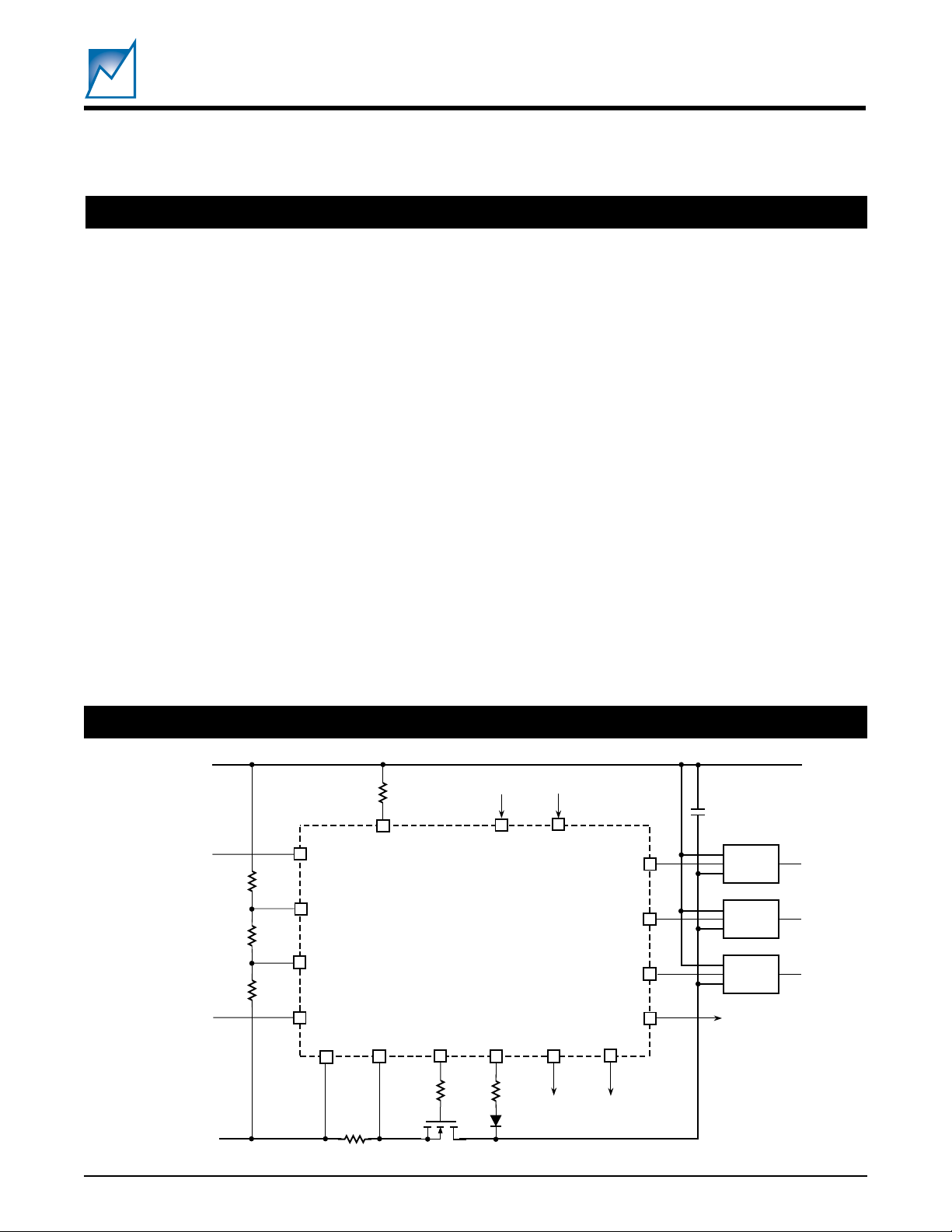

SIMPLIFIED APPLICATION DRAWING

0V

Pin Detect

Pin Detect

PD1#

R3

UV

R2

OV

R1

PD2#

VSS

VDD

CBSENSE

VGATE

l Supply Range ±20VDC to >±500VDC

Disable / Enable

ENPGA

SMH4803A

DRAIN

SENSE

ENPGB

2.5VREF

PG1#

PG2#

PG3#

FAULT#

5.0VREF

DC/DC

DC/DC

DC/DC

–48V

©SUMMIT MICROELECTRONICS, Inc., 2000 • 300 Orchard City Dr., Suite 131 • Campbell, CA 95008 • Phone 408-378-6461 • FAX 408-378-6586 • www.summitmicro.com

Characteristics subject to change without notice

2051 4.4 3/15/01

2051 SAD 1.2

1

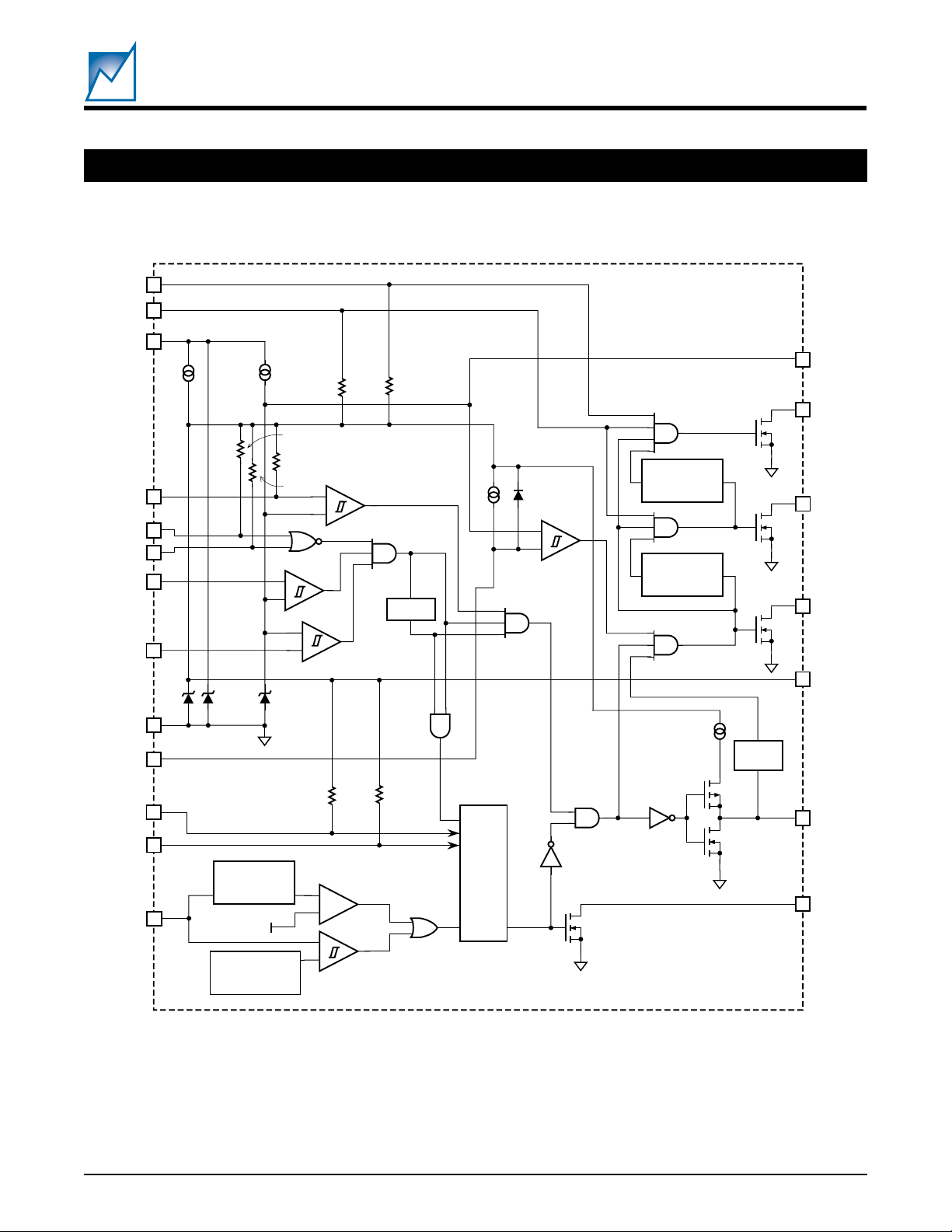

FUNCTIONAL BLOCK DIAGRAM

SMH4803A

Preliminary

ENPGB

ENPGA

VDD

EN/TS

PD1#

PD2#

UV

OV

VSS

DRAIN

SENSE

MODE

15

16

5V

12VREF

12V

2.5V

50kΩ

200kΩ

50kΩ

+

–

14

2.5VREF

50kΩ

+

–

+

–

50kΩ

50kΩ

FILTER

50kΩ

17

PG3#

PROGRAMM-

ABLE

DELAY

+

–

PROGRAMM-

ABLE

DELAY

VGATE

SENSE

19

18

13

2

PG2#

PG1#

VGATE

5.0VREF

20

3

4

5

11

12

10

1

8

RESET#

CBSENSE

2

7

PROGRAMM-

ABLE

DELAY

9

50mV

Programmable

Quick Trip

Ref. Voltage

+

–

+

–

FAULT

LATCH

AND

DUTY

CYCLE

TIMER

2051 4.4 3/15/01

6

FAULT#

2051 BD 1.3

SUMMIT MICROELECTRONICS, Inc.

SMH4803A

Preliminary

PRODUCT DESCRIPTION

The SMH4803A is an integrated solution for high reliability

systems to monitor and react to events that could have a

detrimental effect on a system. It can contain or limit faults

to a single circuit board before that fault propagates to the

system. Its programmability lets a single board satisfy

multiple circuit demands while customized to meet special

requirements.

The SMH4803A monitors and controls the primary voltage

in a distributed power system while providing for both hotswapping and secondary voltage sequencing in multisupply systems. The primary power source can be shut

down if events are sensed that could result in damage to

either the circuit board or the system supply. An external

FET switch is used to soft start the primary voltage once

normal operating conditions are met. The external FET

also uses an external shunt to monitor current for the

circuit breaker function.

The SMH4803A sequences secondary voltage by timed

or externally controlled outputs that enable DC/DC converters. Its reference voltages provide isolation between

primary and secondary voltages, but allow expansion of its

features.

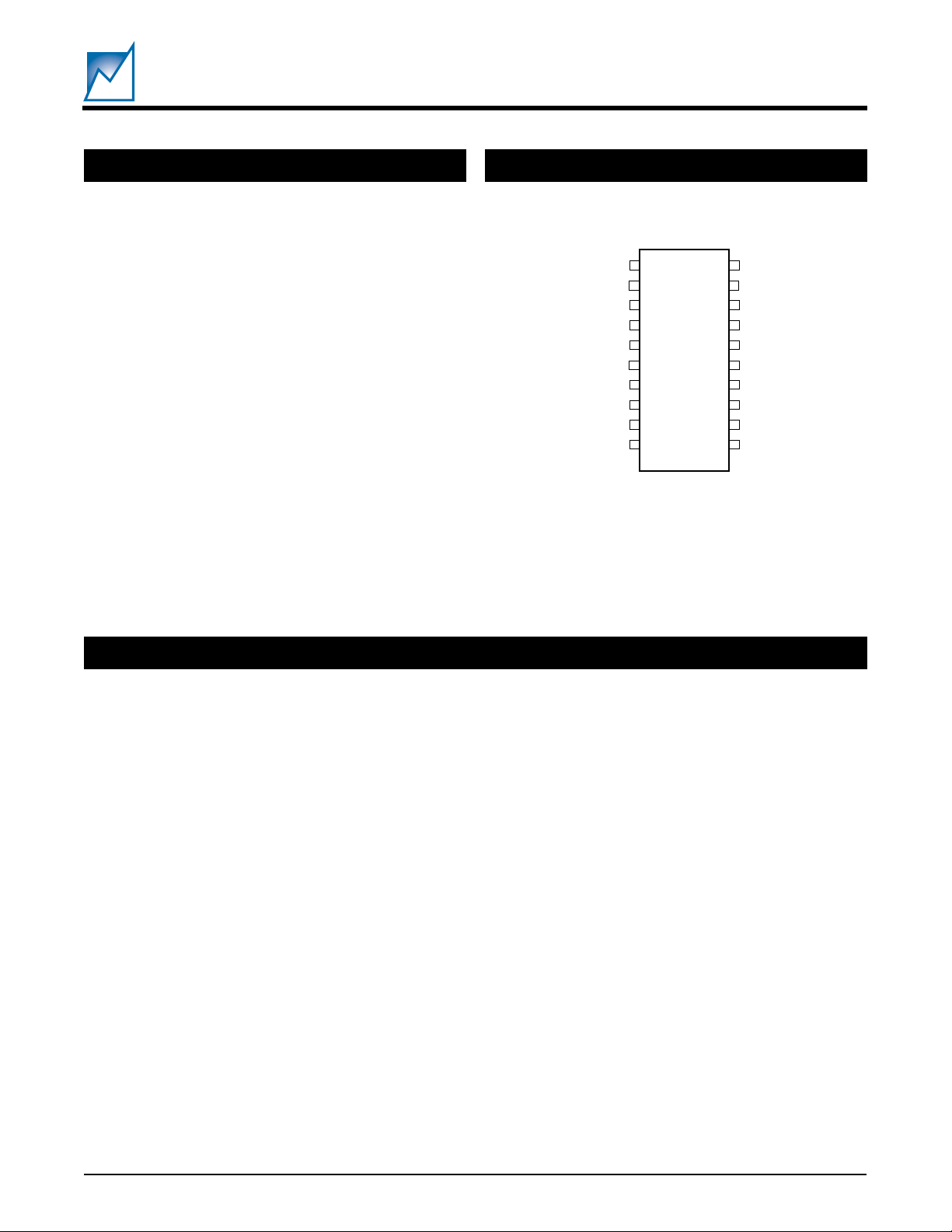

PIN CONFIGURATION

20-Pin SOIC

DRAIN SENSE

VGATE

EN/TS

PD1#

PD2#

FAULT#

RESET#

MODE

CBSENSE

V

SS

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

V

DD

PG2#

PG1#

PG3#

ENPGA

ENPGB

2.5VREF

5.0VREF

OV

UV

2051 PCon 1.0

PIN DESCRIPTIONS

DRAIN SENSE (1)

The DRAIN SENSE input monitors the voltage at the drain

of the external power MOSFET switch with respect to VSS.

An internal 10µA source pulls the DRAIN SENSE signal

towards the 5V reference level. DRAIN SENSE must be

held below 2.5V to enable the PG outputs.

VGATE (2)

The VGATE output activates an external power MOSFET

switch. This signal supplies a constant current output

(100µA typical), which allows easy adjustment of the

MOSFET turn on slew rate.

EN/TS (3)

The Enable/Temperature Sense input is the master enable input. If EN/TS is less than 2.5V, VGATE will be

disabled. This pin has an internal 200kΩ pull-up to 5V.

PD1# and PD2# (4 & 5)

These are logic level active low inputs that can optionally

be employed to enable VGATE and the PG outputs when

they are at VSS. These pins each have an internal 50kΩ

pull-up to 5V.

FAULT# (6)

This is an open-drain, active-low output that indicates the

fault status of the device.

RESET# (7)

Reset# is used to clear latched fault conditions. When this

pin is held low the VGATE and PG outputs are disabled.

Refer to the Circuit Breaker Operation and the associated

timing diagrams for detailed characteristics. This pin has

an internal 50kΩ pull-up to 5V.

MODE (8)

The state of the MODE signal determines how fault

conditions are cleared. The device is in the latched mode

when the signal is held at VSS, and the cycle mode when

held at 5V or left floating. This pin has an internal 50kΩ

pull-up to 5V.

CBSENSE (9)

The circuit breaker sense input is used to detect overcurrent conditions across an external, low value sense

resistor (RS) tied in series with the Power MOSFET. A

voltage drop of greater than 50mV across the resistor for

longer than t

will trip the circuit breaker. A program-

CBD

mable Quick-Trip™ sense point is also available.

SUMMIT MICROELECTRONICS, Inc.

2051 4.4 3/15/01

3

SMH4803A

Preliminary

UV (11)

The UV pin is used as an under-voltage supply monitor,

typically in conjunction with an external resistor ladder.

VGATE will be disabled if UV is less than 2.5V. Programmable internal hysteresis is available on the UV input,

adjustable in increments of 62.5mV. Also available is a

filter delay on the UV input.

OV (12)

The OV pin is used as an over-voltage supply monitor,

typically in conjunction with an external resistor ladder.

VGATE will be disabled if OV is greater than 2.5V. A filter

delay is available on the OV input.

5.0VREF & 2.5VREF (13 & 14)

These are precision 5V and 2.5V output reference voltages that may be use to expand the logic input functions

on the SMH4803A. The reference outputs are with respect to V

SS

.

ENPGA (16)

This is an active high input that controls the PG2# and

PG3# outputs. When ENPGA is pulled low the PG2# and

PG3# outputs are immediately placed in a high impedance

state. When ENPGA is driven high or left floating then

PG2# will be driven low at a time period of t

after PG1#

PGD

has been active. This pin has an internal 50kΩ pull-up to

5V.

ENPGB (15)

This is an active high input that controls the PG3# output.

When ENPGB is pulled low the PG3# output is immediately placed in a high impedance state. When ENPGB is

driven high or left floating then PG3# will be driven low at

a time period of t

after PG2# has been active. This pin

PGD

has an internal 50kΩ pull-up to 5V.

PG1#, PG2#, & PG3# (18, 19, & 17)

The PGn# pins are open-drain, active-low outputs with no

internal pull-up resistor. They can be used to switch a load

or enable a DC/DC converter. PG1# is enabled immediately after VGATE reaches VDD – VGT and the DRAIN

SENSE voltage is less than 2.5V. Each successive PG

output is enabled t

after its predecessor, provided also

PGD

that the appropriate ENPG input(s) are high. Voltage on

these pins cannot exceed 12V, as referenced to V

SS.

VDD (20)

VDD is the positive supply connection. An internal shunt

regulator limits the voltage on this pin to approximately

12V with respect to VSS. A resistor must be placed in

series with the VDD pin to limit the regulator current (RD in

the application illustrations).

VSS (10)

VSS is connected to the negative side of the supply.

RECOMMENDED OPERATING CONDITIONS

Temperature –40°C to 85°C.

ABSOLUTE MAXIMUM RATINGS*

Temperature Under Bias ...................... –55°C to 125°C

Storage Temperature ........................... –65°C to 150°C

Lead Solder Temperature (10s)........................... 300°C

Terminal Voltage with Respect to VSS:

VGATE ......................................... VDD + 0.5V

UV, OV, CBSENSE, DRAIN SENSE,

FAULT#, PG1#, PG2#,

and PG3# ...................... –0.5V to VDD + 0.5V

4

2051 4.4 3/15/01

PD1#, PD2#, MODE, RESET#,

ENPGA, ENPGB, EN/TS ......................... 10V

*Comment

Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions

outside those listed in the operational sections of this specification is not

implied. Exposure to any absolute maximum rating for extended

periods may affect device performance and reliability.

SUMMIT MICROELECTRONICS, Inc.

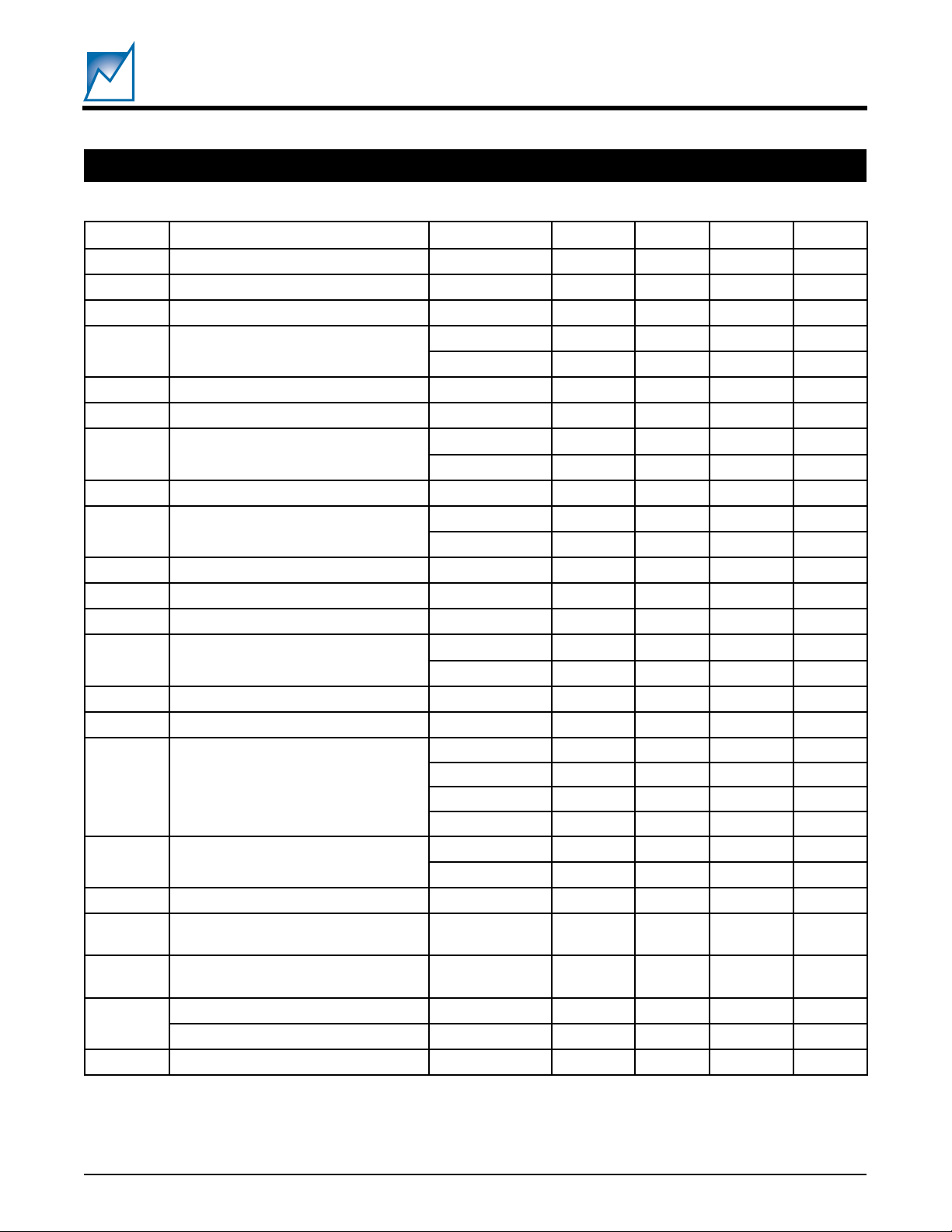

DC OPERATING CHARACTERISTICS

(Over Recommended Operating Conditions; Voltages are relative to VSS, except VGT)

lobmySretemaraPsnoitidnoC.niM.pyT.xaMstinU

V

DD

FERV0.5tuptuoecnereferV5I

I

5DAOL

FERV5.2tuptuoecnereferV5.2

I

5.2DAOL

I

DD

V

VU

V

TSYHVU

V

VO

V

TSYHVO

V

ETAGV

I

ETAGV

V

ESNES

I

ESNES

V

BC

V

BCQ

V

STNE

V

V

V

V

V

(1) TA = 25°C.

TSYHSTNE

HI

LI

LO

TG

egatlovylppuSI

tnerructuptuoecnereferV5I

I

I

tnerructuptuoecnereferV5.2I

tnerrucylppusrewoPdelbanetuptuO2 01Am

I

dlohserhtegatloV-rednU

I

siseretsyhegatloV-rednUI

I

dlohserhtegatloV-revO

I

siseretsyhegatloV-revOI

egatlovtuptuoETAGV V

tuptuotnerrucETAGV001Aµ

I

dlohserhtESNESNIARD

I

tuptuotnerrucESNESNIARDV

dlohserhtrekaerbtiucriCI

tiucricpirTkciuQelbammargorP

dlohserhtrekaerb

I

dlohserhtST/NE

I

siseretsyhST/NEI

,B/AGPNE:egatlovhgihtupnI

#TESER,EDOM

,B/AGPNE:egatlovwoltupnI

#TESER,EDOM

#TLUAF:egatlovwoltuptuOI

#3/#2/#1GP:egatlovwoltuptuOI

dlohserhtetaG7.08.10.3V

Am3=112131V

DD

Am3=57.400.552.5V

DD

Am3=1– 1Am

DD

Am3=)1(574.2005.2525.2V

DD

Am3=524.2005.2575.2V

DD

Am3=2.0– 1Am

DD

Am3=)1(574.2005.2525.2V

DD

Am3=524.2005.2575.2V

DD

Am3=01Vm

DD

Am3=)1(574.2005.2525.2V

DD

Am3=524.2005.2575.2V

DD

Am3=01Vm

DD

Am3=)1(574.2005.2525.2V

DD

Am3=524.2005.2575.2V

DD

V=

ESNES

DD

)1(9 0111Aµ

SS

Am3=040506Vm

002Vm

001Vm

06Vm

ffO —

Am3=)1(574.2005.2525.2V

DD

Am3=524.2005.2575.2V

DD

Am3=01Vm

DD

2FERV0.5V

1.0– 8.0V

Am2=0 4.0V

LO

Am2=0 4.0V

KNIS

SMH4803A

Preliminary

DD

V

2051 Elect Table 2.2

SUMMIT MICROELECTRONICS, Inc.

2051 4.4 3/15/01

5

FUNCTIONAL DESCRIPTION

SMH4803A

Preliminary

GENERAL OPERATION

The SMH4803A is an integrated power controller for hot

swappable add-in cards. The device operates from a wide

supply range and generates the signals necessary to drive

isolated output DC/DC converters. As a typical add-in

board is inserted into the powered backplane physical

connections must first be made with the chassis to discharge any electrostatic voltage potentials. The board

then contacts the long pins on the backplane that provide

power and ground. As soon as power is applied the device

starts up, but does not immediately apply power to the

output load. Under-voltage and over-voltage circuits

inside the controller check to see that the input voltage is

within a user-specified range, and pin detection signals

determine whether the card is seated properly.

These requirements must be met for a Pin Detect Delay

period of t

, after which time the hot-swap controller

PDD

enables VGATE to turn on the external power MOSFET

switch. The VGATE output is current limited to I

VGATE

allowing the slew rate to be easily modified using external

passive components. During the controlled turn-on period

the VDS of the MOSFET is monitored by the drain sense

input. When drain sense drops below 2.5V, and VGATE

gets above VDD – VGT, the power good outputs can begin

turning on the DC/DC controllers. Power Good Enable

inputs may be used to activate or deactivate specific

output loads.

Steady state operation is maintained as long as all conditions are normal. Any of the following events may cause

the device to disable the DC/DC controllers by shutting

down the power MOSFET: an under-voltage or overvoltage condition on the host power supply; an overcurrent event detected on the CBSENSE input; a failure of

the power MOSFET sensed via the DRAIN SENSE pin;

the pin detect signals becoming invalid; or the master

enable (EN/TS) falling below 2.5V. The SMH4803A may

be configured so that after any of these events occur the

VGATE output shuts off and either latches into an off state

or recycles power after a cooling down period, t

Powering V

DD

CYC

.

The SMH4803A contains a shunt regulator on the VDD pin

that prevents the voltage from exceeding 12V. It is

necessary to use a dropper resistor (RD) between the host

power supply and the VDD pin in order to limit current into

the device and prevent possible damage. The dropper

resistor allows the device to operate across a wide range

of system supply voltages, and also helps protect the

device against common-mode power surges. Refer to the

Applications Section for help on calculating the RD resistance value.

6

2051 4.4 3/15/01

System Enables

There are several enabling inputs, which allow a host

system to control the SMH4803A. The Pin Detect pins

(PD1# & PD2#) are two active low enables that are

generally used to indicate that the add-in circuit card is

properly seated. This is typically done by clamping the

inputs to VSS through the implementation of an injector

switch, or alternatively through the use of a staggered pins

at the card-cage interface. Two shorter pins arrayed at

opposite ends of the connector force the card to be fully

seated (not canted) before both pin detects are enabled.

Care must be taken not to exceed the maximum voltage

rating of these pins during the insertion process. Refer to

details in the Applications Section for proper circuit implementation.

The EN/TS input provides an active high comparator input

that may be used as a master enable or temperature

sense input. These inputs must be held low for a period of

t

before a power-up sequence may be initiated.

PDD

,

Under-/Over-Voltage Sensing

The Under-Voltage (UV) and Over-Voltage (OV) inputs

provide a set of comparators that act in conjunction with an

external resistive divider ladder to sense when the host

supply voltage exceeds the user defined limits. If the input

to the UV pin rises above 2.5V, or the input to the OV pin

falls below 2.5V for a period of t

quence may be initiated. The t

, the power-up se-

PDD

filter helps prevent

PDD

spurious start-up sequences while the card is being inserted. If UV falls below 2.5V or OV rises above 2.5V, the

PG and VGATE outputs will be shut down immediately.

Under-/Over-Voltage Filtering

The SMH4803A may also be configured so that an out of

tolerance condition on UV/OV will not shut off the output

immediately. Instead, a filter delay may be inserted so that

only sustained under-voltage or over-voltage conditions

will shut off the output. When the UV/OV filter option is

enabled an out of tolerance condition on UV/OV for longer

than the filter delay time, t

, activates the FAULT#

UOFLTR

output, and the VGATE and PG outputs will be latched in

the off state. To initiate another power-up sequence the

FAULT# output must first be reset. Refer to the appropriate section on resetting the FAULT# output. The Under/Over-Voltage Filtering feature is disabled in the default

configuration of the device.

Under-Voltage Hysteresis

The Under-Voltage comparator input may be configured

with a programmable level of hysteresis. The compare

SUMMIT MICROELECTRONICS, Inc.

Loading...

Loading...