SUMMIT S93VP662S-2.7TE13, S93VP662S-2.7TE7, S93VP662S-ATE13, S93VP662S-ATE7, S93VP662S-BTE13 Datasheet

...

SUMMIT MICROELECTRONICS, Inc. • 300 Orchard City Drive, Suite 131 • Campbell, CA 95008 • Telephone 408-378-6461 • Fax 408-378-6586 • www.summitmicro.com

1

S93VP662/S93VP663

© SUMMIT MICROELECTRONICS, Inc. 1998

2019 1.1 5/15/98

Characteristics subject to change without notice

SUMMIT

MICROELECTRONICS, Inc.

FEATURES

• Voltage Protection™

• Precision Low-VCC Write Lockout

• All Write Operations Inhibited When VCC Falls

below V

LOCK

• One 3Volt and Two 5Volt System Versions

–V

LOCK

= 2.6V+.1V/-.05V

–V

LOCK

= 4.25V +.25V/-0.0V

–V

LOCK

= 4.50 +.25V/-0.0V

• 100% Compatible with Industry Standard

Microwire Devices

• 1,000,000 Program/Erase Cycles

• 100 Year Data Retention

• Commercial Industrial Temperature Range

OVERVIEW

The S93VP662 and S93VP663 are 4K-bit serial

E2PROM memories integrated with a precision V

CC

sense circuit. The sense circuit will disable write operations whenever VCC falls below the V

LOCK

voltage. They

are fabricated using SUMMIT’s advanced CMOS

E2PROM technology and is suitable for both 3 and 5 volt

systems.

Both devices have 4k-bits of E2PROM memory that is

accessible via the industry standard microwire bus. The

S93VP662 is configured with an internal ORG pin tied

low providing an 8-bit byte organization and the

S93VP663 is configured with an internal ORG pin tied

high providing a 16-bit word organization. Both the

S93VP662 and S93VP663 have page write capability.

The devices are designed for a minimum 1,000,000

program/erase cycles and have data retention in excess of 100 years.

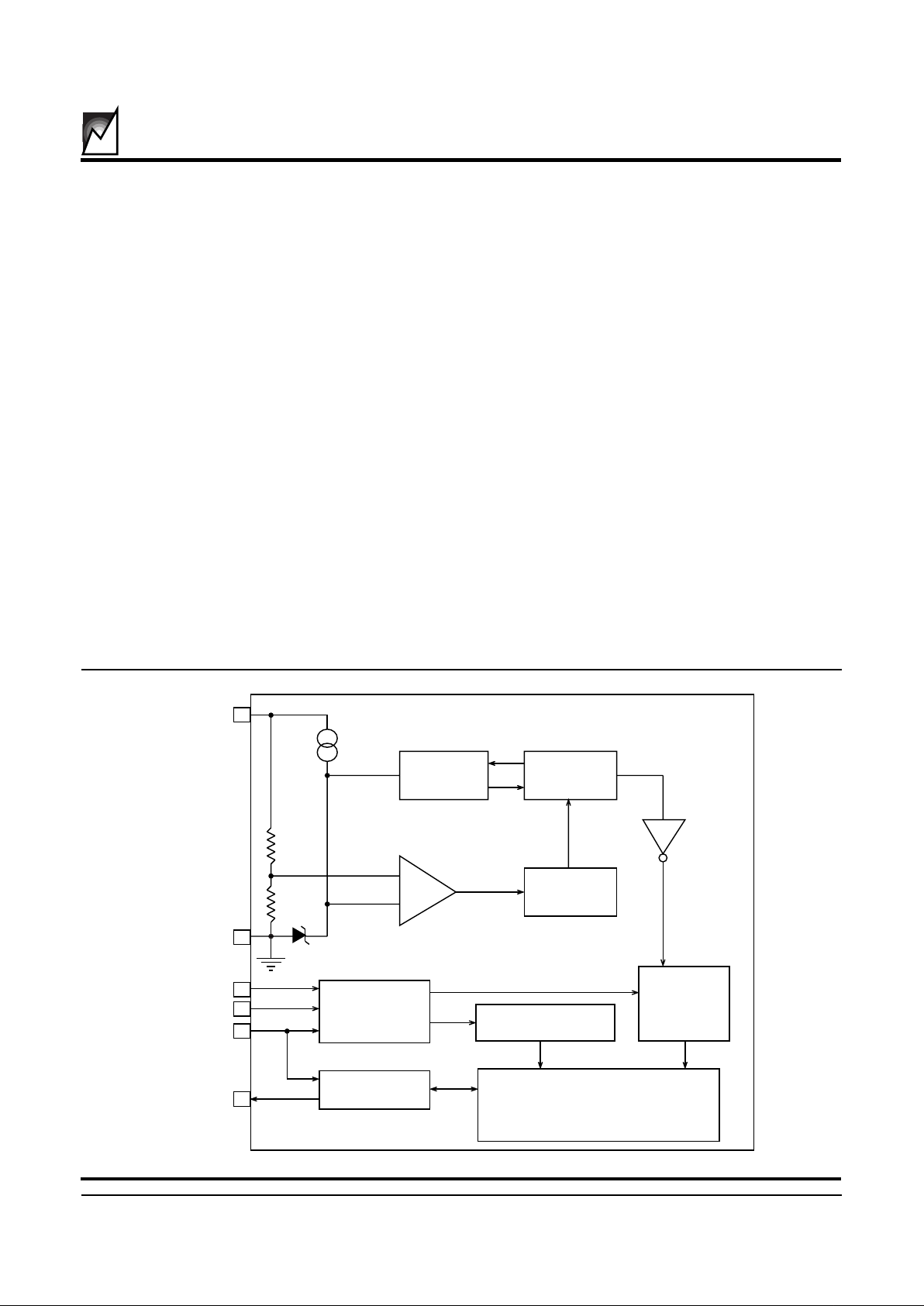

BLOCK DIAGRAM

4K Serial E2PROM with a Precision Low-VCC Lockout Circuit

+

-

8

CS

DI

DO

SK

1

2

3

4

5GND

2019 ILL2 1.0

MEMORY

ARRAY

4K-Bit

E2PROM

WRITE

CONTROL

ADDRESS

DECODER

MODE

DECODE

DATA I/O

RESET

CONTROL

RESET

PULSE

GENERATOR

5KHz

Oscillator

V

TRIP

1.26V

V

CC

2

S93VP662/S93VP663

2019 1.1 5/15/98

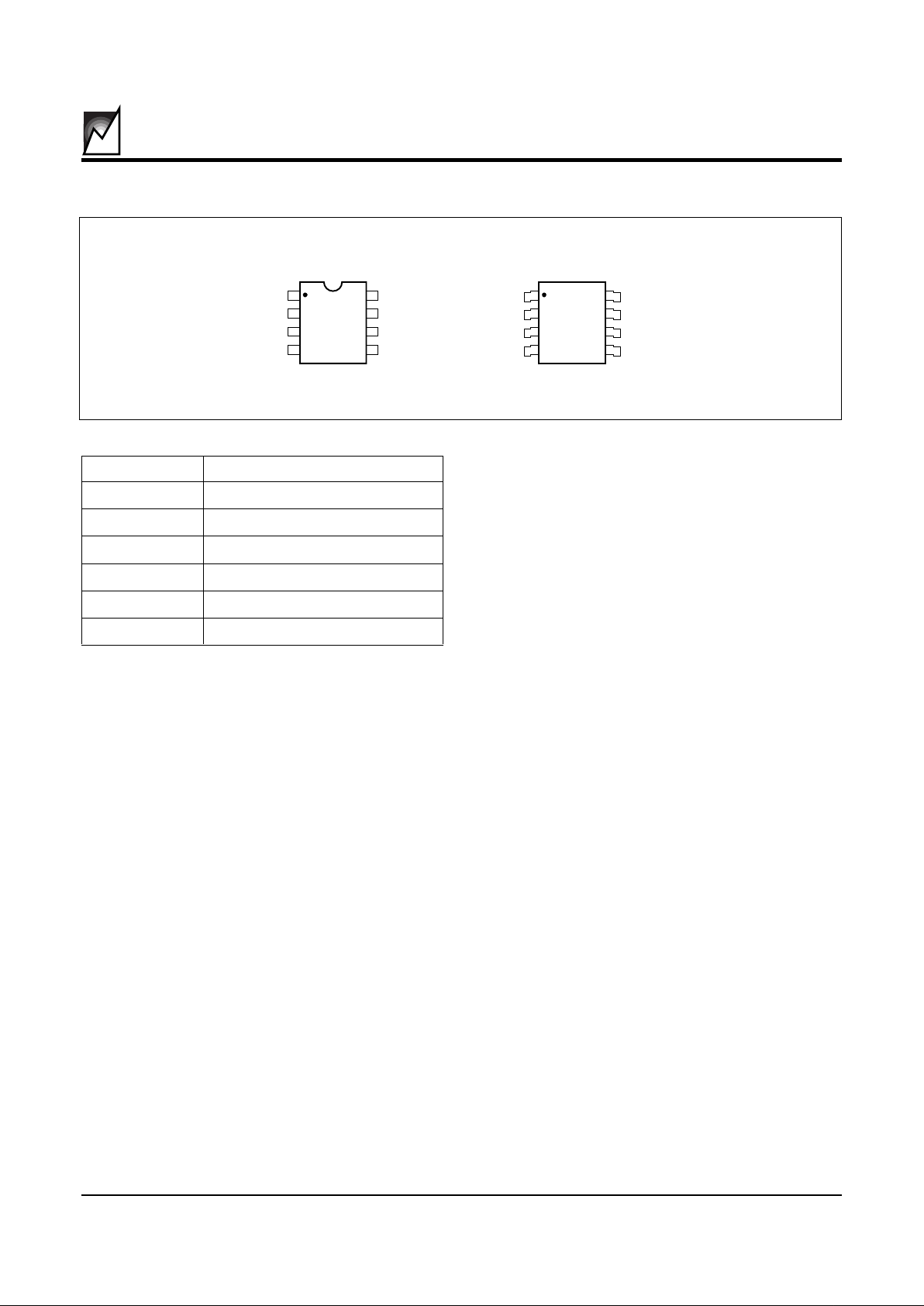

PIN FUNCTIONS

Pin Name Function

CS Chip Select

SK Clock Input

DI Serial Data Input

DO Serial Data Output

V

CC

+2.7 to 6.0V Power Supply

GND Ground

PIN CONFIGURATION

DIP Package (P)

SOIC Package (S)

DEVICE OPERATION

APPLICATIONS

The S93VP662/VP663 was designed specifically for

applications where the integrity of the stored data is

paramount. In recent years, as the operating voltage

range of serial E2PROMs has widened, most semiconductor manufacturers have arbitrarily eliminated their

V

CC

sense circuits. The S93VP662/VP663 will protect

your data by guaranteeing write lockout below the selected VCC Lockout voltage.

VCC Lockout

The S93VP662/VP663 has an on-board precision V

CC

sense circuit. Whenever VCC is below V

LOCK

, the

S93VP662/VP663 will disable the internal write circuitry.

The VCC lockout circuit will ensure a higher level of data

integrity than can be expected from industry standard

devices that have either a very loose specification or no

VCC lockout specification.

During a power-on sequence all writes will be inhibited

below the V

LOCK

level and will continue to be held in a

write inhibit state for approximately 200ms after V

CC

reaches, then stays at or above V

LOCK

. The 200ms delay

provides a buffer space for the microcontroller to complete its power-on initialization routines (reading is OK)

while still protecting against inadvertent writes.

During a power-down sequence initiation of writes will

be inhibited whenever VCC falls below V

LOCK

. This will

guard against the system’s microcontroller performing

an inadvertent write within the ‘danger zone’. (see

AN003)

GENERAL OPERATION

The S93VP662/VP663 is a 4096-bit nonvolatile memory

intended for use with industry standard microprocessors. The S93VP663 is organized as X16, seven 11-bit

instructions control the reading, writing and erase

operations of the device. The S93VP662 is organized as

X8, seven 12-bit instructions control the reading, writing

and erase operations of the device. The device operates

on a single 3V or 5V supply and will generate on chip, the

high voltage required during any write operation.

Instructions, addresses, and write data are clocked into

the DI pin on the rising edge of the clock (SK). The DO

pin is normally in a high impedance state except when

reading data from the device, or when checking the

ready/busy status after a write operation.

The ready/busy status can be determined after the start

of a write operation by selecting the device (CS high) and

polling the DO pin; DO low indicates that the write

operation is not completed, while DO high indicates that

the device is ready for the next instruction. If necessary,

the DO pin may be placed back into a high impedance

2019 ILL1 1.0

CS

SK

DI

DO

V

CC

NC

NC

GND

1

2

3

4

8

7

6

5

CS

SK

DI

DO

V

CC

NC

NC

GND

1

2

3

4

8

7

6

5

3

S93VP662/S93VP663

2019 1.1 5/15/98

state during chip select by shifting a dummy “1” into the

DI pin. The DO pin will enter the high impedance state

on the falling edge of the clock (SK). Placing the DO pin

into the high impedance state is recommended in applications where the DI pin and the DO pin are to be tied

together to form a common DI/O pin.

The format for all instructions is: one start bit; two op

code bits and either eight (x16) or nine (x8) address/

instruction bits.

Read

Upon receiving a READ command and an address

(clocked into the DI pin), the DO pin of the S93VP662/

VP663 will come out of the high impedance state and,

will first output an initial dummy zero bit, then begin

shifting out the data addressed (MSB first). The output

data bits will toggle on the rising edge of the SK clock

and are stable after the specified time delay (t

PD0

or

t

PD1

).

Write

After receiving a WRITE command, address and the

data, the CS (Chip Select) pin must be deselected for a

minimum of 250ns (t

CSMIN

). The falling edge of CS will

start automatic erase and write cycle to the memory

location specified in the instruction. The ready/busy

status of the S93VP662/VP663 can be determined by

selecting the device and polling the DO pin.

Erase

Upon receiving an ERASE command and address, the

CS (Chip Select) pin must be deslected for a minimum

of 250ns (t

CSMIN

). The falling edge of CS will start the

auto erase cycle of the selected memory location. The

ready/busy status of the S93VP662/VP663 can be

determined by selecting the device and polling the DO

pin. Once cleared, the content of a cleared location

returns to a logical “1” state.

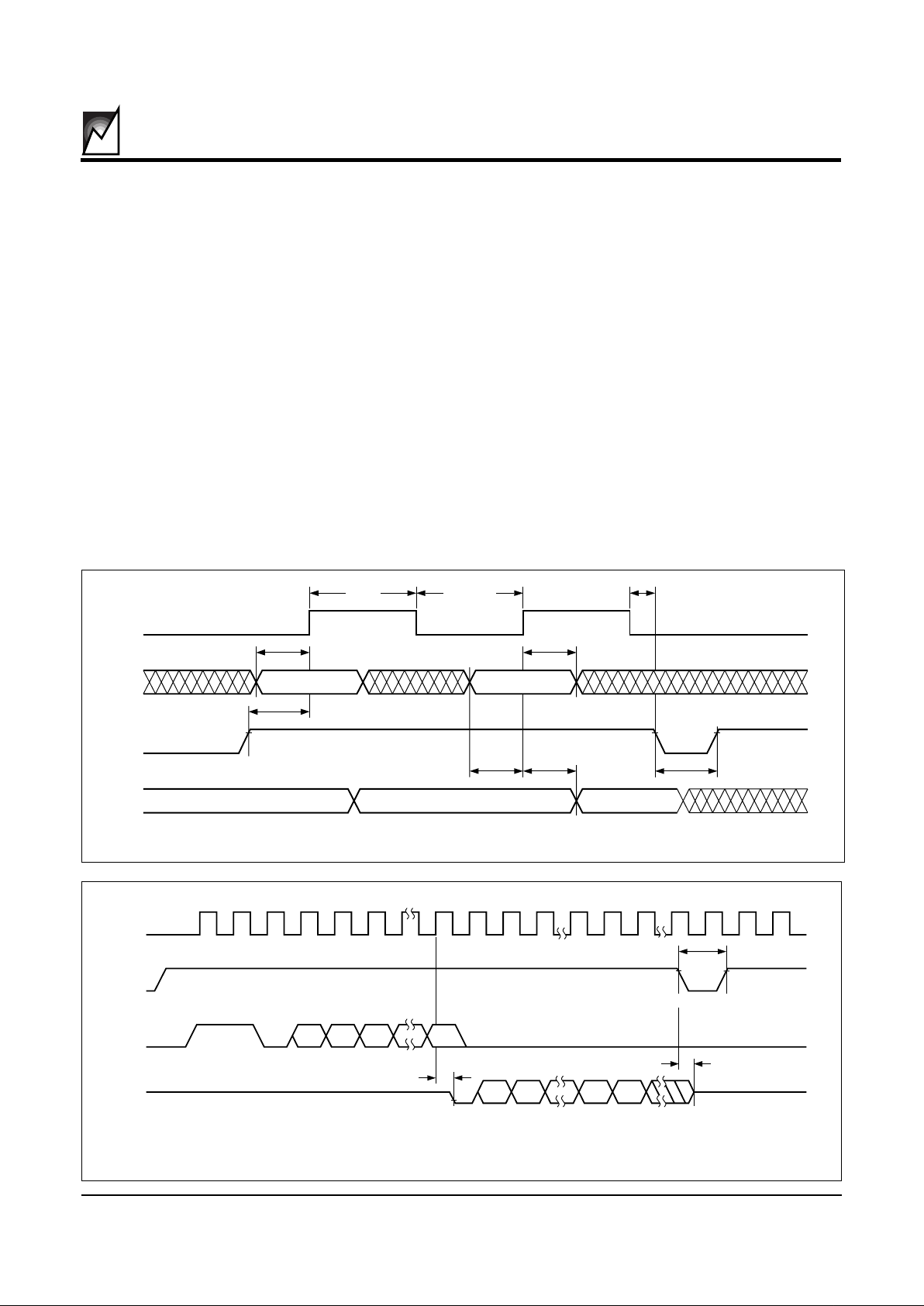

Figure 1. Sychronous Data Timing

Figure 2. Read Instruction Timing

SK

2019 ILL 3 1.0

DI

CS

DO

t

DIS

t

PD0,tPD1

t

CSMIN

t

CSS

t

DIS

t

DIH

t

SKHI

t

CSH

VALID VALID

DATA VALID

t

SKLOW

SK

2019 ILL4 1.0

CS

DI

DO

t

CS

STANDBY

t

HZ

HIGH-ZHIGH-Z

11 0

ANA

N–1

A

0

0

DND

N–1

D1D

0

t

PD0

4

S93VP662/S93VP663

2019 1.1 5/15/98

Erase/Write Enable and Disable

The S93VP662/VP663 powers up in the write disable

state. Any writing after power-up or after an EWDS

(write disable) instruction must first be preceded by the

EWEN (write enable) instruction. Once the write instruction is enabled, it will remain enabled until power to

the device is removed, or the EWDS instruction is sent.

The EWDS instruction can be used to disable all

S93VP662/VP663 write and clear instructions, and will

prevent any accidental writing or clearing of the device.

Data can be read normally from the device regardless

of the write enable/disable status.

Erase All

Upon receiving an ERAL command, the CS (Chip

Select) pin must be deselected for a minimum of 250ns

(t

CSMIN

). The falling edge of CS will start the self clocking

clear cycle of all memory locations in the device. The

clocking of the SK pin is not necessary after the device

has entered the self clocking mode. The ready/busy

status of the S93VP662/VP663 can be determined by

selecting the device and polling the DO pin. Once

cleared, the contents of all memory bits return to a

logical “1” state.

Write All

Upon receiving a WRAL command and data, the CS

(Chip Select) pin must be deselected for a minimum of

250ns (t

CSMIN

). The falling edge of CS will start the self

clocking data write to all memory locations in the device.

The clocking of the SK pin is not necessary after the

device has entered the self clocking mode. The ready/

busy status of the S93VP662/VP663 can be determined

by selecting the device and polling the DO pin. It is not

necessary for all memory locations to be cleared before

the WRAL command is executed.

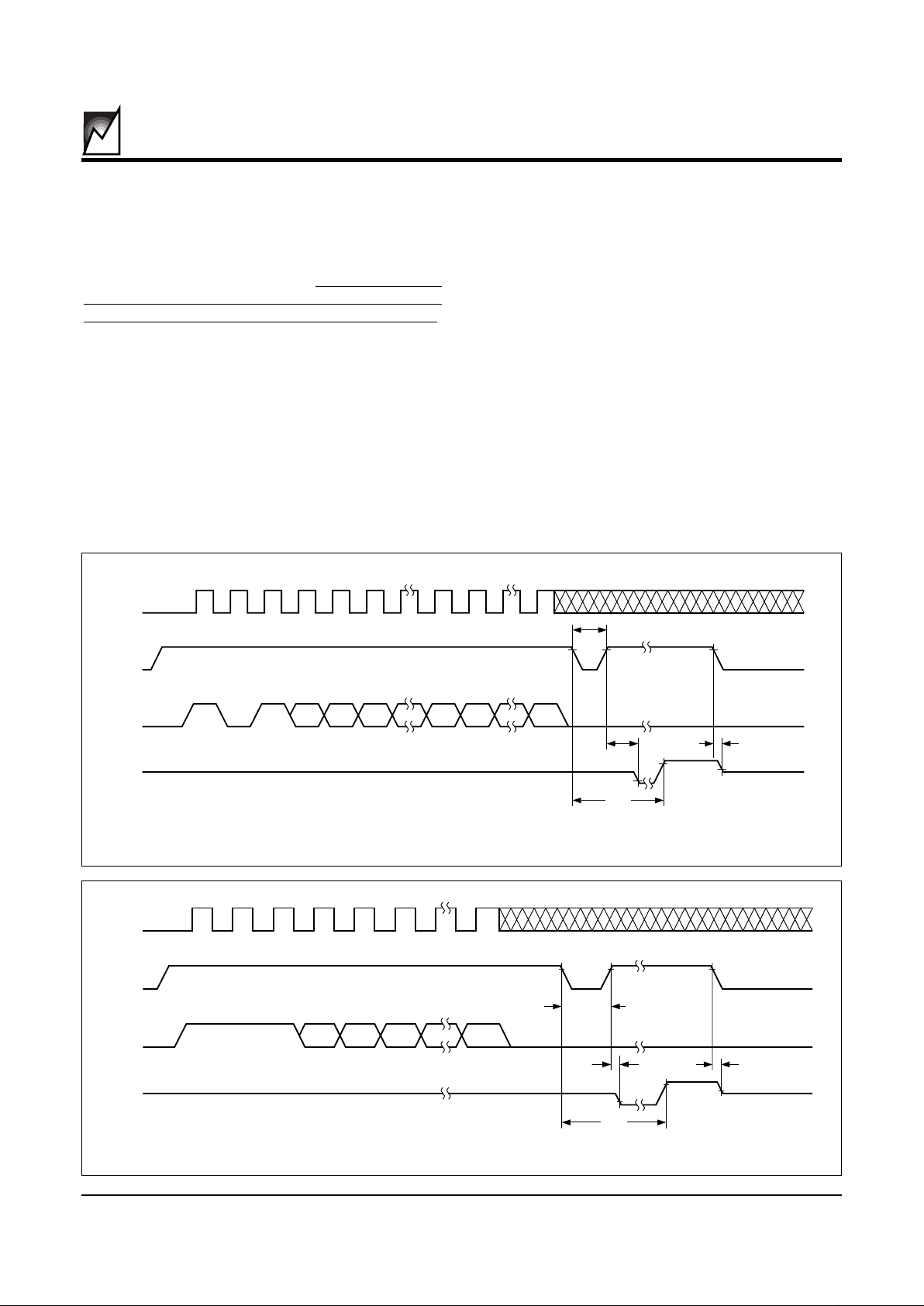

Figure 3. Write Instruction Timing

Figure 4. Erase Instruction Timing

SK

2019 ILL 5 1.0

CS

DI

DO

t

CS

STANDBY

HIGH-Z

HIGH-Z

101

A

N

A

N-1

A

0

D

N

D

0

BUSY

READY

STATUS

VERIFY

t

SV

t

HZ

t

EW

SK

2019 ILL6 1.0

CS

DI

DO

STANDBY

HIGH-Z

HIGH-Z

1

A

N

A

N-1

BUSY READY

STATUS VERIFY

t

SV

t

HZ

t

EW

t

CS

11

A

0

Loading...

Loading...