Page 1

FEAT URES SUM MARY

■ PRECISION V

– STM706/708

T: 3.00V ≤ V

S: 2.88V ≤ V

R; STM706P: 2.59V ≤ V

■ RST AND RST OUTPUTS

■ 200ms (TYP) t

■ WATCHDOG TIMER - 1.6sec (TYP)

■ MANUAL RESET INPUT (MR)

■ POWER-FAIL COMPARATOR (PFI/PFO)

■ LOW SUPPLY CURRENT - 40µA (TYP)

■ GUARANTEED RST (RST) ASSERTION

DOWN TO V

■ OPERATING TEMPERAT UR E:

–40°C to 85°C (Industrial Grade)

MONITO R

CC

RST

RST

rec

= 1.0V

CC

≤ 3.15V

≤ 3.00V

RST

≤ 2.70V

STM706, STM706P, STM708

3V Supervisor

Figure 1. Packages

8

1

SO8 (M)

TSSOP8 3x3 (DS)

Table 1. Device Options

Watchdog

Input

STM706 ✔✔✔ ✔✔

STM706P

STM708 ✔✔✔✔

Note: 1. Push-Pull Output

(2)

2. The STM706P is identical to the STM706R, except its res et output is act i ve-high.

✔✔ ✔✔✔

Watchdog

Output

Active-Low

(1)

RST

Active-High

(1)

RST

Manual

Reset Input

Power-fail

Comparator

1/25July 2004

Page 2

STM706/706P/708

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 1. Device Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 2. Logic Diagram (STM706/706P). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. Logic Diagram (STM708). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 2. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 4. STM706/706P SO8 Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 5. STM706/706P TSSOP8 Connec tions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 6. STM708 SO8 Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 7. STM708 TSSOP8 Connection s. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 3. Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 8. Block Diagram (STM706/706P). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 9. Block Diagram (STM708) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Figure 10.Hardware Hookup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Reset Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Push-button Reset Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Watchdog Input (STM706/706P) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Watchdog Output (STM706/706P) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Power-fail Input/Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Ensuring a Valid Reset Output Down to V

= 0V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

CC

Figure 11.Reset Output Valid to Ground Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Interfacing to Microprocessors with Bi-directional Reset Pins . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 12.Interfacing to Microprocessors with Bi-directional Reset I/O. . . . . . . . . . . . . . . . . . . . . . . 9

TYPICAL OPERATING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 13.Supply Current vs. Temperature (no load) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 14.V

Threshold vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

PFI

Figure 15.Reset Comparator Propagation Delay vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 16.Power-up t

vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

rec

Figure 17.Normalized Reset Threshold vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Figure 18.Watchdog Time-out Period vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 19.PFI to PFO

Figure 20.RST

Output Voltage vs. Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Propagation Delay vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 21.RST Output Voltage vs. Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 22.RST

Response Time (Assertion). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 23.RST Response Time (Assertion) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 24.Power-fail Comparator Response Time (Assertion) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 25.Power-fail Comparator Response Time (De-Assertion) . . . . . . . . . . . . . . . . . . . . . . . . .15

Figure 26.V

to Reset Propagation Delay vs. Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

CC

2/25

Page 3

STM706/706P/708

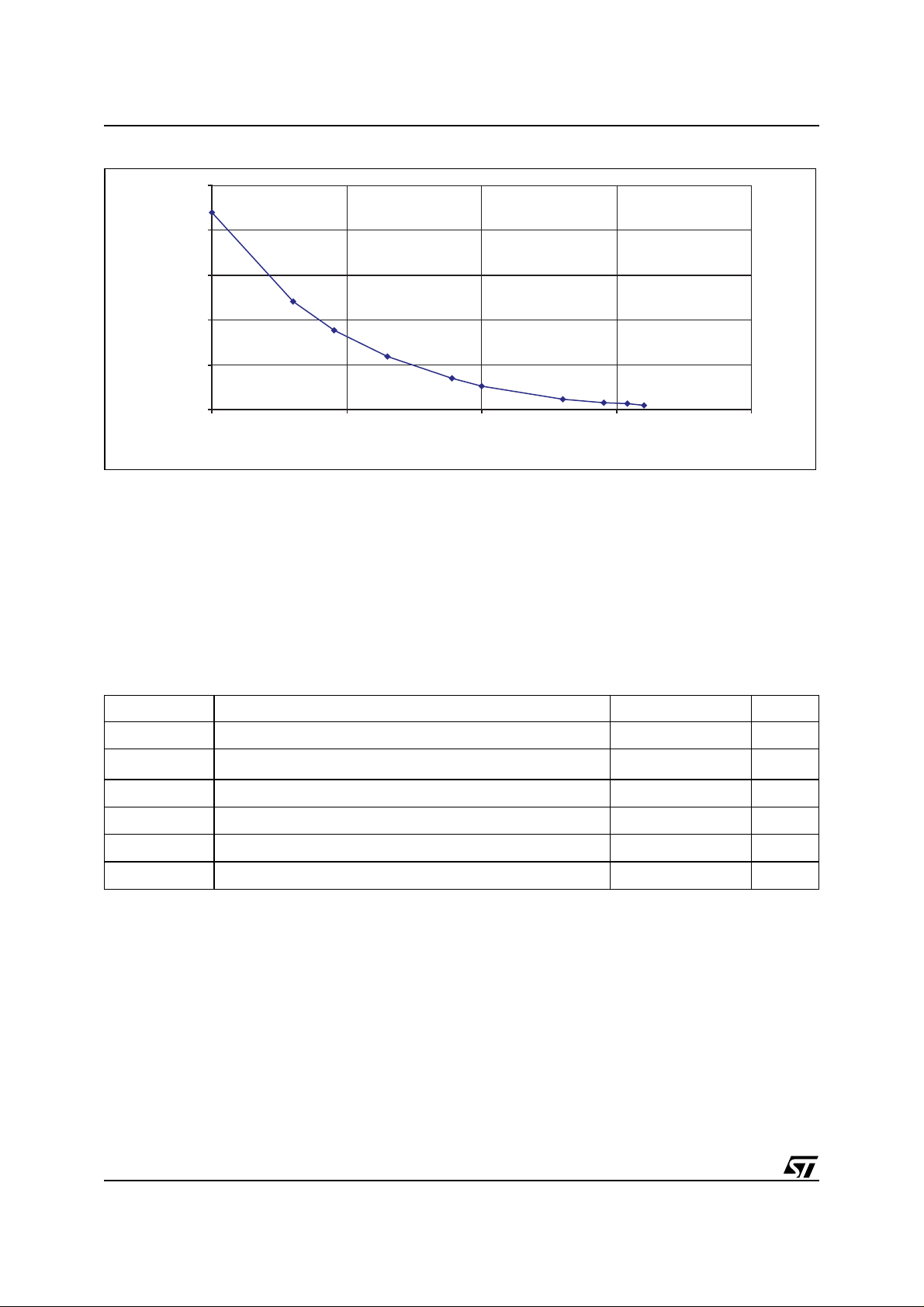

Figure 27.Maximum Transient Duration vs. Reset Threshold Overdrive. . . . . . . . . . . . . . . . . . . . . 16

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 4. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 5. Operating and AC Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 28.AC Testing Input/Output Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 29.Power-fail Comparator Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 30.MR

Figure 31.Watchdog Timing (STM706/706P ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 6. DC and A C Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 32.SO8 – 8-lead Plastic Small Outline, 150 mils body width, Package Mechanical. . . . . . . 20

Table 7. S O8 – 8-lead Plast ic Small Outline, 150 mils body widt h, Package Mechanical Data . . 20

Figure 33.TSSOP8 – 8-lead, Thin Shrink Small Outline, 3x3mm body size, Outline . . . . . . . . . . . 21

Table 8. TS SOP 8 – 8-lead, Thin Shrink Smal l Outline, 3x3mm body size , Mechanical Data . . . . 21

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 9. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 10.Marking Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 11.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3/25

Page 4

STM706/706P/708

SUMMARY DESCRIPT ION

The STM70X SUPERVISORs are self-contained

devices which provide microprocessor supervisory functions. A precision voltage reference and

comparator monitors the V

tolerance condition. When an invalid V

tion occurs, the reset output (RST

(or high in the ca se of RST). These devices also

offer a watchdog timer (except for STM708) as

well as a power-fail comparator to provide the sys-

input for an out-of-

CC

CC

condi-

) is forced low

tem with an early warning of impending power failure.

The STM706P is identical to the STM706R, except

its reset output is active-high.

These devices are available in a standard 8-pin

SOIC package or a space-saving 8-pin TSSOP

package.

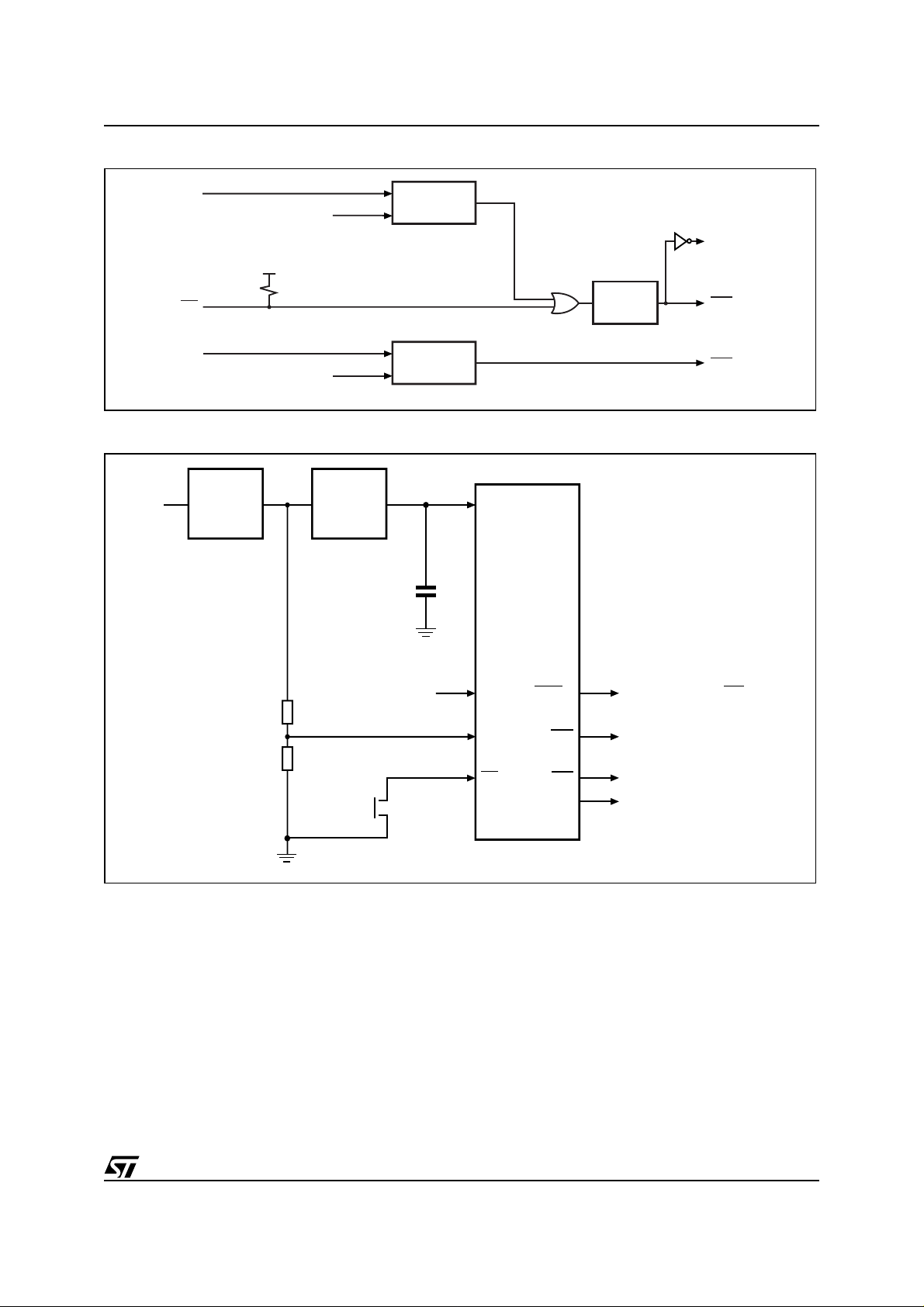

Figure 2. Logic Diagram (STM706/706P)

V

CC

WDI

MR

STM706

PFI

Note: 1. For STM 7 06P only.

V

SS

WDO

RST (RST)

PFO

AI08841

Figure 3. Logic Diagram (STM708)

(1)

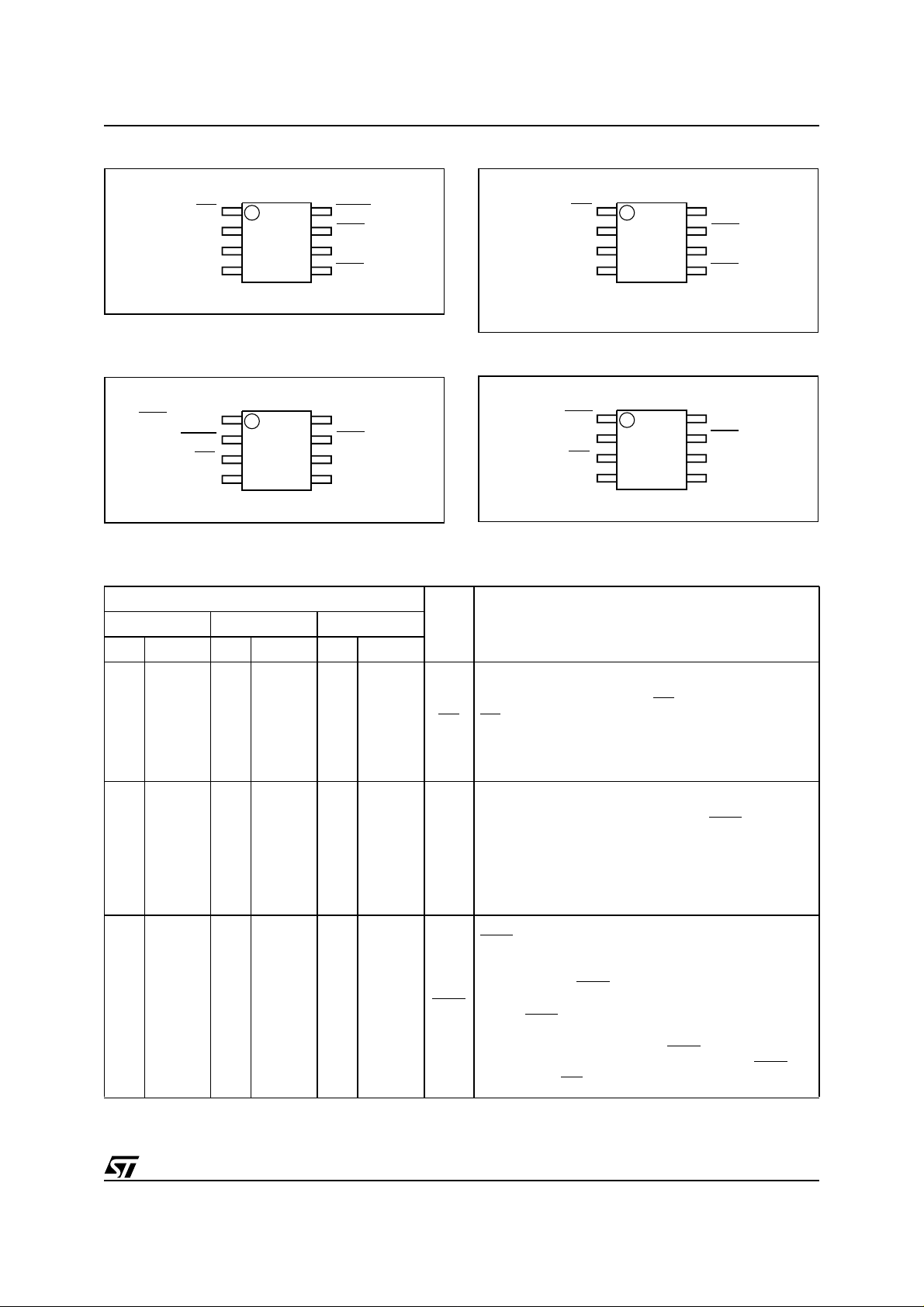

Table 2. Signal Names

MR Push-button Reset Input

WDI Watchdog Input

WDO

RST

(1)

RST

V

CC

PFI Power-fail Input

PFO

V

SS

NC No Conn ect

Note: 1. For STM 7 06P/708 onl y.

Watchdog Output

Active-Low Reset Output

Active-High Reset Output

Supply Voltage

Power-fail Output

Ground

4/25

MR

PFI

V

CC

STM708

V

SS

RST

RST

PFO

AI08842

Page 5

STM706/706P/708

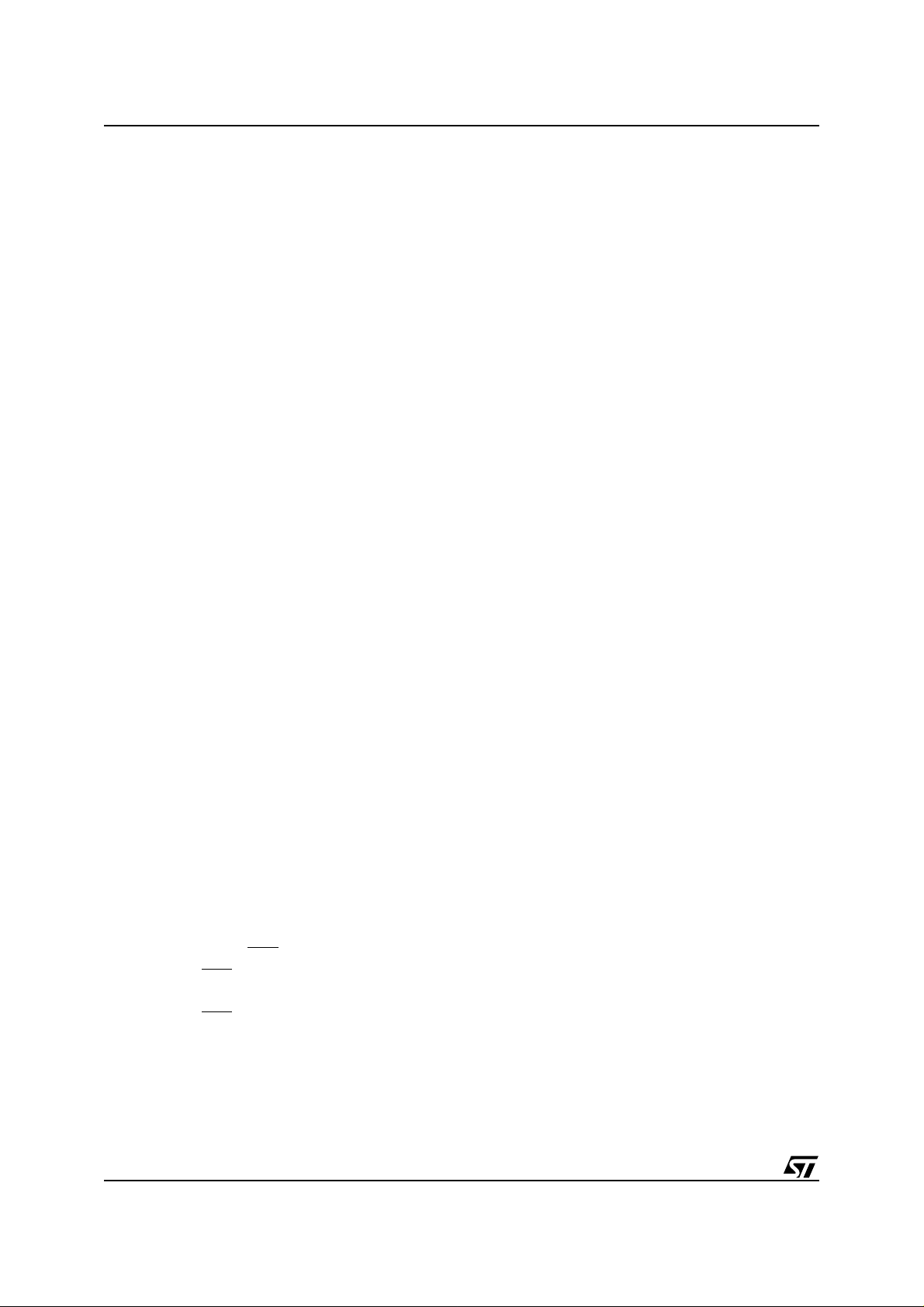

Figure 4. STM706/706P SO8 Connecti ons

SO8

MR

V

V

PFI

Note: 1. For STM706P reset output is active-high.

CC

SS

1

2

3

4

8

7

6

5

WDO

RST(RST)

WDI

PFO

AI08837

(1)

Figure 5. STM706/706P TSSOP8 C onnecti on s

RST(RST)

(1)

WDO

MR

V

CC

Note: 1. For STM706P reset output is active-high.

TSSOP8

1

2

3

4

WDI

8

PFO

7

PFI

6

V

5

SS

AI08838

Table 3. Pin Description

Pin

Name FunctionSTM706P STM706 STM708

SO8 TSSOP8 SO8 TSSOP8 SO8 TSSOP8

131313MR

6868––WDI

8282––WDO

Figure 6. STM708 SO8 Connections

SO8

MR

V

V

PFI

CC

SS

1

2

3

4

RST

8

RST

7

NC

6

PFO

5

AI08839

Figure 7. STM708 TSSOP8 Connections

TSSOP8

RST

RST

MR

V

CC

Push-button Reset Input.

A logic low on /MR asserts the reset output. Reset

remains asserted as long as MR

MR returns high. This active-low input has an internal

pull-up. It can be driven from a TTL or CMOS logic line,

or shorted to ground with a switch. Leave open if

unused.

Watchdog Input.

If WDI remains high or low for 1.6sec, the internal

watchdog timer runs out and reset (or WDO

triggered. The internal watchdog timer clears while

reset is asserted or when WDI sees a rising or falling

edge.

The watchdog function cannot be disabled by allowing

the WDI pin to float.

Watchdog Output.

goes low when a transition does not occur on

WDO

WDI within 1.6sec, and remains low until a transition

occurs on WDI (indicating the watchdog interrupt has

been serviced). WDO

below the reset threshold; however, unlike the reset

output, WDO

reset threshold.

Note: For those devices with a WDO

watchdog timeout will not trigger reset unless WDO

connected to MR

goes high as soon as VCC exceeds the

1

2

3

4

also goes low when VCC falls

.

NC

8

PFO

7

PFI

6

V

5

is low and for t

SS

AI08840

) is

output, a

rec

after

is

5/25

Page 6

STM706/706P/708

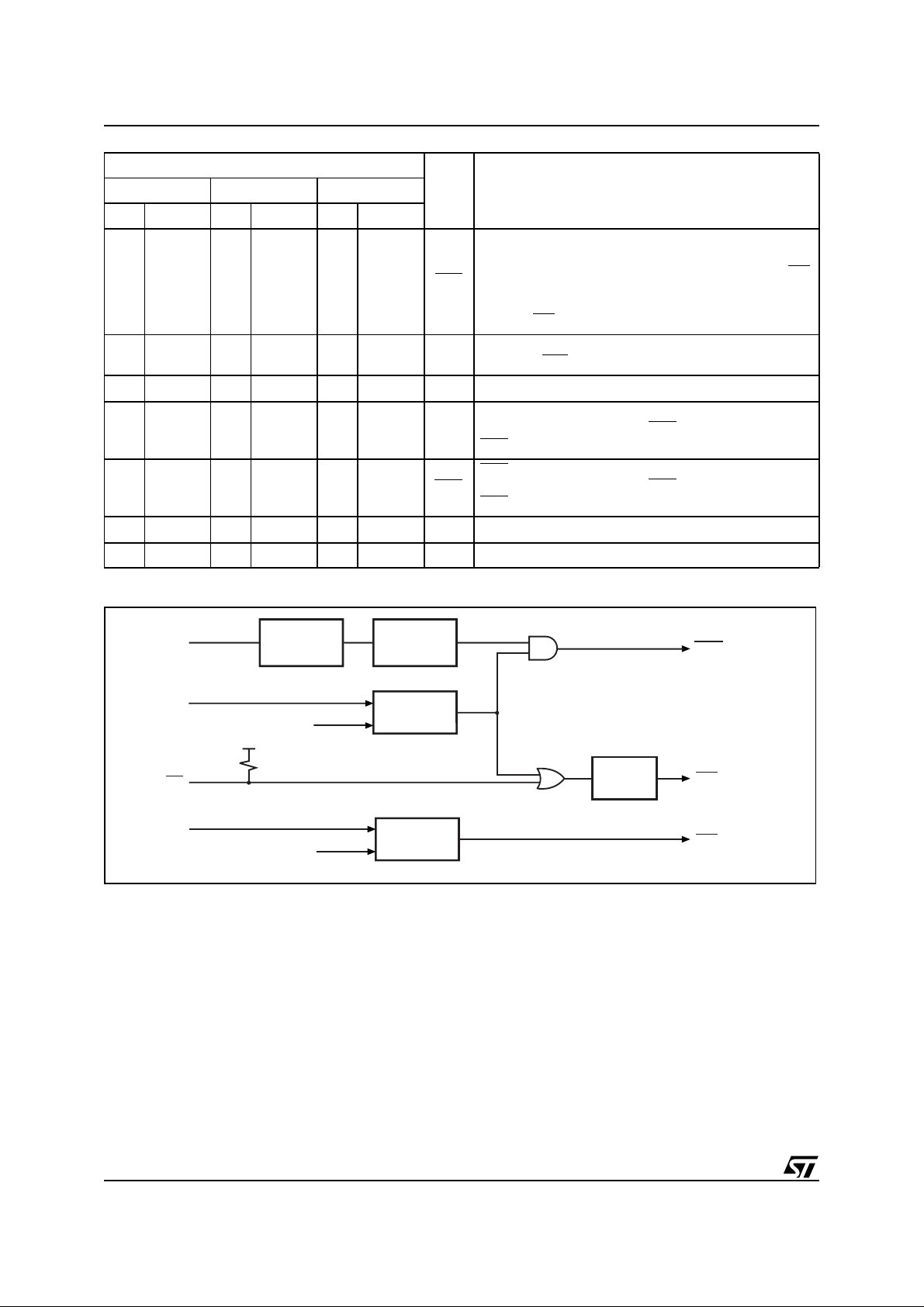

Pin

Name FunctionSTM706P STM706 STM708

SO8 TSSOP8 SO8 TSSOP8 SO8 TSSOP8

Active-Low Reset Output.

Pulses low for t

––7171RST

71––82RST

242424

464646PFI

575757PFO

353535

––––68NCNo Connect.

whenever VCC is below the reset threshold or when MR

is a logic low. It remains low for t

rises above the reset threshold, the watchdog triggers a

reset, or MR

Active-High Reset Output.

Inverse of RST

V

Supply Voltage.

CC

PFI Power-fail Input.

When PFI is less than V

PFO remains high. Connect to ground if unused.

PFO Power-fail Output.

When PFI is less than V

PFO remains high. Leave open if unused.

V

Ground.

SS

when triggered, and stays low

rec

after either VCC

rec

goes from low to high.

.

, PFO goes low; otherwise,

PFI

, PFO goes low; otherwise,

PFI

Figure 8. Block Diagram (STM706/706P)

WDI

V

CC

V

MR

PFI

Note: 1. For STM 7 06P only.

CC

WDI

Transitional

Detector

V

RST

V

WATCHDOG

PFI

TIMER

COMPARE

COMPARE

t

rec

Generator

WDO

RST(RST)

PFO

AI08829

(1)

6/25

Page 7

Figure 9. Block Diagram (STM708)

V

CC

V

CC

MR

STM706/706P/708

V

RST

COMPARE

t

rec

Generator

RST

RST

PFI

Figure 10. Hardware Hookup

Unregulated

Voltage

R1

R2

V

PFI

COMPARE

Regulator

V

V

CC

IN

0.1µF

From Microprocessor

Push-button

V

CC

WDI

PFI

MR

STM70X

(1)

WDO

PFO

RST

RST

PFO

AI08830

(1)

To Microprocessor IRQ

To Microprocessor NMI

(2)

To Microprocessor Reset

Note: 1. For STM706/706P.

2. For ST M 706P/708.

AI08843

7/25

Page 8

STM706/706P/708

OPERATION

Reset Output

The STM70X SUPERVI SOR asserts a reset signal to the MCU whenever V

set threshold (V

(if WDO

is connected to M R), or when the Push-

button Reset Input (MR

), a watchdog time-out o ccurs

RST

) is taken low. RST is guar-

anteed to be a log ic lo w (log ic hig h for S T M70 6P/

708) for V

CC

< V

down to VCC =1V for TA = 0°C

RST

to 85°C.

During power-up, once V

threshold an internal timer keeps RST

reset time-out period, t

rec

returns high.

drops below the reset threshold, RST goes

If V

CC

low. Each time RST

is asserted, it stays low for at

least the reset time-out period (t

goes below the reset threshold the internal timer

clears. The reset timer starts when V

above the reset threshold.

Push-button Reset Input

A logic low on MR

asserted while MR

asserts reset. Reset remains

is low, and for t

30., page 18) after it returns high. The MR

has an internal 40kΩ pull-up resistor, allowing it to

be left open if not used. This input can be driven

with TTL/CMOS-logic levels or with open-drain/

collector outputs. Connect a normally open momentary switch from MR

ual reset function; external debounce circuitry is

not required. If MR

is driven from long cables or

the device is used in a noisy environment, connect

a 0.1µF capacitor from M R

ditional noise immunity. MR

when not used.

V

CC

Watchdog Input (STM706/706P)

The watchdog timer can be used to detect an outof-control MCU. If the MCU does not toggle the

Watchdog Input (WDI) within t

Watchdog Output pin (WDO

ternal 1.6sec timer is cleared by either:

1. a reset pulse, or

2. by toggling WDI (high-to-low or low-to-high),

which can detect pulses as short as 50ns.

See F igure 31., page 18 for STM706/706 P.

The timer remains cleared and does not count for

as long as reset is asserted. As soon as reset is released, the timer starts counting.

goes below the re-

CC

exceeds the reset

CC

low for the

. After this interval RST

). Any time V

rec

rec

CC

(see Figure

CC

returns

input

to GND to create a man-

to GND to provide ad-

may float, or be tied to

(1.6sec), the

WD

) is asserted. The in-

Watchdog Output (STM706/706P)

When V

drops below the reset threshold, WDO

CC

will go low even if the wa tchdog timer has not yet

timed out. However, unlike the reset output, WDO

goes high as soon as VCC exceeds the reset

thres h old. W DO

pulse by connecting it to the MR

may be used to generate a reset

input.

Power-fail Input/Output

The Power-fail Input (PFI) is compared to an internal reference voltage (independent from the V

RST

comparator). If PFI is less than the power-fail

threshold (V

), the Power-Fail Output (PFO) will

PFI

go low. This function is intended for use as an undervoltage detector to signal a failing power supply. Typically PFI is connected through an external

voltage divider (see Figure 10. , page 7) to either

the unregulated DC input (if it is a vailable) or the

regulated output of the V

regulator. The voltage

CC

divider can be set up such that the voltage at PFI

falls below V

regulated V

several milliseconds before the

PFI

input to the STM70X or the micro-

CC

processor drops below the minimum operating

voltage.

If the comparator is unused, PFI should be connected to V

and PFO left unconnected. PFO

SS

may be connected to MR on t he STM70X s o that

a low voltage on PFI will gene ra te a reset output.

Ensuring a Valid Reset Output Down to

=0V

V

CC

When V

falls below 1V, the state of the RST out-

CC

put can no longer be guaranteed, and becomes

essentially an open circuit. If a high value pulldown resistor is added to the RST

pin, the output

will be held low during this condition. A resistor value of approximately 100kΩ will be large enough to

not load the output under operating conditions, but

still sufficient to pull RST

to ground during this low

voltage condition (see Figure 11).

Figure 11. Reset Output Valid to Ground Circuit

STM70X

RST

R1

8/25

AI08844

Page 9

STM706/706P/708

Interfacing to Microprocessors with Bidirectional Reset Pins

Figure 12. Interfacing to Microprocessors with Bi-directional Reset I/O

Microprocessors with bi-directional reset pins can

contend with the STM70X reset output. For example, if the reset output is driven high and the micro

wants to pull it low, signal contention will result. To

prevent this from occurring, connect a 4.7kΩ resistor between the reset output and the micro’s reset

I/O as in Figure 12.

TYPICAL OPERATING CHARACTERISTICS

Note: Typical values are at TA = 25°C .

Figure 13. Supply Current vs. Temperature (no load )

30

V

CC

STM70X

GND

RST

Buffered Reset to other

System Components

4.7k

V

CC

Microprocessor

RST

GND

AI08845

25

20

15

Supply Current [µA]

10

5

0

–50 –40 –30 –20 –10 0 10 20 30 40 50 60 70 80 90 100

TEMPERATURE [°C]

2.5V

3.3V

3.6V

5.0V

5.5V

AI09141

9/25

Page 10

STM706/706P/708

Figure 14. V

Threshold vs. Temperature

PFI

1.255

1.250

1.245

1.240

1.235

THRESHOLD [V]

PFI

V

1.230

V

1.225

–50 –30 –10 10 30 50 70 90 110 130

V

BAT

CC

= 3.0V

VCC = 5V

V

CC

= 2.5V

= 3.3V

TEMPERATURE [°C]

Figure 15. Reset Comparator Propagation Delay vs. Temperature

24

22

20

18

16

14

12

PROPAGATION DELAY [µs]

10

–60 –40 –20 0 20 40 60 80 100

TEMPERATURE [°C]

V

= 3.0V

BAT

100mV OVERDRIVE

AI09142

AI09143

Figure 16. Power-up t

215

210

205

[ms]

rec

t

200

195

–50 –30 –10 10 30 50 70 90 110 130

10/25

vs. Temperature

rec

TEMPERATURE [°C]

AI09144

Page 11

Figure 17. Normalized Reset Threshold vs. Temperature

1.002

1.000

0.998

[V]

0.996

V

= 3.0V

BAT

0.994

NORMALIZED RESET THRESHOLD

–60 –40 –20 0 20 40 60 80 100 120 140

TEMPERATURE [°C]

Figure 18. Watchdog Time-out Period vs. Temperature

1.74

1.72

1.70

1.68

1.66

1.64

1.62

PERIOD [sec]

1.60

WATCHDOG TIME-OUT

1.58

1.56

–50 –30 –10 10 30 50 70 90 110 130

TEMPERATURE [°C]

STM706/706P/708

AI09145

AI09146

11/25

Page 12

STM706/706P/708

Figure 19. PFI to PFO Propagation Delay vs. Temper ature

9

8

7

6

5

4

3

PROPAGATION DELAY [µs]

2

1

0

–60 –40 –20 0 20 40 60 80 100 120 140

TEMPERATURE [°C]

AI09148

Figure 20. R

6

5

4

3

2

RST OUTPUT VOLTAGE [V]

1

0

ST Output Voltage vs. Supply Voltage

V

CC

V

RST

500 ms/div

AI09149

12/25

Page 13

Figure 21. RS T Ou t put V ol ta ge vs . Su ppl y V ol ta ge

6

5

V

CC

4

3

2

V

RST OUTPUT VOLTAGE [V]

1

0

RST

500 ms/div

STM706/706P/708

AI09150

Figure 22. R

6

5

4

3

LEVEL [V]

CC

V

2

1

0

ST Response Time (Assertion)

2 µs/div

V

RST

V

CC

AI09151

13/25

Page 14

STM706/706P/708

Figure 23. RST Response Time (Assertion)

6

V

CC

5

4

3

LEVEL [V]

CC

V

2

1

V

RST

0

2µs/div

Figure 24. Power-fail Com parator Response Tim e (Assertion)

6

5

4

PFO

3

LEVEL [V]

PFO

2

V

1

0

PFI

2µs/div

1.45

1.40

1.35

1.30

1.25

1.20

1.15

AI09152

AI09153

LEVEL [V]

PFI

V

14/25

Page 15

Figure 25. Power-fail Comparator Response Time (De-A ssertion )

6

STM706/706P/708

1.45

5

4

3

LEVEL (V)

PFO

2

V

1

0

Figure 26. V

60

50

40

30

20

PFO

PFI

2 µs/div

to Reset Propagation Delay vs. Temperature

CC

1.40

1.35

1.30

1.25

1.20

1.15

AI09154

LEVEL (V)

PFI

V

10V/ms

1V/ms

0.25V/ms

10

PROPAGATION DELAY [µs]

0

–60 –40 –20 0 20 40 60 80 100

TEMPERATURE [°C]

AI09155

15/25

Page 16

STM706/706P/708

Figure 27. Maximum Transient Duration vs. Reset Thresh old Over drive

250

200

150

100

50

TRANSIENT DURATION [µs]

0

1 10 100 1000 10000

RESET COMPARATOR OVERDRIVE, V

– VCC [mV]

RST

MAXIMUM RA T ING

Stressing the device above the rating l isted in t he

Absolute Maximum Ratings” table may cause permanent damage to the device. These are stress

ratings only and operation of the device at t hese or

any other conditions ab ove those i ndicated in t he

Operating sections of this specificat ion is not im-

plied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device

reliability. Refer also to the STMicroelectronics

SURE Program and other relevan t quality documents.

AI09156

Table 4. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

STG

(1)

T

SLD

V

IO

V

CC

I

O

P

D

Note: 1. Reflow at peak temp erature of 2 55°C to 260°C for < 30 sec onds (total the rm al budget not to exceed 180°C for between 90 to 150

seconds).

Storage Temperature (VCC Off)

–55 to 150 °C

Lead Solder Temperature for 10 seconds 260 °C

Input or Output Voltage

–0.3 to V

CC

+0.3

V

Supply Voltage –0.3 to 7.0 V

Output Current 20 mA

Power Dissipation 320 mW

16/25

Page 17

STM706/706P/708

DC AND AC PARAMETERS

This section summarizes t he operating m easurement conditions, and the DC and AC characteristics of the device. The parameters in the D C and

AC characteristics Tables that follow, are derived

from tests performed under the Measurement

Table 5. Operating and AC Measurement Conditions

Parameter STM70X Unit

V

Supply Voltage

CC

Ambient Operating Temperature (T

Input Rise and Fall Times ≤ 5ns

)

A

Conditions summarized in Table 5, Operating and

AC Measurement Conditions. Designers should

check that the operating cond itions in their circuit

match the operating conditions when relying on

the quoted parameters.

1.0 to 5.5 V

–40 to 85 °C

Input Pulse Voltages

Input and Output Timing Ref. Voltages

Figure 28. AC Testing Input/Output Waveforms

0.8V

0.2V

CC

CC

0.7V

0.3V

AI02568

CC

CC

Figure 29. Power-fail Com p a rat or Wa v ef orm

V

CC

V

RST

PFO

0.2 to 0.8V

0.3 to 0.7V

CC

CC

V

V

trec

RST

AI08860a

17/25

Page 18

STM706/706P/708

Figure 30. MR Timing Waveform

MR

tMLRL

(1)

RST

tMLMH

Note: 1. RST for STM706P/708.

Figure 31. Watchdog Timing (STM706/706P)

V

CC

RST

WDI

WDO

trec

Table 6. DC and AC Characteristics

Sym

V

Alter-

native

CC

I

CC

Operating Voltage

VCC Supply Current

Description

Input Leakage Current (WDI)

Input Leakage Current (PFI)

I

LI

Input Leakage Current (MR

V

IH

V

IH

V

IL

V

IL

Input High Voltage (MR)

Input High Voltage (WDI)

Input Low Voltage (MR)

Input Low Voltage (WDI)

)

trec

tWD

IN

= V

CC

CC

CC

(1)

CC

CC

< 5.5V

< 5.5V

< 5.5V

Test Condition

V

< 3.6V

CC

< 5.5V

V

CC

0V = V

0V = VIN = V

(max) < VCC < 3.6V

V

RST

4.5V < V

4.5V < V

(max) < VCC < 3.6V 0.7V

V

RST

V

(max) < VCC < 5.5V 0.7V

RST

4.5V < V

(max) < VCC < 3.6V

V

RST

V

(max) < VCC < 5.5V 0.3V

RST

Min Typ Max Unit

(2)

1.2

35 50 µA

40 60 µA

–1 +1 µA

–25 2 +25 nA

25 80 250 µA

75 125 300 µA

2.0 V

CC

CC

AI07837a

AI08833

5.5 V

0.8 V

0.6 V

CC

V

V

V

18/25

Page 19

STM706/706P/708

OL

OL

Alter-

native

Output Low Voltage (PFO,

, RST, WDO)

RST

Output Low Voltage (RST)

Sym

V

V

Output High Voltage (RST,

RST, WDO

V

OH

Output High Voltage (PFO

Power-fail Comparator

V

PFI

t

PFD

PFI to PFO Propagation Delay 2 µs

Reset Thresholds

V

RST

Description

)

PFI Input Threshold

Reset Threshold

Test Condition

= V

V

CC

I

SINK

I

= 50µA; VCC = 1.0V;

SINK

T

= 0°C to 85°C

A

= 100µA; VCC = 1.2V

I

SINK

I

SOURCE

VCC = V

I

)

SOURCE

= V

V

CC

PFI Falling

(STM70XP/R, V

STM70XS/T, VCC = 3.3V)

STM706P/70XR 2.55 2.63 2.70 V

STM70XS 2.85 2.93 3.00 V

STM70XT 3.00 3.08 3.15 V

(max),

RST

= 3.2mA

= 1mA,

(max)

RST

= 75µA,

(max)

RST

CC

(1)

= 3.0V;

Min Typ Max Unit

0.3 V

0.3 V

0.3 V

2.4 V

0.8V

CC

1.20 1.25 1.30 V

V

Reset Threshold Hysteresis 20 mV

t

rec

RST Pulse Width 140 200 280 ms

Push-button Reset Input

V

(max) < VCC < 3.6V

t

MLMHtMR

t

MLRLtMRD

MR Pulse Width

MR to RST Output Delay

RST

V

RST

4.5V < V

4.5V < V

CC

(max) < VCC < 3.6V

CC

Watchdog Timer (STM706/706P)

STM706P/70XR,

= 3.0V

V

t

WD

Watchdog Timeout Period

WDI Pulse Width

V

Note: 1. Valid for Ambient Operating Tem perature: TA = –40 to 85°C; VCC = V

(min) = 1.0V for TA = 0°C to +85°C.

2. V

CC

CC

STM70XS/70XT,

= 3.3V

V

CC

4.5V < V

RST

CC

(max) < VCC < 3.6V

500 ns

< 5.5V

150 ns

< 5.5V

1.12 1.60 2.24 s

< 5.5V

50 ns

100 ns

(max) to 5 .5V (except where noted).

RST

750 ns

250 ns

19/25

Page 20

STM706/706P/708

PACKAG E MECHANI CAL

Figure 32. SO8 – 8-lead Plastic Small Outline, 150 mils body width, Package Mech anical

h x 45˚

A2

A

C

B

e

ddd

D

8

E

H

1

Note: Drawing is not to scale.

LA1 α

SO-A

Table 7. SO8 – 8-lead Plastic Small Outline, 150 mils body width, Package Mechanica l Data

Symb

Typ Min Max Typ Min Max

A – 1.35 1.75 – 0.053 0.069

mm inches

A1 – 0.10 0.25 – 0.004 0.010

B – 0.33 0.51 – 0.013 0.020

C – 0.19 0.25 – 0.007 0.010

D – 4.80 5.00 – 0.189 0.197

ddd– –0.10– –0.004

E – 3.80 4.00 – 0.150 0.157

e1.27– –0.050– –

H – 5.80 6.20 – 0.228 0.244

h – 0.25 0.50 – 0.010 0.020

L – 0.40 0.90 – 0.016 0.035

α –0°8°–0°8°

N8 8

20/25

Page 21

Figure 33. TSSOP8 – 8-lead, Thin Shrink Small Outline, 3x3mm body size, Outline

D

STM706/706P/708

8

1

5

EE1

4

α

A1

A2A

CP

eb

Note: Drawing is not to scale.

L

L1

TSSOP8BM

Table 8. TSSOP8 – 8-lead, Thin Shrink Small Outline, 3x3mm body size, Mechanical Data

Symb

Typ Min Max Typ Min Max

A – –1.10– –0.043

mm inches

c

A1 – 0.05 0.15 – 0.002 0.006

A2 0.85 0.75 0.95 0.034 0.030 0.037

b – 0.25 0.40 – 0.010 0.016

c – 0.13 0.23 – 0.005 0.009

CP – – 0.10 – – 0.004

D 3.00 2.90 3.10 0.118 0.114 0.122

e0.65– –0.026– –

E 4.90 4.65 5.15 0.193 0.183 0.203

E1 3.00 2.90 3.10 0.118 0.114 0.122

L 0.55 0.40 0.70 0.022 0.016 0.030

L1 0.95 – – 0.037 – –

α –0°6°–0°6°

N8 8

21/25

Page 22

STM706/706P/708

PART NUMBERING

Table 9. Ordering Information Scheme

Example: STM70X T M 6 E

Device Type

STM70X

Reset Threshold Voltage

T: 3.00V ≤ V

S: 2.88V ≤ V

R, STM706P: 2.59V ≤ V

Package

M = SO8

DS = TSSOP8

RST

RST

≤ 3.15V

≤ 3.00V

RST

≤ 2.70V

Temperature Range

6 = –40 to 85°C

Shipping Method

E = Tubes (Pb-Free - ECO PACK

F = Tape & Reel (Pb-Free - ECO PACK

®

)

®

)

For other options, or for more information on any aspect of this device, please contact the ST Sales Office

nearest you.

22/25

Page 23

Table 10. Marking Description

Part Number Reset Threshold Package Topside Marking

STM706/706P/708

STM706P 2.63V

STM706T 3.08V

STM706S 2.93V

STM706R 2.63V

STM708T 3.08V

STM708S 2.93V

STM708R 2.63V

SO8

706P

TSSOP8

SO8

706T

TSSOP8

SO8

706S

TSSOP8

SO8

706R

TSSOP8

SO8

708T

TSSOP8

SO8

708S

TSSOP8

SO8

708R

TSSOP8

23/25

Page 24

STM706/706P/708

REVISION HISTORY

Table 11. Document Revision History

Date Version Revision Details

October 2003 1.0 First Issue

12-Dec-03 2.0

16-Jan-04 2.1

09-Apr-04 3.0 Reformatted; update characteristics (Figure 15, 19, 20, 21, 22, 23, 26, 27; Table 6)

25-May-04 4.0 Update characteristics (Table 3, 6)

02-Jul-04 5.0 Datasheet promoted; waveform corrected (Figure 29)

Reformatted; update characteristics (Figure 2, 3, 8, 9, 10, 29, 30, 31; Table 6, 7, 8,

9)

Add Typical Operating Characteristics (Figure 13, 14, 15, 16, 17, 18, 19, 20, 21, 22,

23, 24, 25, 26, 27)

24/25

Page 25

STM706/706P/708

Information furnished is believed to be accurate and reliable. However, STMicroelectronics a ssumes no responsibility fo r the c onsequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authori zed for use as crit i cal compon ent s in life supp ort devices or systems with out express written app roval of STMi cr oel ectronics.

The ST logo is a registered trademark of STM icroelectr onics.

All other na m es are the prop erty of their respectiv e owners.

© 2004 STMi croelectro ni cs - All rights reserved

Australi a - B elgium - Brazil - Canad a - China - Czech Republic - F in l and - France - Germany -

Hong Kong - India - Israe l - It al y - Japan - Mal ays i a - Malta - Morocco - Singa pore -

STMicroelectroni cs GROUP OF COMPANIES

Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com

25/25

Loading...

Loading...