STMicroelectronics HCF4013B Technical data

HCF4013B

DUAL D-TYPE FLIP FL OP

■ SET - RESET CAPABILITY

■ STATIC FLIP-FLOP OPERATION - RETAINS

STATE INDEFINITELY WITH CLOCK LEVEL

EITHER "HIGH" OR "LOW"

■ MEDIUM SP EED OPERATION 1 6MHz (TY P.)

CLOCK TOGGLE RATE AT 10V

■ STANDARDIZED SYMMETRICAL OUTPUT

CHARACTERISTICS

■ QUIESCENT CURRENT SPECIFIED UP TO

20V

■ 5V, 10V AND 15V PARAMETRIC RA T INGS

■ INPUT LEAKAGE CURRENT

I

= 100nA (MAX) AT VDD = 18V TA = 25°C

I

■ 100% TESTED FOR QUIESCENT CURRENT

■ MEETS ALL REQUIREMENTS OF JEDEC

JESD13B " STANDARD SPECIFICATIONS

FOR DESCRIPTI ON OF B SERI ES CMOS

DEVICES"

DESCRIPTION

The HCF4013B is a m onolithic integrated circuit

fabricated in Metal Oxide Semiconductor

technology available in DIP and SOP packages.

The HCF4013B consists of two identical,

independent data type flip-flops. Each flip-flop has

independent data, set, reset, and clock inputs and

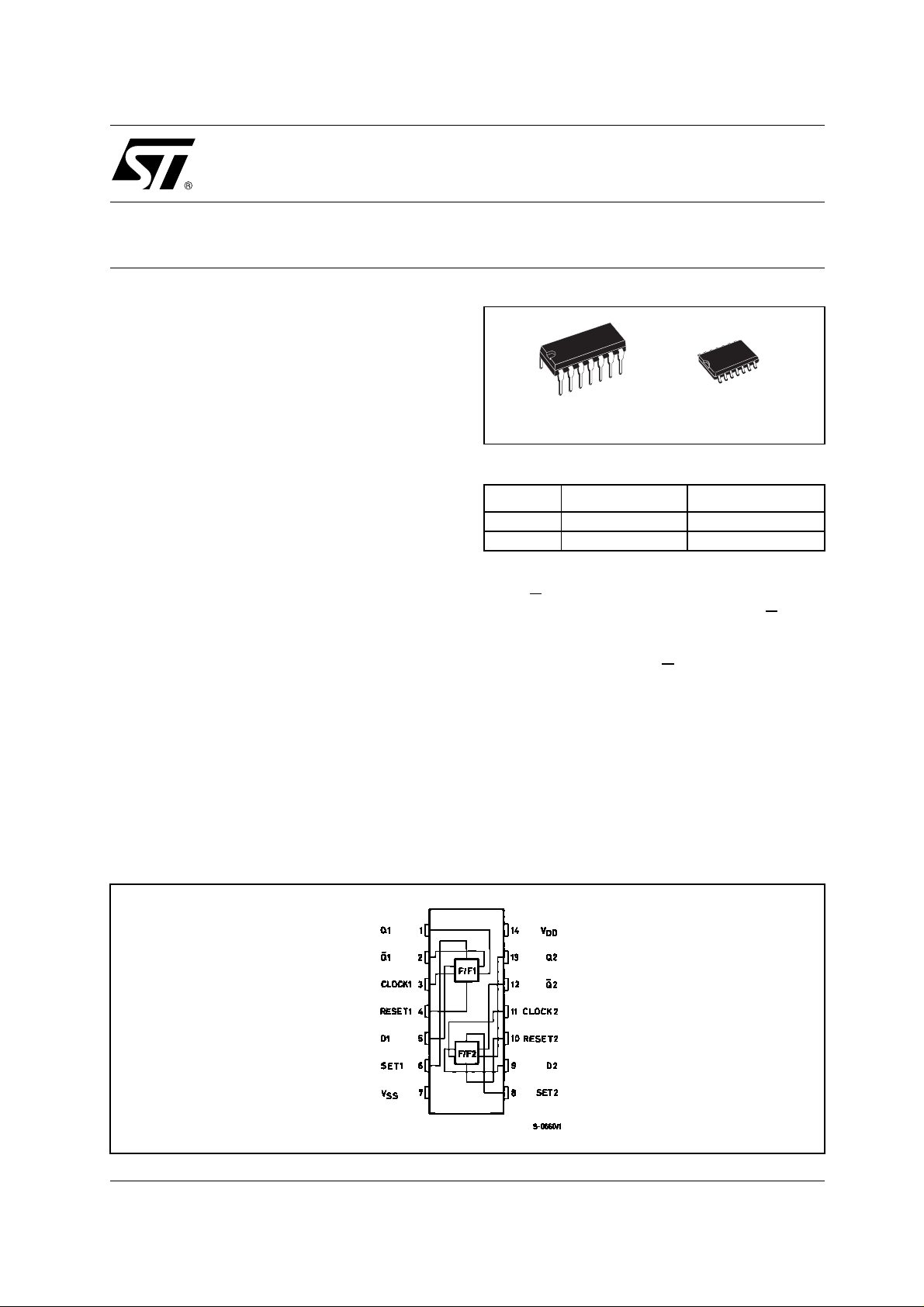

DIP SOP

ORDER CODES

PACKAGE TUBE T & R

DIP HCF4013BEY

SOP HCF4013BM1 HCF4013M013TR

Q and Q

register applications, and, by connecting Q

outputs. This device can be used for shift

output

to the data input, for counter and toggle

applications. The logic level present at the D input

is transferred to the Q

output during the

positive-going transition of the clock pulse. Setting

or resetting is independent of the clock and is

accomplished by a hi gh level on the set or reset

line, respectivel y

PIN CONNECTION

1/9September 2001

HCF4013B

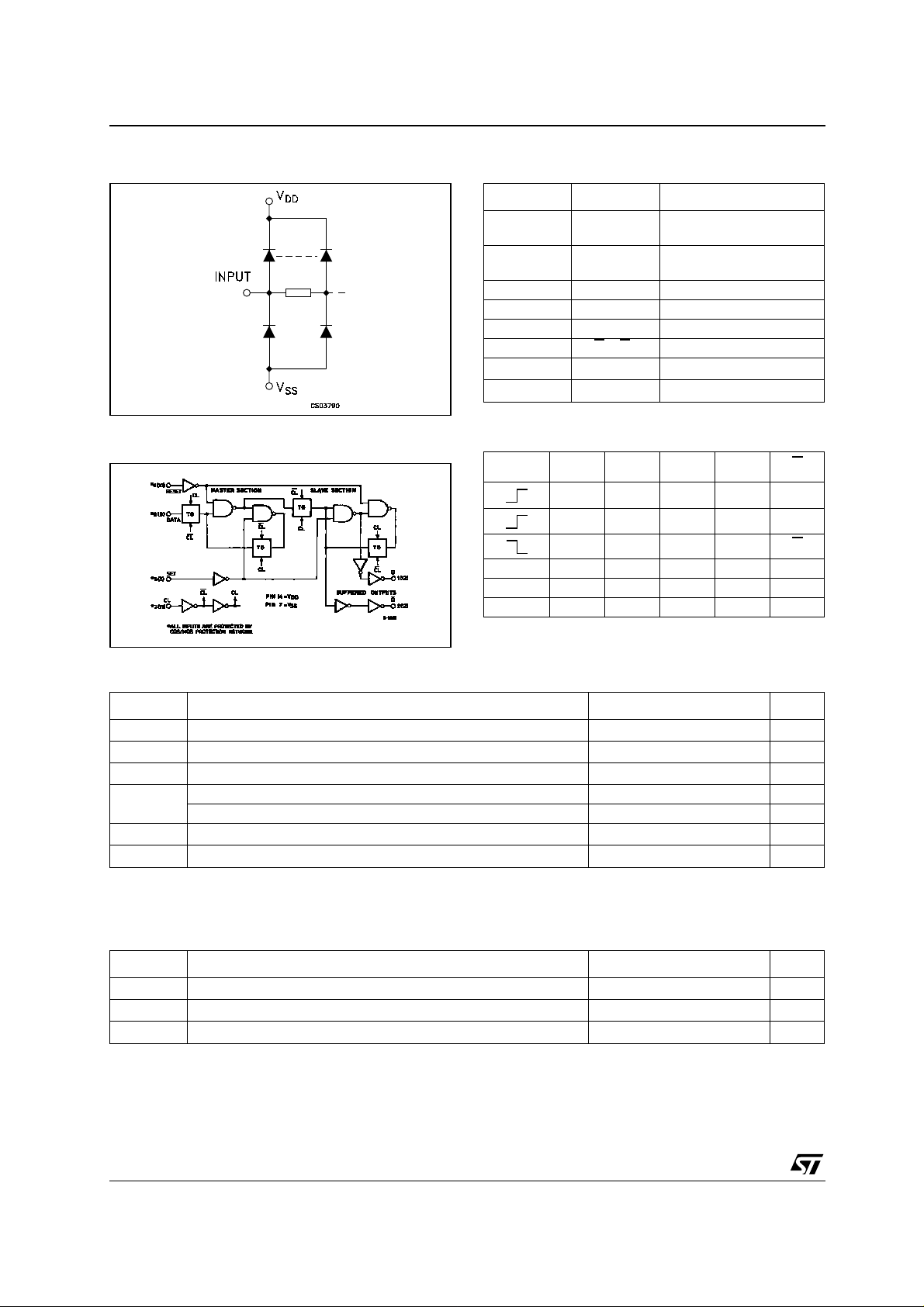

INPUT EQUIVALENT CIRCUIT

LOGIC DIAGRAM

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

3, 11

4, 10

CLOCK1

CLOCK2

RESET1

RESET2

Clock Inputs

Reset Inputs

6, 8 SET1, SET2 Set Inputs

5, 9 D1, D2 Data Inputs

1, 13 Q1, Q2 Data Outputs

2, 12 Q

7

14

1, Q2 Data Outputs

V

SS

V

DD

Negative Supply Voltage

Positive Supply Voltage

TRUTH TABLE

∆

CLOCK

XXHLLH

XXLHHL

X XHHHH

X : Don’t Care

∆ :

Low Level

D RESET SET Q Q

LLLLH

HLLHL

XLLQQ

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

V

P

Supply Voltage

DD

DC Input Voltage -0.5 to VDD + 0.5

I

I

DC Input Current

I

Power Dissipation per Package 200 mW

D

-0.5 to +22 V

± 10 mA

V

Power Dissipation per Output Transistor 100 mW

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied.

All voltage values ar e referred to V

Operating Temperature

op

Storage Temperature

stg

pin voltage.

SS

-55 to +125 °C

-65 to +150 °C

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Value Unit

V

V

T

Supply Voltage

DD

Input Voltage 0 to V

I

Operating Temperature

op

3 to 20 V

DD

-55 to 125 °C

V

2/9

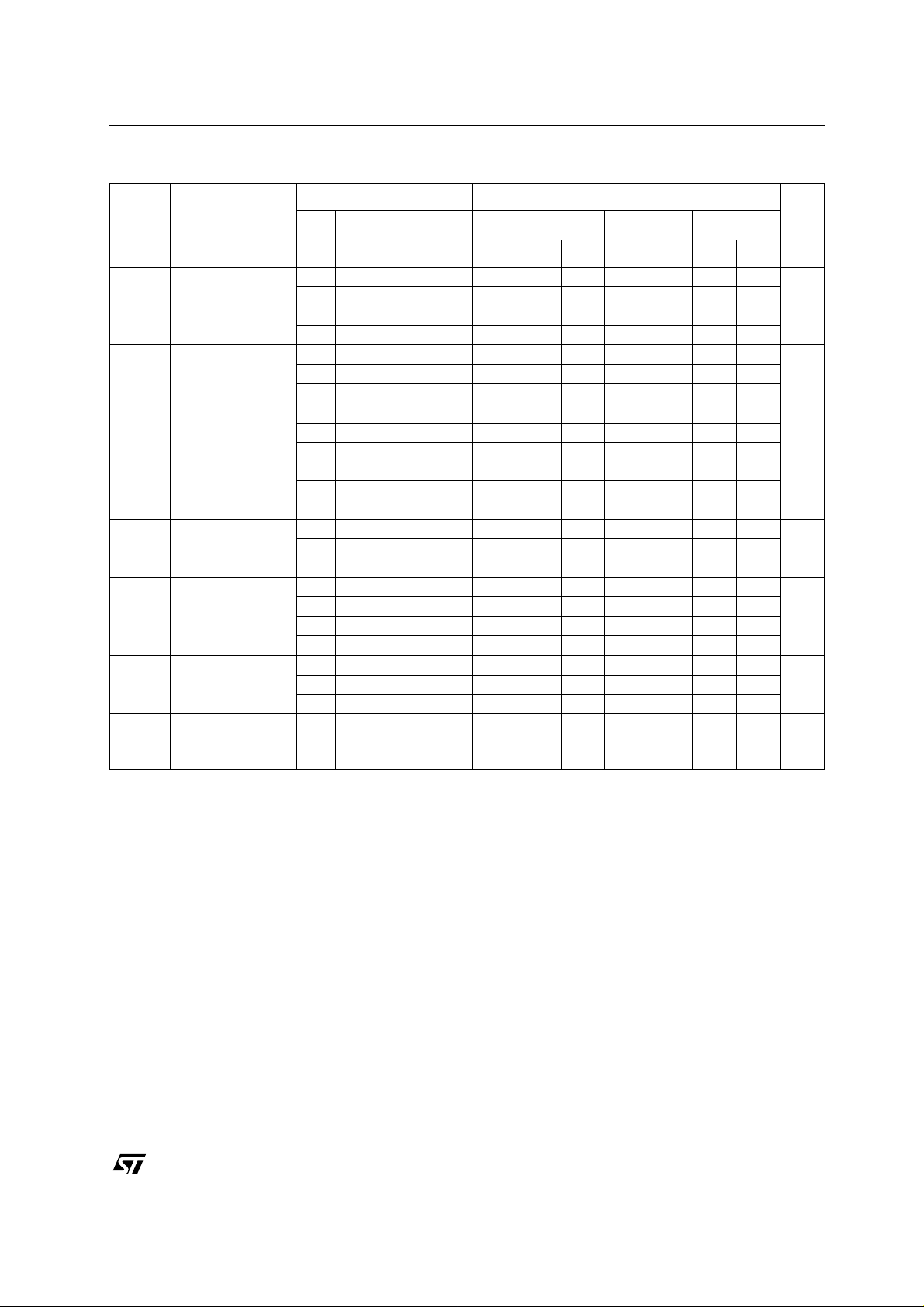

DC SPECIFICATIONS

Test Condition Value

T

Symbol Parameter

I

Quiescent Current 0/5 5 0.02 1 30 30

L

V

(V)

V

I

(V)

|I

|

O

O

(µA)

V

DD

(V)

= 25°C

A

Min. Typ. Max. Min. Max. Min. Max.

0/10 10 0.02 2 60 60

0/15 15 0.02 4 120 120

0/20 20 0.04 20 600 600

V

High Level Output

OH

Voltage

0/5 <1 5 4.95 4.95 4.95

0/15 <1 15 14.95 14.95 14.95

Low Level Output

V

OL

Voltage

5/0 <1 5 0.05 0.05 0.05

15/0 <1 15 0.05 0.05 0.05

High Level Input

V

IH

Voltage

0.5/4.5 <1 5 3.5 3.5 3.5

1.5/13.5 <1 15 11 11 11

V

IL

Low Level Input

Voltage

4.5/0.5 <1 5 1.5 1.5 1.5

13.5/1.5 <1 15 4 4 4

I

OH

Output Drive

Current

0/5 2.5 <1 5 -1.36 -3.2 -1.15 -1.1

0/5 4.6 <1 5 -0.44 -1 -0.36 -0.36

0/10 9.5 <1 10 -1.1 -2.6 -0.9 -0.9

0/15 13.5 <1 15 -3.0 -6.8 -2.4 -2.4

I

OL

Output Sink

Current

0/5 0.4 <1 5 0.44 1 0.36 0.36

0/15 1.5 <1 15 3.0 6.8 2.4 2.4

Input Leakage

I

I

Current

C

Input Capacitance

I

The Noi se Margin for both "1" and "0 " le vel is: 1V min. wi th VDD=5V, 2V min. with VDD=10V, 2.5V min. with VDD=15V

0/18 Any Input 18

Any Input 5 7.5 pF

±10

-5

-40 to 85°C -55 to 125°C

±0.1 ±1 ±1 µA

HCF4013B

Unit

µA

V0/10 <1 10 9.95 9.95 9.95

V10/0 <1 10 0.05 0.05 0.05

V1/9 <1 10 7 7 7

V9/1 <1 10 3 3 3

mA

mA0/10 0.5 <1 10 1.1 2.6 0.9 0.9

3/9