100-watt mono BTL class-D audio amplifier

Features

100-W output power at

THD = 10% with R

80-W output power at

THD = 10% with R

Wide-range single-supply operation (14 - 39 V)

High efficiency (η = 90%)

Four selectable, fixed gain settings of

nominally 25.6 dB, 31.6 dB, 35.1 dB and

37.6 dB

Differential inputs minimize common-mode

noise

Standby and mute features

Short-circuit protection

Thermal overload protection

Externally synchronizable

= 6 Ω and V

L

= 8 Ω and V

L

CC

CC

= 36 V

= 34 V

TDA7498MV

PowerSSO-36

with exposed pad up

Description

The TDA7498MV is a mono BTL class-D audio

amplifier with single power supply designed for

home systems and active speaker applications.

It comes in a 36-pin PowerSSO package with

exposed pad up (EPU) to facilitate mounting a

separate heatsink.

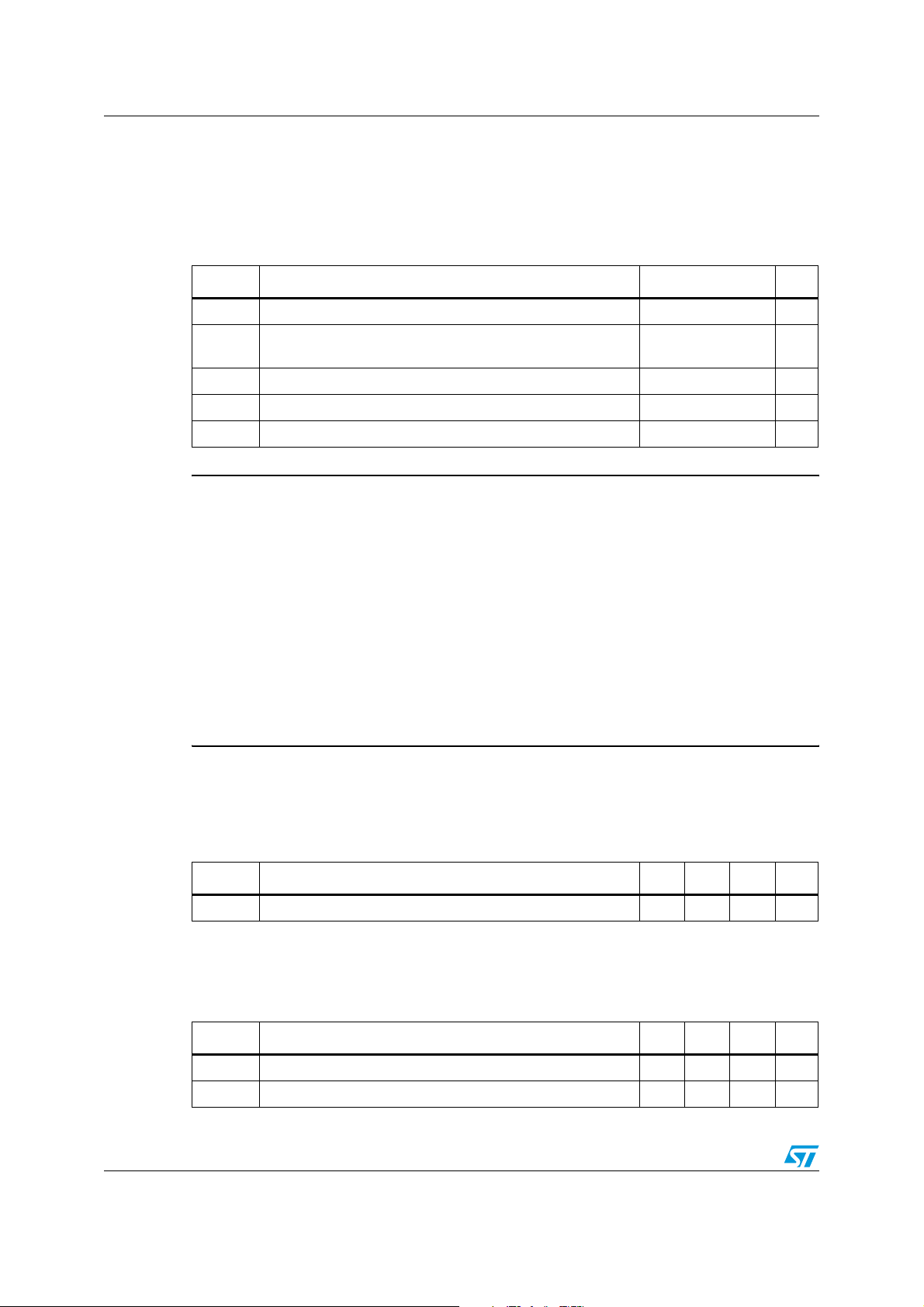

Table 1. Device summary

Order code Temperature range Package Packaging

TDA7498MV -40 to 85 °C PowerSSO-36 (EPU) Tube

TDA7498MVTR -40 to 85 °C PowerSSO-36 (EPU) Tape and reel

January 2011 Doc ID 16505 Rev 3 1/27

www.st.com

27

Contents TDA7498MV

Contents

1 Device block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.1 Pin-out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2 Pin list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.3 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.4 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4 Characterization curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.1 Test board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2 Characterization curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.2.1 For RL = 6 Ω . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

4.2.2 For R

= 8 Ω . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

L

5 Applications information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.1 Applications circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2 Mode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.3 Gain setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.4 Input resistance and capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.5 Internal and external clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.5.1 Master mode (internal clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.5.2 Slave mode (external clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.6 Output low-pass filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.7 Protection function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.8 Diagnostic output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

6 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

7 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2/27 Doc ID 16505 Rev 3

TDA7498MV List of figures

List of figures

Figure 1. Internal block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. Pin connection (top view, PCB view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. Test board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 4. Output power (THD = 10%) vs supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 5. THD vs output power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 6. THD vs frequency (1 W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. THD vs frequency (100 mW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 8. Frequency response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 9. FFT performance (0 dBFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 10. FFT performance (-60 dBFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 11. Output power (THD = 10%) vs supply voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 12. THD vs output power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 13. THD vs frequency (1 W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 14. THD vs frequency (100 mW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 15. Frequency response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 16. FFT performance (0 dB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 17. FFT performance (-60 dB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 18. Applications circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 19. Standby and mute circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 20. Turn-on/off sequence for minimizing speaker “pop” . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 21. Input circuit and frequency response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 22. Master and slave connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 23. Typical LC filter for a 8-Ω speaker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 24. Typical LC filter for a 6-Ω speaker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 25. Behavior of pin DIAG for various protection conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 26. PowerSSO-36 EPU outline drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Doc ID 16505 Rev 3 3/27

List of tables TDA7498MV

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Pin description list. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 5. Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 6. Electrical specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 7. Mode settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 8. Gain settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 9. How to set up SYNCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 10. PowerSSO-36 EPU dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 11. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4/27 Doc ID 16505 Rev 3

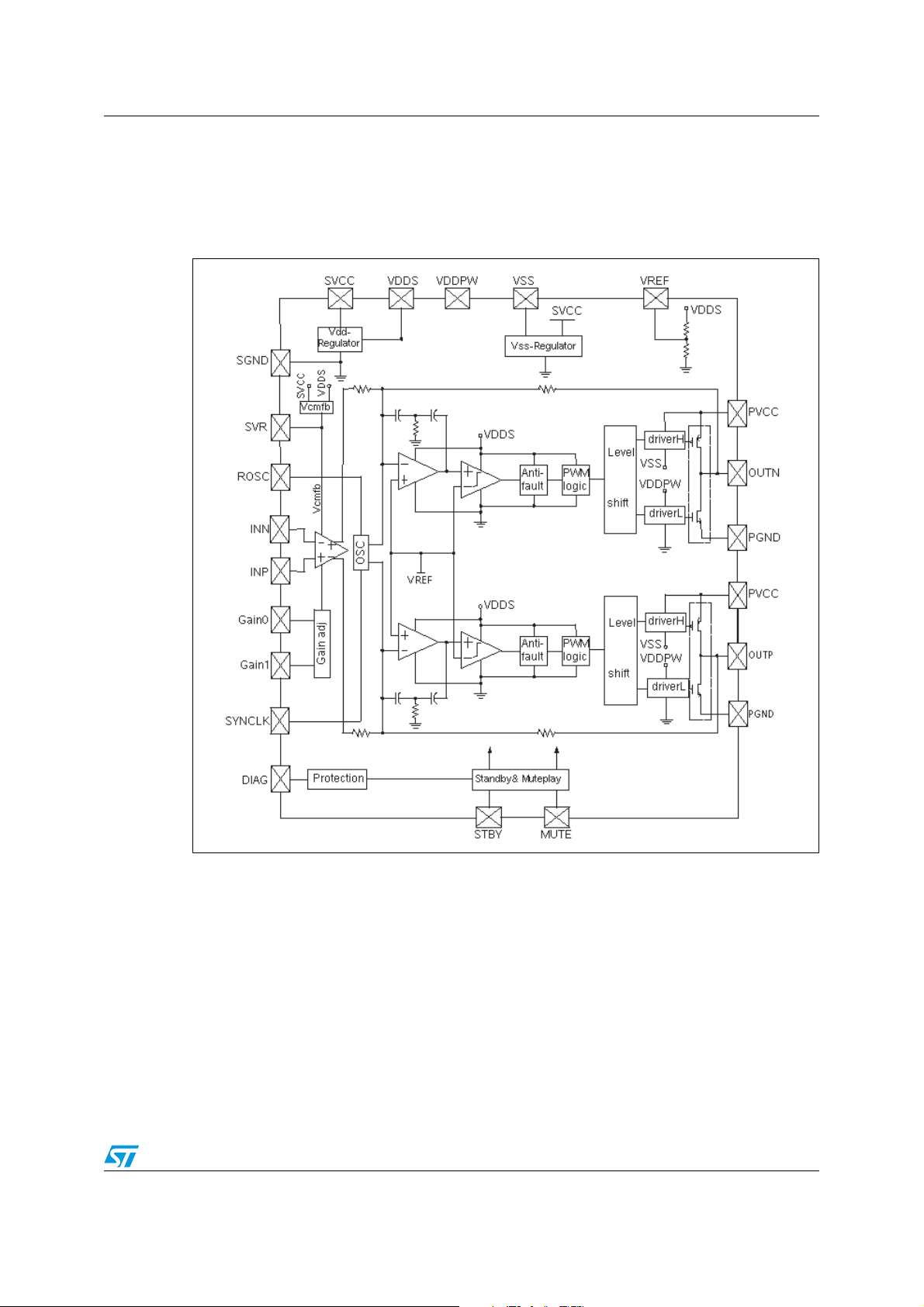

TDA7498MV Device block diagram

1 Device block diagram

Figure 1 shows the block diagram of the TDA7498MV.

Figure 1. Internal block diagram

Doc ID 16505 Rev 3 5/27

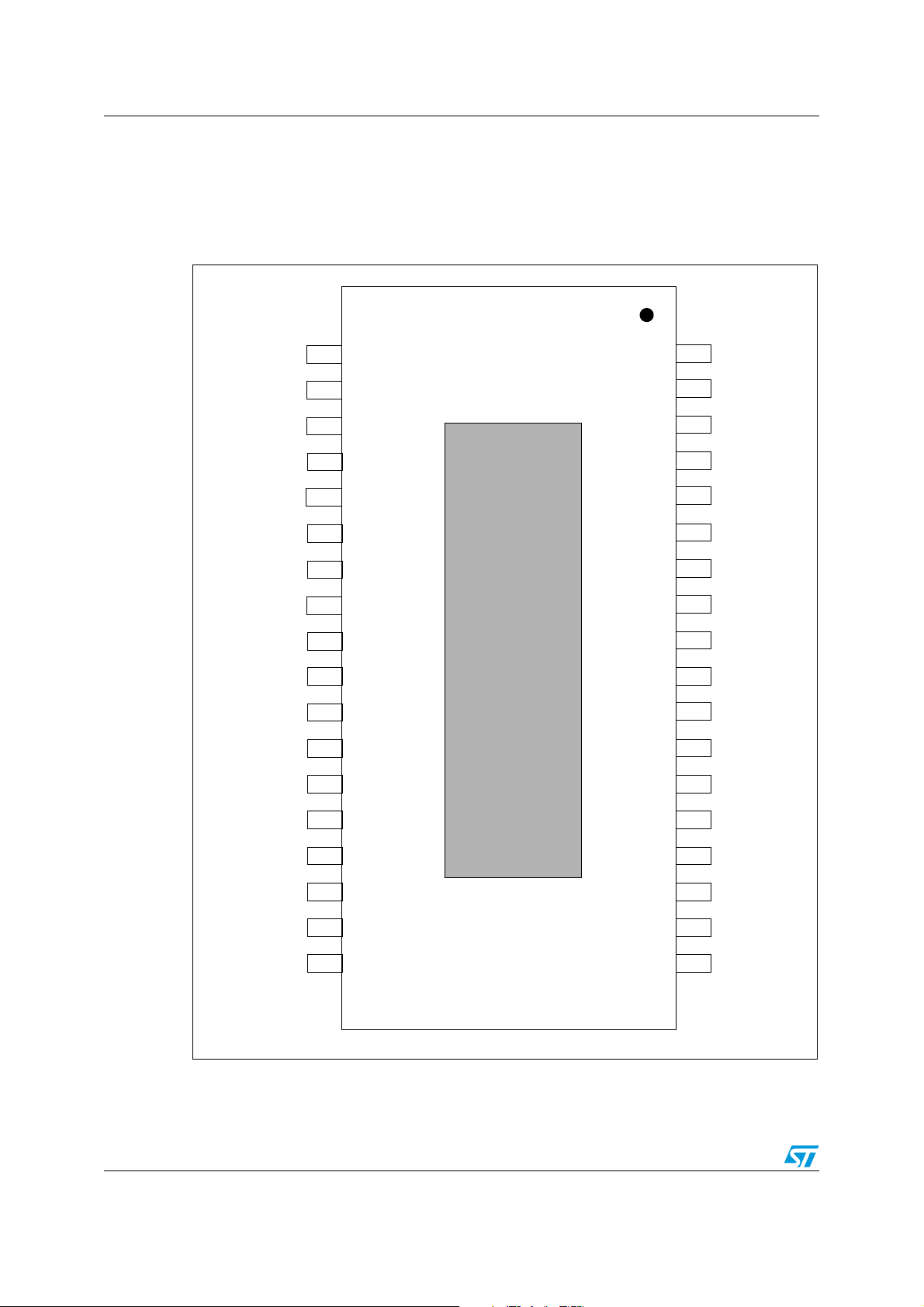

Pin description TDA7498MV

2 Pin description

2.1 Pin-out

Figure 2. Pin connection (top view, PCB view)

36

35

34

33

32

31

30

29

28

27

26

25

24

VSS

SVCC

VREF

SGND2

VDDS2

GAIN1

GAIN0

SVR

DIAG

SGND

VDDS

SYNCLK

ROSC

SUB_GND

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

OUTN

OUTN

PVCC

PVCC

1

2

3

4

5

6

7

8

9

10

11

12

13

23

INN

22

INP

21

MUTE

20

STBY

19

VDDPW

6/27 Doc ID 16505 Rev 3

EP, exposed pad

Connect to ground

PGND

PGND

OUTP

OUTP

PGND

14

15

16

17

18

TDA7498MV Pin description

2.2 Pin list

Table 2. Pin description list

Number Name Type Description

1 SUB_GND PWR Connect to the frame

2,3 N.C. - No internal connection

4,5 N.C. - No internal connection

6,7 N.C. - No internal connection

8,9 N.C. - No internal connection

10,11 OUTN O Negative PWM output for audio channel

12,13 PVCC PWR Power supply for audio channel

14,15 PGND PWR Power stage ground

16,17 OUTP O Positive PWM output for audio channel

18 PGND PWR Power stage ground

19 VDDPW O

3.3-V (nominal) regulator output referred to ground for power

stage

20 STBY I Standby mode control

21 MUTE I Mute mode control

22 INP I Positive differential input

23 INN I Negative differential input

24 ROSC O Master oscillator frequency-setting pin

25 SYNCLK I/O Clock in/out for external oscillator

26 VDDS O

3.3-V (nominal) regulator output referred to ground for signal

blocks

27 SGND PWR Signal ground

28 DIAG O Open-drain diagnostic output

29 SVR O Supply voltage rejection

30 GAIN0 I Gain setting input 1

31 GAIN1 I Gain setting input 2

32 VDDS2 O Connect to VDDS (pin 26)

33 SGND2 PWR Connect to SGND (pin 27)

34 VREF O Half VDDS (nominal) referred to ground

35 SVCC PWR Signal power supply decoupling

36 VSS O 3.3-V (nominal) regulator output referred to power supply

- EP - Exposed pad for heatsink, to be connected to ground

Doc ID 16505 Rev 3 7/27

Electrical specifications TDA7498MV

3 Electrical specifications

3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

V

CC_MAX

V

L_MAX

T

j_MAX

T

op_MAX

T

stg

DC supply voltage for pins PVCCA, PVCCB 44 V

Voltage limits for input pins STBY, MUTE, INNA, INPA,

INNB, INPB, GAIN0, GAIN1

Operating junction temperature 0 to 150 °C

Operating temperature -40 to 85 °C

Storage temperature -40 to 150 °C

-0.3 to 3.6 V

Warning: Stresses beyond those listed under “Absolute maximum

ratings” make cause permanent damage to the device. These

are stress ratings only, and functional operation of the device

at these or any other conditions beyond those indicated

under “Recommended operating condition” are not implied.

Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability. In the real

application, power supply with nominal value rated inside

recommended operating conditions, may experience some

rising beyond the maximum operating condition for short

time when no or very low current is sinked (amplifier in mute

state). In this case the reliability of the device is guaranteed,

provided that the absolute maximum rating is not exceeded.

3.2 Thermal data

Table 4. Thermal data

Symbol Parameter Min Typ Max Unit

R

th j-case

Thermal resistance, junction to case - 2 3 °C/W

3.3 Recommended operating conditions

Table 5. Recommended operating conditions

Symbol Parameter Min Typ Max Unit

V

CC

T

amb

8/27 Doc ID 16505 Rev 3

Supply voltage for pins PVCCA, PVCCB 14 - 39 V

Ambient operating temperature -20 - 85 °C

TDA7498MV Electrical specifications

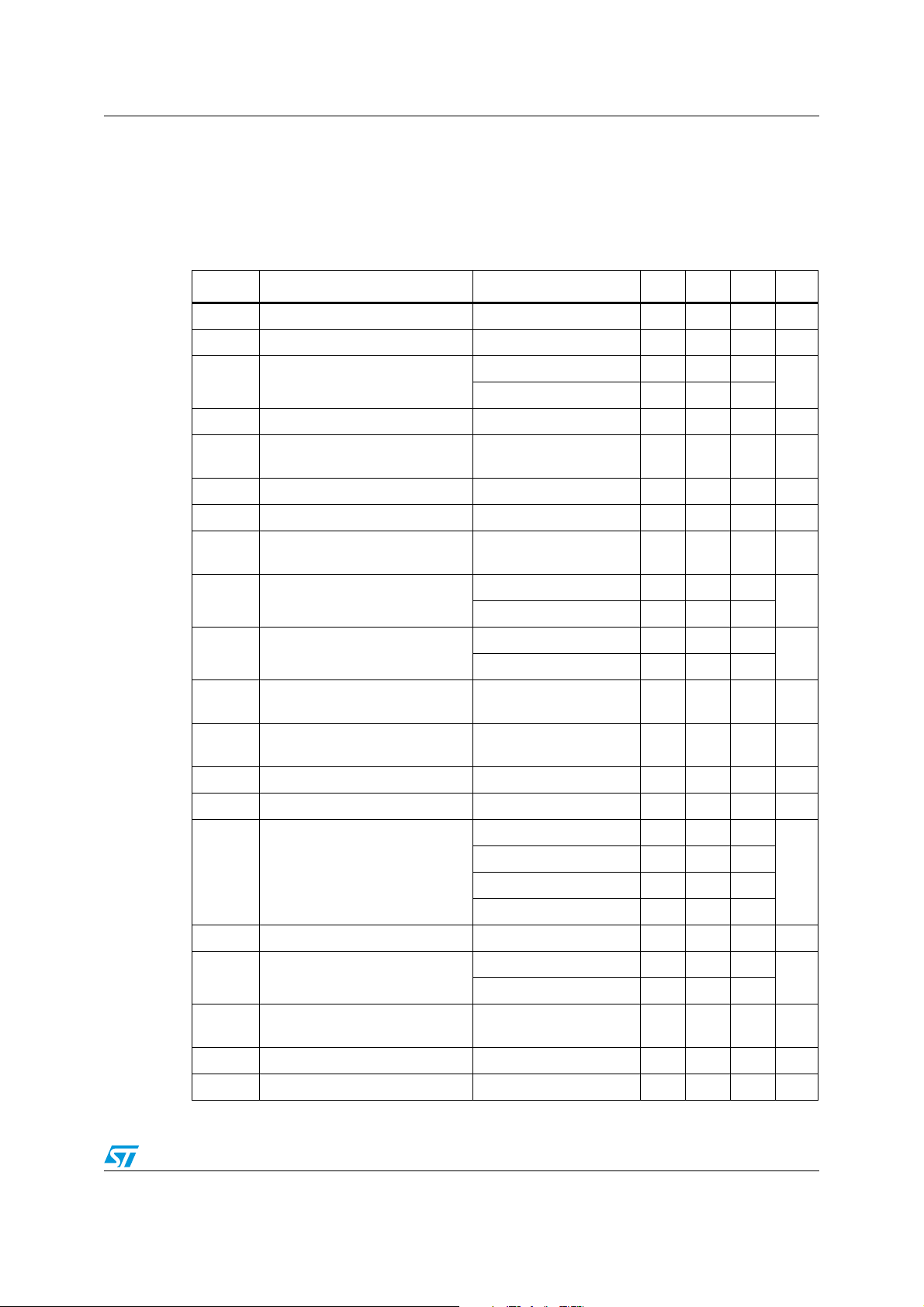

3.4 Electrical specifications

Unless otherwise stated, the results in Ta bl e 6 below are given for the conditions:

V

=36V, RL (load) = 6 Ω, R

CC

Ta mb = 25 ° C.

Table 6. Electrical specifications

Symbol Parameter Condition Min Typ Max Unit

= R3 = 39 kΩ, C8 = 100 nF, f = 1 kHz, GV = 25.6 dB and

OSC

I

q

I

qSTBY

V

OS

I

OCP

T

jS

R

i

V

OVP

V

UVP

R

dsON

P

o

P

o

P

D

Total quiescent current No LC filter, no load - 40 60 mA

Quiescent current in standby - - 1 10 µA

Output offset voltage

Overcurrent protection threshold RL = 0 Ω 5.5 7 - A

Junction temperature at thermal

shutdown

Input resistance Differential input 48 60 - kΩ

Overvoltage protection threshold - 42 43 - V

Undervoltage protection

threshold

Power transistor on resistance

Output power

Output power

Dissipated power

η Efficiency P

THD Total harmonic distortion P

G

∆G

V

V

Closed-loop gain

Gain matching - -1 - 1 dB

eN Total input noise

SVRR Supply voltage rejection ratio

T

f

r

SW

, T

Rise and fall times - - 50 - ns

f

Switching frequency Internal oscillator 290 310 330 kHz

Play mode -100 - 100

mV

Mute mode -60 - 60

- - 150 - °C

- --8V

High side - 0.2 -

Ω

Low side - 0.2 -

THD = 10% - 100 -

W

THD = 1% - 78 -

= 8 Ω, THD = 10%,

R

L

VCC= 36V

P

= 100 W,

o

THD = 10%

= 100 W - 90 - %

o

= 1 W - 0.1 - %

o

-80-W

-10-W

GAIN0 = L, GAIN1 = L 24.6 25.6 26.6

GAIN0 = L, GAIN1 = H 30.6 31.6 32.6

dB

GAIN0 = H, GAIN1 = L 34.1 35.1 36.1

GAIN0 = H, GAIN1 = H 36.6 37.6 38.6

A Curve, G

= 20 dB - 15 -

V

µV

f = 22 Hz to 22 kHz - 25 50

fr = 100 Hz, Vr = 0.5 Vpp,

= 10 µF

C

SVR

-70-dB

Doc ID 16505 Rev 3 9/27

Electrical specifications TDA7498MV

Table 6. Electrical specifications (continued)

Symbol Parameter Condition Min Typ Max Unit

(1)

f

SWR

V

inH

V

inL

Output switching frequency

range

Digital input high (H)

Digital input low (L) - - 0.8

Pin STBY voltage high (H)

V

STBY

Pin STBY voltage low (L) - - 0.5

Pin MUTE voltage high (H)

V

MUTE

A

MUTE

1. fSW = 106 / ((16 * R

2. f

Pin MUTE voltage low (L) - - 0.8

Mute attenuation V

SW

= f

/ 2 with the external oscillator.

SYNCLK

+ 182) * 4) kHz, f

OSC

With internal oscillator

With external oscillator

-

-

-

< 0.8 V - 70 - dB

MUTE

= 2 * fSW with R3 = 39 kΩ (see Figure 18.).

SYNCLK

250 - 400

(2)

250 - 400

2.3 - -

2.9 - -

2.5 - -

kHz

V

V

V

10/27 Doc ID 16505 Rev 3

TDA7498MV Characterization curves

4 Characterization curves

Figure 18 on page 18 shows the test circuit with which the characterization curves, shown in

the next sections, were measured. Figure 3 shows the PCB layout.

4.1 Test board

Figure 3. Test board

Top view Top copper

Bottom view Bottom copper

Doc ID 16505 Rev 3 11/27

Characterization curves TDA7498MV

4.2 Characterization curves

Unless otherwise stated the measurements were made under the following conditions:

V

= 36 V, f = 1 kHz, GV = 25.6 dB, R

CC

4.2.1 For RL = 6 Ω

Figure 4. Output power (THD = 10%) vs supply voltage

Output power (W)

120

110

100

90

80

70

60

50

40

30

20

10

= 39 kΩ, C

OSC

= 100 nF, Tamb = 25 °C.

OSC

+10 +36+12 +14 +16 +18 +20 +22 +24 +26 +28 +30+32+34

Figure 5. THD vs output power

10

5

THD+N (%)

2

1

0.5

0.2

0.1

0.05

0.02

0.01

0.005

100m 200200m 500m 1 2 5 10 20 50 100

Supply voltage (V)

f = 1 kHz

f = 100 Hz

Output power (W)

12/27 Doc ID 16505 Rev 3

TDA7498MV Characterization curves

Figure 6. THD vs frequency (1 W)

2

1

THD+N (%)

0.5

0.2

0.1

0.05

0.02

0.01

20 20k50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

Figure 7. THD vs frequency (100 mW)

2

1

THD+N (%)

0.5

0.2

0.1

0.05

0.02

0.01

20 20k50 100 200 500 1k 2k 5k 10k

Figure 8. Frequency response

+3

+2.5

Ampl (dB)

+2

+1.5

+1

+0.5

+0

-0.5

-1

-1.5

-2

-2.5

-3

10 20k20 50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

Frequency (Hz)

Doc ID 16505 Rev 3 13/27

Characterization curves TDA7498MV

Figure 9. FFT performance (0 dBFS)

+0

-10

-20

FFT (dB)

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

-160

-170

-180

20 20k50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

Figure 10. FFT performance (-60 dBFS)

+0

-10

-20

FFT (dB)

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

-160

-170

-180

20 20k50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

14/27 Doc ID 16505 Rev 3

TDA7498MV Characterization curves

4.2.2 For RL = 8 Ω

Figure 11. Output power (THD = 10%) vs supply voltage

120

Output power (W)

Figure 12. THD vs output power

110

100

90

80

70

60

50

40

30

20

10

+10 +36+12 +14 +16 +18 +20 +22 +24 +26 +28 +30+32+34

10

5

THD+N (%)

2

1

0.5

Supply voltage (V)

0.2

0.1

0.05

0.02

0.01

0.005

100m 200200m 500m 1 2 5 10 20 50 100

Output power (W)

f = 1 kHz

f = 100 Hz

Doc ID 16505 Rev 3 15/27

Characterization curves TDA7498MV

Figure 13. THD vs frequency (1 W)

2

1

THD+N (%)

0.5

0.2

0.1

0.05

0.02

0.01

20 20k50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

Figure 14. THD vs frequency (100 mW)

2

1

THD+N (%)

0.5

0.2

0.1

0.05

0.02

0.01

20 20k50 100 200 500 1k 2k 5k 10k

Figure 15. Frequency response

+3

+2.5

Ampl (dB)

+2

+1.5

+1

+0.5

+0

-0.5

-1

-1.5

-2

-2.5

-3

10 20k20 50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

Frequency (Hz)

16/27 Doc ID 16505 Rev 3

TDA7498MV Characterization curves

Figure 16. FFT performance (0 dB)

))7G%

N N N N N

)UHTXHQF\+]

Figure 17. FFT performance (-60 dB)

+0

-10

-20

FFT (dB)

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

-160

-170

-180

20 20k50 100 200 500 1k 2k 5k 10k

Frequency (Hz)

Doc ID 16505 Rev 3 17/27

18/27 Doc ID 16505 Rev 3

VCC

GND

OUT-1

OUT-2

TDA7498MV

MUTE

STBY

3V3 Power supply

single-ended

*

*

input

CLASS-D AMPLIFIER

*

*

Load = 6 ohm

For

Frequency shift

OUTPUT

INPUT

*

LC filter components

Load

L1,L2 C26 C24,C28

6 ohm

8 ohm

22 µH

22 µH

470 nF

680 nF

220 nF

220 nF

C5

100nF

R3

39K

L4

22µH

C1

1µF

C2

1µF

C8

100nF

C25

100nF

C27

330pF

R6

22R

C40

220nF

C41

220nF

R1

100k

R7

22R

C6

100nF

R4

120k

R2

33k

C26

680nF

C10

100nF

J6

J5

2

1

3

S1

2

1

3

S2

C29

2.2µF

2

GND

1

OUT

3

IN

IC2

L4931CZ33

1

2

J2

J7

+

C23

2200µF

50V

L3

22µH

J4

C30

1µF

R14

100k

R15

8R

C28

220nF

R16

8R

C24

220nF

R13

47k

+

C7

2.2µF

16V

D1

18V

C9

100nF

C4

1nF

C3

1nF

C16

10µF

10V

C17

10µF

10V

R9

180K

1

2

3

Q1

KTC3875(S)

32

VDDS2

36

VSS

9

NC

5

NC

7

NC

3

NC

10

OUTN

12

PVCC

14

PGND

16

OUTP

33

SGND2

8

NC

4

NC

21

MUTE

6

NC

2

NC

29

SVR

11

OUTN

1

SUB_GND

22

INP

23

INN

27

SGND

26

VDDS

28

DIAG

19

VDDPW

18

PGND

20

STBY

24

ROSC

31

GAIN1

35

SVCC

30

GAIN0

25

SYNCLK

17

OUTP

15

PGND

34

VREF

13

PVCC

IC3

TDA7498MV

J3

1

2

J9

R8

6.8k

+

C15

2.2µF

16V

DIAG

3V3

FS

FS

VDDS

VDDS

VDDS

VCC

3V3

5 Applications information

5.1 Applications circuit

Figure 18. Applications circuit

Applications information TDA7498MV

TDA7498MV Applications information

5.2 Mode selection

The three operating modes of the TDA7498MV are set by the two inputs, STBY (pin 20) and

MUTE (pin 21).

z Standby mode: all circuits are turned off, very low current consumption.

z Mute mode: inputs are connected to ground and the positive and negative PWM

outputs are at 50% duty cycle.

z Play mode: the amplifiers are active.

The protection functions of the TDA7498MV are realized by pulling down the voltages of the

STBY and MUTE inputs shown in Figure 19. The input current of the corresponding pins

must be limited to 200 µA.

Table 7. Mode settings

Mode STBY MUTE

Standby L

Mute H

Play H H

1. Drive levels defined in Table 6: Electrical specifications on page 9

(1)

(1)

X (don’t care)

L

Figure 19. Standby and mute circuits

0 V

0 V

Standby

3.3 V

Mute

3.3 V

R2

30 kΩ

R4

30 kΩ

C7

2.2 µF

C15

2.2 µF

STBY

TDA7498MV

MUTE

Figure 20. Turn-on/off sequence for minimizing speaker “pop”

VCC

0

STBY

0

MUTE

0

Input

0

Output

0

Standby Mute Play Mute Standby

I

q

0

t

t

t

t

t

t

Doc ID 16505 Rev 3 19/27

Applications information TDA7498MV

5.3 Gain setting

The gain of the TDA7498MV is set by the two inputs, GAIN0 (pin 30) and GAIN1 (pin31).

Internally, the gain is set by changing the feedback resistors of the amplifier.

Table 8. Gain settings

GAIN0 GAIN1 Nominal gain, Gv (dB)

LL25.6

LH31.6

HL 35.6

HH37.6

5.4 Input resistance and capacitance

The input impedance is set by an internal resistor Ri = 60 kΩ (typical). An input capacitor

(Ci) is required to couple the AC input signal.

The equivalent circuit and frequency response of the input components are shown in

Figure 21. For Ci = 470 nF the high-pass filter cut-off frequency is below 20 Hz:

fC = 1 / (2 * π * Ri * Ci)

Figure 21. Input circuit and frequency response

Input

signal

Input

Ci

pin

Ri

Rf

20/27 Doc ID 16505 Rev 3

TDA7498MV Applications information

5.5 Internal and external clocks

The clock of the class-D amplifier can be generated internally or can be driven by an

external source.

If two or more class-D amplifiers are used in the same system, it is recommended that all

devices operate at the same clock frequency. This can be implemented by using one

TDA7498MV as master clock, while the other devices are in slave mode, that is, externally

clocked. The clock interconnect is via pin SYNCLK of each device. As explained below,

SYNCLK is an output in master mode and an input in slave mode.

5.5.1 Master mode (internal clock)

Using the internal oscillator, the output switching frequency, fSW, is controlled by the

resistor, R

fSW = 106 / ((R

where R

In master mode, pin SYNCLK is used as a clock output pin whose frequency is:

f

SYNCLK

For master mode to operate correctly then resistor R

below in Ta bl e 9 .

, connected to pin ROSC:

OSC

* 16 + 182) * 4) kHz

OSC

is in kΩ.

OSC

= 2 * fSW

must be less than 60 kΩ as given

OSC

5.5.2 Slave mode (external clock)

In order to accept an external clock input the pin ROSC must be left open, that is, floating.

This forces pin SYNCLK to be internally configured as an input as given in Ta bl e 9 .

The output switching frequency of the slave devices is:

f

= f

SW

SYNCLK

Table 9. How to set up SYNCLK

Master R

Slave Floating (not connected) Input

Figure 22. Master and slave connection

/ 2

Mode ROSC SYNCLK

OSC

Master Slave

TDA7498MV

ROSC SYNCLK

Cosc

100 nF

Rosc

39 kΩ

< 60 kΩ Output

TDA7498MV

SYNCLK ROSC

Output

Input

Doc ID 16505 Rev 3 21/27

Applications information TDA7498MV

5.6 Output low-pass filter

To avoid EMI problems, it may be necessary to use a low-pass filter before the speaker. The

cut-off frequency should be larger than 22 kHz and much lower than the output switching

frequency. It is necessary to choose the L and C component values depending on the

loudspeaker impedance. Some typical values, which give a cut-off frequency of 27 kHz, are

shown in Figure 23 and Figure 24 below.

Figure 23. Typical LC filter for a 8-Ω speaker

0?-70

.?-7

0

(U

&P

&N

MHO

(U

Figure 24. Typical LC filter for a 6-Ω speaker

0

?-70

.?-70

(U

&P

&N

M

HO

(U

MHO

&N

&N

MHO

&N

&N

MHO

MHO

&N

&N

MHO

&N

&N

MHO

22/27 Doc ID 16505 Rev 3

TDA7498MV Applications information

5.7 Protection function

The TDA7498MV is fully protected against overvoltages, undervoltages, overcurrents and

thermal overloads as explained here.

Overvoltage protection (OVP)

If the supply voltage exceeds the value for V

given in Table 6: Electrical specifications on

OVP

page 9 the overvoltage protection is activated which forces the outputs to the

high-impedance state. When the supply voltage falls back to within the operating range the

device restarts.

Undervoltage protection (UVP)

If the supply voltage drops below the value for V

specifications on page 9 the undervoltage protection is activated which forces the outputs to

the high-impedance state. When the supply voltage recovers to within the operating range

the device restarts.

given in Table 6: Electrical

UVP

Overcurrent protection (OCP)

If the output current exceeds the value for I

page 9 the overcurrent protection is activated which forces the outputs to the

high-impedance state. Periodically, the device attempts to restart. If the overcurrent

condition is still present then the OCP remains active. The restart time, T

by the R-C components connected to pin STBY.

given in Table 6: Electrical specifications on

OCP

, is determined

OC

Thermal protection (OTP)

If the junction temperature, Tj, reaches 145 °C (nominally), the device goes to mute mode

and the positive and negative PWM outputs are forced to 50% duty cycle. If the junction

temperature reaches the value for T

device shuts down and the output is forced to the high-impedance state. When the device

cools sufficiently the device restarts.

given in Table 6: Electrical specifications on page 9 the

j

5.8 Diagnostic output

The output pin DIAG is an open drain transistor. When any protection is activated it switches

to the high-impedance state. The pin can be connected to a power supply (< 39 V) by a pullup resistor whose value is limited by the maximum sinking current (200 µA) of the pin.

Figure 25. Behavior of pin DIAG for various protection conditions

VDD

Overcurrent

protection

VDD

TDA7498MV

Protection logic

Restart

Doc ID 16505 Rev 3 23/27

DIAG

R1

OV, UV, OT

protection

Restart

Package mechanical data TDA7498MV

6 Package mechanical data

The TDA7498MV comes in a 36-pin PowerSSO package with exposed pad up (EPU).

Figure 26 shows the package outline and Ta bl e 1 0 gives the dimensions.

Table 10. PowerSSO-36 EPU dimensions

Dimensions in mm Dimensions in inches

Symbol

Min Typ Max Min Typ Max

A 2.15 - 2.45 0.085 - 0.096

A2 2.15 - 2.35 0.085 - 0.093

a1 0 - 0.10 0 - 0.004

b 0.18 - 0.36 0.007 - 0.014

c 0.23 - 0.32 0.009 - 0.013

D 10.10 - 10.50 0.398 - 0.413

E 7.40 - 7.60 0.291 - 0.299

e - 0.5 - - 0.020 -

e3 - 8.5 - - 0.335 -

F - 2.3 - - 0.091 -

G- - 0.10 - - 0.004

H 10.10 - 10.50 0.398 - 0.413

h- - 0.40 - - 0.016

k 0 - 8 degrees - - 8 degrees

L 0.60 - 1.00 0.024 - 0.039

M - 4.30 - - 0.169 -

N - - 10 degrees - - 10 degrees

O - 1.20 - - 0.047 -

Q - 0.80 - - 0.031 -

S - 2.90 - - 0.114 -

T - 3.65 - - 0.144 -

U - 1.00 - - 0.039 -

X 4.10 - 4.70 0.161 - 0.185

Y 4.90 - 7.10 0.193 - 0.280

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

24/27 Doc ID 16505 Rev 3

Doc ID 16505 Rev 3 25/27

Figure 26. PowerSSO-36 EPU outline drawing

TDA7498MV Package mechanical data

h x 45°

Revision history TDA7498MV

7 Revision history

Table 11. Document revision history

Date Revision Changes

30-Nov-2009 1 Initial release.

Removed datasheet preliminary status, updated features list and

updated device summary table on page 1

28-Jul-2010 2

27-Jan-2011 3 Updated applications circuit in Figure 18 on page 18.

Added operating temperature range to Table 3 on page 8

Updated minimum supply voltage and temperature range in Ta bl e 5:

Recommended operating conditions on page 8

Updated voltage for logical 1 on pin STBY in Table 6 on page 9

26/27 Doc ID 16505 Rev 3

TDA7498MV

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 16505 Rev 3 27/27

Loading...

Loading...