WLL and ISDN-TA subscriber line interface circuit

Features

■ Monochip subscriber line interface circuit

(SLIC) optimised for WLL and VoIP

applications

■ Implement all key features of the BORSHT

function

■ Single supply (5.5 V to 12 V)

■ Built in DC/DC converter controller

■ Soft battery reversal with programmable

transition time.

■ On-hook transmission.

■ Programmable off-hook detector threshold

■ Metering pulse generation and filter

■ Integrated ringing

■ Integrated ring trip

■ Parallel control interface (3.3 V logic level)

■ Programmable constant current feed

■ Surface mount package

■ Integrated thermal protection

■ Dual gain value option

■ BCD III S, 90 V technology

■ -40 to +85 °C operating range

STLC3055N

LQFP44

generate the negative battery by means of an

on chip DC/DC converter controller that drives an

external MOS switch.

The battery level is properly adjusted depending

on the operating mode. A useful characteristic for

these applications is the integrated ringing

generator.

The control interface is a parallel type with open

drain output and 3.3 V logic levels.

The metering pulses are generated on chip

starting from two logic signals (0 and 3.3 V) one

define the metering pulse frequency and the other

the metering pulse duration. An on chip circuit

then provides the proper shaping and filtering.

Metering pulse amplitude and shaping (rising and

decay time) can be programmed by external

components. A dedicated cancellation circuit

avoid possible codec input saturation due to

metering pulse echo.

Description

The STLC3055N is a SLIC device specifically

designed for wireless local loop (WLL) and ISDNterminal adaptors (ISDN-TA) and VoIP

applications. One of the distinctive characteristic

of this device is the ability to operate with a single

supply voltage (from 5.5 V to 12 V) and self

Table 1. Device summary

Order code

E-STLC3055N

1. ECOPACK® (see Section 10)

February 2009 Rev 11 1/34

(1)

Constant current feed can be set from 20 mA to

40 mA. Off-hook detection threshold is

programmable from 5 mA to 9 mA.

The device, developed in BCD III S technology

(90 V process), operates in the extended

temperature range and integrates a thermal

protection that sets the device in power down

when T

Package Packing

LQFP44 Tray

exceeds 140 °C.

j

www.st.com

1

Contents STLC3055N

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.1 Absolute maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2 Operating range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.3 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.1 DC/DC converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4.2 Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.2.1 Power down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.2.2 High impedance feeding (HI-Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.2.3 Active . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.2.4 Ringing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.1 Layout recommendation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.2 External components list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.3 Application diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

6.1 Test circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7 Overvoltage protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8 Typical state diagram for STLC3055N operation . . . . . . . . . . . . . . . . . 30

9 STLC3055Q vs STLC3055N compatibility. . . . . . . . . . . . . . . . . . . . . . . 31

9.1 Typical power consumption comparison . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.2 Hardware differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9.3 Parameter differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

10 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

11 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2/34

STLC3055N List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. Operating range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 5. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 6. SLIC operating modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 7. Gain set in active mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 8. SLIC states in active mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 9. CREST factor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 10. External components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 11. External components @gain set = 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 12. External components @gain set = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 13. Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 14. Power consumption differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 15. Hardware differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 16. Parameter differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 17. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3/34

List of figures STLC3055N

List of figures

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. Pin connection (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. DC characteristic in HI-Z mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 4. DC characteristic in active mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 5. TIP/RING typical transition from direct to reverse polarity . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 6. Metering pulse generation circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. TIP/RING typical ringing waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 8. Application diagram with metering pulse generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 9. Application diagram without metering pulse generation . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 10. 2W return loss 2WRL = 20Log(|Zref + Zs|/|Zref-Zs|) = 20Log(E/2Vs) . . . . . . . . . . . . . . . . 26

Figure 11. THL trans hybrid loss THL = 20Log|Vrx/Vtx|. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 12. G24 transmit gain G24 = 20Log|2Vtx/E| . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 13. G42 receive gain G42 = 20Log|VI/Vrx| . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 14. PSRRC power supply rejection Vpos to 2W port PSSRC = 20Log|Vn/Vl| . . . . . . . . . . . . . 27

Figure 15. L/T longitudinal to transversal conversion L/T = 20Log|Vcm/Vl| . . . . . . . . . . . . . . . . . . . . . 27

Figure 16. T/L transversal to longitudinal conversion T/L = 20Log|Vrx/Vcm|. . . . . . . . . . . . . . . . . . . . 28

Figure 17. VTTX metering pulse level on line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 18. V2Wp and W4Wp: idle channel psophometric noise at line and TX.

V2Wp = 20Log|Vl/0.774l|; V4Wp = 20Log|Vtx/0.774l| . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 19. Simplified configuration for indoor overvoltage protection . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 20. Standard overvoltage protection configuration for K20 compliance . . . . . . . . . . . . . . . . . . 29

Figure 21. State diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 22. LQFP44 (10 x 10 x 1.4 mm) mechanical data and package dimensions . . . . . . . . . . . . . . 32

4/34

STLC3055N Block diagram

1 Block diagram

Figure 1. Block diagram

PD D0 D1 D2 DET

GAIN

SETTING

TX

RX

ZAC1

ZAC

RS

ZB

CKTTX

CTTX1

CTTX2

FTTX

INPUT LOGIC AND DECODER

Status and functions

SUPERVISION

AC PROC

TTX PROC

RTTX CAC ILTF RD IREF RLIM RTH

REFERENCE

OUTPUT LOGIC

LINE

DRIVER

Vcc

Vss

Agnd

OUTPUT

STAGE

DC PROC

DC/DC

CONV.

VOLT.

REG.

AGND

BGND

TIP

RING

CREV

CSVR

CLK

RSENSE

GATE

VF

CVCC

VPOS

VBAT

Vbat

5/34

Pin description STLC3055N

2 Pin description

Figure 2. Pin connection (top view)

VBAT1

CREV

N.C.

TIP

N.C.

N.C.

RING

N.C.

VBAT

BGND

33

CSVR

32

ILTF

31

RD

30

RTH

29

IREF

28

RLIM

27

AGND

26

CVCC

25

VPOS

24

RSENSE

23

GATE

TX

D00TL488-MOD

VF

CLK

GAIN SET

N.C.

N.C.

DET

CKTTX

CTTX1

CTTX2

44 43 42 413940 38 37 36 35 34

1

D0

2

D1

3

D2

4

PD

5

6

7

8

9

10

12 13 14 15 16

RX

RTTX

FTTX

ZAC1

ZAC

N.C.

171118 19 20 21 22

ZB

RS

CAC

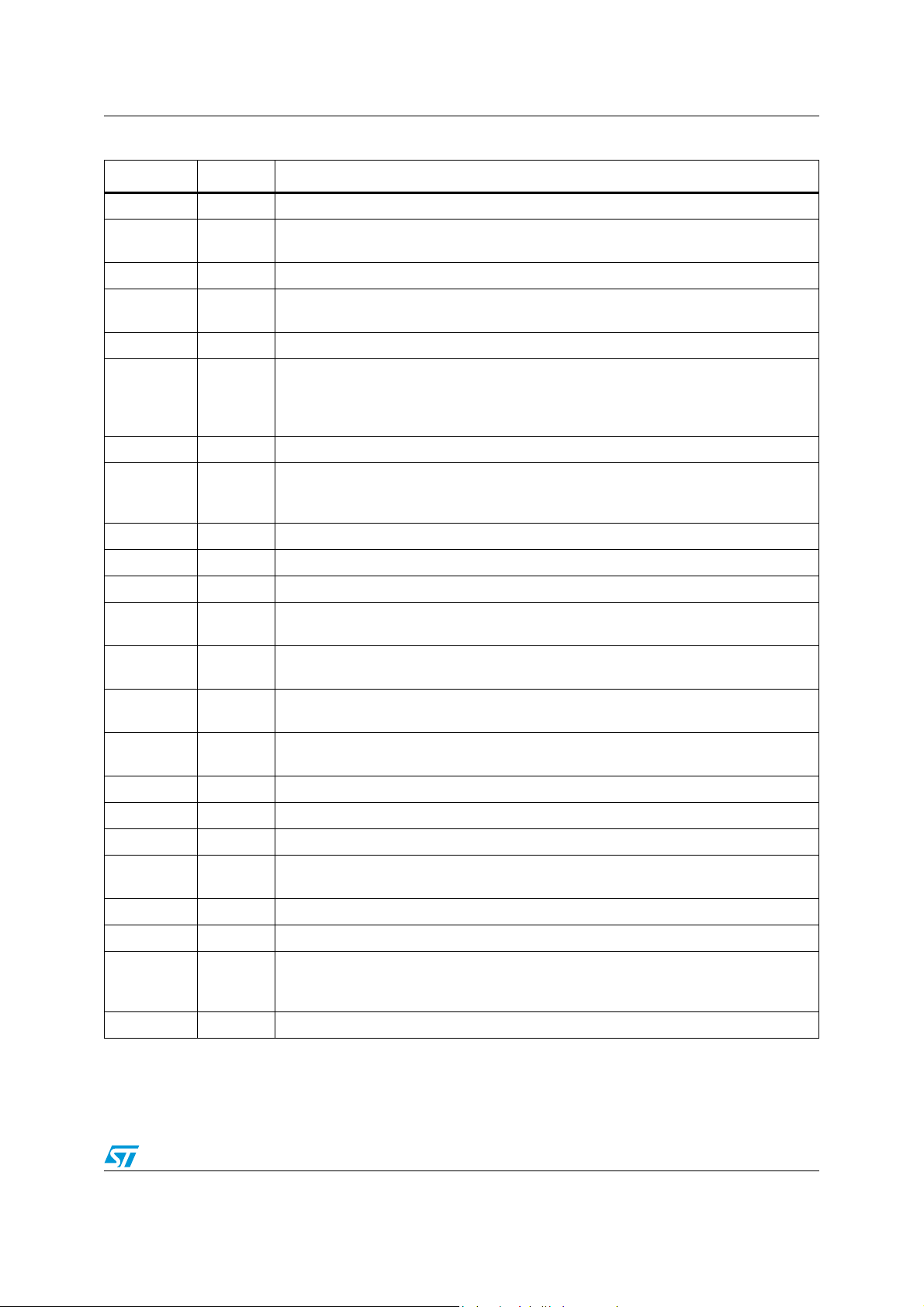

Table 2. Pin description

N° Pin Function

1 D0 Control Interface: input bit 0.

2 D1 Control Interface: input bit 1.

3 D2 Control interface: input bit 2.

4 PD Power down input. Normally connected to CVCC (or to logic level high).

5 Gain SET

6,7,36,

38,39,40,42

Control gain interface: 0 Level R

NC Not connected.

1 Level R

= 0dB T

xgain

= +6dB T

xgain

xgain

xgain

= -6dB

= -12dB

8 DET Logic interface output of the supervision detector (active low).

9 CKTTX Metering pulse clock input (12 KHz or 16KHz square wave).

10 CTTX1 Metering burst shaping external capacitor.

11 CTTX2 Metering burst shaping external capacitor.

12 RTTX

13 FTTX

Metering pulse cancellation buffer output. TTX filter network should be connected to

this point. If not used should be left open.

Metering pulse buffer input this signal is sent to the line and used to perform TTX

filtering.

4 wire input port (RX input). A 100 kΩ external resistor must be connected to AGND to

14 RX

bias the input stage. This signal is referred to AGND. If connected to single supply

CODEC output it must be DC decoupled with proper capacitor.

15 ZAC1 RX buffer output, (the AC impedance is connected from this node to ZAC).

16 ZAC AC impedance synthesis.

6/34

STLC3055N Pin description

Table 2. Pin description (continued)

N° Pin Function

17 RS Protection resistors image (the image resistor is connected from this node to ZAC).

18 ZB

19 CAC AC feedback input, AC/DC split capacitor (CAC).

20 TX

21 VF Feedback input for DC/DC converter controller.

22 CLK

23 GATE Driver for external Power MOS transistor (P-channel).

24 RSENSE

25 VPOS Positive supply

26 CVCC Internal positive voltage supply filter.

27 AGND Analog ground, must be shorted with BGND.

28 RLIM

29 IREF

30 RTH

Balance network for 2 to 4 wire conversion (the balance impedance ZB is connected

from this node to AGND. ZA impedance is connected from this node to ZAC1).

4 wire output port (TX output). The signal is referred to AGND. If connected to single

supply CODEC input it must be DC decoupled with proper capacitor.

Power switch controller clock (typ. 125 kHz). This pin can also be connected to CVCC

or AGND. When the CLK pin is connected to CVCC an auto-oscillation is internally

generated and it is used instead of the external clock. When the CLK pin is connected

to AGND, the GATE output is disabled.

Voltage input for current sensing. RSENSE should be connected close to this pin and

VPOS pin. The PCB layout should minimize the extra resistance introduced by the

copper tracks.

Constant current feed programming pin (via RLIM). RLIM should be connected close to

this pin and AGND pin to avoid noise injection.

Internal bias current setting pin. RREF should be connected close to this pin and

AGND pin to avoid noise injection.

Off-hook threshold programming pin (via RTH). RTH should be connected close to this

pin and AGND pin to avoid noise injection.

31 RD

32 ILTF Transversal line current image output.

33 CSVR Battery supply filter capacitor.

34 BGND Battery ground, must be shorted with AGND.

35 VBAT

37 RING 2 wire port; RING wire (Ib is the current sunk into this pin).

41 TIP 2 wire port; TIP wire (Ia is the current sourced from this pin).

43 CREV

44 VBAT1 Frame connection. Must be shorted to VBAT.

DC feedback and ring trip input. RD should be connected close to this pin and AGND

pin to avoid noise injection.

Regulated battery voltage self generated by the device via DC/DC converter. Must be

shorted to VBAT1.

Reverse polarity transition time control. One proper capacitor connected between this

pin and AGND is setting the reverse polarity transition time. This is the same transition

time used to shape the "trapezoidal ringing" during ringing injection.

7/34

Electrical specification STLC3055N

3 Electrical specification

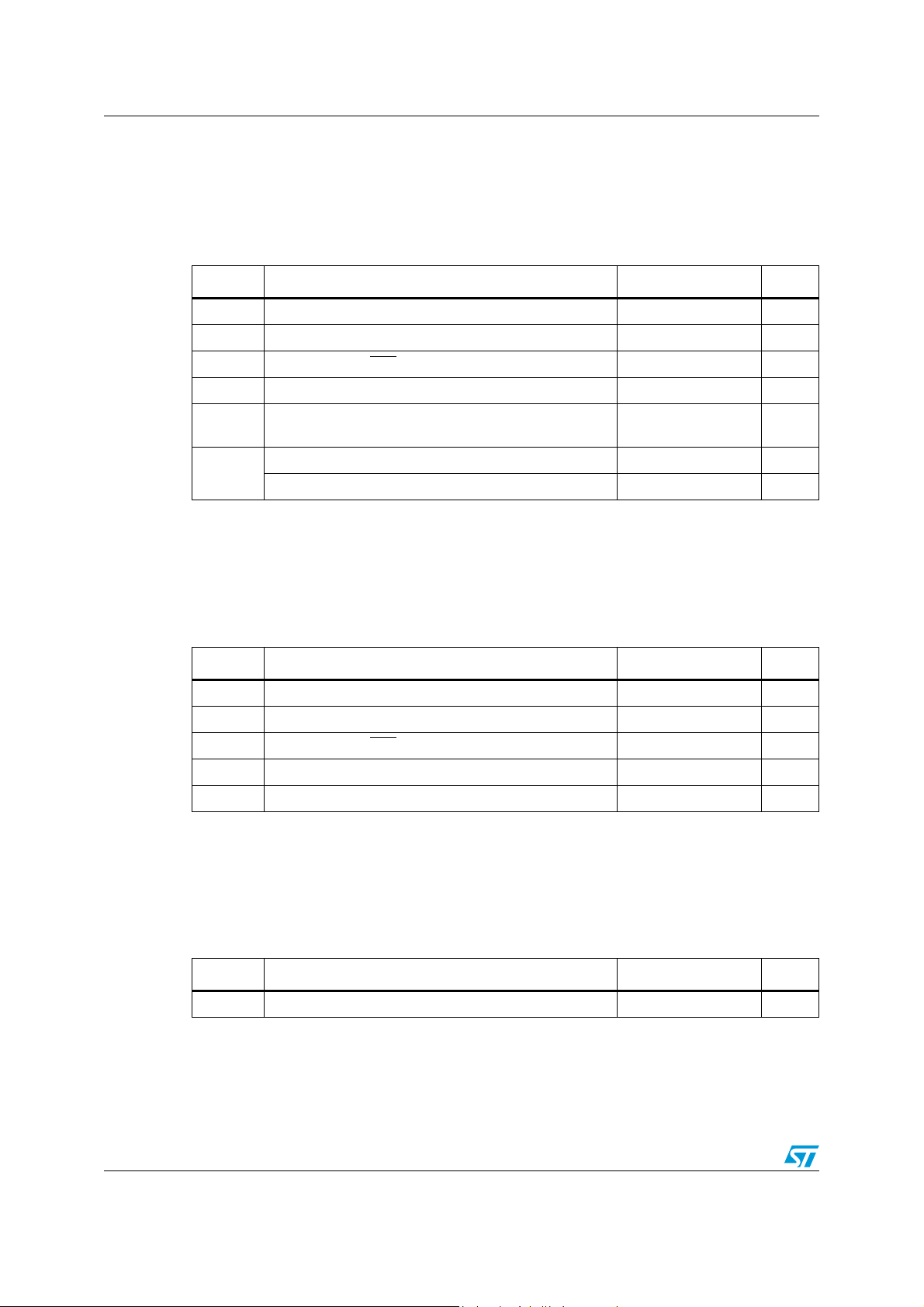

3.1 Absolute maximum rating

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

V

Positive supply voltage -0.4 to +13 V

pos

A/BGND AGND to BGND -1 to +1 V

V

V

btot

ESD

RATING

1. Vbat is self generated by the on chip DC/DC converter and can be programmed via RF1 and RF2.

RF1 and RF2 shall be selected in order to fulfil the a.m limits (see Table 10: External components on

page 17).

Pin D0, D1, D2, DET, CKTTX -0.4 to 5.5 V

dig

T

Max. junction temperature 150 °C

j

Vbtot=|Vpos|+|Vbat|. (Total voltage applied to the device

(1)

supply pins).

Human body model ±1750 V

Charged device model ±500 V

3.2 Operating range

Table 4. Operating range

Symbol Parameter Value Unit

V

A/BGND AGND to BGND -100 to +100 mV

V

T

V

bat

1. Vbat is self generated by the on chip DC/DC converter and can be programmed via RF1 and RF2.

RF1 and RF2 shall be selected in order to fulfill the a.m limits (see Table 10: External components on

page 17).

Positive supply voltage 5.5 to +12 V

pos

Pin D0, D1, D2, DET, CKTTX, PD -0.25 to 5.25 V

dig

Ambient operating temperature range -40 to +85 °C

op

(1)

Self generated battery voltage -74 max. V

90 V

3.3 Thermal data

Table 5. Thermal data

Symbol Parameter Value Unit

R

th j-amb

8/34

Thermal resistance junction to ambient Typ. 60 °C/W

STLC3055N Functional description

4 Functional description

The STLC3055N is a device specifically developed for WLL VoIP and ISDN-TA applications.

It is based on a SLIC core, on purpose optimised for these applications, with the addition of

a DC/DC converter controller to fulfil the WLL and ISDN-TA design requirements.

The SLIC performs the standard feeding, signalling and transmission functions.

It can be set in four different operating modes via the D0, D1, D2 pins of the control logic

interface (0 to 3.3 V logic levels). The loop status is carried out on the DET

pin (active low).

The DET

pin is an open drain output to allow easy interfacing with both 3.3 V and 5 V logic

levels.

The four possible SLIC’s operating modes are:

● Power down

● High impedance feeding (HI-Z)

● Active

● Ringing

Ta bl e 6 shows how to set the different SLIC operating modes.

Table 6. SLIC operating modes.

PD D0 D1 D2 Operating mode

000XPower down

1 0 0 X H.I. feeding (HI-Z)

1 0 1 0 Active normal polarity

1011Active reverse polarity

1 1 1 0 Active TTX injection (N.P.)

1 1 1 1 Active TTX injection (R.P.)

1 1 0 0/1 Ring (D2 bit toggles @ fring)

4.1 DC/DC converter

The DC/DC converter controller is driving an external power MOS transistor (P-channel) in

order to generate the negative battery voltage needed for device operation.

The DC/DC converter controller is synchronised with an external CLK (125 kHz typ.) or with

an internal clock generated when the pin CLK is connected to CVCC. One sensing resistor

in series to Vpos supply allows to fix the maximum allowed input peak current. This feature

is implemented in order to avoid overload on Vpos supply in case of line transient (ex. ring

trip detection).

The typical value is obtained for a sensing resistor equal to 110 mΩ that will guarantee an

average current consumption from Vpos < 700 mA. When in on-hook the self generated

battery voltage is set to a predefined value.

This value can be adjusted via one external resistor (RF1) and it is typical -50 V. When

RING mode is selected this value is increased to -70 V typ.

9/34

Functional description STLC3055N

Once the line goes in off-hook condition, the DC/DC converter automatically adjust the

generated battery voltage in order to feed the line with a fixed DC current (programmable via

RLIM) optimising in this way the power dissipation.

4.2 Operating modes

4.2.1 Power down

When this mode is selected the SLIC is switched off and the TIP and RING pins are in high

impedance. Also the line detectors are disabled therefore the off-hook condition cannot be

detected.

This mode can be selected in emergency condition when it is necessary to cut any current

delivered to the line.

This mode is also forced by STLC3055N in case of thermal overload (T

In this case the device goes back to the previous status as soon as the junction temperature

decrease under the hysteresis threshold.

No AC transmission is possible in this mode.

4.2.2 High impedance feeding (HI-Z)

This operating mode is normally selected when the telephone is in on-hook in order to

monitor the line status keeping the power consumption at the minimum.

The output voltage in on-hook condition is equal to the self generated battery voltage (-50 V

typ).

When off-hook occurs the DET

The off-hook threshold in HI-Z mode is the same value as programmed in ACTIVE mode.

The DC characteristic in HI-Z mode is just equal to the self generated battery with

2x(1600 Ω+Rp) in series (see Figure 3), where Rp is the external protection resistance.

No AC transmission is possible in this mode.

Figure 3. DC characteristic in HI-Z mode.

becomes active (low logic level).

IL

Vbat

2x(R1+Rp)

Slope: 2x(R1+Rp)

(R1=1600ohm)

> 140 °C).

j

4.2.3 Active

DC characteristics and supervision

When this mode is selected the STLC3055N provides both DC feeding and AC

transmission.

10/34

VL

Vbat (-50V)

STLC3055N Functional description

The STLC3055N feeds the line with a constant current fixed by RLIM (20 mA to 40 mA

range). The on-hook voltage is typically 40 V allowing on-hook transmission; the self

generated Vbat is -50 V typ.

If the loop resistance is very high and the line current cannot reach the programmed

constant current feed value, the STLC3055N behaves like a 40 V voltage source with a

series impedance equal to the protection resistors 2xRp (typ. 2 x 50 Ω). Figure 4 shows the

typical DC characteristic in Active mode.

Figure 4. DC characteristic in active mode

IL

Ilim

(20 to

40mA)

2Rp

10V

Vbat (-50V)

VL

The line status (on/off-hook) is monitored by the SLIC’s supervision circuit. The off-hook

threshold can be programmed via the external resistor RTH in the range from 5 mA to 9 mA.

Independently on the programmed constant current value, the TIP and RING buffers have a

current source capability limited to 80 mA typ. Moreover the power available at Vbat is

controlled by the DC/DC converter that limits the peak current drawn from the Vpos supply.

The maximum allowed current peak is set by R

SENSE

resistor.

AC characteristics

The SLIC provides the standard SLIC transmission functions:

Once in active mode the SLIC can operate with two different Tx, Rx Gain. Setting properly

by the gain set control bit (see Ta bl e 7 ).

Table 7. Gain set in active mode

Gain set 4 to 2 wire gain 2 to 4 wire gain Impedance synthesis scale factor

0 0 dB -6 dB x 50

1 +6 dB -12 dB x 25

● Input impedance synthesis: can be real or complex and is set by a scaled (x 50 or

x 25) external ZAC impedance.

● Transmit and receive: The AC signal present on the 2W port (TIP and RING pins) is

transferred to the TX output with a -6 dB or -12 dB gain and from the RX input to the

2W port with a 0 dB or +6 dB gain.

● 2 to 4 wire conversion: The balance impedance can be real or complex, the proper

cancellation is obtained by means of two external impedance ZA and ZB

Once in Active mode (D1=1) the SLIC can operate in different states setting properly D0 and

D2 control bits (see also Ta bl e 8 ).

11/34

Loading...

Loading...