ST STiH207 User Manual

STiH207

Advanced dual HD AVC processor with integrated low power standby controller

Features

■ST40 applications CPU with 256 KB L2 cache

■32-bit LMI supporting DDR2/DDR3

■Decoding of H264, MPEG2, VC-1 and AVS HD video streams

■Decoding of 1080p60 AVC, dual HD AVC and MVC SHP video streams

■3DTV decoding and display compatible with HDMI 1.4a

■Extensive connectivity (2 × USB 2.0 ports; Ethernet MII/RMII/TMII port; SD/MMC card port; eSATA port; PCIe)

■Secure booting from SLC NAND Flash or Serial NOR Flash; eMMC booting option

■Low-power process and architecture

■Integrated low power standby controller

Data brief

■High-quality video resizing and de-interlacing

■Integrated Ethernet PHY

Description

The STiH207 uses the latest process technology to provide a cost-effective, feature rich, highly integrated SoC for Set-Top Boxes (STBs). It is targeted at the advanced decoding STB market across all networks (Cable/Satellite/DTT/x-DSL/IP) worldwide and is suitable both for operator markets (with advanced security) and retail markets.

The STiH207 provides a solution for operators and manufacturers to specify a range of costeffective, high performance STBs including basic zappers, interactive STBs, IP clients, and DVR STBs with content delivery possible using broadcast or broadband networks or both (Hybrid STBs).

|

|

Resets |

Analog out |

|

|

|

|

|

|

|

||

|

|

Clocks |

PCM I/O |

STB peripherals I/O |

|

|

|

|

|

|||

JTAG |

Modes |

S/PDIF out |

external interrupts |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

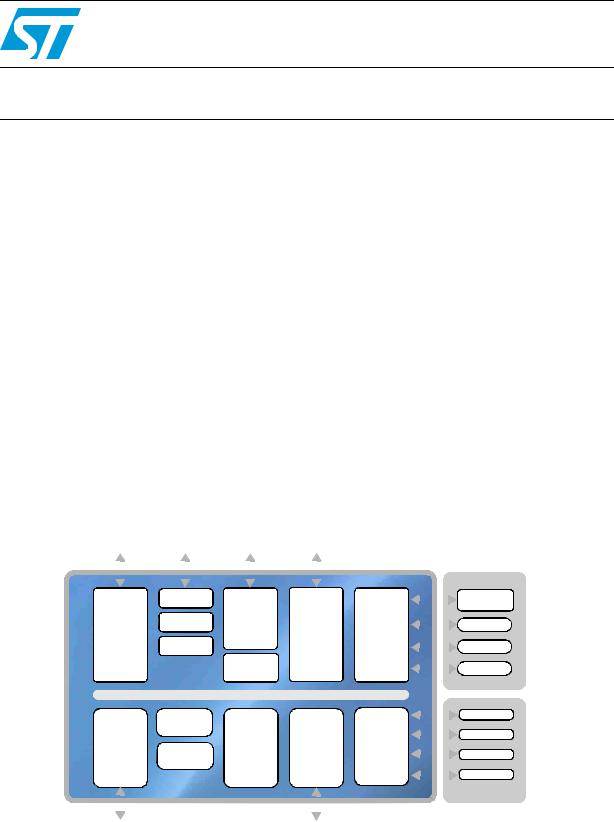

CPU/FPU |

Clock Gen |

Audio I/O |

Peripherals |

System |

|

|

|

SLC NAND Flash |

||||

|

|

System serv |

PCM Players |

SSC |

interfaces |

|

|

|

||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

||||

|

|

Dual FDMA |

UART |

|

|

|

|

|

||||

|

|

PCM Reader |

EMI |

|

|

|

Serial Flash |

|||||

|

|

RTC |

|

|

|

|||||||

|

|

|

|

DACs |

|

|

|

|||||

|

|

|

|

PWM |

SPI |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

L2 cache |

|

|

GPIOs |

|

|

|

|

CI-Plus cards |

||

|

|

|

|

IR/UHF |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Audio decoder |

Smartcard |

|

|

|

|

|

||

|

|

|

|

Key scan |

DDR3 LMI |

|

|

|

|

|||

|

|

|

|

ST231 CPU |

|

|

|

DDR2/DDR3 |

||||

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

STBus |

|

|

|

|

|

|

|

|

Transport |

Video decoder |

Display |

Video I/O |

|

|

|

|

Dual USB |

||||

|

|

|

|

|||||||||

Security |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Low power |

|

|

|

|

|

|

|

|

eSATA/PCI-E |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

Connectivity |

|

|

|

Ethernet |

||

|

|

standby |

|

|

|

|

|

|

|

|||

|

|

controller |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SD-MMC/SDIO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Transport streams |

|

|

|

|

Analog video |

|

|

|

|

|

||

Parallel/serial in/out |

|

|

|

|

HDMI |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

October 2011 |

Doc ID 022309 Rev 1 |

1/4 |

For further information contact your local STMicroelectronics sales office. |

www.st.com |

|

Introduction |

STiH207 |

|

|

1 Introduction

The STiH207 offers current users of ST’s growing family of advanced decoding ICs enhancements in performance and features, enabling operators to offer consumers new multimedia-rich services and viewing experiences, including new 3DTV features. Faster DDR3 memory is also supported, and the applications CPU benefits from an L2 cache. The STiH207 keeps pace with the latest advanced security requirements of the main CA vendors, and an integrated standby controller enables the STiH207 to target stringent low power regulations.

Features |

|

Benefits |

|

|

|

ST40 applications CPU, with 32KI and 32KD L1 caches and 256K L2 cache.

Integrated low power standby controller within its own power island.

High performance processing up to 1020 DMIPS(1) for applications and middleware.

Secure hibernation to, and fast resume from, very low power passive standby mode, targeting STB standby power < 0.5 W.

Latest generation of ST's Delta video decoder with an ST231-based multi-codec capable controller, coupled with a High Quality Video Display Pipeline (HQVDP).

Decoding of advanced high definition standards (MPEG2, H264, VC-1, AVS) plus the performance and flexibility for web-based content decoding such as Flash®, DivX™, MJPEG and Real®, without impacting applications CPU performance.

Dual USB 2.0 hosts, eSATA, Ethernet MAC with MII/RMII/TMII interfaces, PCI-e, SD-MMC/SDIO interface.

Extensive high speed connectivity for the widest range of STB peripherals, such as Flash drives, external HDDs, Ethernet, home network controllers (such as MoCA®, Wi-Fi), DOCSIS® modem and memory cards.

Decoding of 1080p60 AVC, dual HD AVC and MVC SHP video streams.

Enables advanced high-definition viewing experiences including full resolution per eye 3DTV, full-HD 2D services and HD picture-in-picture support (HD-PIP).

NOCS1.0/1.1/1.2/3.0, NSK2.0 and DVB-CSA3 |

Fully compliant with the latest advanced security |

ready. |

requirements of CA vendors. |

1. Frequency for extended mode to be confirmed after silicon characterization.

2/4 |

Doc ID 022309 Rev 1 |

Loading...

Loading...