4-channel digital audio system with FFX™ driver

Features

High efficiency FFX™ class-D modulator

100-dB dynamic range

Two stereo channels with I

interface

16-bit stereo ADC input with PGA and

microphone biasing

Analog and digital muxing/mixing capability

4-channel input sample rate converter

(8 kHz to 192 kHz)

Four channels of 24-bit audio processing

Flexible channel mapping and routing

Output configurations:

–2.0

–2.1

–4.0

–Mono

Embedded CMOS bridge: up to 0.5 W/channel

pfStart™ for pop-free single-ended operations

Play and record simultaneous operation

Pre and post mix stages

Individual channel and master gain/attenuation

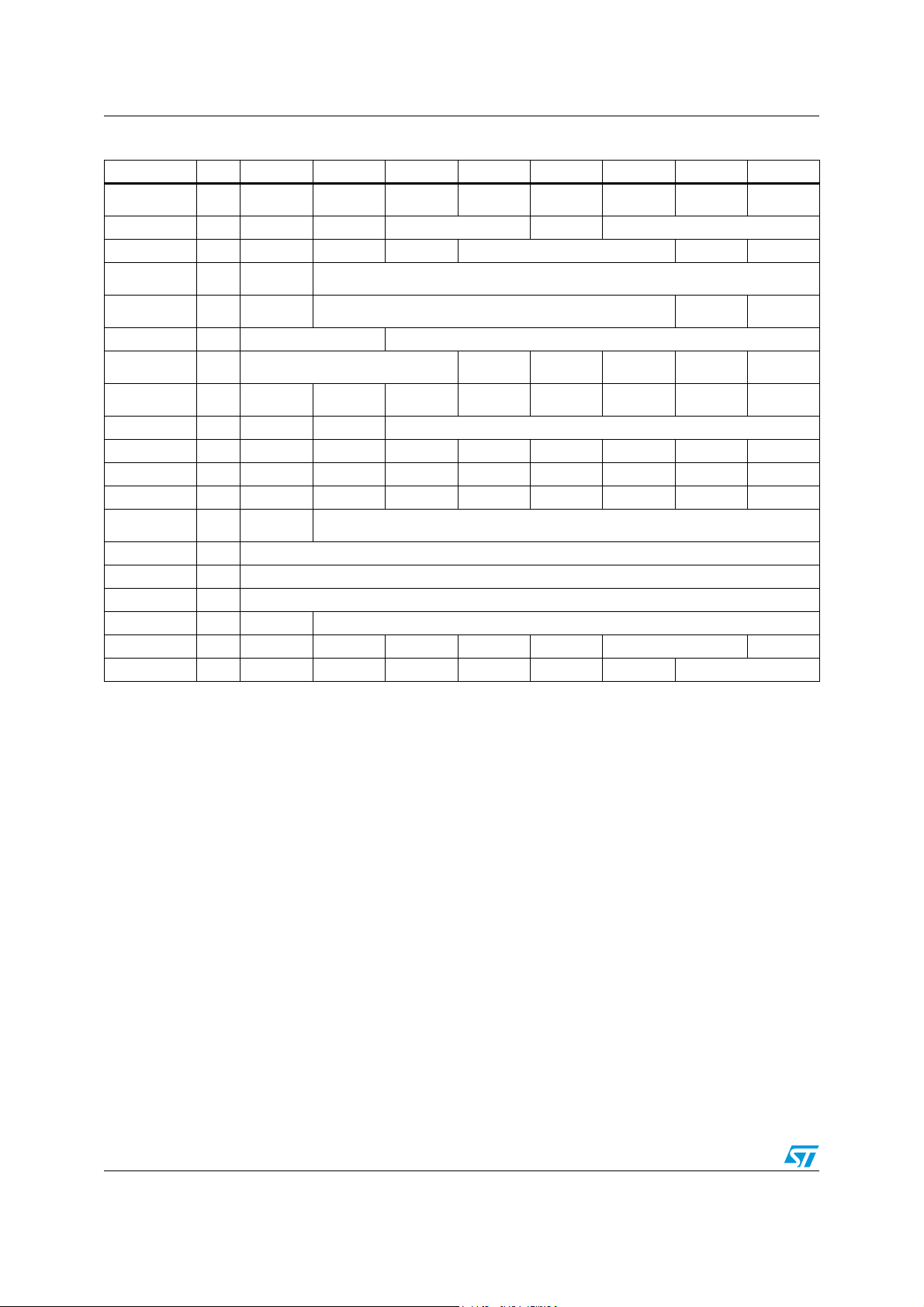

Table 1. Device summary

2

S input/output data

STA321

LQFP-64 package

with exposed pad down (EPD)

Digital gain/attenuation -105 dB to +36 dB in

0.5-dB steps

Soft volume update and muting

DC-blocking selectable high-pass filter

Selectable de-emphasis filter

Up to 13 28-bit user programmable biquads

(EQ) per channel

Bass/treble tone control

Ternary, binary or phase shift modulation

PWM output

Headphone output with jack detector

2

I

C control.

Order code Temperature range Package Packaging

STA321 0 to 70 °C LQFP-64 EPD Tray

STA321TR 0 to 70 °C LQFP-64 EPD Tape and reel

October 2009 Doc ID 15351 Rev 3 1/157

www.st.com

1

Contents STA321

Contents

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.4 Embedded crystal oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.5 Embedded DC regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4 Power-up and power-down sequences . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.1 Device power-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2 Software power-down mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.1 Configuration example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.3 Hardware power-down mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.3.1 Mild power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3.2 Full power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5 Clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.1 System clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.1.1 Configuration example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.2 Peripheral clock manager . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.3 Fractional PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.3.1 PLL block description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.3.2 Output frequency computation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6 Digital processing stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.1 Signal processing flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2 Sampling rate converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.3 Pre-EQ mix 1 and post-EQ mix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

6.3.1 Presets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.4 Pre scaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2/157 Doc ID 15351 Rev 3

STA321 Contents

6.4.1 Presets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.5 Equalization, tone control and effects . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6.6 Biquads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.6.1 Presets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.7 High-pass filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.8 Deemphasis filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

6.9 Bass and treble control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.9.1 Configuration example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.10 Programmable delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.10.1 Presets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.11 Volume and mute control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.12 Limiter (clamping) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.13 FFX channel re-mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.14 Memory programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.14.1 Writing one coefficient/location to RAM . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.14.2 Writing a set of five coefficients/locations to RAM . . . . . . . . . . . . . . . . . 45

6.14.3 Reading a set of five coefficients/locations from RAM . . . . . . . . . . . . . . 46

6.14.4 RAM mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

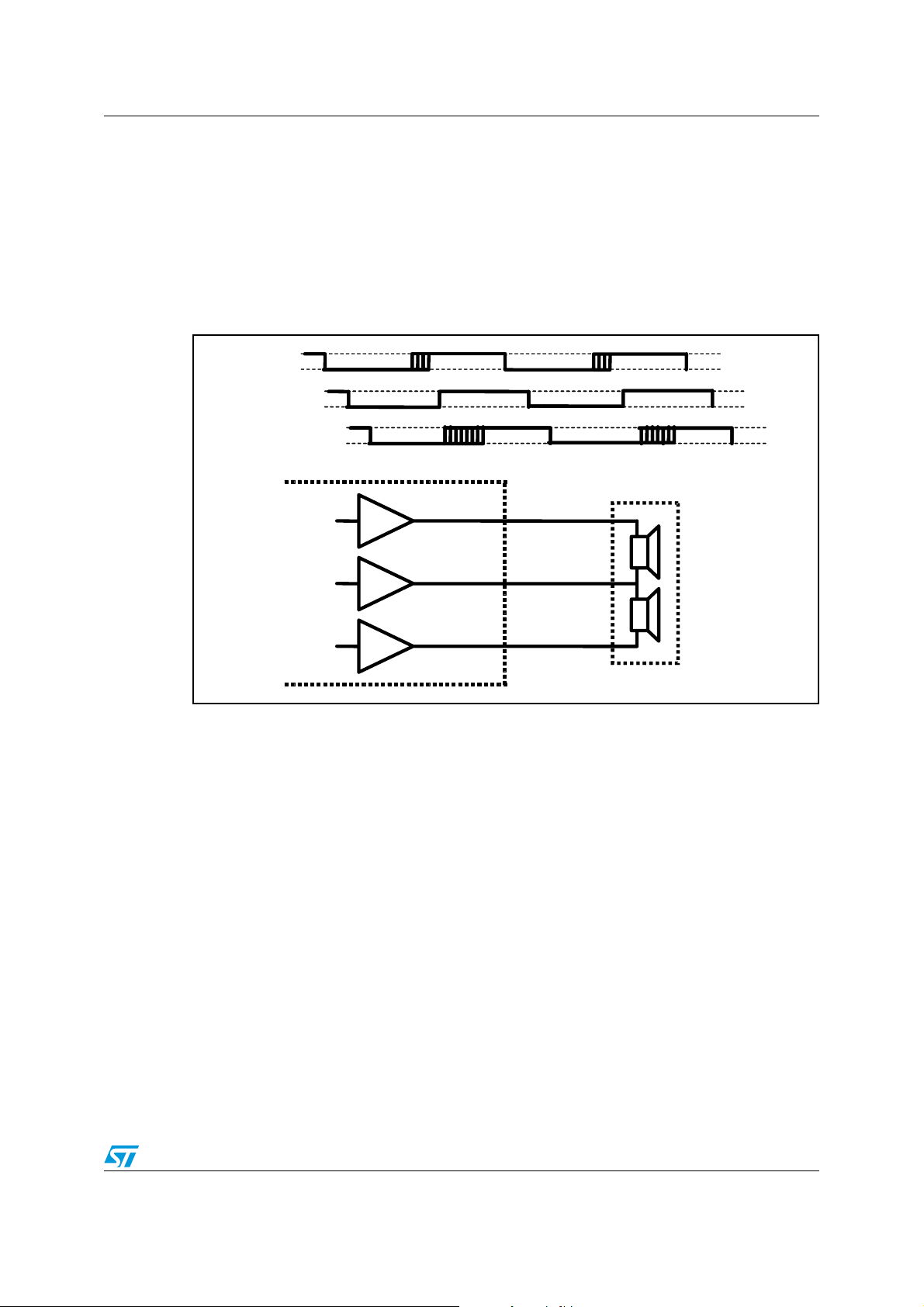

7 FFX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.1 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.2 Modulation schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.3 PWM shift feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

7.4 Ternary mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

7.5 Minimum pulse limitation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

7.6 Headphone modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

7.7 pfStart™ operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

7.8 PWM00 output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

8 CMOS power stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

9 Fault detection and recovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

9.1 External amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

9.2 CMOS bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Doc ID 15351 Rev 3 3/157

Contents STA321

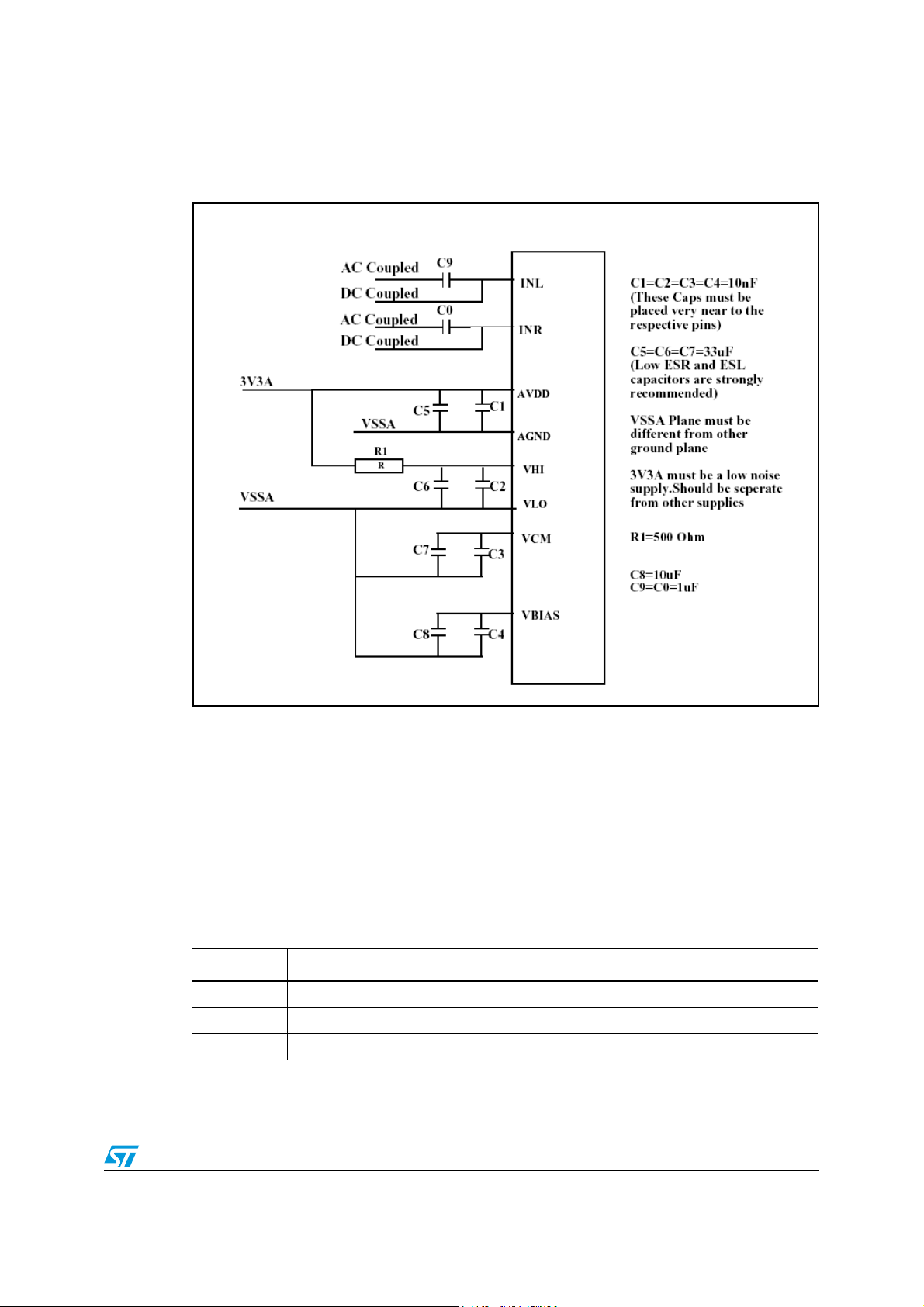

10 ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

10.2 Application schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

10.2.1 Configuration example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

11 Serial audio interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

11.1 Master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

11.2 Slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

11.3 Serial formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

11.3.1 Right justified . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

11.3.2 Left justified . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

11.3.3 DSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

11.3.4 I

11.3.5 PCM/IF (non-delayed mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

11.3.6 PCM/IF (delayed mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

2

S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

11.4 Invalid detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

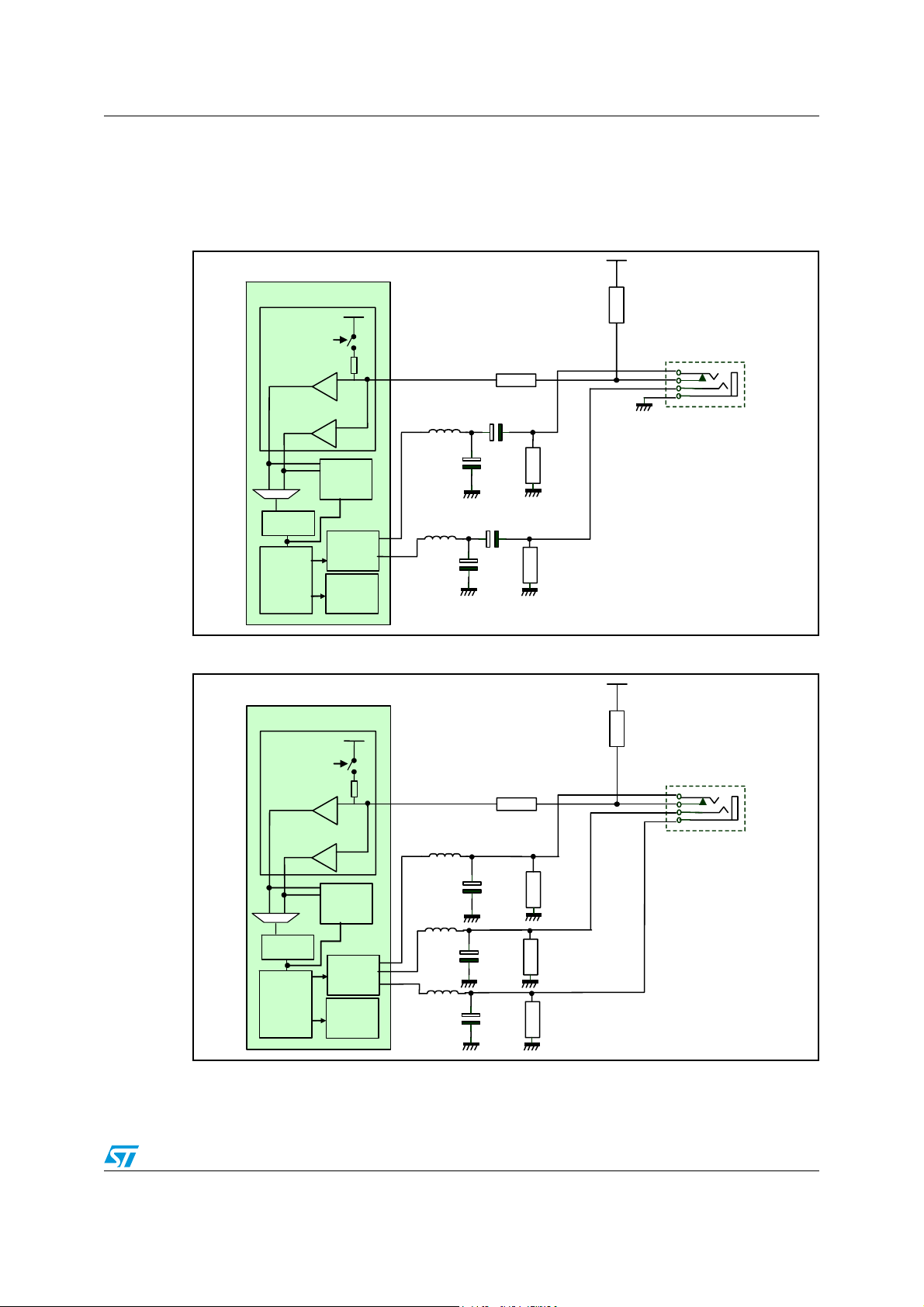

12 Headphone detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

12.1 Applications circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

12.2 Configuration example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

13 I2C interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1 Communication protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.1 Data transition and change . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.2 Start condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.3 Stop condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.4 Data input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.5 Device addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.6 Write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

13.1.7 Read operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

14 Register description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

15 I2C disabled (microless) mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

16 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

4/157 Doc ID 15351 Rev 3

STA321 Contents

17 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

18 Trademarks and other acknowledgements . . . . . . . . . . . . . . . . . . . . . 155

19 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Doc ID 15351 Rev 3 5/157

List of tables STA321

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

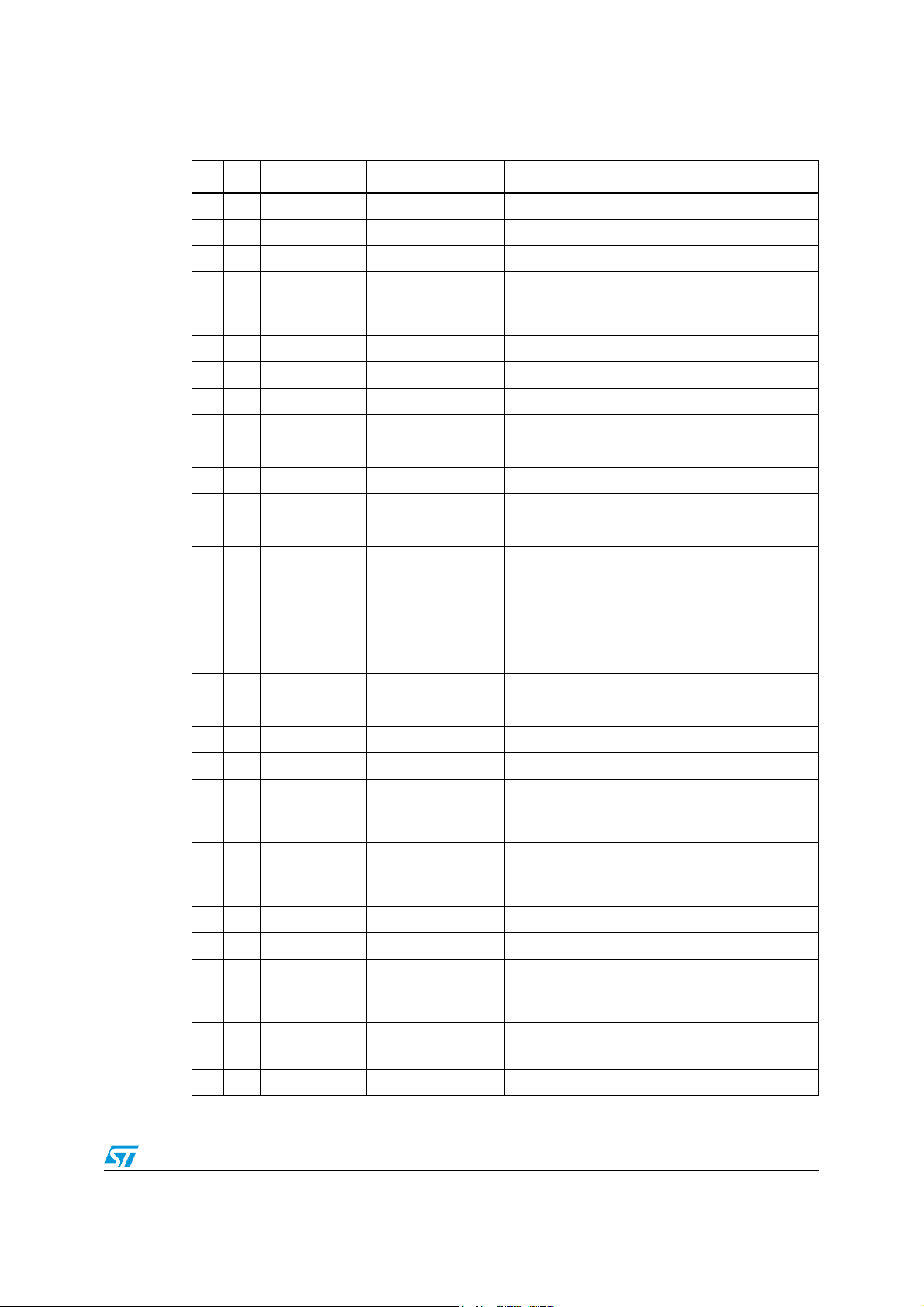

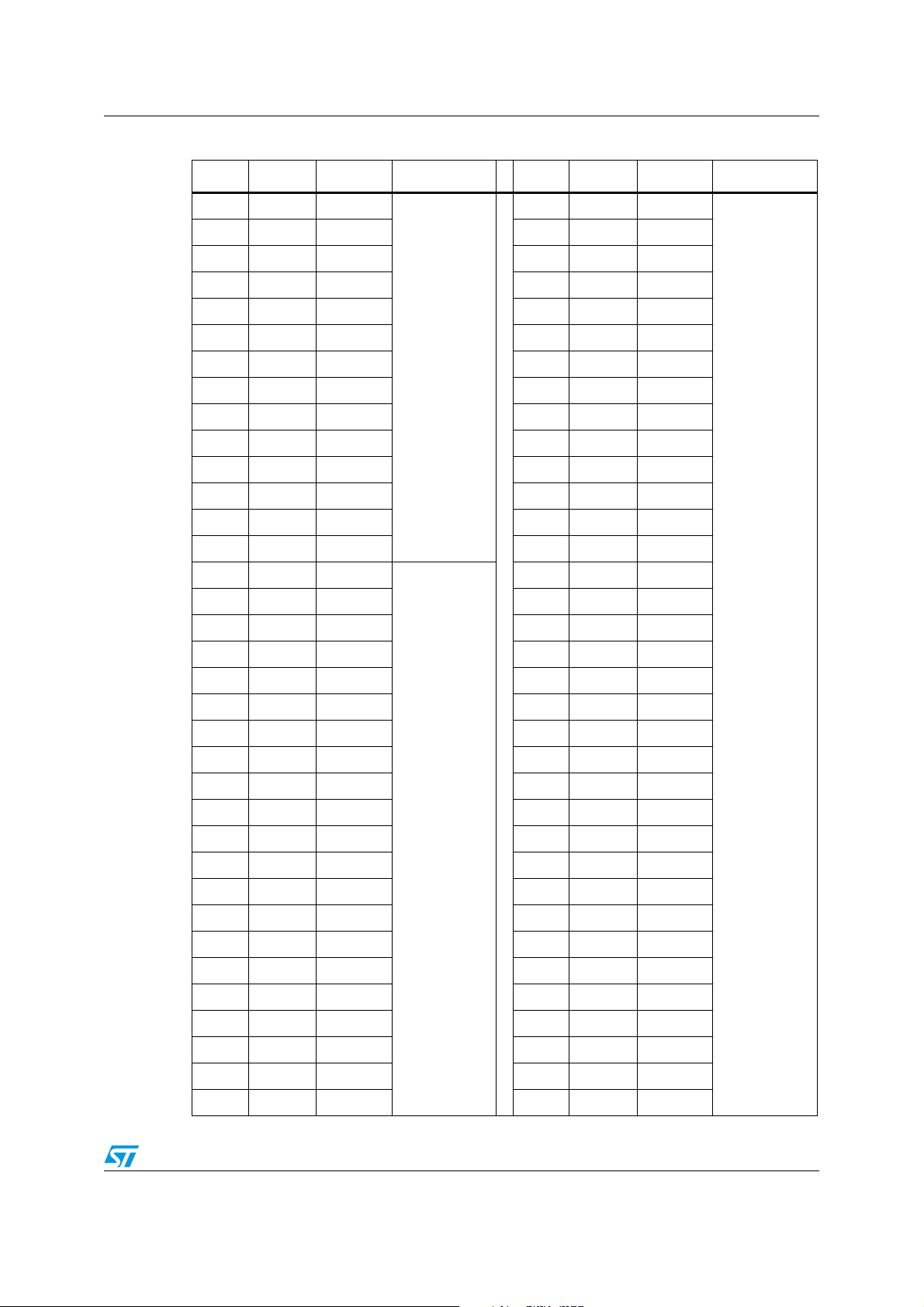

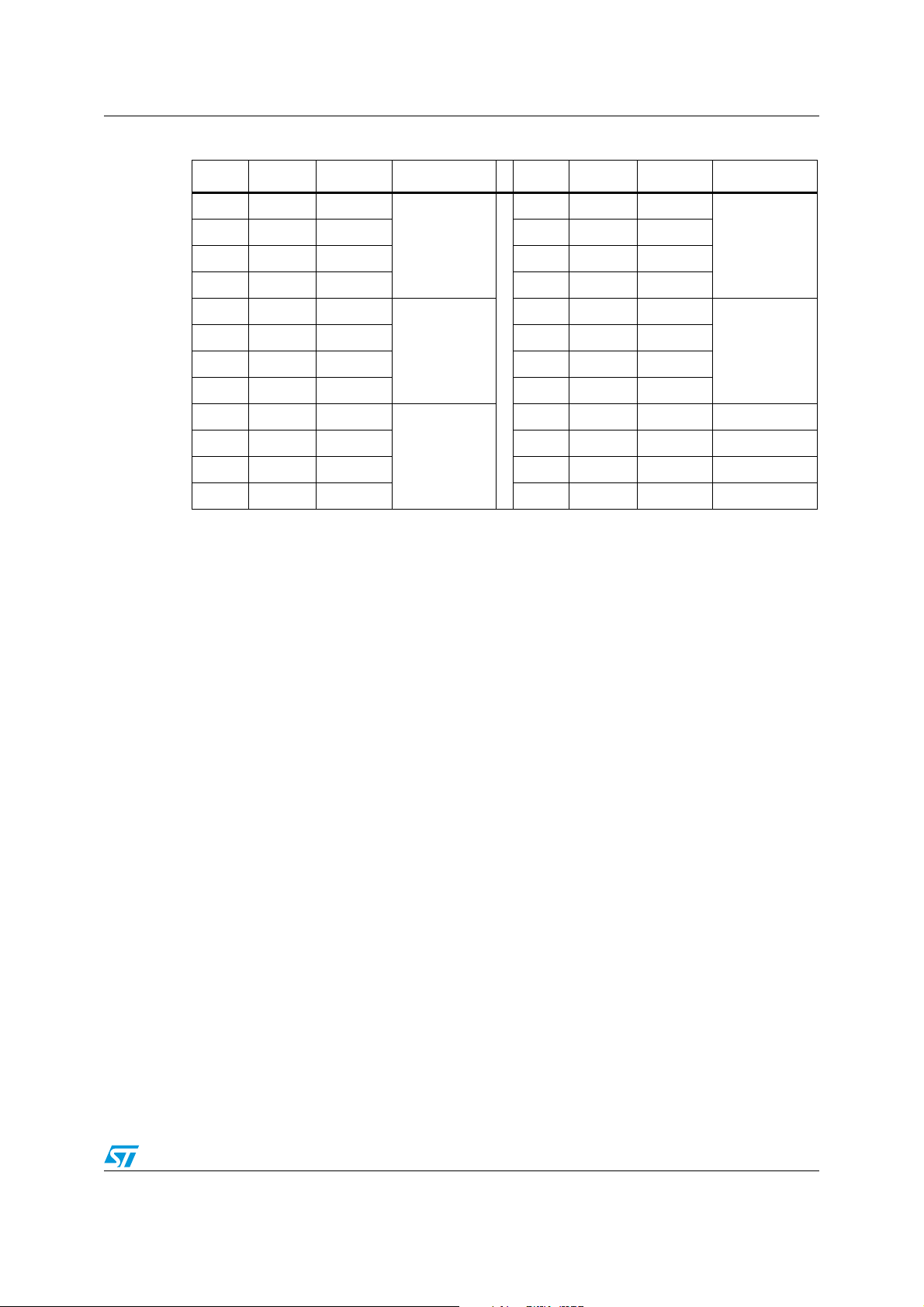

Table 2. Pin list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 3. Power supply pin list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

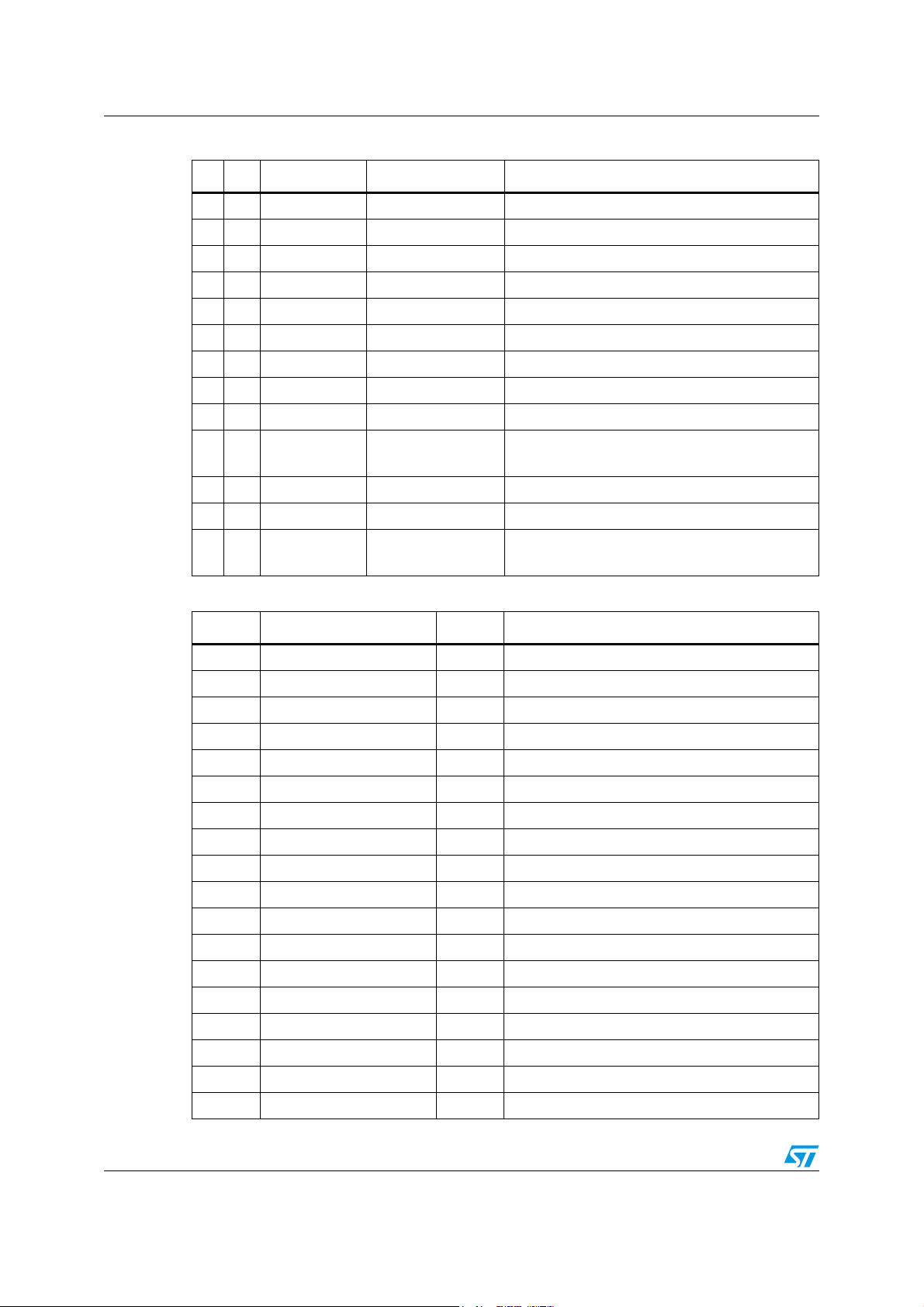

Table 4. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 5. Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 6. Electrical specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 7. Oscillator specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

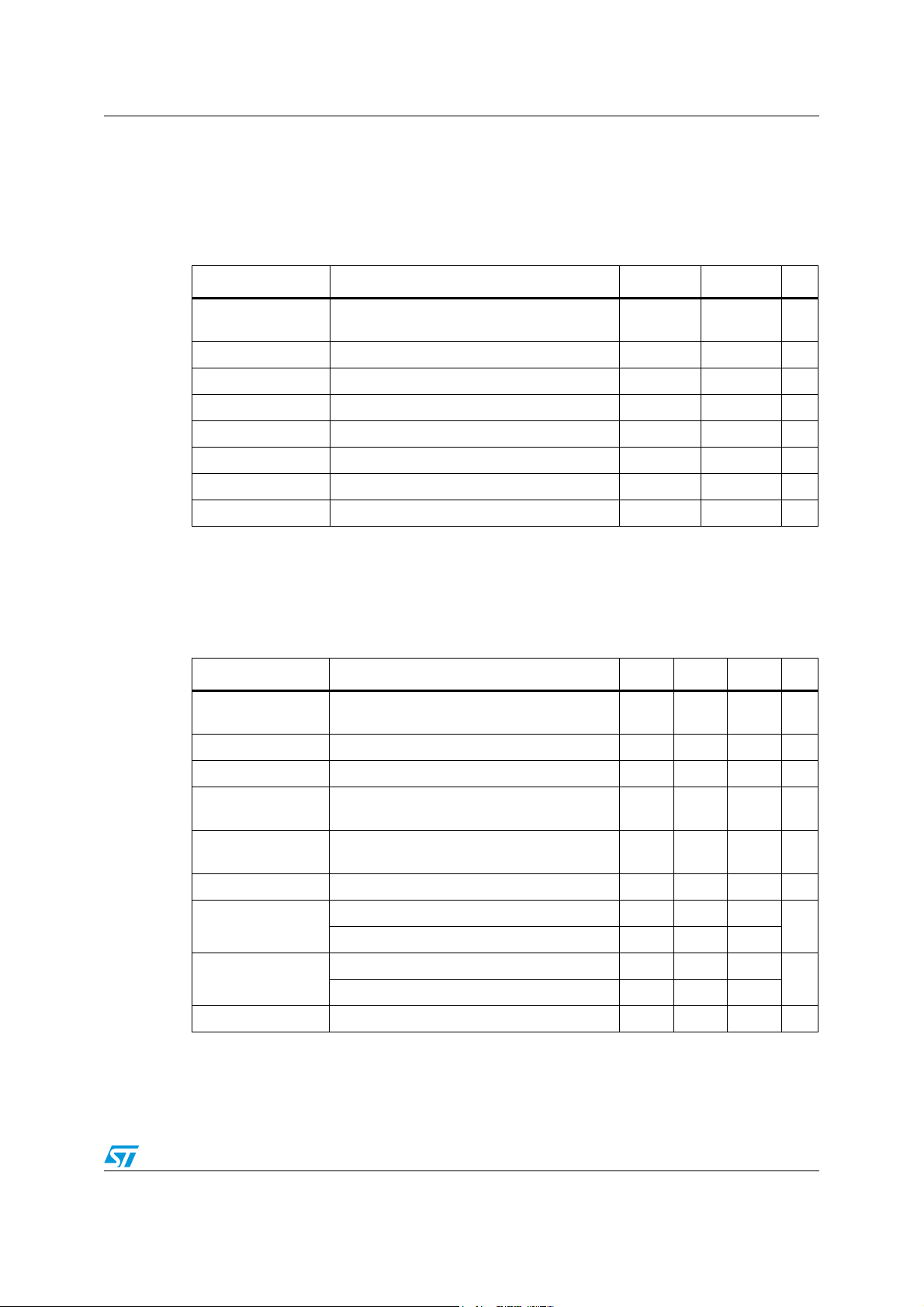

Table 8. Power-up signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 9. Startup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 10. Configuration example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 11. Registers for power-down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 12. Example configurations for power-down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

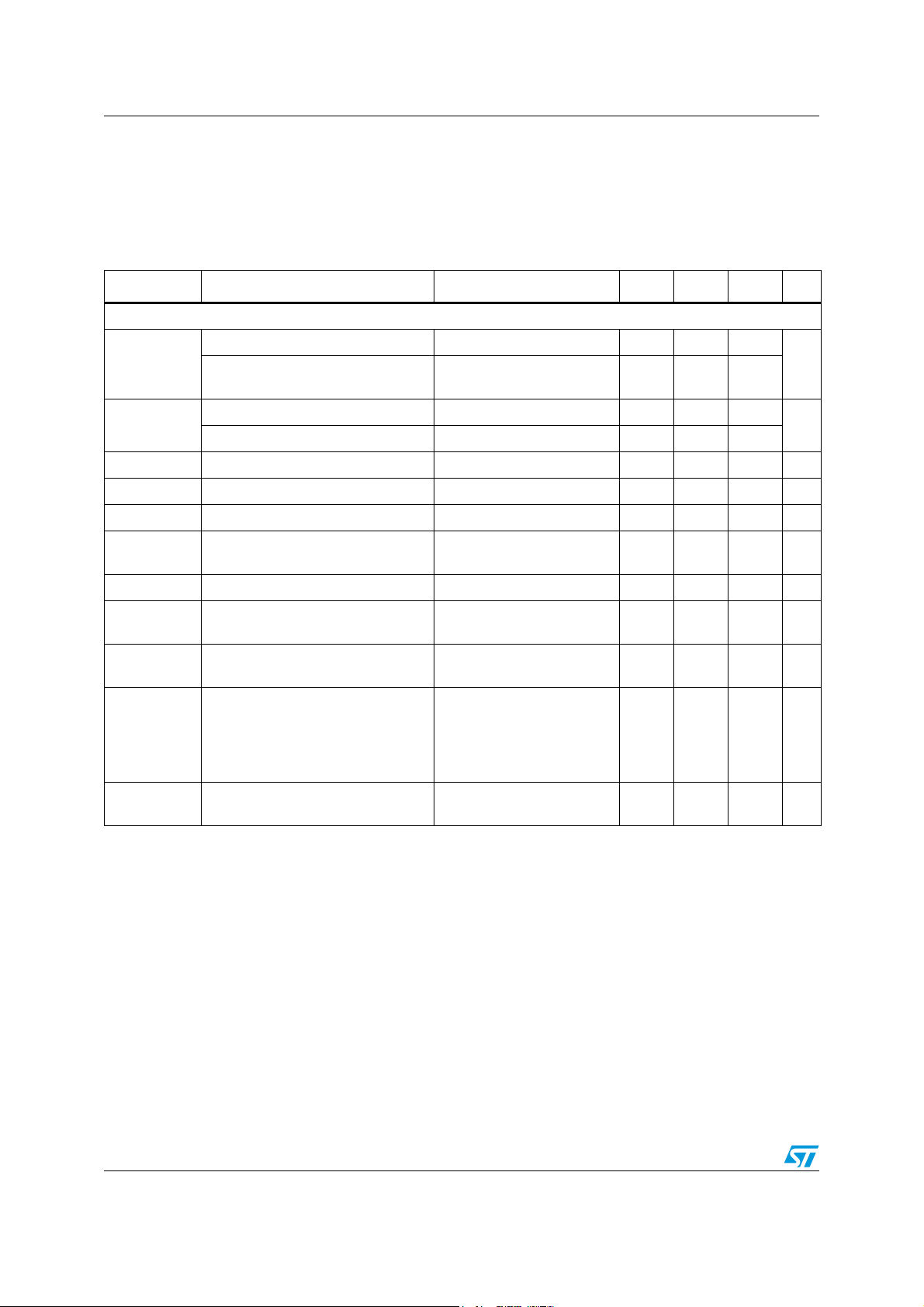

Table 13. Frequently used signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 14. Clock control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 15. Clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 16. Register setup to provide sys_clk from MCLK to PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 17. Input division factor (IDF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 18. Loop division factor (LDF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 19. Channel mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 20. EQ control signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 21. Selecting EQ curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 22. RAM mapping for processing stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 23. Modulation type with register programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 24. CMOS bridge signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 25. Power output (at 1% THD) in headphone mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 26. Logic circuit at bridge input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 27. Example register settings for ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

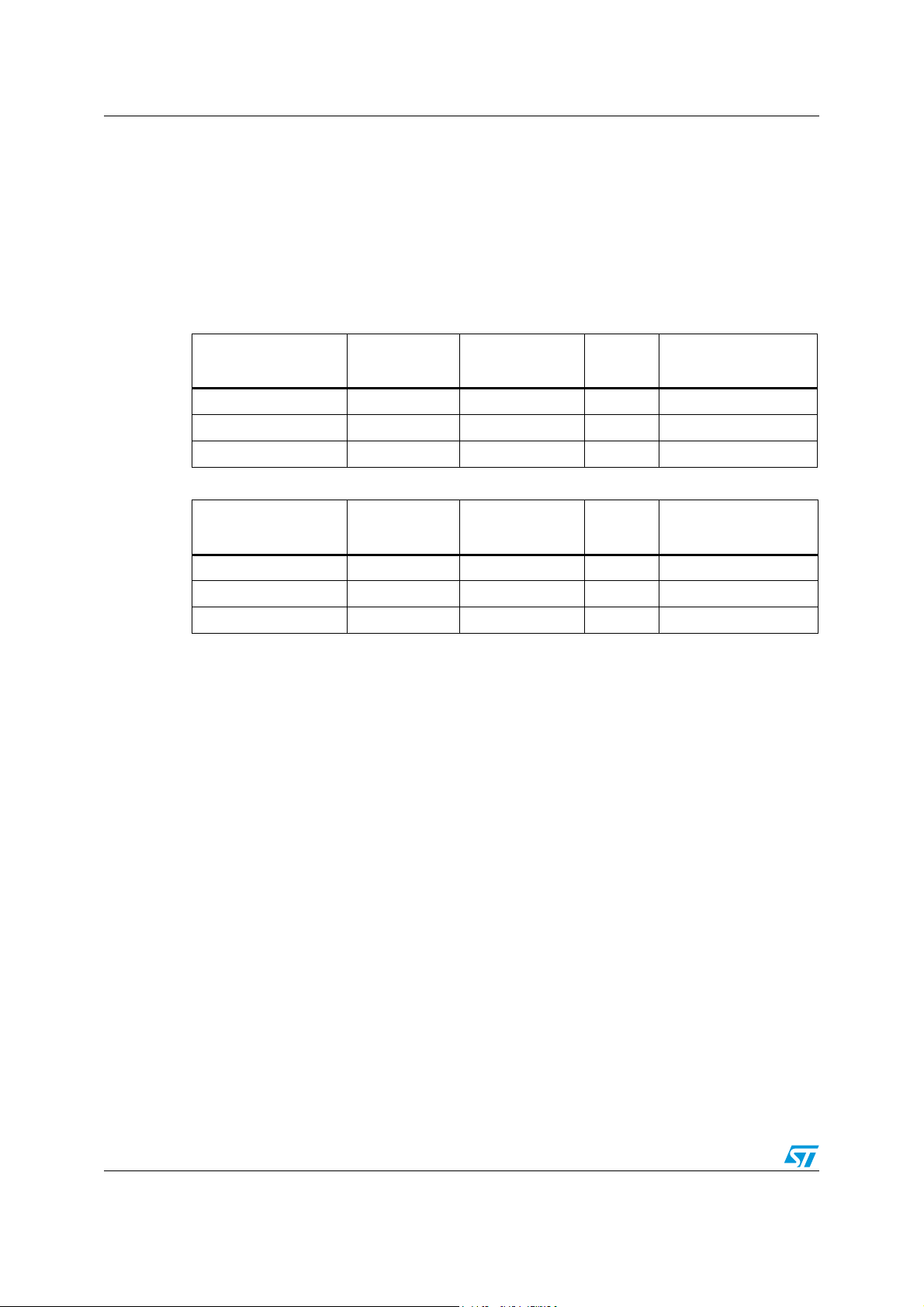

Table 28. Timing parameters for master mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 29. Timing parameters for slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 30. Headphone 1 detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 31. Headphone 2 detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 32. Headphone detection configuration sequence for binary SE . . . . . . . . . . . . . . . . . . . . . . . 74

Table 33. Headphone detection configuration sequence for binary headphone . . . . . . . . . . . . . . . . 74

Table 34. Register summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 35. Bass/treble filter gains used in register addresses 0x78 - 0x7F . . . . . . . . . . . . . . . . . . . . 115

Table 36. LQFP-64L EPD dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 37. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

6/157 Doc ID 15351 Rev 3

STA321 List of figures

List of figures

Figure 1. STA321 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 2. Pin out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 3. Test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 4. Oscillator configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 5. Equivalent circuit of crystal and external components . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 6. Embedded DC regulator scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 7. Startup sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 8. Hardware power-done sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 9. Hardware powerdown sequence (mild mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 10. Hardware power-down sequence (full mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 11. Clock management scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 12. PLL block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 13. Processing flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 14. Processing data multiplexer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 15. SAI_out data multiplexer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 16. Sample rate converter block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 17. Mixers block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 18. EQ/tone block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 19. Biquad coefficient selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 20. Biquad filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 21. High-pass filter frequency response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 22. Deemphasis filter frequency response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 23. Frequency responses of treble control at 1-dB gain steps . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 24. Frequency responses of bass control at 1-dB gain steps . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 25. FFX re-mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Figure 26. Writing RAM location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 27. Writing five contiguous RAM locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 28. Reading five contiguous RAM locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 29. FFX processing schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 30. PWM modes for outputs A and B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 31. Modulation waveforms corresponding to Table 23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 32. New phase shift modulation with shift feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 33. Ternary modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 34. Modulation for headphones . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 35. Digital pop-free ramp implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 36. CMOS half bridge block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 37. Analog pop-free schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 38. Analog pop-free start-up and switch-off sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 39. ADC front-end block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 40. Typical connections for power supplies and inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 41. SAI typical sampling rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 42. Timing diagram for master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 43. Timing diagram for slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 44. Right justified serial format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 45. Left justified serial format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 46. DSP serial format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 47. I

Figure 48. PCM (non-delayed) serial format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

2

S serial format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Doc ID 15351 Rev 3 7/157

List of figures STA321

Figure 49. PCM (delayed) serial format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 50. Invalid input detection schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 51. Headphone detection circuit for single-ended configuration . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 52. Headphone detection circuit for binary HP configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 53. I

Figure 54. I

2

C write operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

2

C read operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 55. Microless mode block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 56. LQFP-64L EPD outline drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

8/157 Doc ID 15351 Rev 3

STA321 Overview

1 Overview

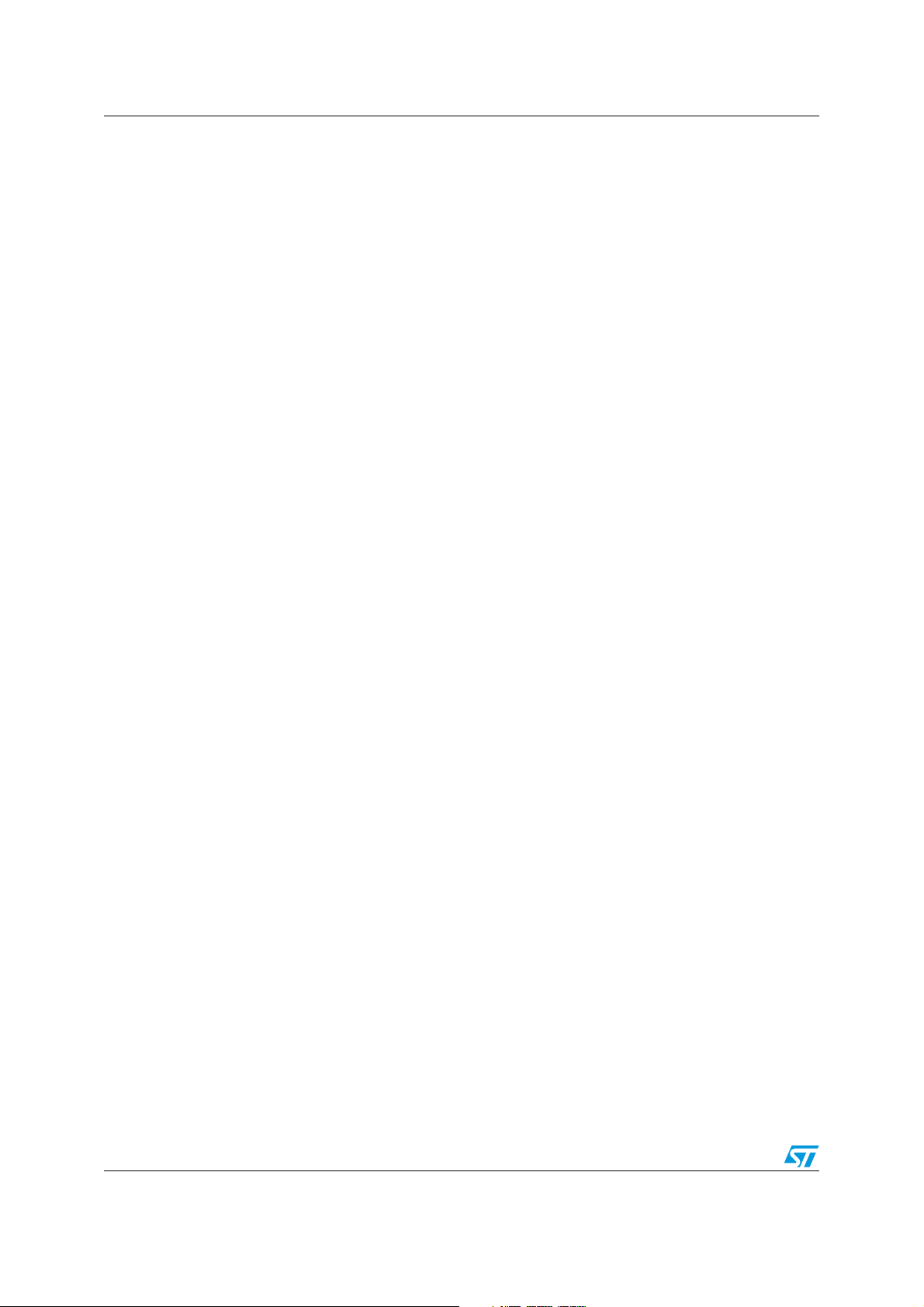

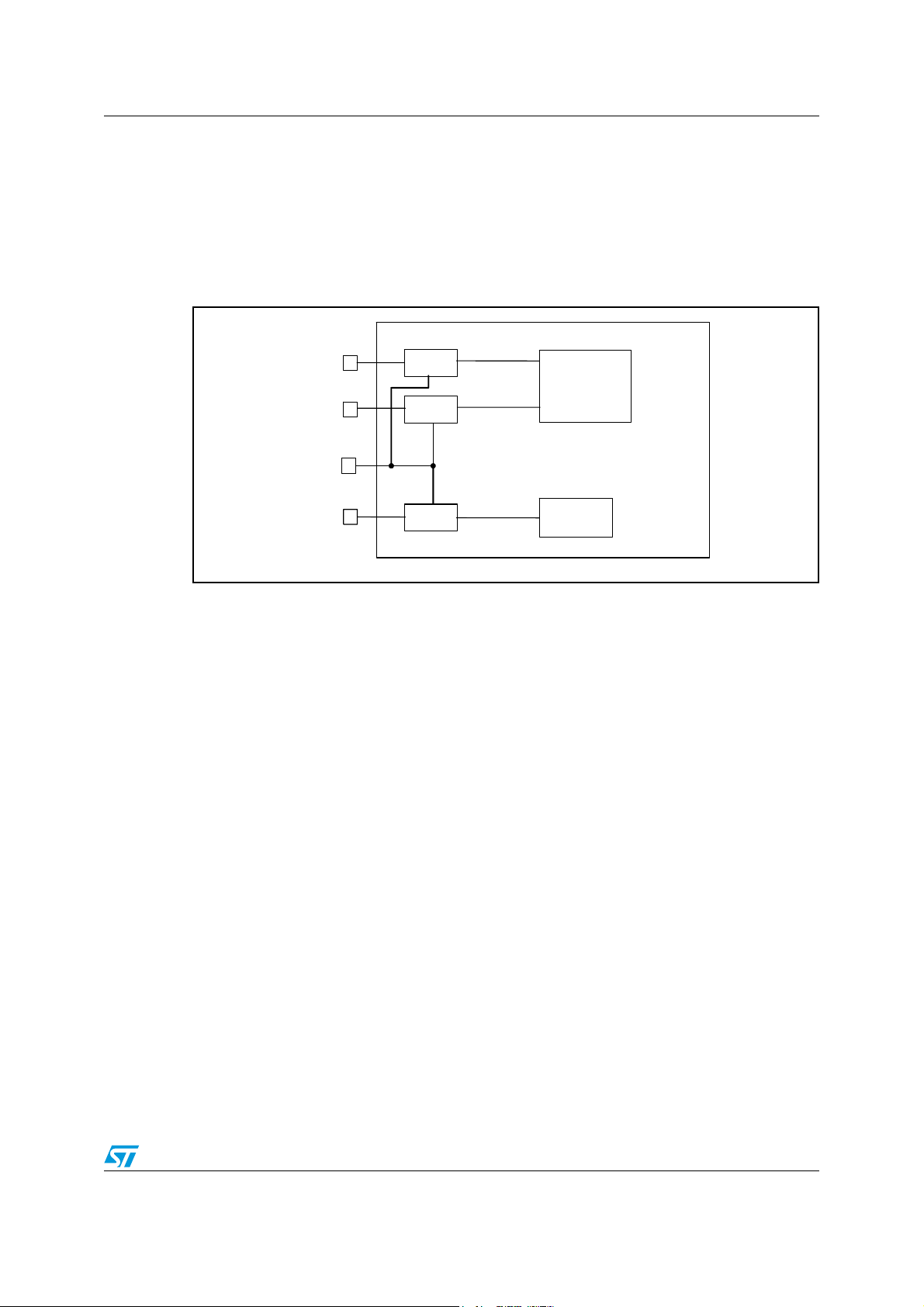

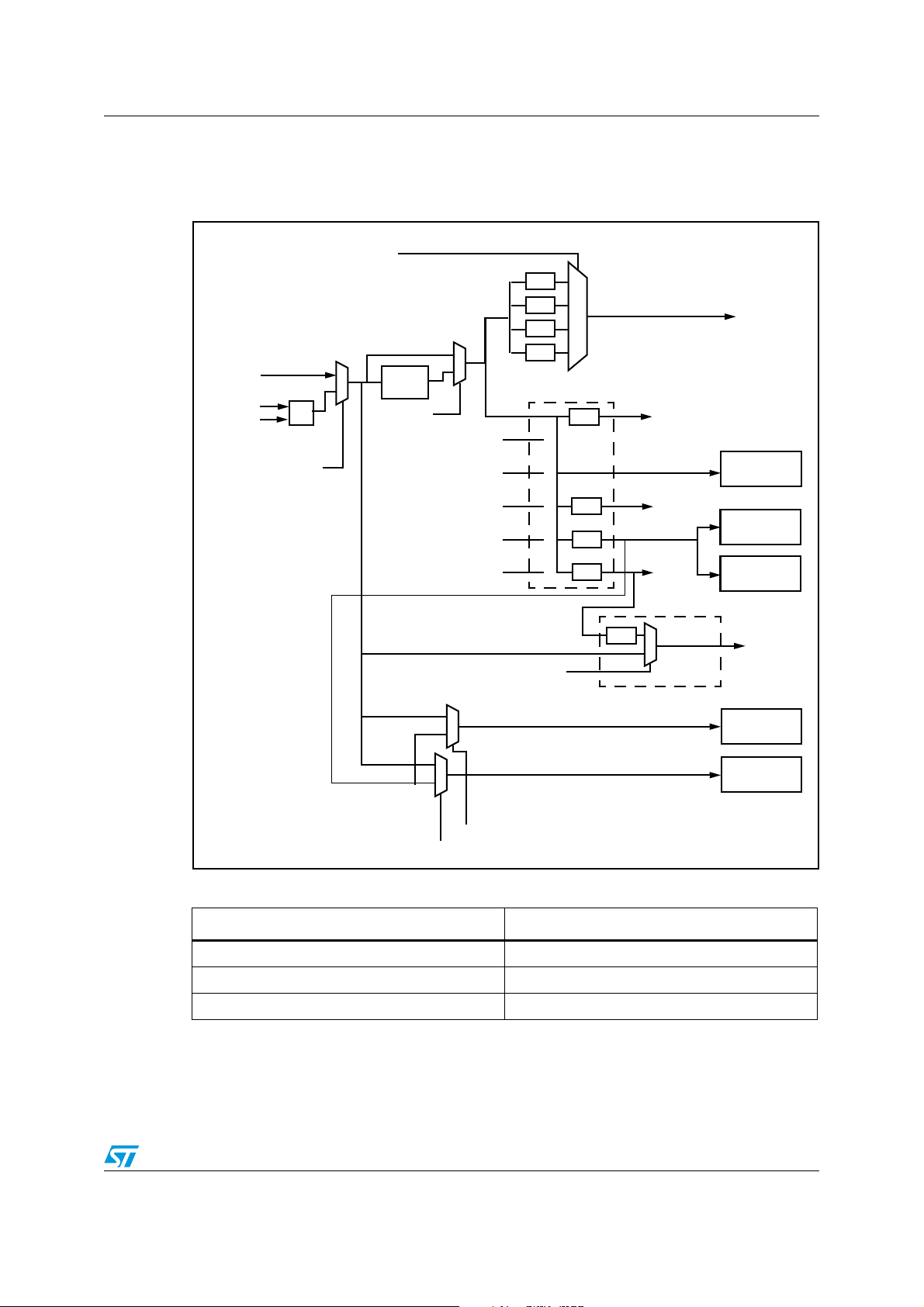

The STA321 is a single chip solution for digital audio processing applications of up to

4.0 channels.

The STA321 is part of the Sound Terminal™ family that together with the digital power stage

provides full digital audio streaming to the speaker, offering cost effectiveness, low energy

dissipation and sound enrichment.

The STA321 input section consists of two multiplexed stereo analog inputs, a 16-bit ADC

and two independent digital input interfaces. The serial audio data input interface accepts all

possible formats, including the popular I

by the ADC or by the digitally processed signals.

The device has a full assortment of digital processing features. This includes sample rate

converter, pre and post mixing, up to 13 programmable 28-bit biquads (EQ) per channel,

bass/treble tone control and DRC. The embedded headphone detector indicates when

headphone jack is inserted.

The STA321 provides four independent channels of FFX™ output capabilities. In

conjunction with a power device, it provides high-quality, high-efficiency, all digital

amplification.

2

S format. There is also a digital output interface fed

The embedded CMOS bridge supplies up to 0.5 W into an 8-Ω load and 70 mW into a 16-Ω

load for the headphones output.

Figure 1. STA321 block diagram

SDATAO1

BICLKO

LRCLKO

SDATAO2

Serial audio

Osc

interface

4-channel

SRC

XTI

XTO

PLL

pre mixer

MCLK

V_BIAS

VCM

VHI

VLO

BICLKI1

LRCLKI1

SDATAI1

BICLKI2

LRCLKI2

SDATAI2

INL1

INL2

INR1

INR2

HPDET

Bias

Serial audio

interface

Serial audio

interface

PGA

PGA

HP detection

.

ADC

RSTN

Pre scaler

Divider

CLKOUT

STBY

Equalizer

TM

EAFTN

EATSN

EAPDN

Delay

13 biquad filters

Post mixer

Volume control and

saturation

FFX™

modulator

CMOS

headphone

bridge

EAPWM4

EAPWM3

EAPWM2

EAPWM1

OUT1

OUT2

OUT3

PWM00

I2C interface

SCL

MUTE

SDA

I2CDIS

ACLK

REG_BYP

Doc ID 15351 Rev 3 9/157

Pin description STA321

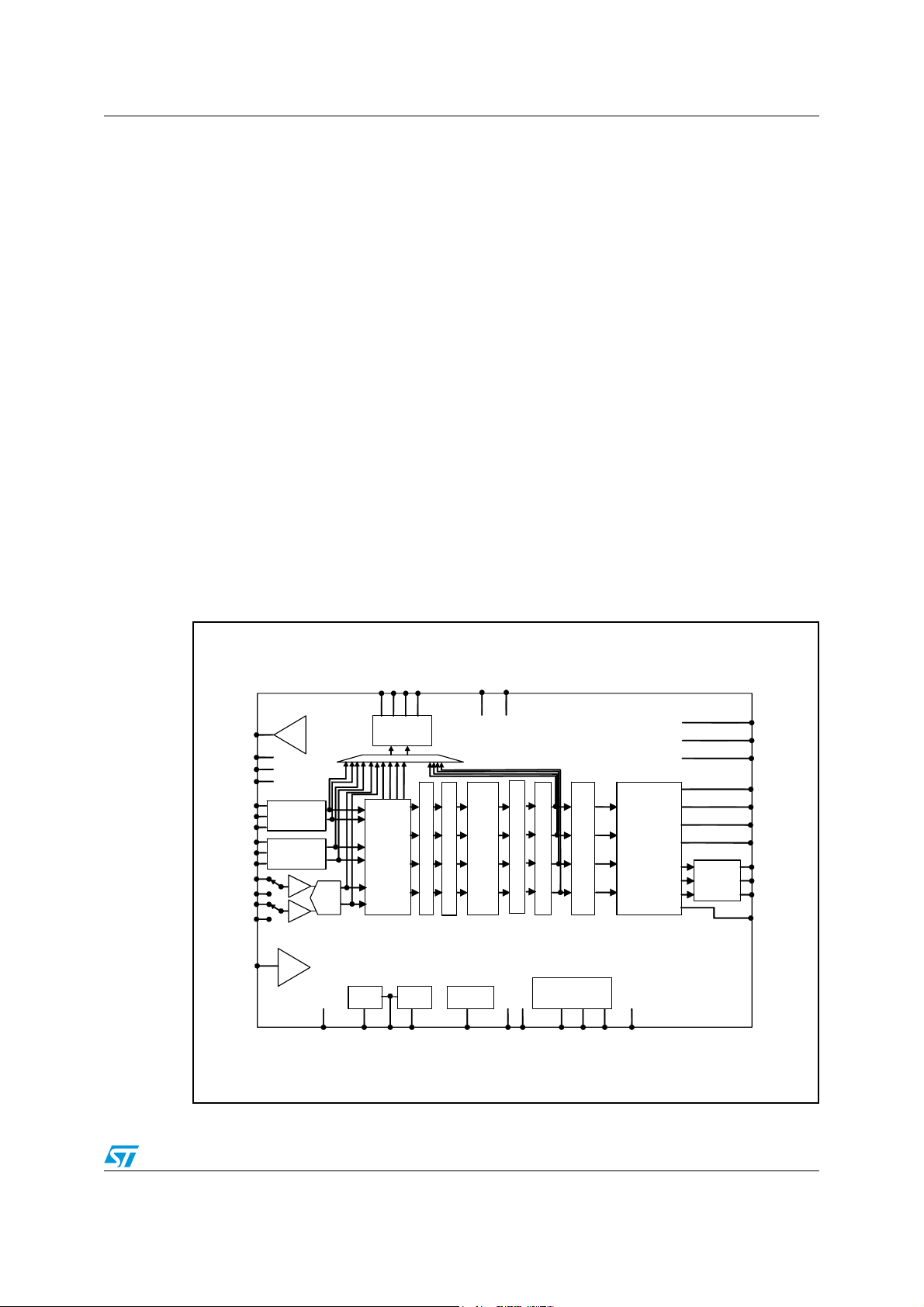

2 Pin description

Figure 2. Pin out

BICLKO

BICLKI1

BICLKI2

LRCLKO

LRCLKI1

LRCLKI2

SDATAO1

SDATAO2

SDATAI1

SDATAI2

MCLK

XTI

XTO

NC

PGND

PVDD

64

63

62

61

SCL

VCC1

OUT1

GND1

GND2

OUT2

VCC2

VCC3

OUT3

GND3

NC

PWM00

NC

HPDET

GND33

VCC33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

605958

19

20

21

57

56

STA321

22

23

24

25

55

54

53

52

51

50

49

48

TM

47

VDDIO2

46

VDD_REG2

45

DGND2

44

I2CDIS

43

ACLK

42

EAPDN

41

EATSN

40

EAFTN

39

EAPWM1

38

EAPWM2

37

EAPWM3

36

EAPWM4

35

STBY

34

RSTN

33

26

27

28

29

30

31

32

INL1

SDA

MUTE

CLKOUT

Table 2. Pin list

Pin Pull Name Type Description

1 - SCL In (digital), schmitt tr I

3 - OUT1 Out (analog) HP/line-out PWM 1

6 - OUT2 Out (analog) HP/line-out PWM 2

9 - OUT3 Out (analog) HP/line-out PWM 3

11 - NC - Not connected

10/157 Doc ID 15351 Rev 3

12 - PWM00 Out (digital) Auxiliary PWM

13 - NC - Not connected

14 - HPDET In (analog) Headphone detection

DGND1

REG_BYP

VDD_REG1

AGND

V_BIAS

VDDIO1

VHI

VLO

2

C serial clock, schmitt trigger input

AVDD

INR1

VCM

INR2

INL2

STA321 Pin description

Table 2. Pin list (continued)

Pin Pull Name Type Description

17 - CLKOUT Out (digital) Buffered clock output

18 - SDA In/Out (digital) I

19 H MUTE In (digital) Mute (active high)

21 - REG_BYPASS In (analog)

24 - BIAS In/Out (analog) ADC microphone bias voltage

26 - VLO In (analog) ADC low reference voltage

27 - VHI In (analog) ADC high reference voltage

29 - INR1 In/Out (analog) ADC right channel line input1

30 - INR2 In/Out (analog) ADC right channel line input2

31 - VCM In/Out (analog) ADC common mode voltage

32 - INL2 In (analog) ADC left channel line input2 or microphone input2

33 - INL1 In (analog) ADC left channel line input1 or microphone input1

2

C serial data

DC regulator bypass:

0: normal operation, regulator enabled

1: regulator bypassed

Reset:

34 H RSTN In (digital)

0: reset state

1: normal operation

Standby mode:

35 - STBY In (digital)

0: normal operation

1: power-down

36 - EAPWM4 Out (digital) External amplifier PWM 4B

37 - EAPWM3 Out (digital) External amplifier PWM 4A

38 - EAPWM2 Out (digital) External amplifier PWM 3B

39 - EAPWM1 Out (digital) External amplifier PWM 3A

External power fault signal:

40 H EAFTN Out (digital)

0: fault

1: normal operational mode

External amplifier control:

41 - EATSN Out (digital)

0: active

1: 3-state

42 - EAPDN Out (digital) External amplifier powerdown (active low)

43 - ACLK In (digital), schmitt tr Reserved pin, connect to ground

2

C disable:

I

44 L I2CDIS In (digital)

2

C enabled

0: I

1: I2C disabled

48 L TM In (digital)

Test mode:

0: normal operation

51 - NC - Not connected

Doc ID 15351 Rev 3 11/157

Pin description STA321

Table 2. Pin list (continued)

Pin Pull Name Type Description

52 - XTO Out (digital), 1.8 V Crystal output

53 - XTI In (digital), 1.8 V Crystal input or master clock input

54 - MCLK In (digital), schmitt tr Master clock input 3.3-V compatible, schmitt input

55 - SDATAI2 In (digital) Input serial audio interface data

56 - SDATAI1 In (digital) Input serial audio interface data

57 - SDATAO2 Out (digital) Output serial audio interface data

58 - SDATAO1 Out (digital) Output serial audio interface data

59 - LRCLKI2 In/Out (digital) Input serial audio interface L/R-clock

60 - LRCLKI1 In/Out (digital) Input serial audio interface L/R-clock

61 - LRCLKO In/Out (digital)

62 - BICLKI2 In/Out (digital) Input serial audio interface bit clock

63 - BICLKI1 In/Out (digital) Input serial audio interface bit clock

64 - BICLKO In/Out (digital)

Output serial audio interface L/R-clock

(volume DOWN when I2CDIS=1)

Output serial audio interface bit clock

(volume UP when I2CDIS=1)

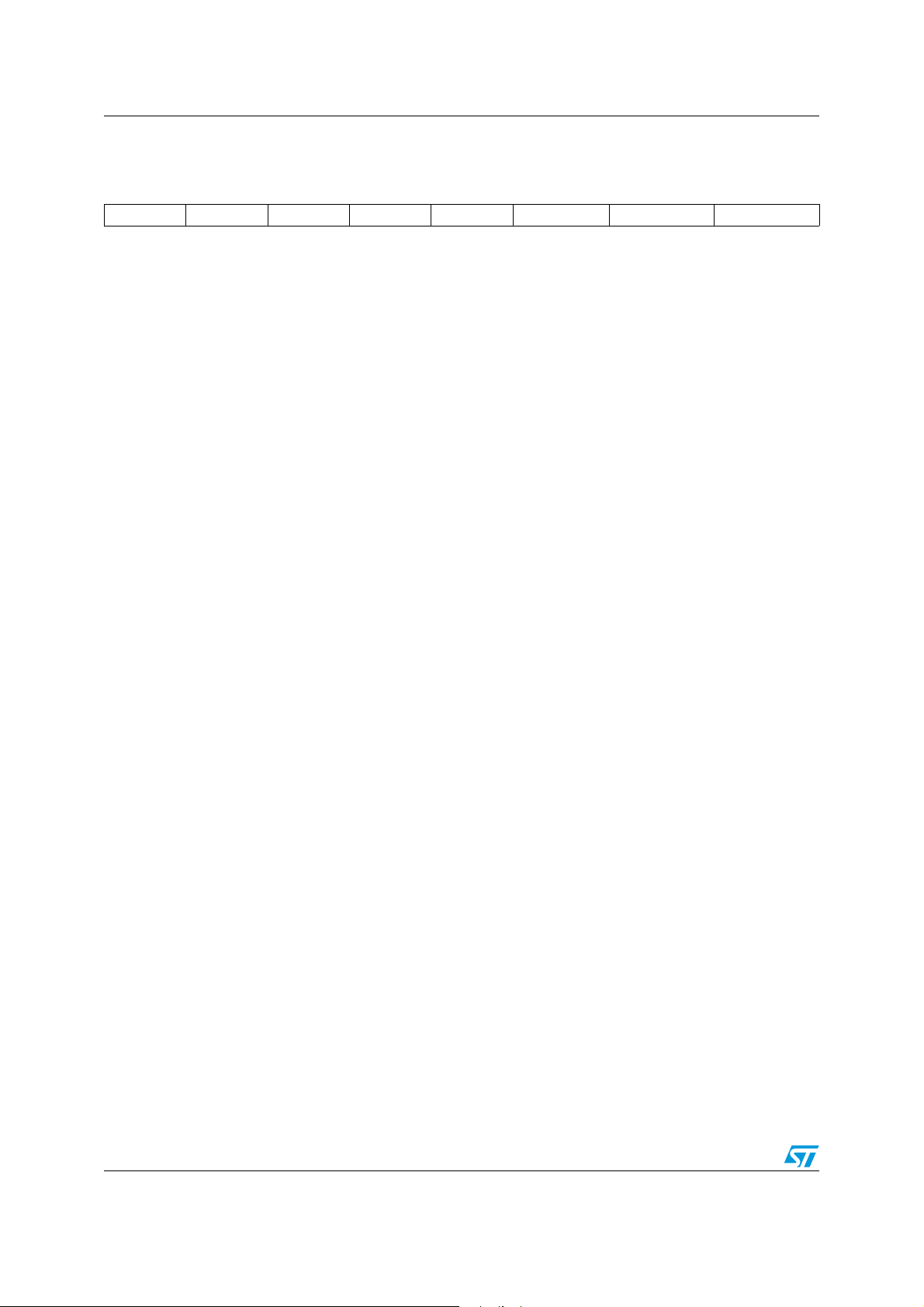

Table 3. Power supply pin list

Number Name Type Description

2 VCC1 Supply CMOS bridge channel 1 supply

4 GND1 Ground CMOS bridge channel 1 ground

5 GND2 Ground CMOS bridge channel 2 ground

7 VCC2 Supply CMOS bridge channel 2 supply

8 VCC3 Supply CMOS bridge channel 3 supply

10 GND3 Ground CMOS bridge channel 3 ground

15 GND33 Ground CMOS bridge level shifter ground

16 VCC33 Supply CMOS bridge level shifter supply

20 DGND1 Ground Digital ground

22 VDD_REG1 Supply DC regulator unit supply

23 VDDIO1 Supply 3.3-V IO supply

25 AGND Ground ADC analog ground

28 AVDD Supply ADC analog supply

45 DGND2 Ground Digital ground

46 VDD_REG2 Supply DC regulator unit supply

47 VDDIO2 Supply 3.3-V IO supply

49 PVDD Supply PLL analog supply

50 PGND Ground PLL analog ground

12/157 Doc ID 15351 Rev 3

STA321 Electrical specifications

3 Electrical specifications

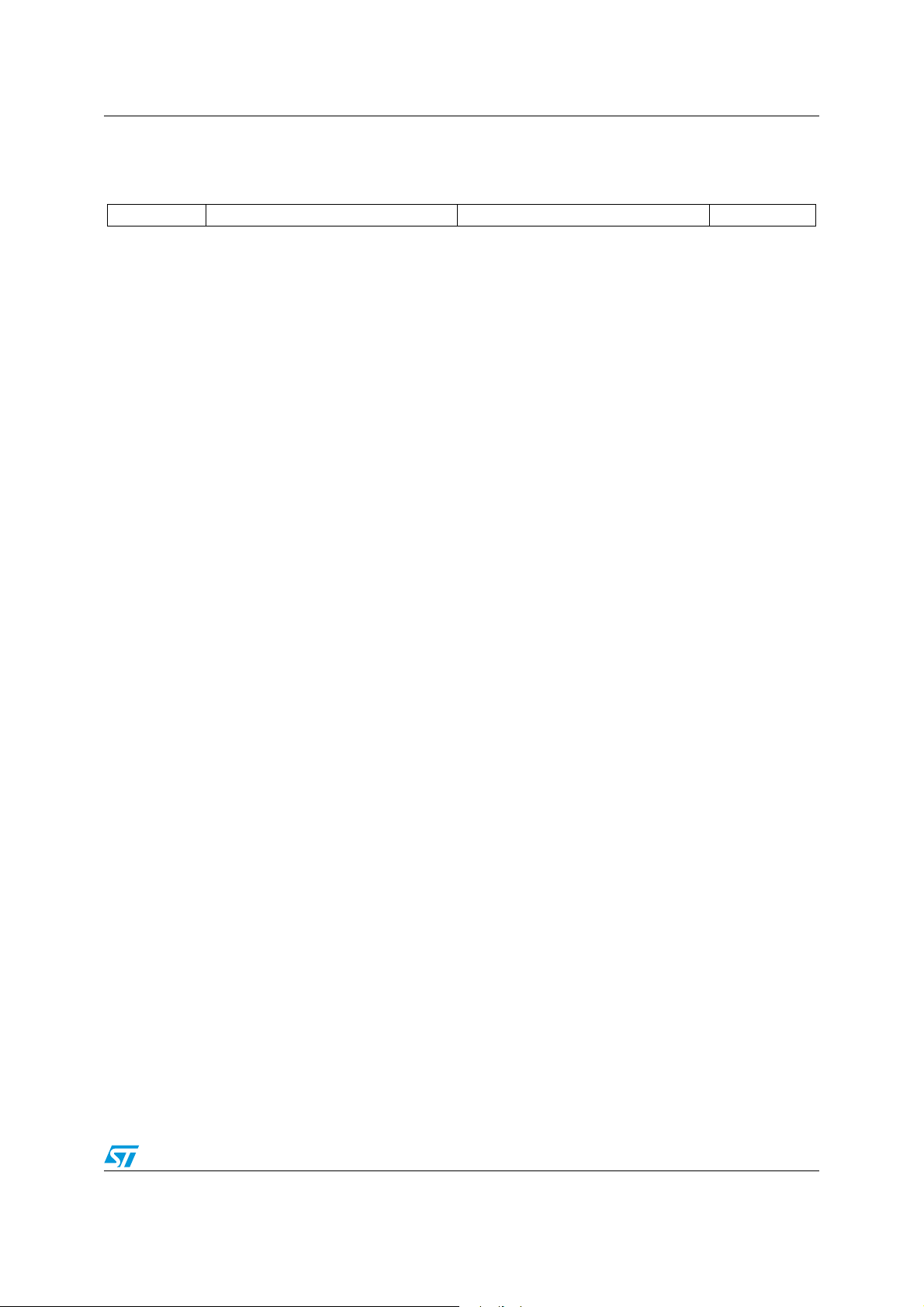

3.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

Pin name/Symbol Parameter Negative Positive Unit

VDD_REG1,

VDD_REG2

Digital supply voltage -0.3 4.0 V

VDDIO1, VDDIO2 Digital IO supply voltage -0.3 4.0 V

PVDD PLL analog supply voltage -0.3 4.0 V

AVDD ADC analog supply voltage -0.3 4.0 V

VCC1, VCC2, VCC3 CMOS bridge supply voltage -0.3 4.0 V

VCC33 CMOS bridge level shifter power supply -0.3 4.0 V

T

T

STG

OP

Storage temperature -40 150 °C

Operating junction temperature -20 125 °C

Note: All grounds must always be within 0.3 V of each other.

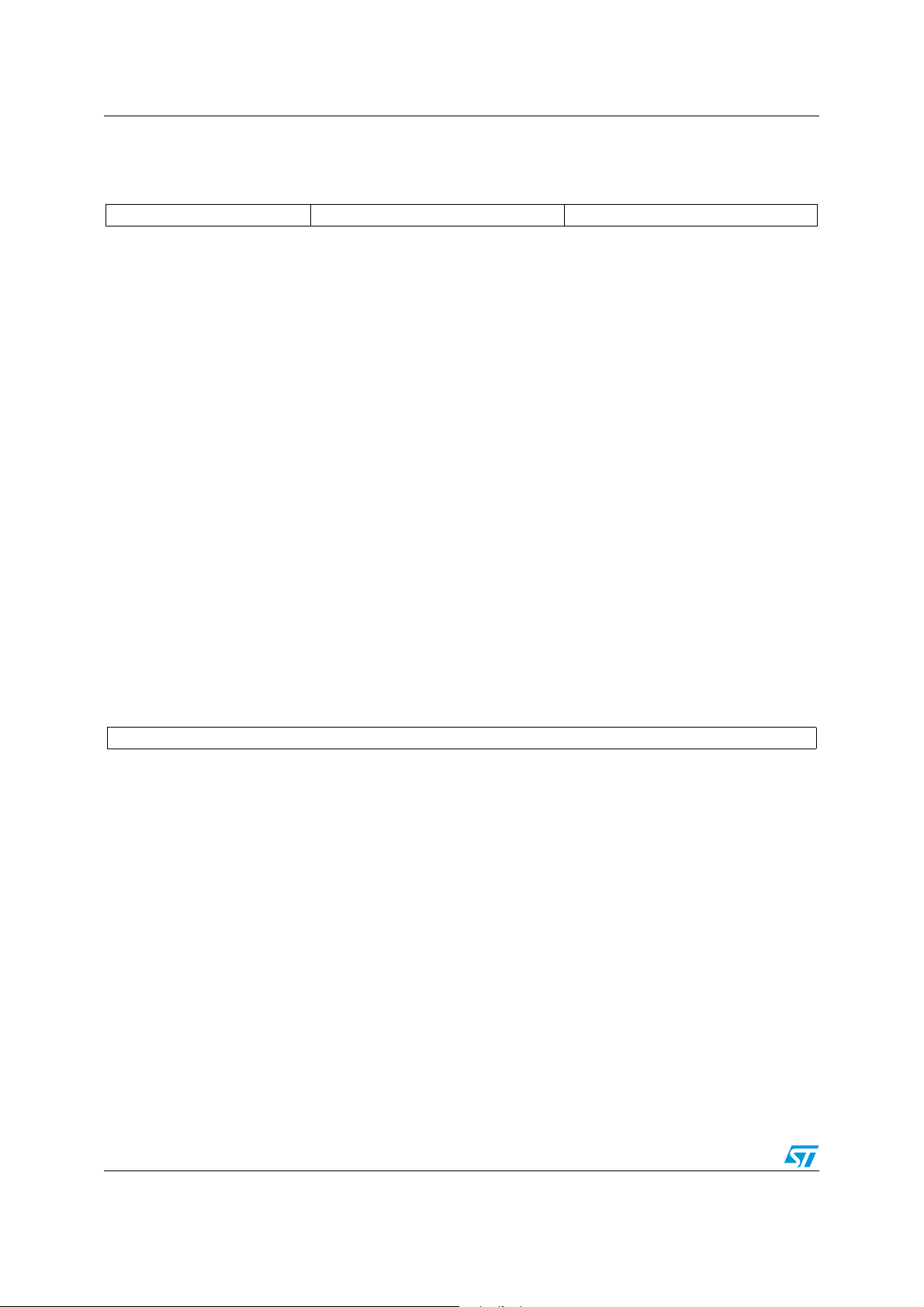

3.2 Recommended operating conditions

Table 5. Recommended operating conditions

Symbol Parameter Min Typ Max Unit

V

VDD_REG1

V

VDD_REG2

V

PVDD

V

AVD D

V

VCC1

V

VCC3

V

VCC33

V

VDDIO1

V

IH

V

IL

T

amb

, V

VCC2

, V

,

,

VDDIO2

Digital supply voltage 2.5 3.3 3.6 V

PLL analog supply voltage 2.5 3.3 3.6 V

ADC analog supply voltage 1.8 3.3 3.6 V

CMOS bridge supply voltage 1.55 - 3.3 V

CMOS bridge level shifter power supply.

Ensure that V

VCC33

<= V

3.3-V IO supply 2.7 3.3 3.6 V

High input voltage, 1.8-V pads 1.3 - -

High input voltage, 3.3-V pads 2.0 - -

Low input voltage, 1.8-V pads - - 0.6

Low input voltage, 3.3-V pads - - 0.8

Ambient temperature 0 - 70 °C

VCCx

always

1.55 - 3.3 V

V

V

Doc ID 15351 Rev 3 13/157

Electrical specifications STA321

3.3 Electrical characteristics

Unless otherwise specified, the results in Table 6 below are given for the operating

conditions V

to default conditions.

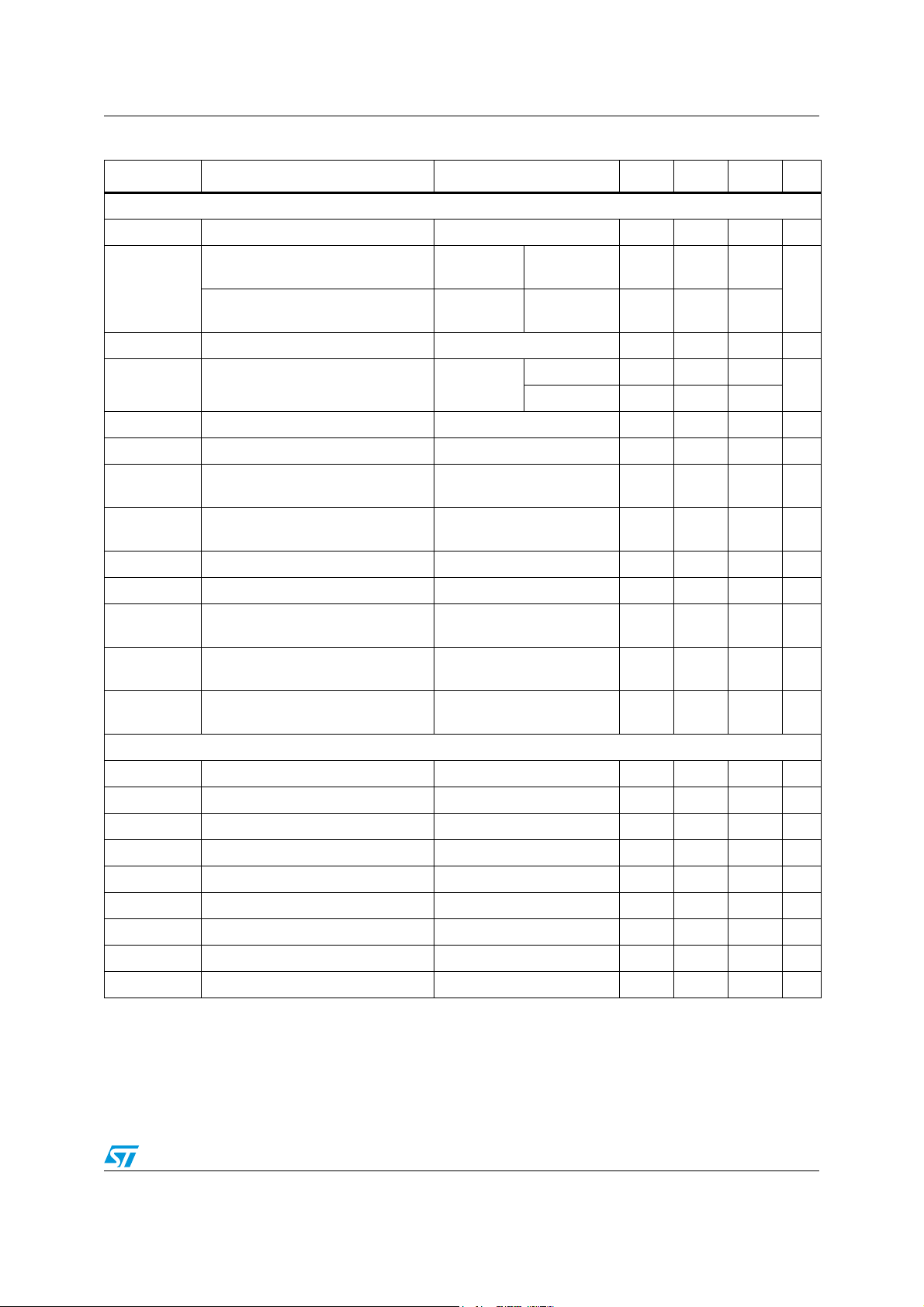

Table 6. Electrical specifications

Symbol Parameter Test conditions Min Typ Max Unit

General

V

OH

V

OL

V

hys

R

UP

R

DN

I

STBYIO

High output voltage, 1.8-V pads - 1.4 - -

High output voltage, 3.3-V pads -

Low output voltage, 1.8-V pads IOL = 2 mA --0.15

Low output voltage, 3.3-V pads I

Schmitt trigger hysteresis, 3.3-V IO - - 0.4 - V

Pull-up resistance - - 50 - kΩ

Pull-down resistance - - 50 - kΩ

Standby current, pins VDDIO1,2

=3.3 V, RL = 32 Ω, f

CC

= 12.288 MHz, Tamb = 25 °C and with the PLL set

MCLK

V

VDDIO

- 0.15

= 2 mA --0.15

OL

Pin STBY = 3.3 V

CLKOUT disabled

-450-µA

--

V

V

I

DDIO

I

STBYL0

I

STBYL1

I

DDL1

I

STBYPD

Operating current, pins VDDIO1,2 - - 3 - mA

Standby current, pins VDD_REG1,2

Standby current, pins VDD_REG1,2

Operating current,

pins VDD_REG1,2

Pre-drive supply current in standby,

pin VCC33

Deep power-down,

V

VDD_REG1,2

= 3.3 V

Mild power-down,

V

VDD_REG1,2

f

MCLK

= 3.3 V

= 12.288 MHz, Play

from SAI to CMOS bridge

and EAPWM, f

on SAI_out, V

V

VDD_REG1,2

ADC

AVD D

= 3.3 V

= 48 kHz

= 3.3 V,

- - 4.7 - µA

-450-µA

-2-mA

-45-mA

14/157 Doc ID 15351 Rev 3

STA321 Electrical specifications

Table 6. Electrical specifications (continued)

Symbol Parameter Test conditions Min Typ Max Unit

Amplifier (CMOS bridge)

η Output power efficiency - - 90 - %

Output power in HP mode with

THD = 1%

P

HPOUT

Output power in HP mode with

THD = 10%

SNR Signal to noise ratio 20 Hz to 20 kHz - 75 - dB

3.3-V supply R

3.3-V supply R

= 32 Ω -41-

L

= 32 Ω -53-

L

mW

THD + N Total harmonic distortion plus noise

RL = 32 Ω,

HP mode

0 dBFs In - 0.3 -

%

-6 dBFs In - 0.05 -

DR Dynamic range A-weighted - 80 - dB

I

STBYP

I

DDP

I

DDPD

t

R

t

F

R

DSON

I

OCH

I

OCL

Current in standby, pins VCCx - - 2 - µA

Operating current, pins VCCx

Pre-drive supply current in

operation, pin VCC33

No LC filter, no load,

PWM at 50% duty-cycle

No load,

PWM at 50% duty-cycle

-1-mA

- 250 350 µA

Driver rise time, pins OUT1-3 Resistive load, see Figure 3 -5-ns

Driver fall time, pins OUT1-3 Resistive load, see Figure 3 -5-ns

Headphone output stage N/P MOS

on-resistance

Over-current limit for OUT1-3 to

VCCx short circuit

Over-current limit for OUT1-3 to

ground short circuit

- - 500 700 mΩ

- - 1.88 - A

- - 1.72 - A

PLL

I

STDBYPLL

I

DDPLL

f

CLKIN_Range

Duty

CLKIN

t

CLKIN_RF

f

F_INT

f

VCO_Range

Duty

VCO

T

LOCK

PLL supply current in standby - - 20 - µA

PLL supply current in operation - - 0.4 1.0 mA

Input clock frequency range - 2.048 - 49.152 MHz

Input clock duty cycle - 40 - 60 %

Input clock rise/fall time - - - 0.2 ns

PFD input clock frequency PLL_FR_CTRL = 1 2.048 - 12.288 MHz

Clock out range - 65.536 - 98.304 MHz

Clock out duty cycle - 35 - 65 %

Lock time - - - 200 µs

Doc ID 15351 Rev 3 15/157

Electrical specifications STA321

Table 6. Electrical specifications (continued)

Symbol Parameter Test conditions Min Typ Max Unit

ADC

I

DDA

I

STDBYA

DR Dynamic range

SNR

ADC

THD

ADC

CT Channel cross talk V

- Group delay

Supply current in operating mode V

AVDD supply current in standby V

Signal to noise ratio

Total harmonic distortion

= 3.3V - 10 15 mA

AVD D

= 3.3V - 2 - µA

AVD D

1 kHz, A-weigthed

= 3.3 V

V

AVD D

1 kHz, A-weighted

= 3.3 V

V

AVD D

1 kHz, -1dB

V

= 3.3 V

AVD D

= 3.3 V - 80 - dB

AVD D

Fs mode (f

Fs_by_4 mode (f

= 32 kHz) - 0.4 -

S

= 16 kHz) - 0.7 -

S

= 8 kHz) - 1.4 -

S

-90-dB

-92-dB

-85-dB

msFs_by_2 mode (f

- Pass band - - 0.4535 - Fs

= 44.1 kHz) - 0.08 -

S

-0.08-

-0.08-

= 44.1 kHz) - 45 -

S

-45-

-45-

dB

dB

- Pass band ripple

- Stop band attenuation

Fs mode (f

Fs_by_2 mode

(f

= 22.05 kHz)

S

Fs_by_4 mode

= 11.025 kHz)

(f

S

Fs mode (f

Fs_by_2 mode

(f

= 22.05 kHz)

S

Fs_by_4 mode

= 11.025 kHz)

(f

S

-3 dB - 7 - Hz

- Frequency response

-0.08 dB - 50 - Hz

- Linear phase deviation at 20 Hz - 19.35 - deg

- Pass-band ripple - - 0.08 - dB

Headphone detector threshold limits

HP low threshold - - 2.34 -

E_HP1

HP high threshold - - 2.52 -

HP low threshold - - 0.7 -

E_HP2

HP high threshold - - 0.9 -

16/157 Doc ID 15351 Rev 3

V

V

STA321 Electrical specifications

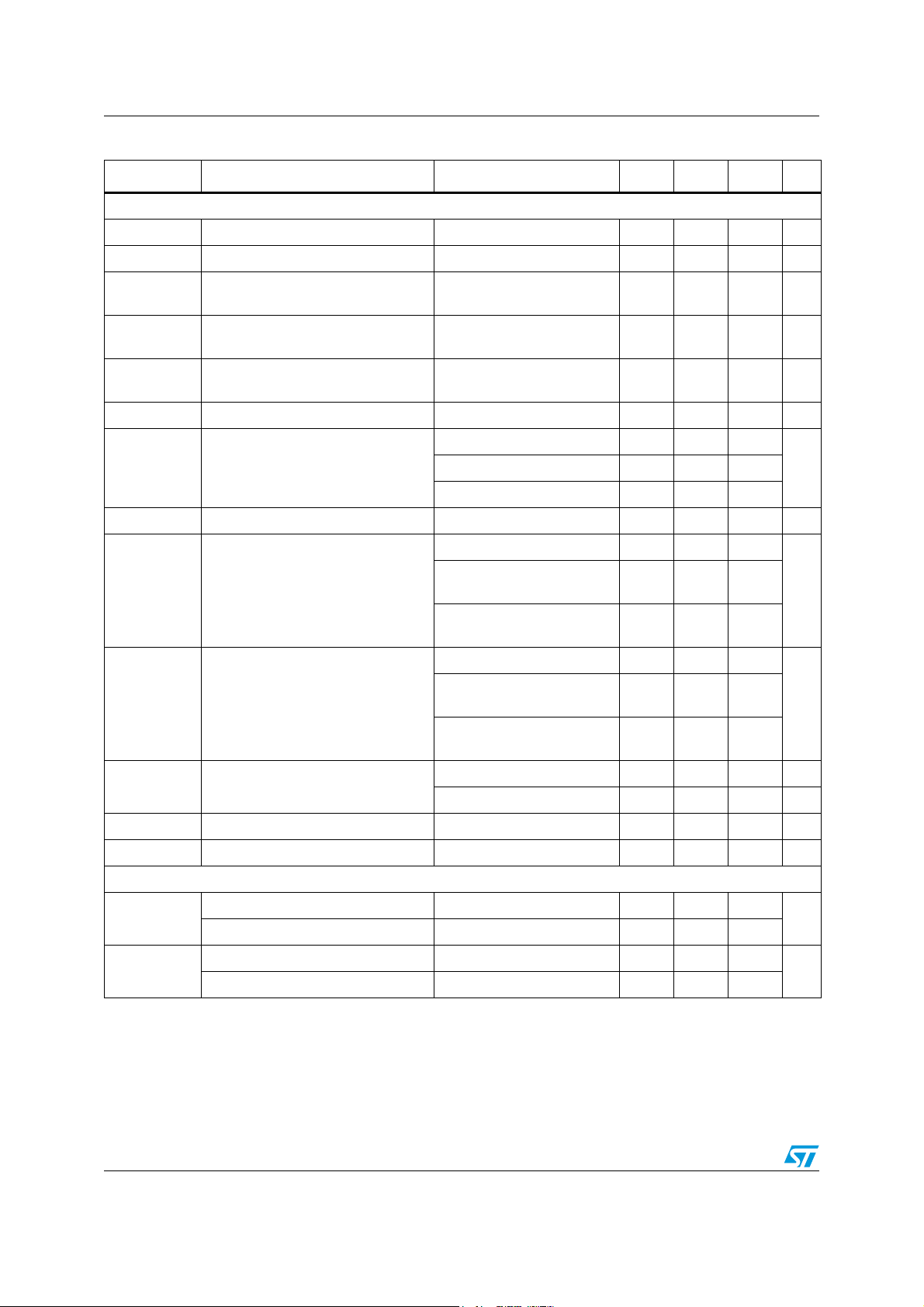

Figure 3. Test circuit

R = 32 Ω

3.4 Embedded crystal oscillator

Figure 4. Oscillator configuration

XTI

STA321

To PLL

Enable from register bit MISC[7]

XTO

Doc ID 15351 Rev 3 17/157

Electrical specifications STA321

The STA321 has an integrated oscillator between pins XTI and XTO.

The architecture is a single-stage oscillator with an inverter working as an amplifier. The

oscillator stage is biased by an internal resistor (of about 500 kΩ), and requires an external

PI network consisting of a crystal and two capacitors as shown in Figure 4 below. An enable

feature is provided in bit 7 of register MISC (address 0xC8) to stop the oscillator and thereby

to reduce power consumption.

Not all crystals operate satisfactorily with the type of oscillator used in the STA321. To find

out if a crystal is suitable for this device the following transconductance formula must be

evaluated and compared to the critical transconductance for the embedded oscillator:

Gm = Rm * ω

2

* (C + 2 * Co)2 < Gm

CRITICAL

/ 3

where ω is the crystal operating frequency, C = CA = CB, Co and Rm are shown in Figure 5

and Gm

CRITICAL

is given in Table 7 .

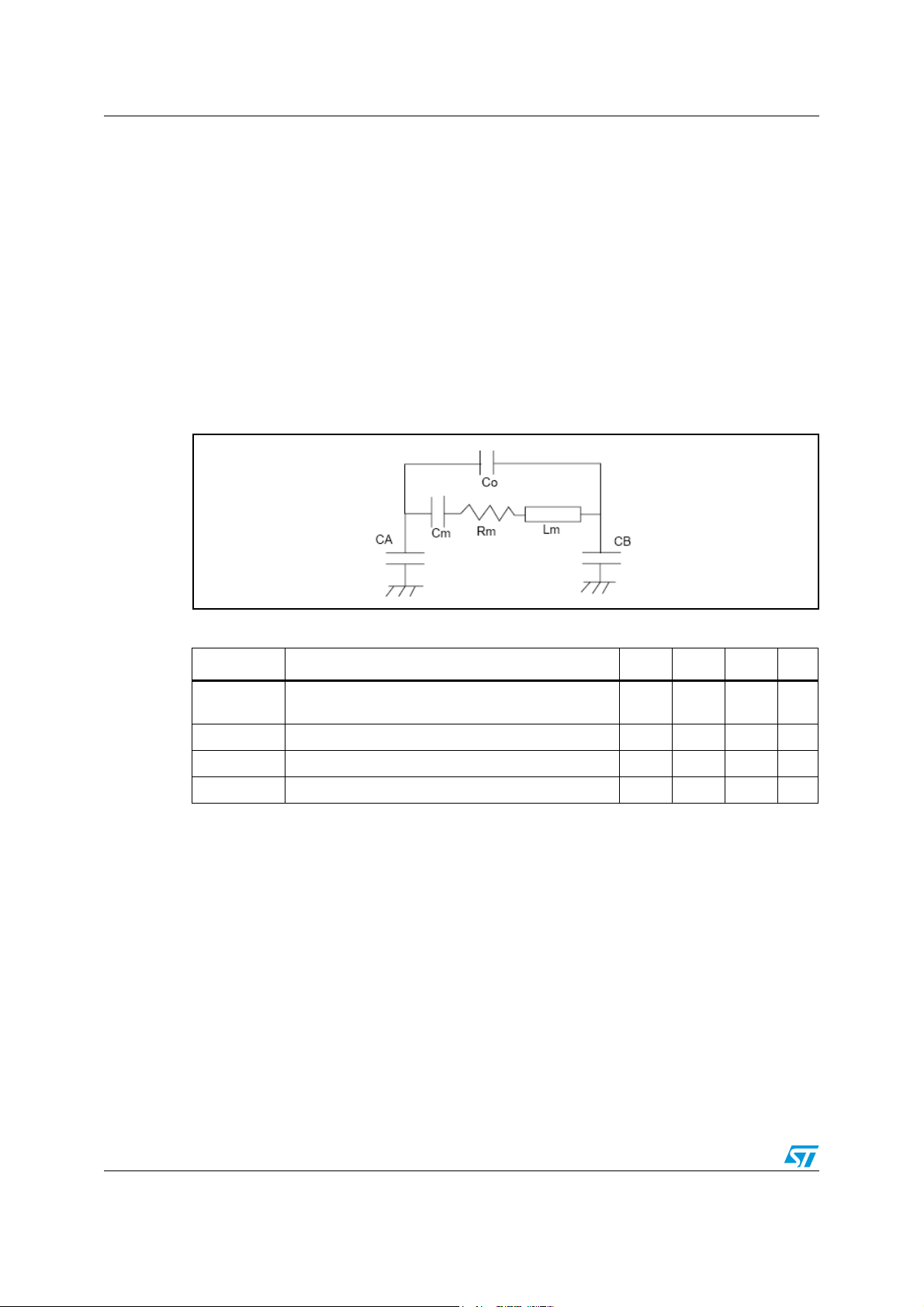

Figure 5. Equivalent circuit of crystal and external components

Table 7. Oscillator specifications

Symbol Parameter Min Typ Max Unit

I

OSC

Duty

OSC

T

UP

Gm

CRITICAL

1. If no crystal is connected then the power consumption could be much higher.

2. τx is the time constant of the crystal and external components; a typical value is 44 µs.

Oscillator power consumption with crystal

connected

(1)

--215µA

Duty cycle 46.9 47.8% 48.9 %

Startup time - 15 * τx- s

(2)

Oscillator transconductance 1060 - - µA/V

18/157 Doc ID 15351 Rev 3

STA321 Electrical specifications

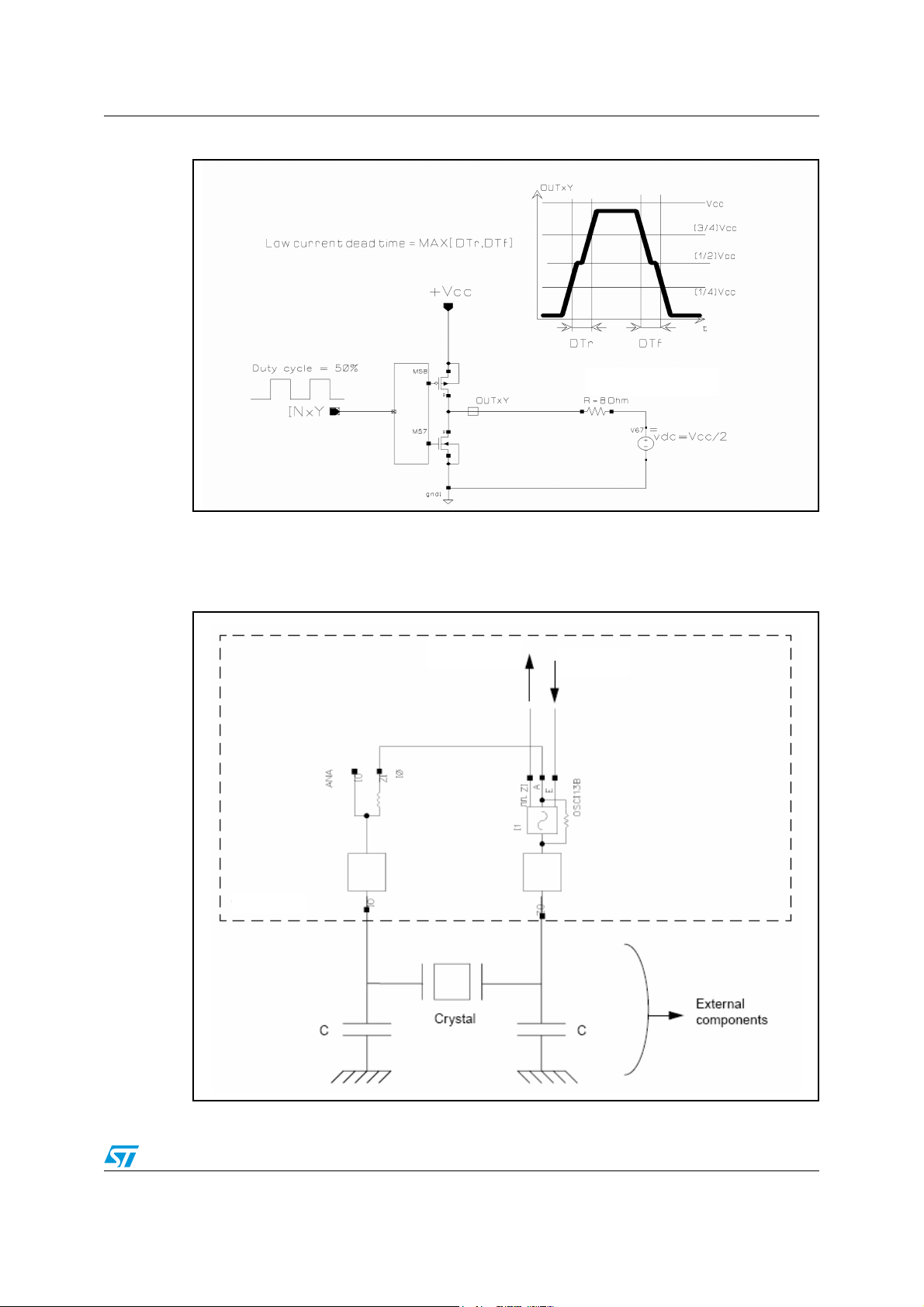

3.5 Embedded DC regulator

The power supply to the digital STA321 core and PLL is provided via embedded linear DC

regulators as shown below in Figure 6. When pin REG_BYPASS is tied to ground, the DC

regulators are active so that a voltage in the range 2.5 V to 3.6 V applied to pins VDD_REGx

or PVDD provides a regulated internal voltage to the core and the PLL. The voltages Vddi

and Vddipll range from 1.55 V to 1.95 V depending on operating conditions.

Figure 6. Embedded DC regulator scheme

PVDD

DC

DC

DC

Vddi

Vddi

Vddipll

Core

PLL

STA321

VDD_REG1

VDD_REG2

REG_BYPASS

If the application allows multiple supplies or the power supply requirements are a

fundamental constraint, pin REG_BYPASS can be tied high and a 1.8 V external supply can

be applied directly to pins VDD_REGx and PVDD. In this case the operating range for such

an external supply is 1.55 V to 1.95 V.

Embedded DC regulators imply also static power consumption that must be take into

account when the power-down modes are active. The STA321 provides a deep powerdown

mode where also the regulators are active but in a low power consumption mode (see

Section 4.3.2 on page 27).

Doc ID 15351 Rev 3 19/157

Power-up and power-down sequences STA321

K

4 Power-up and power-down sequences

4.1 Device power-up

After providing the power supply to the device, it is necessary to wait until the DC regulator

PWUP time has elapsed before the device can be set up and used for normal operations.

(see Figure 7).

Figure 7. Startup sequence

VVDDIO

VDDIO

PVDD

3v3

2v2

VDDREG

VVDD_REG

VPVDD

STBY (active H)

STBY (active H)

RSTN (active L)

RSTN (active L)

DC Reg. PWDN

PWDN (active H)

(active High)

DC Reg. A. OK

(active High)

A.OK (active H)

I2C Writings

I2C read

I2C CL

I2C clock

XTI /MCLK

XTI / MCLK

Vdd ramp

DC reg. PWUP time

Table 8. Power-up signal description

Device in reset mode

User configuration via I2C

Signal/pin Type Description

VDDIO Supply Power supply of the digital pads (= VDDIO1,2)

VDD_REG Supply Power supply of the system core (= VDD_REG1,2)

PVDD Supply Power supply of the PLL

STBY In (digital) External standby signal provided by the user

RSTN In (digital) External reset signal provided by the user

PWDN Internal Power-down of the DC regulator cell, controlled by the core

A. OK Internal DC regulator status, when active the 1.8 V is provided to the core

2

C read In (I2C) Configuration commands coming to the I2C interface

I

2

I

C clock Internal I2C peripheral clock

XTI/MCLK In (digital) Clock input source

20/157 Doc ID 15351 Rev 3

STA321 Power-up and power-down sequences

Table 9. Startup timings

Parameter Description Min Typ Max Unit

DC reg. power-up time

Device in reset mode

Table 10. Configuration example

Register

address

Start up time of the DC Regulator after

connecting the power

Must be greater than

(VDD time + DC reg. power-up time)

- - 300 µs

---µs

Value Description

0xC9 0x00 Remove PLL bypass

0xCA 0x00 Headphone detection polarity = 0

0xB8 0x4A Configure SAI output: SAI_out1 = SAI_in1, SAI_out2 = SAI_in2

0xB7 0x38 SRC source select: SRC1 = ADC, SRC2 = ADC

0xC6 0x02 ADC clock on

2

0xB2 0xF3 I

S configuration

0xC8 0x21 Core clock on, SAI/ADC audio set to 32 kHz - 48 kHz range

0xB2 0xD3 SAI_out: output enabled

0xA0 0x00 Soft volume removed

0x00 0x00 Remove bridge 3-state

4.2 Software power-down mode

The software power-down is obtained by configuring the appropriate I2C registers.

In order to obtain flexibility every peripheral has its independent, standby signal and several

gating clock cells are available.

Obviously, the I

recover from the power-down state only via the reset pin.

In the table below EA is embedded amplifier and CB is CMOS bridge. For complete

information this table must be used in conjunction with Chapter 14: Register description on

page 77.

Table 11. Registers for power-down

Put EA in standby FFXCFG1[7] 0x00 on page 81

Put CB in standby FFXCFG1[6] 0x00

Put PLL in standby PLLPFE[5] 0xC4 on page 132

Put ADC in standby ADCCFG0[3] 0xC6 on page 133

Turn core clock off MISC[0] 0xC8 on page 135

Turn ADC clock off ADCCFG0[1] 0xC6

2

C peripheral can not be turned off in this mode, otherwise the device can

Description Register bit Address

Doc ID 15351 Rev 3 21/157

Power-up and power-down sequences STA321

Table 11. Registers for power-down (continued)

Description Register bit Address

Turn SRC clock off CKOCFG[3] 0xC7 on page 134

Turn PROC clock off CKOCFG[2] 0xC7

Turn FFX clock off CKOCFG[4] 0xC7

4.2.1 Configuration example

This is an example of the register setup for power-down clock. It is assumed that every

peripheral is already configured and working correctly.

There are other configuration examples to help you get started please refer to other

chapters and also to Chapter 14: Register description on page 77 in order to get all the

necessary and complementary details.

Turn off all the peripherals.

Note: The MCLK (or XTI) must be used as system clock (sys_clk) before setting the PLL to

standby.

Table 12. Example configurations for power-down

Register bit Address Value Description

EA_STBY

CB_STBY

0x00 on page 81 0xC0

Set the embedded power amplifier and CMOS

bridge to power-down

CLK_FFX_ON 0xC7 on page 134 0x0C Turn off the FFX modulator clock

ADC_STBY 0xC6 on page 133 0x09 Set the ADC into standby mode

CLK_ADC_ON 0xC6 0x80 Turn the ADC clock off

CLK_PROC_ON 0xC7 0x08 Turn the processing clock off

CLK_SRC_ON 0xC7 0x00 Turn the sample rate converter clock to off

Bypass the PLL clock and use MCLK (or XTI) as

PLL_BYP_UNL 0xC4 on page 132 0x80

source clock when the PLL is not locked (a

safety operational mode)

PLL_PWDN 0xC4 0xA0 Put the PLL in standby

CLK_CORE_ON 0xC8 on page 135 0x00 Turning off the core clock

22/157 Doc ID 15351 Rev 3

STA321 Power-up and power-down sequences

_

_

4.3 Hardware power-down mode

The hardware power-down is obtained by asserting pin STBY to high.

There are two power-down options available, namely mild mode and full (or deep) mode,

that could be selected using the DC_STBY_EN signal in register STBY_MODES

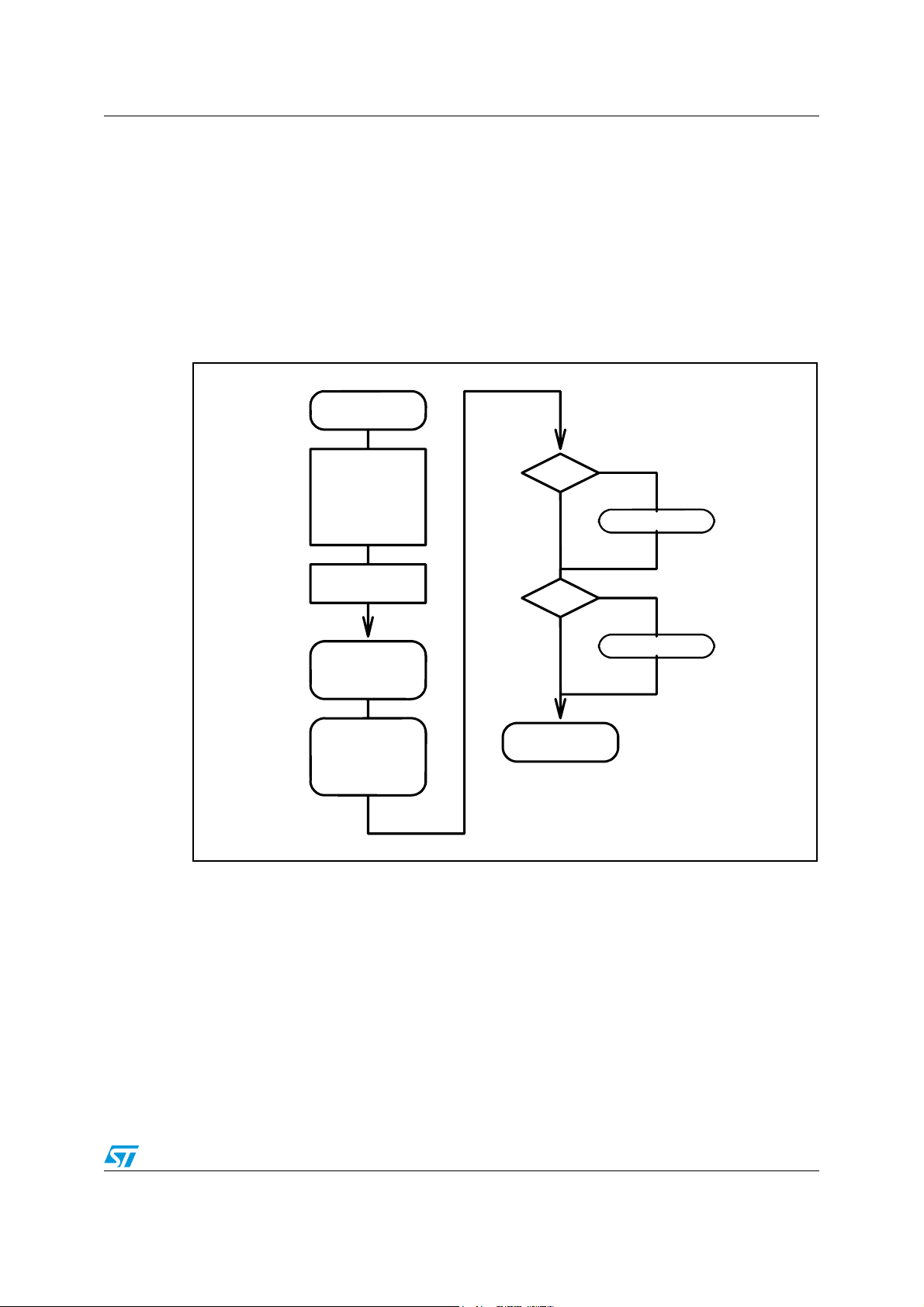

Figure 8 summarizes the main power-down sequence. “Power on” is the normal operating

status where all the startup procedures have already been executed. The rectangular boxes

indicate the steps to be done by the user whilst the rounded boxes indicate the steps done

by the device.

Figure 8. Hardware power-done sequence

Power on

2

I

C programming

register

STBY_MODES

bits:

CMP_EN_N

DC_STBY_EN

CMP_EN_N = 1 ?

NO

YES

Comp Cell Pwdn

Pin STBY <= 1'

DC_STBY_EN = 1 ?

NO

YES

DC Reg. Stby

Embedded amp.

CMOS bridge

Powerdown

I2C off

CLK

CLK

ADC off

Power-down mode

CLK Core off

PLL power down

Doc ID 15351 Rev 3 23/157

Power-up and power-down sequences STA321

Table 13. Frequently used signals

Name Description

STBY Input pin STBY on page 11

PWDN

DC regulator

Internal

A. OK

DC regulator

Internal

CMP_EN_N Bit 1, register STBY_MODES on page 139

EA_STBY

CB_STBY

Bits 7:6, register FFXCFG1 on page 81

EA/CB volume Internal

PLL_UNLOCK Bit 7, register PLLST on page 132

PLL_PWDN Bit 5, register PLLPFE on page 132

CLK_PROC_ON Bit 2, register CKOCFG on page 134

CLK_PROC Processing clock

CLK_FFX_ON Bit 4, register CKOCFG on page 134

clk_ffx FFX clock

CLK_ADC_ON Bit 1, register ADCCFG0 on page 133

clk_adc ADC clock

CLK_SRC_ON Bit 3, register CKOCFG on page 134

clk_src SRC clock

CMP_EN_N Bit 1, register STBY_MODES on page 139

DC_STBY_EN Bit 0, register STBY_MODES on page 139

FFX_ULCK_PLL Bits 4:3, register FFXCFG1 on page 81

24/157 Doc ID 15351 Rev 3

STA321 Power-up and power-down sequences

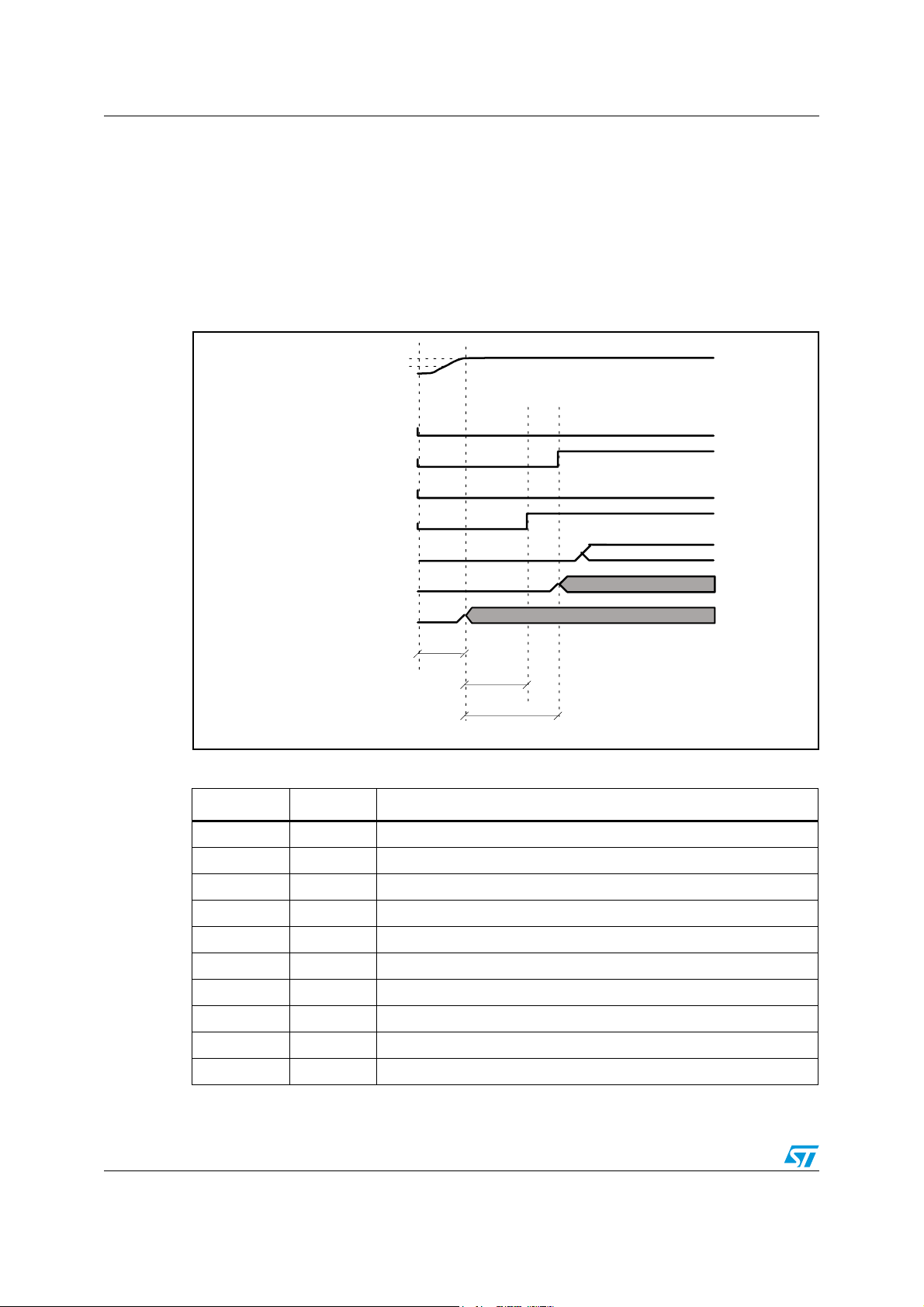

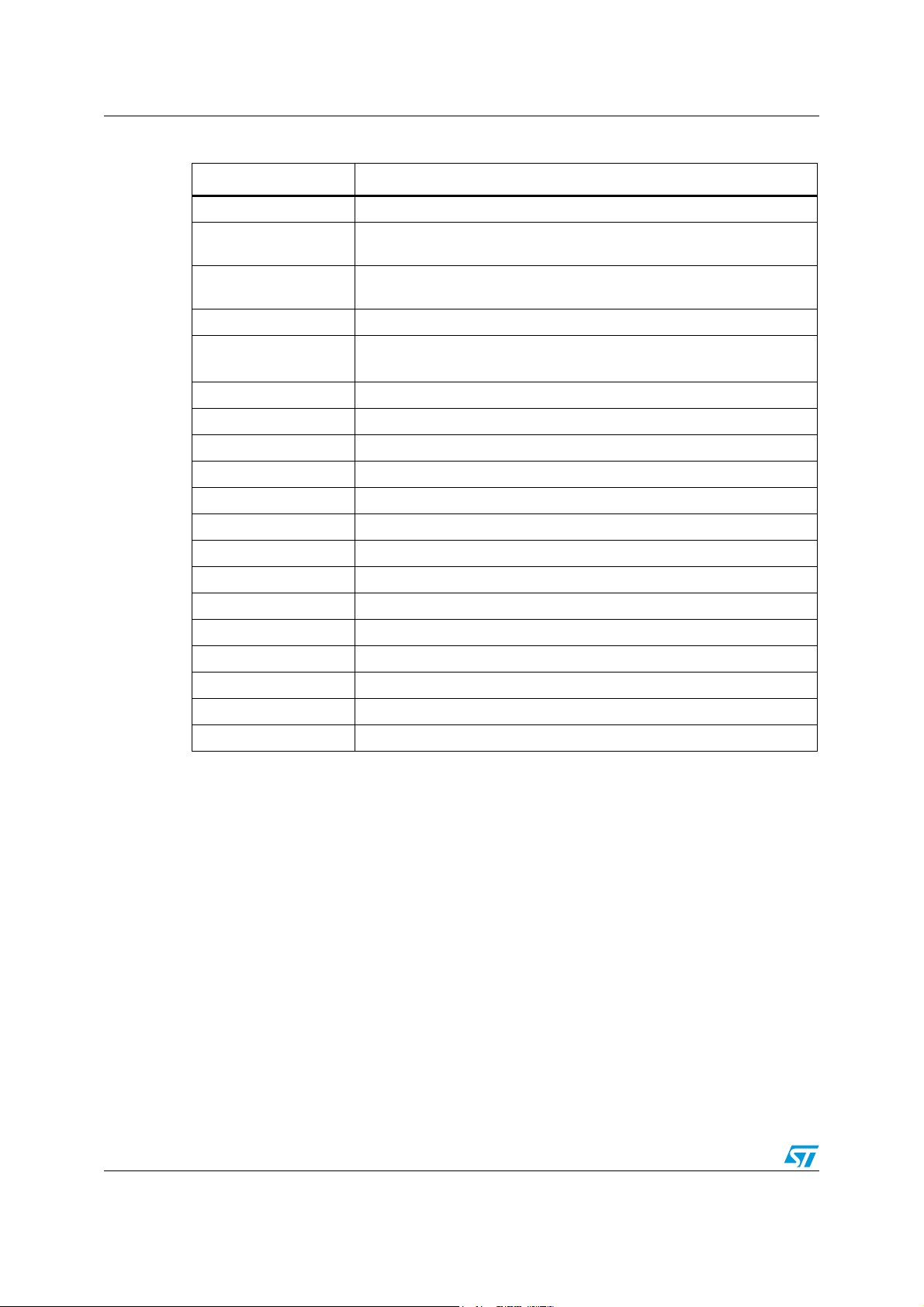

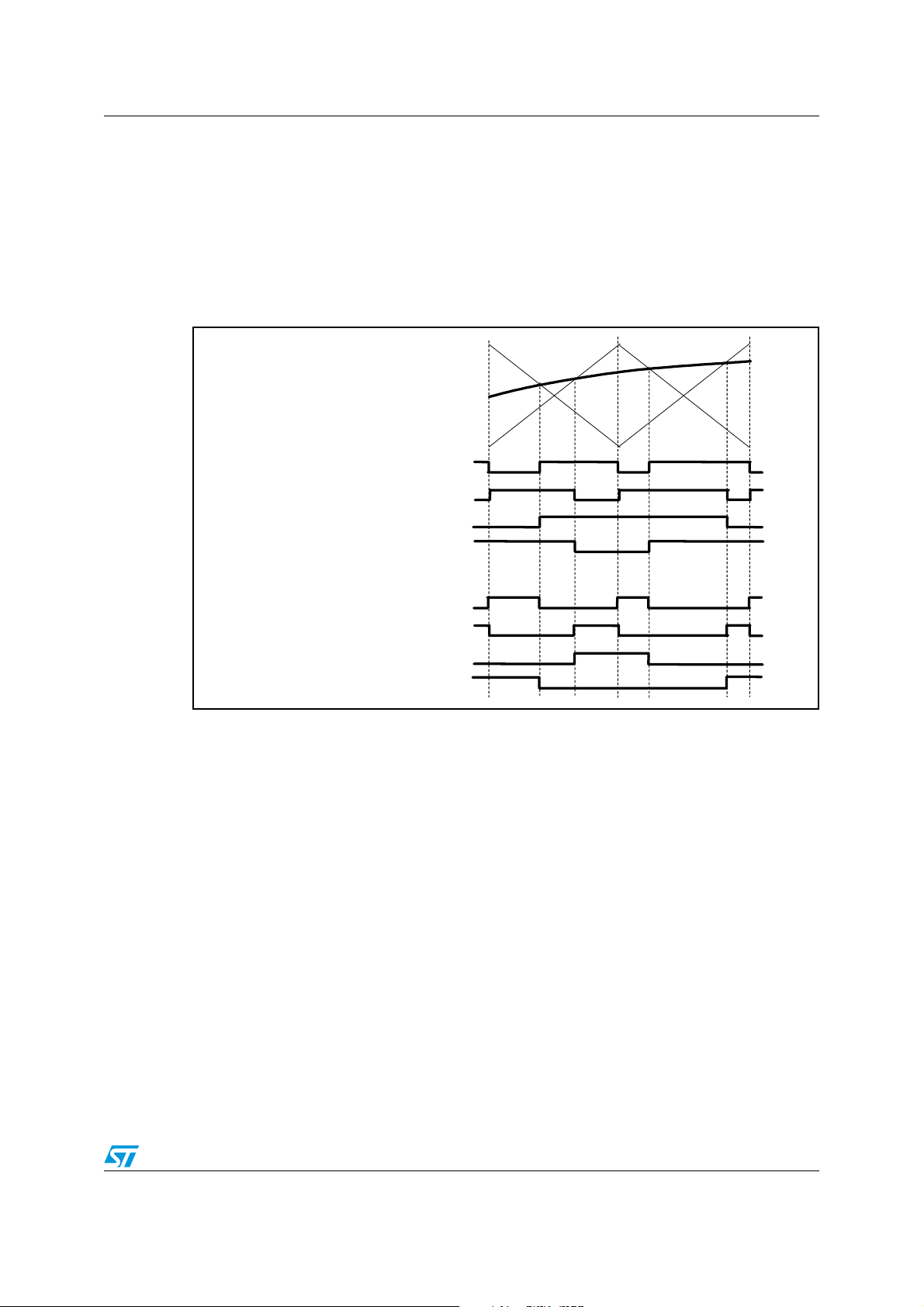

4.3.1 Mild power-down

In this case, the device is put into a mild power-down mode.

All the peripherals are set to standby and their clocks turned off.

2

The I

C configuration is not required as the default values of the registers are sufficient.

z Initial conditions:

FFX_ULCK_PLL = 10

CMP_EN_N = 0

DC_STBY_EN = 0

z Going into power-down:

After the assertion of the pin STBY, the following actions are taken by the device:

1. Embedded amplifier (EA) and CMOS bridge (CB) volume are set to mute (the length of

this step changes according to the fade-out ramp configuration).

2. EA and CB are put into power-down.

After the previous operation is completed:

3. All peripherals are turned off (regardless the register settings).

4. The PLL clock is bypassed, the system clock (sys_clk in Figure 11 on page 29) is XTI.

5. All clocks are shut down.

z Returning to normal mode:

After the release of the pin STBY, the power-up procedure takes place:

1. All clocks are turned on.

2. All peripherals are restored to their previous status (based on the last register settings).

3. If the PLL clock was the system clock it will be selected again after the locking time.

4. The EA and the CB execute the fade-in procedure before becoming ready to be used

(the length of this step changes according to the fade-in ramp configuration).

Doc ID 15351 Rev 3 25/157

Power-up and power-down sequences STA321

Figure 9. Hardware powerdown sequence (mild mode)

STBY (active H)

DC Reg. PWDN

(active High)

DC Reg. A. OK

(active High)

Comp Cell PWDN

(active High)

EA is in Pwdn

EA Volume

CB is in Pwdn

CB Volume

PLL LOCKED

(active High)

PLL_PWDN

(active High)

I2C [CORE_CLK_ON]

CLK_I2C

Operational Volume

Operational Volume

MUTE O.V.

O.V.MUTE

I2C [CLK_PROC_ON]

CLK_PROC_CLK

I2C [CLK_FFX_ON]

CLK_FFX_CLK

I2C [CLK_ADC_ON]

CLK_ADC_CLK

I2C [CLK_SRC_ON]

CLK_SRC_CLK

E.A Fade InE.A Fade Out

Bridge Fade Out Bridge Fade In

PLL Locking Time

26/157 Doc ID 15351 Rev 3

STA321 Power-up and power-down sequences

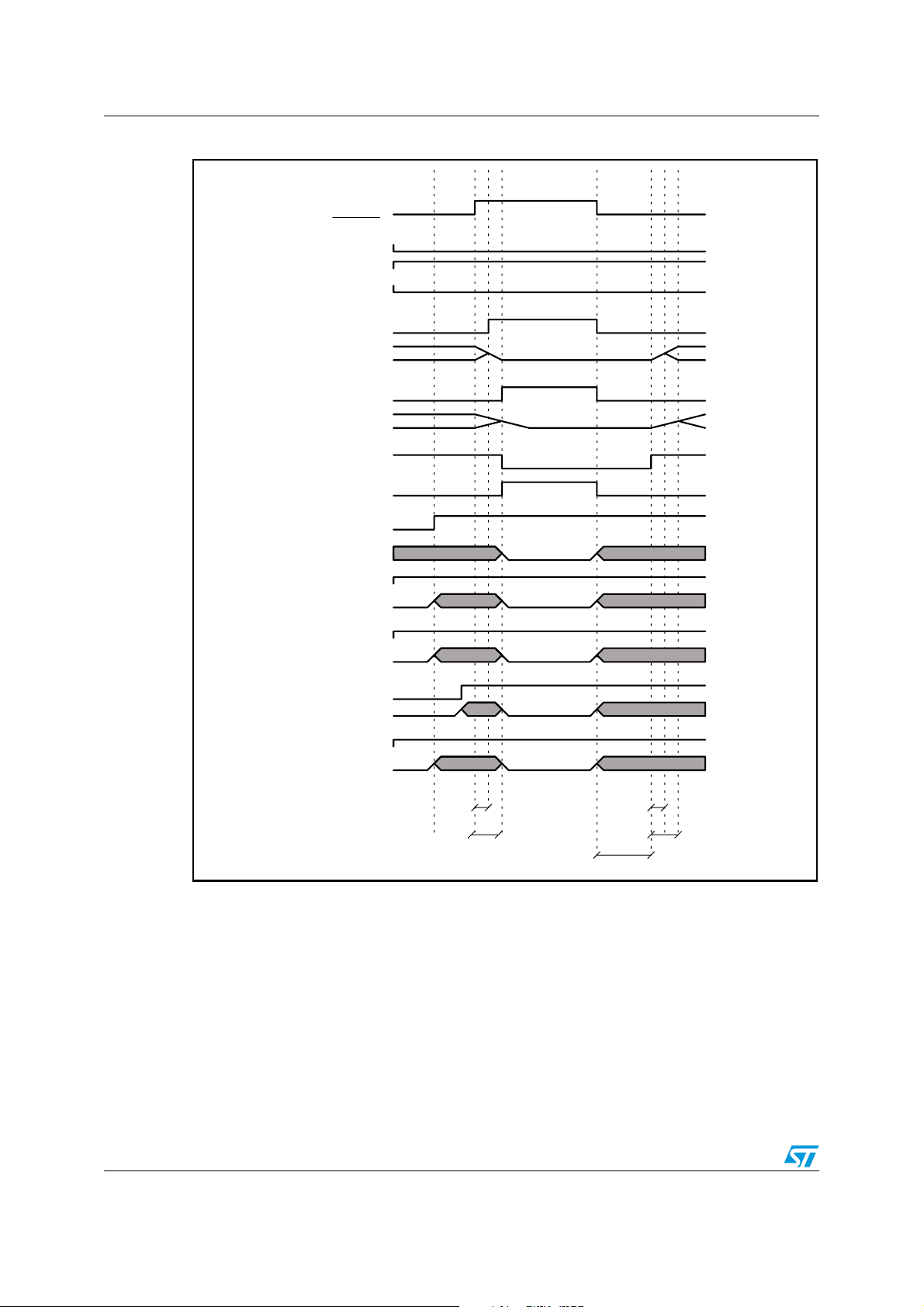

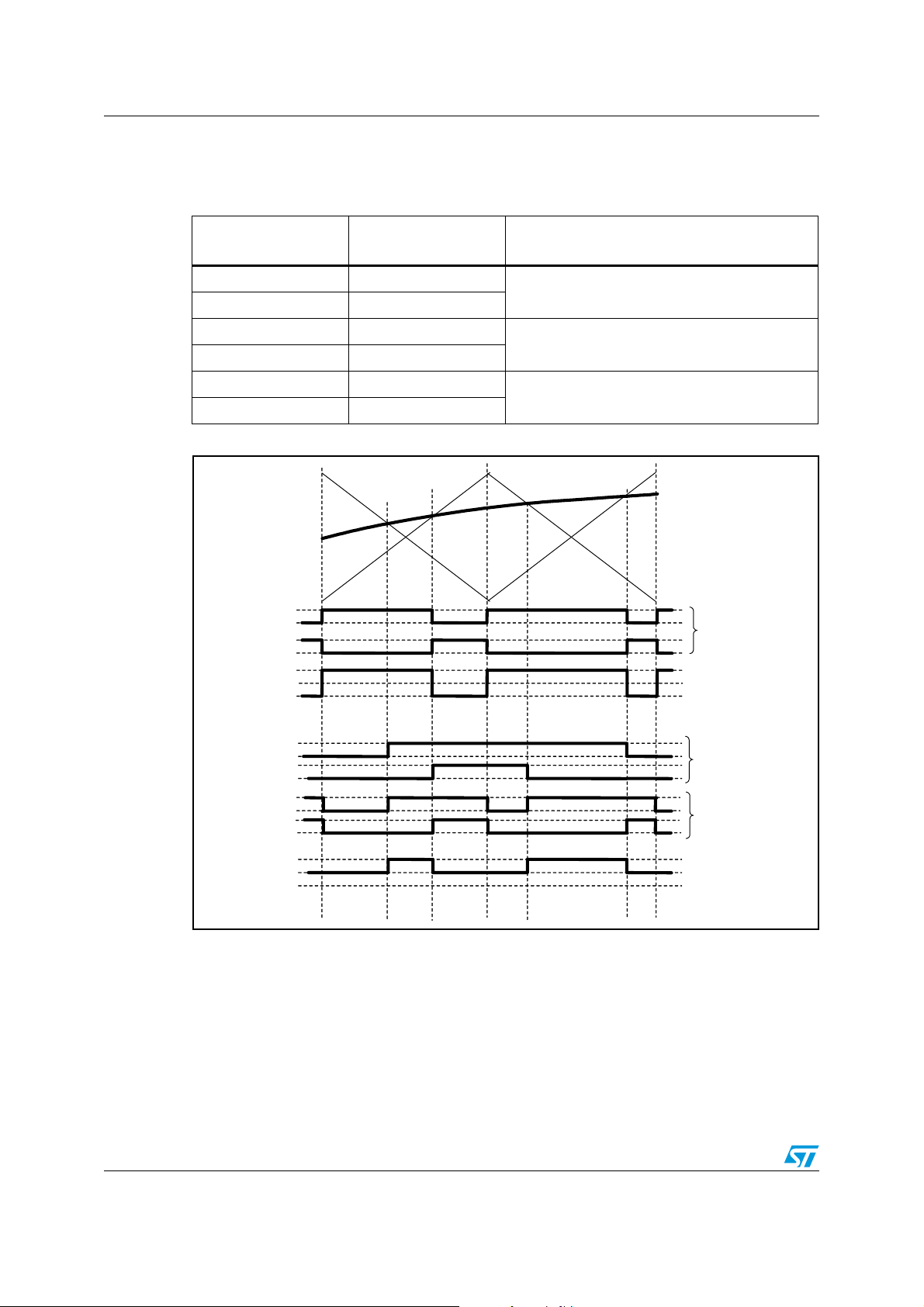

4.3.2 Full power-down

In this case the device is put into a full power-down mode.

This implies lower power consumption than the mild mode, but has a drawback in that it

takes longer to execute.

z Initial conditions

FFX_ULCK_PLL = 10

CMP_EN_N = 1

DC_STBY_EN = 1

z Going into power-down:

This mode differs from the previous one by an additional step at the end of the powerdown procedure and at the beginning of the power-up:

1. Embedded amplifier (EA) and CMOS bridge (CB) volume are set to mute (the length of

this step changes according to the fade-out ramp configuration).

2. EA and CB are put into power-down.

After the acknowledge signals (EA is in power-down and CB is in power-down) are

received:

3. All peripherals are turned off (regardless the register settings).

4. PLL clock is bypassed, the system clock (sys_clk in Figure 11 on page 29) is XTI.

5. All clocks are shut down.

6. DC regulator is put into standby mode. After this point the device is in a very low power

consumption mode.

z Returning to normal mode:

After the release of pin STBY, the power-up procedure will take place:

1. DC regulator is set to operational mode

After the acknowledge signal (DCAOK) from the DC regulator is received:

2. All clocks are turned on.

3. All peripherals are restored to the status based on their relative register settings.

4. If the PLL clock was the system clock it is selected again after the locking time.

5. The EA and the CB execute the fade-in procedure before being ready to be used (the

length of this step changes according to the fade-in ramp configuration).

Doc ID 15351 Rev 3 27/157

Power-up and power-down sequences STA321

DC- Td

Figure 10. Hardware power-down sequence (full mode)

STBY (active H)

DC Reg. PWDN

(active High)

DC Reg. A. OK

(active High)

Comp Cell PWDN

(active High)

EA is in Pwdn

EA Volume

CB is in Pwdn

CB Volume

PLL LOCKED

(active High)

PLL_PWDN

(active High)

I2C [CORE_CLK_ON]

CLK_I2C

own

Operational Volume

Operational Volume

DC- Tup

MUTE O.V.

O.V.MUTE

I2C [CLK_ PROC_ON]

CLK_PROC_CLK

I2C [CLK_FFX_ON]

CLK_FFX_CLK

I2C [CLK_ADC_ON]

CLK_AD C_CLK

I2C [CLK_SRC_ON]

CLK_SRC_CLK

E.A Fade InE.A Fade Out

Bridge Fade Ou t Bridge Fade In

PLL Locking Time

28/157 Doc ID 15351 Rev 3

STA321 Clock management

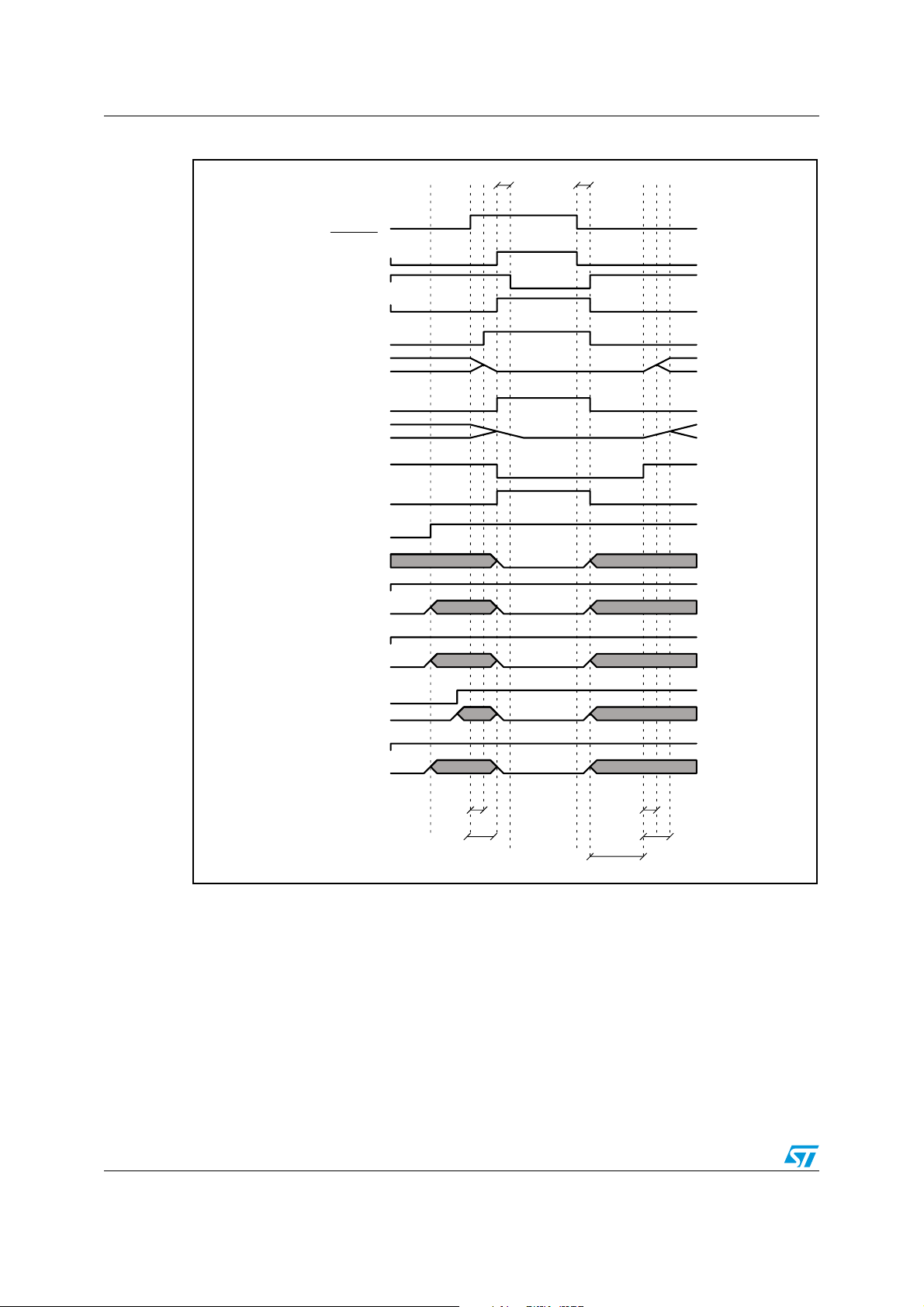

5 Clock management

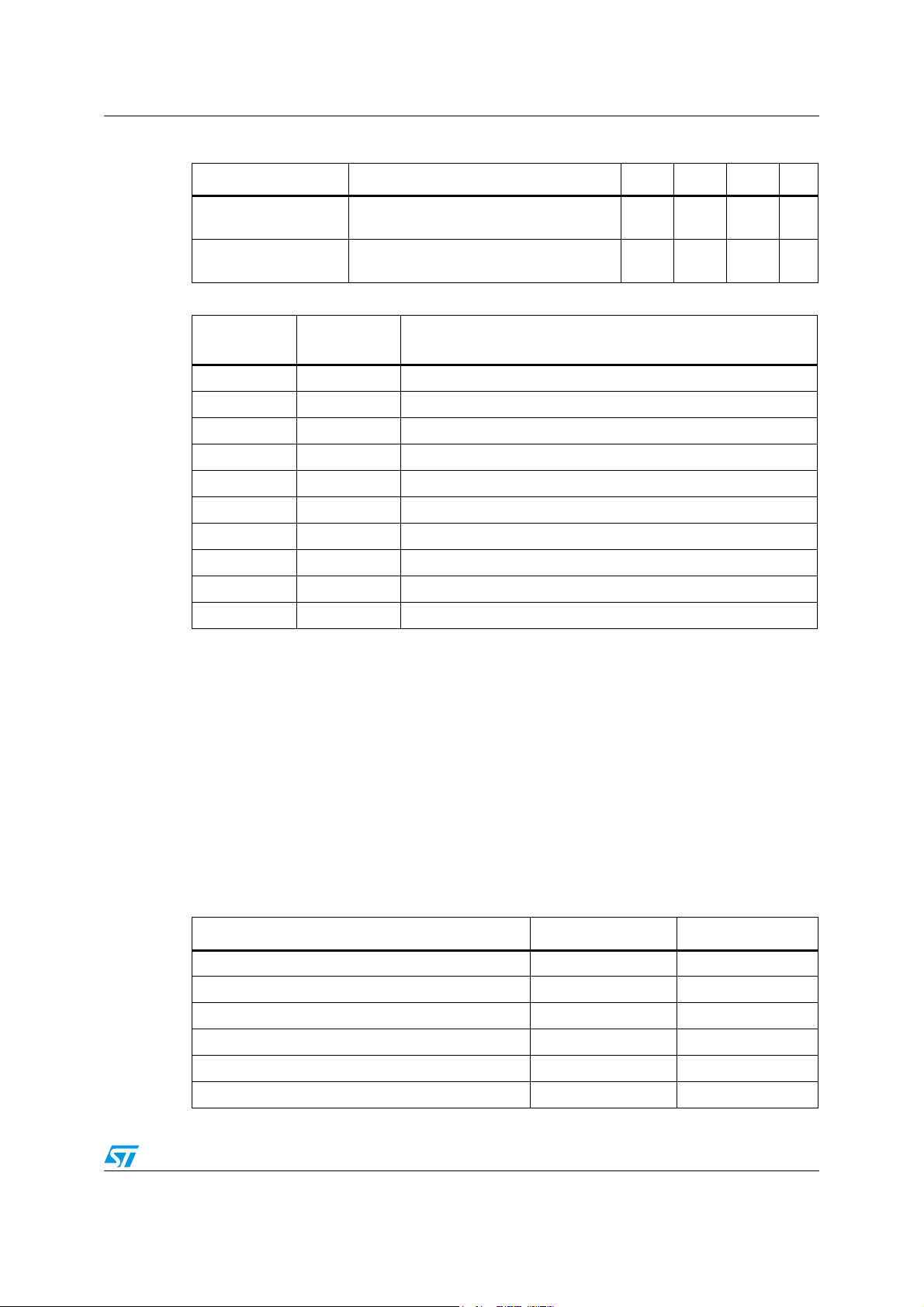

Figure 11. Clock management scheme

CKOCFG[6:5]

CLKOUT_SEL

11

1/2

1/8

1/8

1/4

10

00

01

1/2

1/2

1/2

1/2

clk_i2c

clk_ffx

clk_src

clk_proc

clk_adc

CLKOUT

FFX

SAI_in1

SAI_in2

BICLKI1

MCLK

XTI

OR

PLLPFE[6]

BICLK2PLL

pll_clk_in_i

1

0

PLL

PLLB[7]

CLK_CORE_ON

CKOCFG[4]

CLK_FFX_ON

CKOCFG[3]

CLK_SRC_ON

CKOCFG[2]

CLK_PROC_ON

ADCCFG[1]

CLK_ADC_ON

sys_clk

1

0

Clock management

MISC[0]

ADC

1/4

0

clk_adc_in

1

PLLB[5] ADC_CLKSEL

clk_proc

1

0

1

0

SAI_out1

SAI_out2

PLLB[3] P2S1_CLKSEL

PLLB[1] P2S2_CLKSEL

Table 14. Clock control registers

Register Name Address

PLLB on page 136 0xC9

ADCCFG0 on page 133 0xC6

CKOCFG on page 134 0xC7

Doc ID 15351 Rev 3 29/157

Clock management STA321

Table 15. Clock characteristics

Symbol Parameter Min Typ Max Unit

f

MCLK_Range

Duty

MCLK

t

MCLK_RF

f

XTI_Range

Duty

XTI

t

XTI_RF

f

BICLK1_Range

Duty

BICLK1

t

BICLK1_RF

f

CLKOUT_Range

Input clock frequency range 2.048 - 49.152 MHz

Input clock duty cycle 40 - 60 %

Input clock rise/fall time - - 0.2 ns

Input clock frequency range 2.048 - 49.152 MHz

Input clock duty cycle 40 - 60 %

Input clock rise/fall time - - 0.2 ns

Input clock frequency range 2.048 - 49.152 MHz

Input clock duty cycle 40 - 60 %

Input clock rise/fall time - - 0.2 ns

Output clock frequency range - - 49.152 MHz

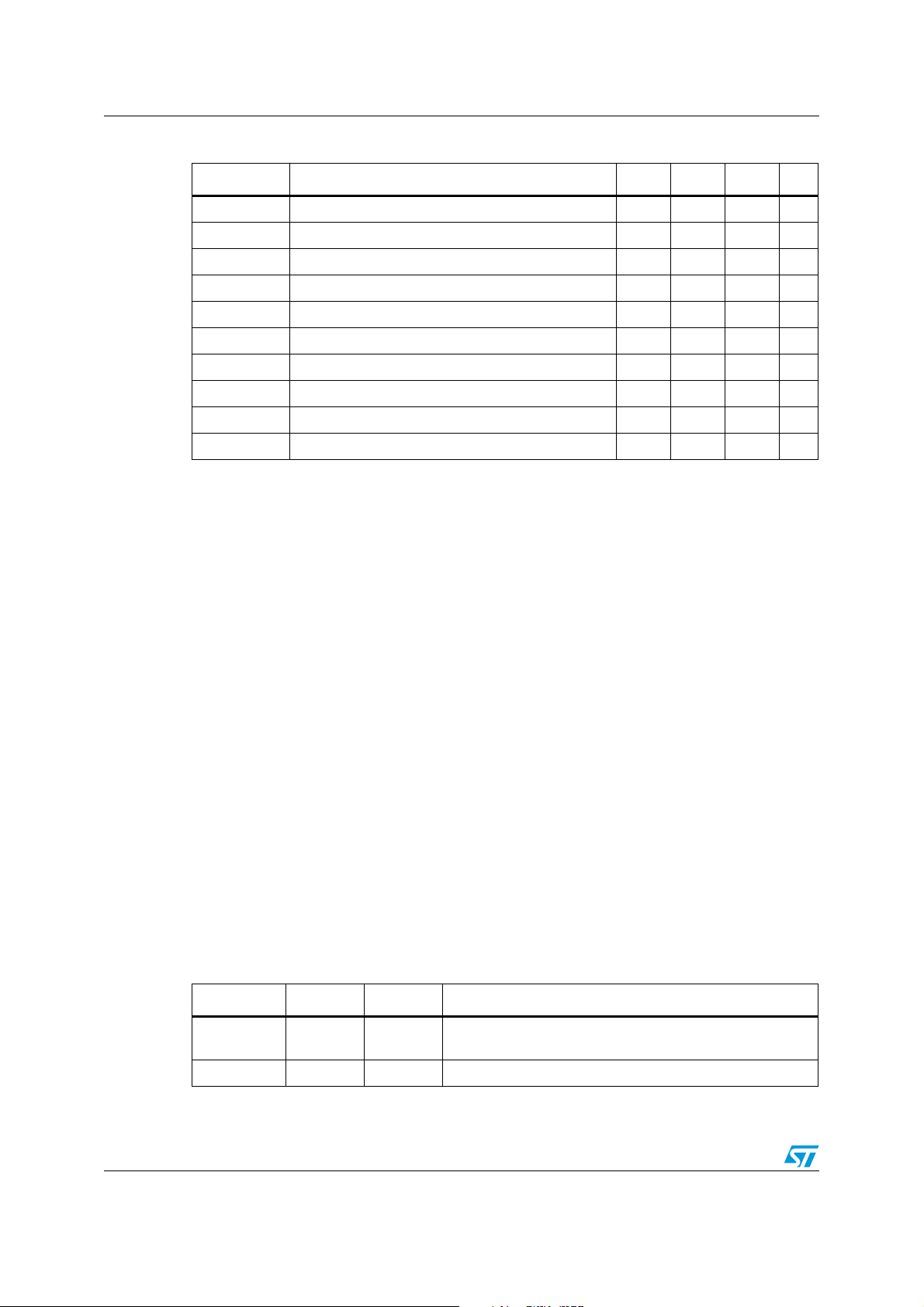

5.1 System clock

Figure 11 above shows the STA321 clock management scheme with all the major clocks. As

can be seen, the system clock (sys_clk) is selected from one of three sources by using

register PLLB on page 136:

z an external clock BICLKI1

z (default) an external clock XTI or MCLK (the unused one must, however, be set to 0)

z the internal PLL.

If the PLL is used there are some design constraints:

z pll_clk_in_i must be in the range: 2.048 MHz to 49.152 MHz

z pll_clk_out must be in the range: 65.536 MHz to 98.304 MHz.

The sys_clk is routed to the peripherals through the clock manager section.

5.1.1 Configuration example

This is an example of the PLL register setup. It is assumed that every peripheral is already

configured and working correctly.

There are other configuration examples to help you get started please refer to other

chapters and also to Chapter 14: Register description on page 77 in order to get all the

necessary and complementary details.

Starting with MCLK as system clock switching to PLL as source

Table 16. Register setup to provide sys_clk from MCLK to PLL

Register Address Value Description

PLLPFE 0xC4 0x80

PLLB 0xC9 0x00 Remove the PLL bypass and use its clock as system

Safety operational mode: automatic use of MCLK (or XTI)

as system clock if the PLL is not locked

30/157 Doc ID 15351 Rev 3

STA321 Clock management

r

5.2 Peripheral clock manager

This block manages the clocks of the core processing peripherals ADC, FFX, PROC

(including memories and SAI interfaces) and SRC.

A clock divider (by 2) is attached before every block except the FFX.

Each block is attached to a global gating cell and to a dedicated one. This allows a flexible

power-consumption management because it is possible to turn off either the whole

processing chain or just a single block. The only exception is the I

2

C peripheral clock which

is disabled only when the device is in hardware power-down mode. In all the other cases this

clock remains active.

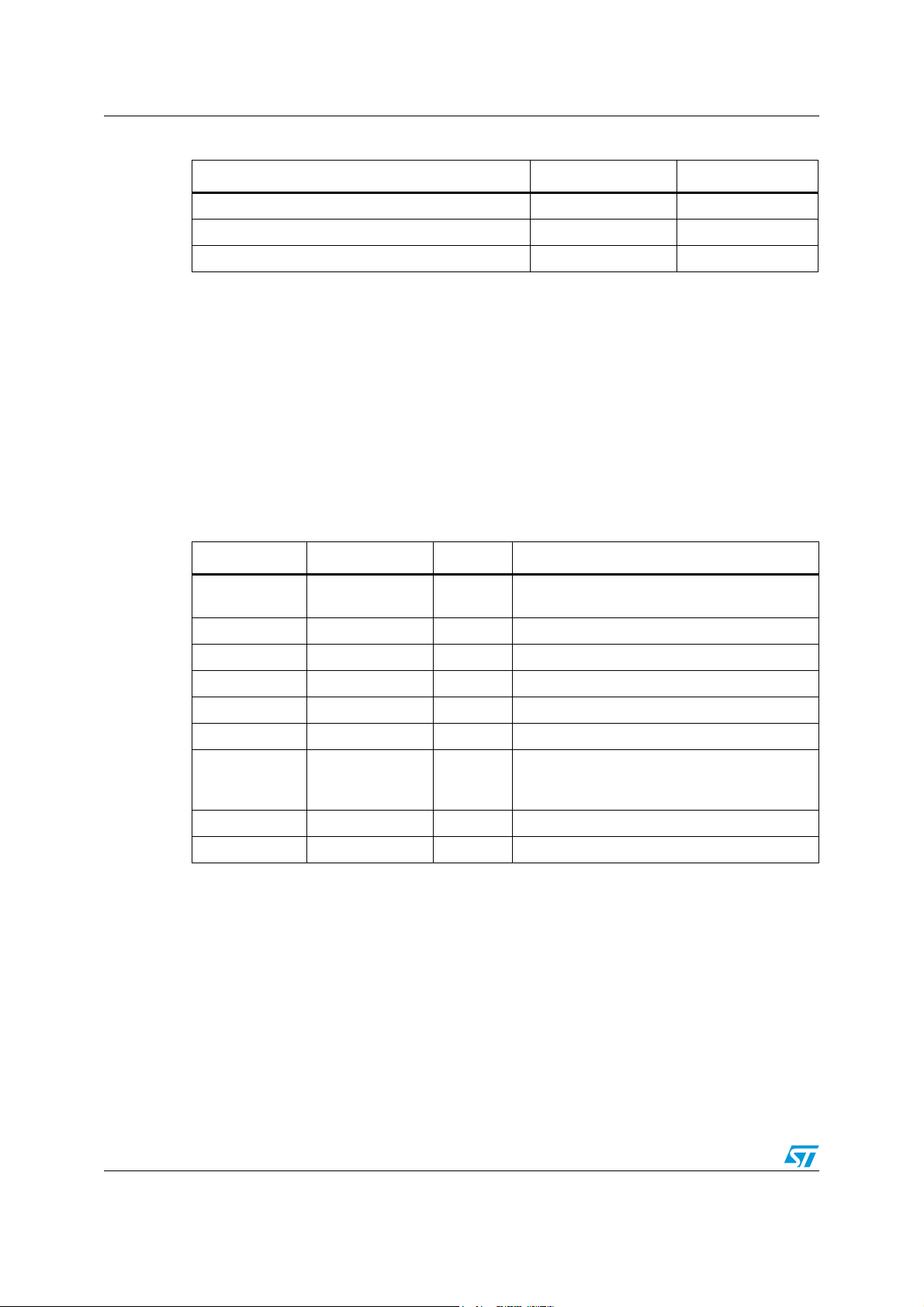

5.3 Fractional PLL

The PLL specifications are given in Table 6 on page 14.

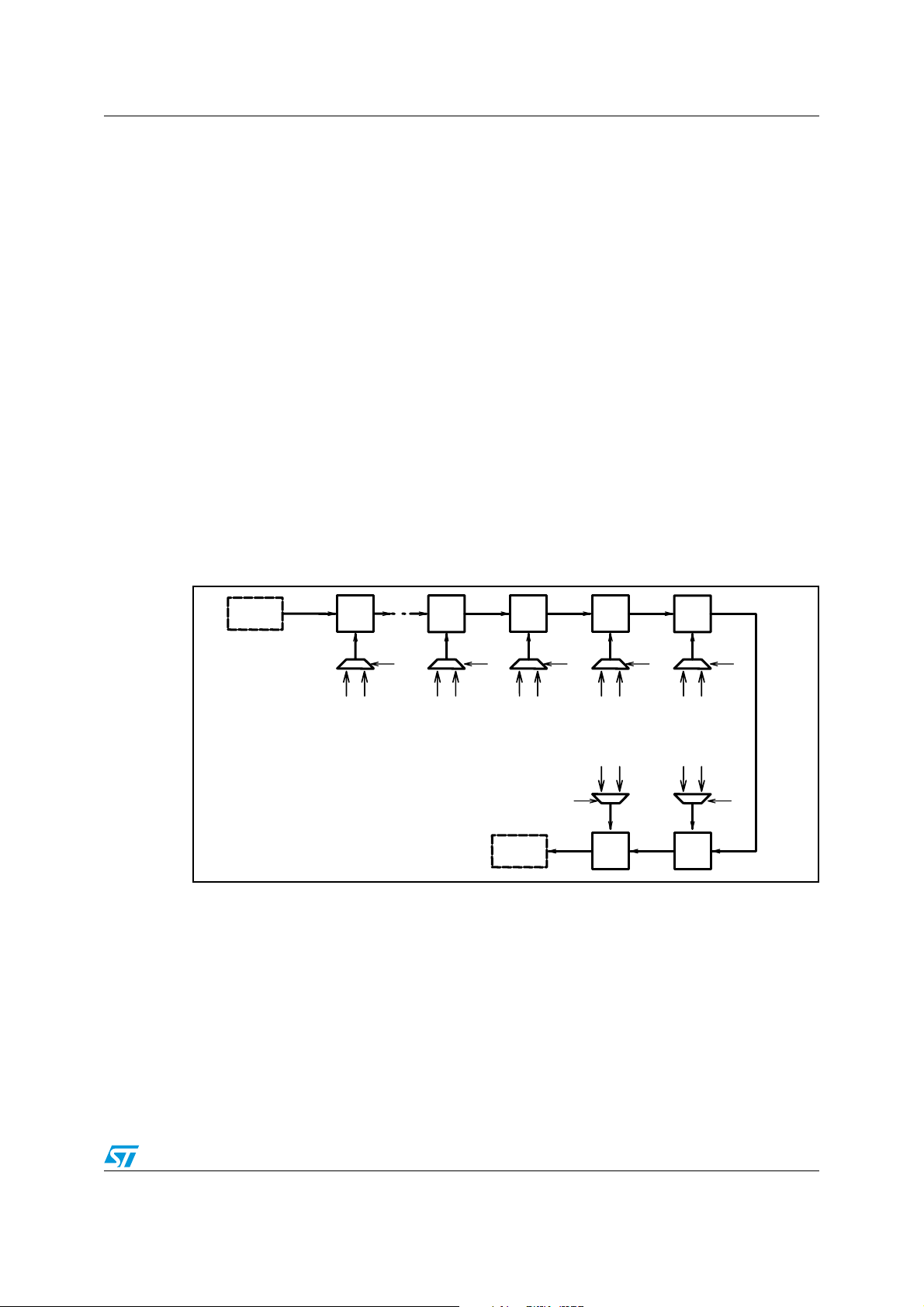

Figure 12. PLL block diagram

PLL_CLK_in

pll_clk_in

PLLCFG0(3-0)

PLLCFG0[3:0]

CLKIN

CLKIN

IDF

IDF

IDF

Input freq. divider

Lock detect

F_INT

LOCKP

LOCKP

PLLCFG3(7)

PLLCFG3[7]

PLLCFG3[6]

PLLCFG3(6)

PLLCFG0[6]

PLL_FR_CTRL

PLLCFG0(6)

5.3.1 PLL block description

Phase/frequency detector (PFD)

This block compares the phase difference between the corresponding rising edges of the

F_INT and the clock coming from the loop frequency divider.

It generates voltage pulses with widths proportional to the input phase error.

Charge pump and loop filter (LPF/CPUMP)

PLL_PWDN

PLL_PWDN

pll_strb

PLL_STRB

pll_strbbyp

PLL_STRBBYP

pll_fr_ctrl

Buffer

DITHER

DITHER

Disable

PLLCFG0(5-4) PLLCFG1(7-0)

Disable

PLLCFG0[5:4]

PFD

LDF

Loop freq. divider

Fractional

controlle

FRAC

FRAC

Input

Input

PLLCFG2(7-0)

PLLCFG1[7:0]

PLLCFG2[7:0]

LPF

cpump

NDIV

NDIV

PLLCFG3(5-0)

PLLCFG3[5:0]

VCO

FVCO

FVCO

This block converts the voltage pulses from the phase/frequency detector to current pulses

which charge the loop filter and generate the control voltage for the voltage controlled

oscillator (VCO).

Doc ID 15351 Rev 3 31/157

Clock management STA321

Voltage controlled oscillator (VCO)

This is the oscillator inside the PLL, which produces a frequency, f

proportional to the input control voltage.

Input frequency divider (IDF)

This frequency divider divides the PLL input clock CLKIN by the input division factor (IDF) to

generate the PFD input frequency. IDF is programmed in register PLLCFG0[3:0].

Loop frequency divider (LDF)

This frequency divider is present within the PLL for dividing the VCO output by the loop

division factor (LDF). LDF is programmed in register bits PLLCFG3[5:0].

Lock circuit

The output of this block, signal LOCKP, is asserted high when the PLL enters the state of

coarse lock in which the output frequency is ±10% of the desired frequency. LOCKP is

refreshed every 32 cycles of F_INT. The status bit PLL_UNLOCK is in register PLLST on

page 132.

5.3.2 Output frequency computation

The input clock frequency of the phase/frequency detector (PFD) is

f

= CLKIN / IDF

F_INT

The VCO frequency depends on the value of register bit PLLCFG0.PLL_FR_CTRL such

that

, on output FVCO

VCO

When PLL_FR_CTRL = 1

f

VCO

= f

* (LDF + FRAC / 216 + 1 / 217)

F_INT

and when PLL_FR_CTRL = 0

f

VCO

= f

F_INT

* LDF

Notes:

1. When dither is disabled (PLL_DDIS = 1), the factor 1 / 2

17

is not used in the multiplication.

2. There are some limits to the input and output frequencies as given in Ta bl e 1 7 and

Ta bl e 1 8 when selecting the values for IDF, LDF, and FRAC.

3. The LDF values of 5, 6 and 7 cannot be used when fractional synthesis mode is on, that

is, when PLL_FR_CTRL = 1.

4. The fractional control bits (FRAC_INPUT) must be set to the required values before

activating the fractional synthesis mode.

Table 17. Input division factor (IDF)

IDF[3] IDF[2] IDF[1] IDF[0] Input division factor (IDF)

00001

00011

00102

……………

32/157 Doc ID 15351 Rev 3

STA321 Clock management

Table 17. Input division factor (IDF) (continued)

IDF[3] IDF[2] IDF[1] IDF[0] Input division factor (IDF)

111014

111115

Table 18. Loop division factor (LDF)

NDIV[5] NDIV[4] NDIV[3] NDIV[2] NDIV[1] NDIV[0] Loop division factor (LDF)

0000xxNA

000100NA

0001015

0001106 (see note 3)

0001117 (see note 3)

0010008

…………………

11011054

11011155

(1)

111xxxNA

1. The LDF values of 5, 6 and 7 cannot be used when fractional synthesis mode is ON (PLL_FR_CTRL = 1)

Doc ID 15351 Rev 3 33/157

Digital processing stage STA321

r

r

6 Digital processing stage

6.1 Signal processing flow

The STA321 provides 4 channels of audio signal processing. The block diagram is shown in

the following figure.

Figure 13. Processing flow

-1

kZ

kZ

kZ

kZ

Delay

Vol 0

-1

-1

-1

Post mix

Vol 1

Vol 2

Volume control

Master volume

Limite

FFX modulator

Processing data mux

Sample

rate

converte

- G0

- G1

Pre mix

- G2

- G3 Vol 3

Pre scaler

Bq0

Bq0

Bq0

Bq0

EQ - tone control

Bq12

Bq12

Bq12

Bq12

13 biquads

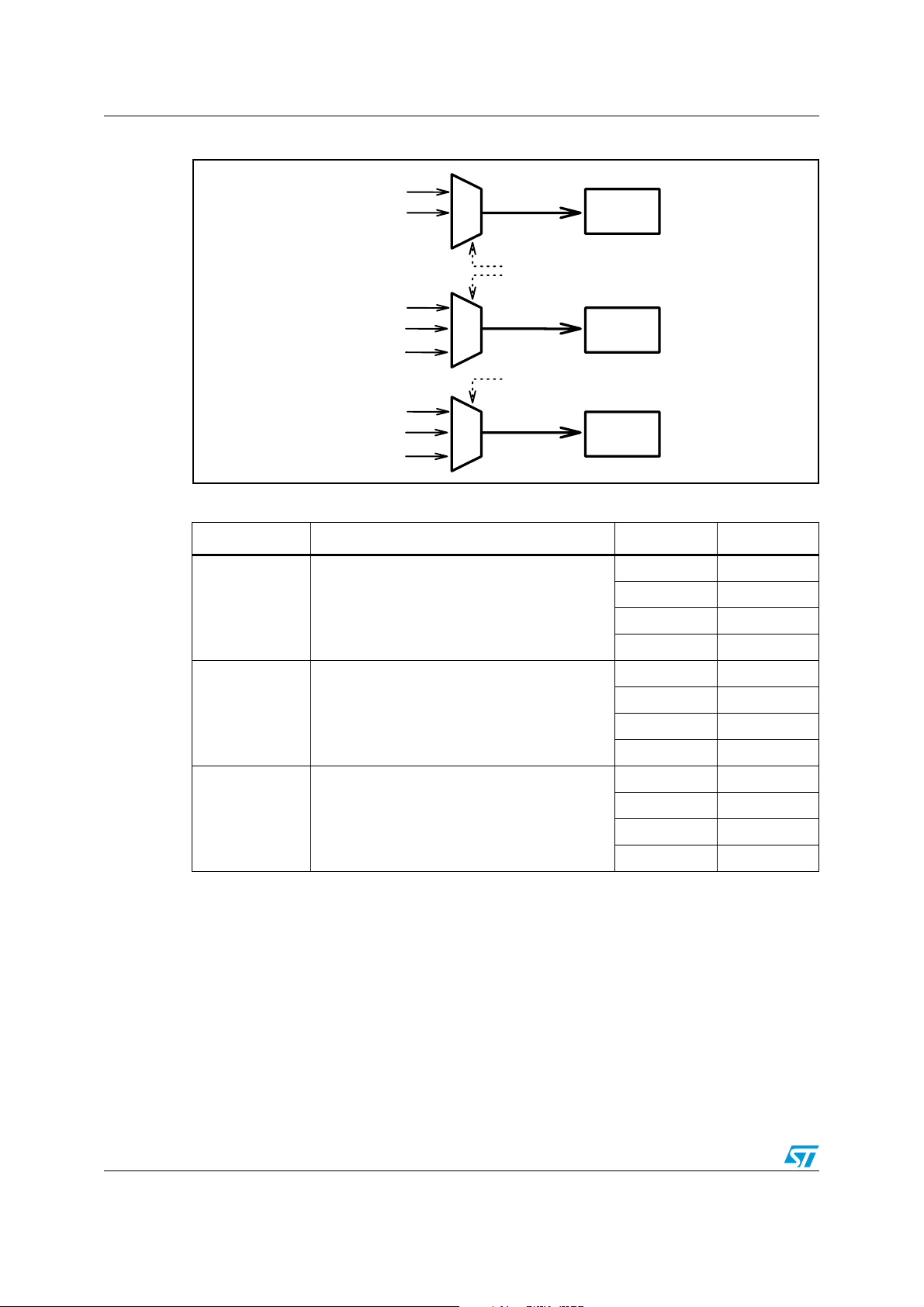

Left and right channels coming from the two serial audio interfaces and ADC (left and right

channels) are fed into the selection multiplexer (controlled by register SRCINSEL on

page 128), so that each channel can be connected to any desired processing chain. The

four channels are then sample rate converted to the fixed internal sampling rate. Pre mix,

EQ/tone processing, programmable delay, post mix, and volume/limiter make up the

STA321 signal processing chain.

Figure 14. Processing data multiplexer

SRCINSEL[7:6]

24

24

24

24

20

20

20

20

2-channel signal

1-channel signal

To SAI_ o u t

multiplexers

FFX

SAI_in1

ADC

SAI_in2

32

00

16

01

32

10

SRC1

24

ch0_in

ch1_in

PROC ch0

PROC ch1

PROC ch2

PROC ch3

Processing

SAI_in1

ADC

SAI_in2

32

00

16

01

32

10

SRC2

24

ch2_in

ch3_in

ch0_out

ch1_out

ch2_out

ch3_out

SRCINSEL[5:4]

34/157 Doc ID 15351 Rev 3

STA321 Digital processing stage

Figure 15. SAI_out data multiplexer

P2SDATA[5:3]

ADC (L/R)

SAI_in1 (L/R)

SAI_in2 (L/R)

SRC1 (L/R)

SRC2 (L/R)

PROC (ch0/ch1)

PROC (ch2/ch3)

ADC (L/R)

SAI_in1 (L/R)

SAI_in2 (L/R)

SRC1 (L/R)

SRC2 (L/R)

PROC (ch0/ch1)

PROC (ch2/ch3)

6.2 Sampling rate converter

The sample rate converter (SRC) re samples the input data source in order to send to the

processing block an audio stream always with a fixed frequency:

sampling frequency, f

In all the examples given here, f

S

= f

sys_clk

= 96 kHz.

S

16

000

32

001

32

010

24

011

24

100

24

101

24

else

16

000

32

001

32

010

24

011

24

100

24

101

24

else

P2SDATA[2:0]

/ 1024 where f

SAI_out1

2-channel signal

1-channel signal

SAI_out2

is the system clock frequency.

sys_clk

Figure 16. Sample rate converter block diagram

Data input

LRCK_IN

Interpolation

FIR x2

DRLL

Threshold

selector

Ratio

Interpolation

FIR x2

Precomp.

FIR

Sync 6

async.

Data output

The selection between x2 FIR interpolation and direct input data is made automatically by

the threshold selector block. If the input sampling frequency (measured by the DRLL) is

higher than the SRC threshold (that is, more than 81 kHz) the direct connection is selected

(first filter bypassed), otherwise the first x2 filter is added to the data path.

A 3-kHz hysteresis is fixed around the SRC threshold nominal value in order to prevent

unstable oscillations.

Doc ID 15351 Rev 3 35/157

Digital processing stage STA321

6.3 Pre-EQ mix 1 and post-EQ mix

The four-channel data, received from the sample rate converters, is sent to Mix1 block to

produce the four mixed-channel data for processing. All this data can be mapped to any

internal processing channel through the appropriate configuration of the RAM memory

locations.

Table 19. Channel mapping

Function Channel Memory location (RAM)

Ch0 from 0x00

Pre mixer

Post mixer

Ch1 from 0x04

Ch2 from 0x08

Ch3 from 0x0c

Ch0 from 0x118

Ch1 from 0x11c

Ch2 from 0x120

Ch3 from 0x124

The post-EQ mixer acts in a similar way for the output channels from the processing and

directed to the FFX. It is placed after the delay block which provides a full 4-channel input

mix on every channel.

Figure 17. Mixers block diagram

G2_0

pre: 0x08

pos: 0x120

ch0_in

pre: 0x00

pos: 0x118

G0_0

ch0_in

ch1_in

ch2_in

G0_1

G0_2

pre: 0x01

pos: 0x119

pre: 0x02

pos: 0x11A

ch0_out

++

ch1_in

ch2_in

G2_1

G2_2

pre: 0x09

pos: 0x121

pre: 0x0A

pos: 0x122

ch2_out

ch3_in

G0_3

pre: 0x03

pos: 0x11B

ch3_in

G2_3

pre: 0x0B

pos: 0x123

pre: 0x04

ch0_in

G1_0

pos: 0x11C

pre: 0x05

ch1_in

G1_1

pos: 0x11D

pre: 0x06

ch2_in

ch3_in

pos: 0x11E

G1_2

pos: 0x11Ff

G1_3

pre: 0x07

ch1_out

+

ch0_in

ch1_in

ch2_in

ch3_in

G3_0

G3_1

G3_2

G3_3

pre: 0x0C

pos: 0x124

pre: 0x0D

pos: 0x125

pre: 0x0E

pos: 0x126

pre: 0x0F

pos: 0x127

ch3_out

+

36/157 Doc ID 15351 Rev 3

STA321 Digital processing stage

6.3.1 Presets

By default, each mixer output is connected to its corresponding input without any attenuation

and without any mixing with the other channels:

ch0_out = ch0_in, ch1_out = ch1_in, ch2_out = ch2_in, ch3_out = ch3_in.

6.4 Pre scaler

The pre scale block, which precedes the first biquad, could be used to attenuate the input

signal when the filters of the processing chain have a gain that could reach the clamping

value.

Each channel has a dedicated 24-bit signed multiplier in the range -1 (0x800000) to almost

+1 (0x7FFFFF).

6.4.1 Presets

By default, all pre-scale factors are set to 0x7FFFFF

6.5 Equalization, tone control and effects

Figure 18. EQ/tone block diagram

From

prescaler

Biquad

00

Biquad

ReservedRAM

07

ReservedReserved

ReservedRAM

Biquad

08

RAM

To

delay stage

Biquad

09

effects_en[0]

High

pass

treb_sel bass_sel

effects_en[1]

RAM Deemph.

Treble

RAM

Biquad

12

Biquad

10

Reserved

RAM

Reserved

RAM Bass

Biquad

11

Four channels of input data are fed to the EQ processing block which provides 13

user-programmable biquad filters per channel as shown in Figure 18 above.

A description of the biquad programming is given in Section 6.14 on page 44.

Some filter coefficients are pre-programmed and stored in the non-volatile memory in order

to supply particular EQ effects (see Figure 19 and Table 20 on page 38).

The selection of RAM, ROM bass/treble or ROM effects is made using registers

EFFS_EN_CHn on page 109 for the effects and BASS_SELn_R on page 111 and

TREB_SELn_R on page 113 for the bass/treble. Each biquad can be configured

independently.

Doc ID 15351 Rev 3 37/157

Digital processing stage STA321

Figure 19. Biquad coefficient selection

RAM

ROM - Effects

RAM

ROM - Effects

ROM - Bass

RAM

ROM - Effects

ROM - Trebl.

Coefficients

ROMCHxx_

ROMCHxx & BASS_SELxx

Coefficients

ROMCHxx & TREB_SELxx

Coefficients

Biquads (00-10)

Biquads (11)

Biquads (12)

Table 20. EQ control signals

Signal name Description Channel Register addr

Ch0 0x71

Ch1 0x73

effects_en[1] 1: enable deemphasysa filter

Ch2 0x73

Ch3 0x77

Ch0 0x78

Ch1 0X79

bass_sel[5] 1: enable bass tone control

Ch2 0X7A

Ch3 0X7B

Ch0 0X7C

Ch1 0X7D

treb_sel[5] 1: enable treble tone control

Ch2 0X7E

Ch3 0X7F

38/157 Doc ID 15351 Rev 3

STA321 Digital processing stage

6.6 Biquads

The biquads are based on the following equation and is shown diagramatically in Figure 20.

Y[n] = b0 * X[n] + b1 * X[n-1] + b2 * X[n-2] - a1 * Y[n-1] - a2 * Y[n-2]

where Y[n] represents the output and X[n] represents the input. Fractional multipliers

are 24-bit signed with coefficient values in the range -1 (0xFFFFFF) to +1 (0x7FFFFF).

Figure 20. Biquad filter

-1

-1

6.6.1 Presets

By default all the biquads values in RAM are set to give a bypass function; in actual fact, the

signal passes through unchanged. The coefficients for this are:

a1 / 2 = 0, a2 / 2 = 0, b0 / 2 = 0.5 (0x400000), b1 / 2 = 0, b2 / 2 = 0.

6.7 High-pass filter

The standard high-pass filter is provided by the STA321

Figure 21. High-pass filter frequency response

b0/2

b1/2

b2 Z

2

2Z

+

+

+

2

-a1/2

-a2

-1

Z

-1

Z

High Pass Filter

0

−5

−10

−15

Gain [dB]

−20

−25

−30

0

10

1

10

10

2

Freq. [Hz]

3

10

4

10

5

10

Doc ID 15351 Rev 3 39/157

Digital processing stage STA321

6.8 Deemphasis filter

The standard deemphasis filter is provided by the STA321.

Figure 22. Deemphasis filter frequency response

40/157 Doc ID 15351 Rev 3

STA321 Digital processing stage

6.9 Bass and treble control

Preset values for the 11th and 12th biquads of every channel are stored in ROM in order to

achieve a bass and treble tone control.

They are channel independent and have 24 curves ranging from -12 to +12 dB gain with

1 dB steps. Their selection (and enable) is via registers BASS_SELx_R and TREB_SELx_R

where x is the number of the channel to be equalized.

The EQ curve and filter cut-off frequencies are shown in Figure 23 and Figure 24.

With a sampling frequency of 96 kHz (inside the processing block), the cut-off frequencies

are 3 kHz for treble curves and 150 Hz for bass curves.

Figure 23. Frequency responses of treble control at 1-dB gain steps

Figure 24. Frequency responses of bass control at 1-dB gain steps

Doc ID 15351 Rev 3 41/157

Digital processing stage STA321

6.9.1 Configuration example

This is an example of the tone control register setup. It is assumed that every peripheral is

already configured and working correctly.

Ta bl e 2 1 gives the register values to obtain +12 dB of bass on all channels and -10 dB of

treble on channels 0 and 1.

Table 21. Selecting EQ curves

Register - Address Programmed value Description

BASS_SEL0_R 0x38 CH0 +12 dB bass

BASS_SEL1_R 0x38 CH1 +12 dB bass

BASS_SEL2_R 0x38 CH2 +12 dB bass

BASS_SEL3_R 0x38 CH3 +12 dB bass

TREB_SEL0_R 0x22 CH0 -10 dB treble

TREB_SEL1_R 0xx22 CH1 - 10 dB treble

6.10 Programmable delay

Every channel, just after the biquads stage, is connected to a dedicated delay block.

The length of the delay is stored in RAM at location 0x128 and can vary from 0 to 35

samples. The corresponding time delay depends on the processing sampling frequency.

6.10.1 Presets

The delay of every channel is set to 0.

6.11 Volume and mute control

The STA321 provides a flexible volume and mute control stage. Using the registers VOLCH0

to VOLCH3 on page 122 it is possible to set the volume for each channel individually from

+36 dB to -105 dB with 0.5-dB steps.

There is a master volume control, register MVOL on page 120, as well. The master volume

adds an offset to all the individual volume settings.

The mute function offers the possibility to turn off the sound by reducing the volume setting

to -127.5 dB. It could be activated in two ways:

z register FFXCFG0 on page 82 provides a dedicated mute control for each channel.

z pin MUTE, driven by an external signal, puts all four channels into mute mode.

Register VOLCFG on page 120 provides some flexibility to set how the mute and volume

change procedures are applied. If bit SVOL_ONx is activated the volume of channel x is

changed gradually (soft volume or soft mute); using a ramp it starts from the current value