Infotainment application processor with embedded GPS

Features

■

High performance ARM926 MCU (up to 333 MHz)

■ MCU memory organization

– Cache: 16 KByte instruction, 16 KByte data

– 8 KByte instruction TCM (tightly coupled

memory)

– 8 KByte data TCM

– 32 KByte embedded ROM for boot

– Two banks of 64 KByte embedded SRAM

– 512 Byte embedded SRAM for back-up

– 4 GByte total linear address space

– Memory extension through:

Flexible static memory controller-FSMC

(NOR/NAND Flash, CF/CF+, ROM, SRAM

support)

Mobile DDR/SDRAM controller:

16 bit data @166 MHz, 2 Chip Select,

512 Kbit each

■ Interrupt

– 64-channel interrupt controller (VIC)

– 16-vectorized interrupts with 16

programmable priority Level

■ DMA

– Two 8-channel double port system DMA

controllers

– 32 DMA request for each controller

– Two external DMA requests are supported

■ 32 channel high performance GPS correlation

embedded subsystem

■ Eight 32-bit free running timers/counters

■ Four 16-bit extended function timer (EFT) with

input capture/output compare and PWM

■ Real time clock (RTC)

■ Pulse width light modulator (PWL)

■ 32-bit watchdog timer

■ Four autobaud UART with 64X8 transmit and

64x12 receive FIFO with DMA and hardware

flow control

■ One IrDA(SIR/MIR/FIR) interface

■ Three I

■ Two synchronous serial port (SSP) with 32x32

separate transmit and receive FIFO with

2

C multi-master/slave interfaces

STA2062

Cartesio™ family

Data Brief

LFBGA361 (16x16x1.4mm)

Motorola-SPI, National-MicroWire and TexasSSI support modes

■ Four multichannel serial ports (MSP) with 32x8

separate transmit and receive FIFO

■ Color LCD controller for STN,TFT or HR-TFT

panels

■ USB 2.0 OTG high speed dual role controller

(ULPI interface)

■ USB full speed dual role controller with

integrated 1.1 physical layer transceiver

■ Two secure-digital multimedia memory card

Interface (SD/SDIO/MMC) up to 8 bit data

■ SPDIF input interface

■ C3 hardware Reed-Solomon decoder

■ Hardware sample rate converter (SaRaC)

■ Four 32-bit GPIO ports

■ JTAG based in-circuit emulator (ICE) with

embedded medium trace module

■ Typical working condition: V

V

: 1.8 V

IO

■ Overdrive: V

: 1.4 V ±5 %, VIO: 1.8 V ±10 %,

dd

2.5 V ±10 %

■ Bus frequency: 166 MHz (overdrive)

■ Bus/DDR frequency: 166 MHz

■ HCMOS 0.90µm process

■ Package:

– LFBGA16x16x1.4 mm (19x19balls)

– 0.8 mm ball pitch, (0.4 mm ball)

– Full array

■ Ambient temperature range: -40 / +85 °C

Table 1. Device summary

Order code Package Packing

STA2062 LFBGA361 Tray

: 1.2 ±10% V,

dd

April 2008 Rev 3 1/5

For further information contact your local STMicroelectronics sales office.

www.st.com

5

Description STA2062

1 Description

The STA2062 is an highly integrated SOC application processor combining host capability

with embedded GPS.

STA2062 targets in vehicle and mobile navigation (PND), telematics, advance audio and

connectivity systems.

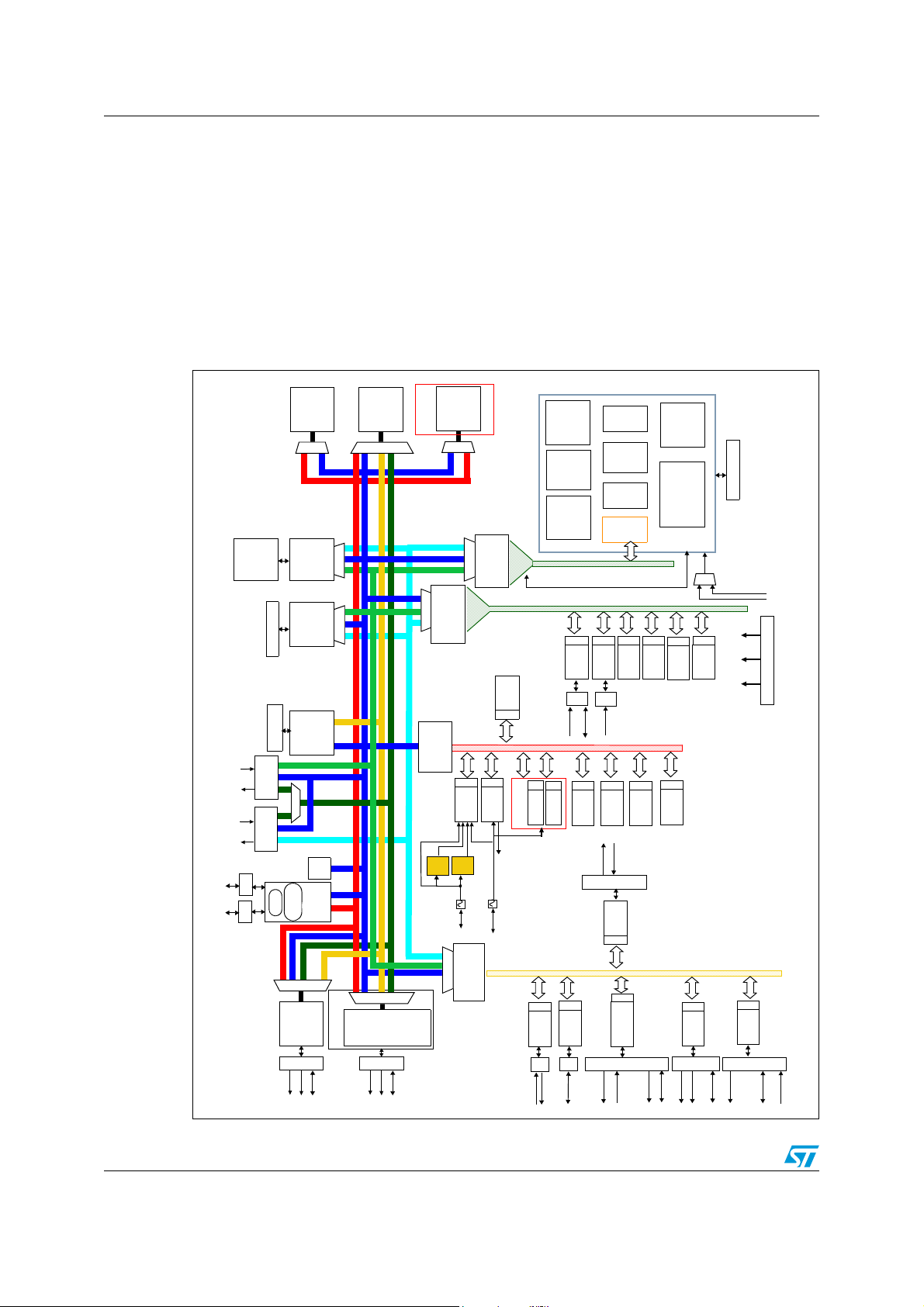

Figure 1: Block diagram gives an overview of the complete processor, showing how the

ARM926 microcontroller and its peripherals are interfaced.

Figure 1. Block diagram

DREQ1

DACK1

DREQ0

DACK0

eSRAM

eROM

(8K x 32)

S

S

USB PHY

USB FS

HS

S

USB OTG

ULPI Interface

(32K x 32)

S

LCD AHB

ARM AHB Instruction

ARM AHB Data

DMA 0/1 M1

DMA 0 M0

M

S

LCD CTRL

LCDC Interface

M0

S

DMA 0

M1

M1

S

DMA 1

M0

S

VIC

(JTAG)

TEST PORT

ETM

JTAG

IM DM

DCACHE

ARM926EJ

16 KB I / 16KB

8K ITCM / 8K DTCM

S

FSMC S

PORT FSMC

SDMC

PORT SDMC

RAM

(128 x 32)

BACKUP

S

,EFT

WDT

Memory

ARM HPGPS

ARM7TMIS

S

AHB / APB

GPS Bridge

S

Bridge

AHB / APB

Audio & Automotive

DMA1 M0

S

Bridge

AHB / APB

Core Peripheral

APB I/F

PLL1

MXTAL

GPIO(0,3)

APB I/F

APB I/F

SRC

PWL

BACKUP

PWLOUT

PLL2

SXTAL

S

DMA

Bridge

AHB / APB

APB I/F

APB I/F

APB I/F

EFT(0,3)

ECLK0-3

APB I/F

APB I/F

RTT

RTC

APB I/F

IrDA

I2C(0,1,2)

(FIR/MIR/SIR)

P RAM

(8K x 32)

EIC

DSP

Emerald

Memory

Acquisition

HPGPS Interface

Y RAM

(12K x 16)

(8K x 16)

X RAM

32-Channels

GPS Correlator

CLK16

CLK2

uC2 APB

CLK2

APB I/F

APB I/F

ICAPxA/ICAPxB

OCMPxA/OCMPxB

APB I/F

C3

SPDIF

SPDIFIN

CHITF

APB I/F

APB I/F

BD

SaRaC

GPSCLK

MXTAL

PLL

PLL

VDD

33

VDD

SUPPLY

12

CORE IOs

VDD

APB

URXD0

APB I/F

APB I/F

UUID

Support

MTU(0,1)

URI0n

UCTSxn

UDSR0n

UDCD0n

APB I/F

PMU

WDT

UTXDx

URTSxn

UDTR0n

UART(0, 3)

APB I/F

MCU APB

APB I/F

APB I/F

SD/SDIO/MMC(0,1)

APB I/F

SSP(0,1)

MSP(0,1,2,3)

ADDRESS

DATA

CTRL

ADDRESS

DATA

CTRL

2/5

FIRRXD

FIRTXD

I2CSDAx

MCFBCLK

MCDIR0

MCDIR31

MCDIR2

MCDIR74

SSPTXDx

SSPTXDx

SSPCLKx

MCCMDDIR

MCCMD

MCCLK

I2CSCLx

MCDAT[7:0]

SSPFRMx

MSPTXDx

MSPTCKx

MSPTFSx

MSPRCKx

MSPRFSx

MSPSCKx

MSPRXDx

STA2062 Package information

2 Package information

In order to meet environmental requirements, ST offers this device in ECOPACK® packages.

This package has a Lead-free second level interconnect. The category of second level

interconnect is marked on the package and on the inner box label, in compliance with

JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also

marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 2. LFBGA361 (16x16x1.4mm) mechanical data & package dimensions

DIM.

A 1.400 0.0551

A1 0.210 0.0082

A2 0.985 0.0387

A3 0.200 0.0079

A4 0.800 0.0315

b 0.350 0.400 0.450 0.0138 0.0157 0.0177

D 15.850 16.000 16.150 0.6240 0.6299 0.6358

D1 14.400 0.5669

E 15.850 16.000 16.150 0.6240 0.6299 0.6358

E1 14.400 0.5669

e 0.800 0.0315

F 0.800 0.0315

ddd 0.100 0.0039

eee 0.150 0.0059

fff 0.080 0.0031

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

OUTLINE AND

MECHANICAL DATA

Body: 16 x 16 x 1.4mm

LFBGA361

Low profile Fine Pitch Ball Grid Array

8033008 B

3/5

Revision history STA2062

3 Revision history

Table 2. Document revision history

Date Revision Changes

3-Oct-2007 1 Initial release.

12-Oct-2007 2 Minor changes.

11-Apr-2008 3 Typo and graphic errors correction.

4/5

STA2062

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

5/5

Loading...

Loading...