Features

■ 42 MHz: 84 Mbps (max) data rate at

V

= 1.8 V, VCC = 3.3 V

L

■ Bidirectional level translation without direction

control pin

■ Wide voltage range (V

–V

–V

■ Power down mode feature - when V

ranges from 1.65 to 3.6 V

L

ranges from 1.65 to 5.5 V

CC

CC

≥ VL):

supply

CC

is off, all I/Os are in high impedance

■ Totem-pole driving

■ 5.5 V tolerant enable pin

■ ESD performance on all pins : ±2 kv HBM

■ Small package and footprint:

QFN10 (1.8 x 1.4 mm)

Applications

■ Low voltage system level translation

■ Mobile phones and other mobile devices

ST2129

2-bit dual supply level translator

without direction control pin

QFN10

(1.8 x 1.4 mm)

Description

The ST2129 is a 2-bit dual supply level translator

which provides the level shifting capability to allow

data transfer in a multi-voltage system. Externally

applied voltages, V

on either side of the device. Its architecture allows

bidirectional level translation without a control pin.

The ST2129 accepts V

V

from 1.65 to 5.5 V, making it ideal for data

CC

transfer between low-voltage ASICs/PLD and

higher voltage systems. This device has a tri-state

output mode which can be used to disable all

I/Os.

and VL, set the logic levels

CC

from 1.65 to 3.6 V and

L

The ST2129 supports power-down mode when

V

is grounded/floating or when the device is

CC

disabled via the OE pin.

Table 1. Device summary

Order Code Package Packaging

ST2129QTR QFN10 (1.8 x 1.4 mm) Tape & reel (3000 parts per reel)

September 2009 Doc ID 15967 Rev 1 1/20

www.st.com

20

Pin settings ST2129

1 Pin settings

1.1 Pin connection

Figure 1. Pin connection (top through view)

V

I/O

VL1

V

10 9

1

CC

L

8

I/O

VCC1

I/O

VL2

OE

1.2 Pin description

Table 2. Pin description

Pin number Symbol Name and function

1I/O

2I/O

3 OE Output enable

4 NC No connection

5 NC No connection

6 GND Ground

7I/O

8I/O

9V

10 V

2

3

VL1

VL2

VCC2

VCC1

CC

L

4

5

NC NC

7

6

I/O

GND

Data input/output

Data input/output

Data input/output

Data input/output

Supply voltage

Supply voltage

VCC2

CS00011

2/20 Doc ID 15967 Rev 1

ST2129 Logic diagram

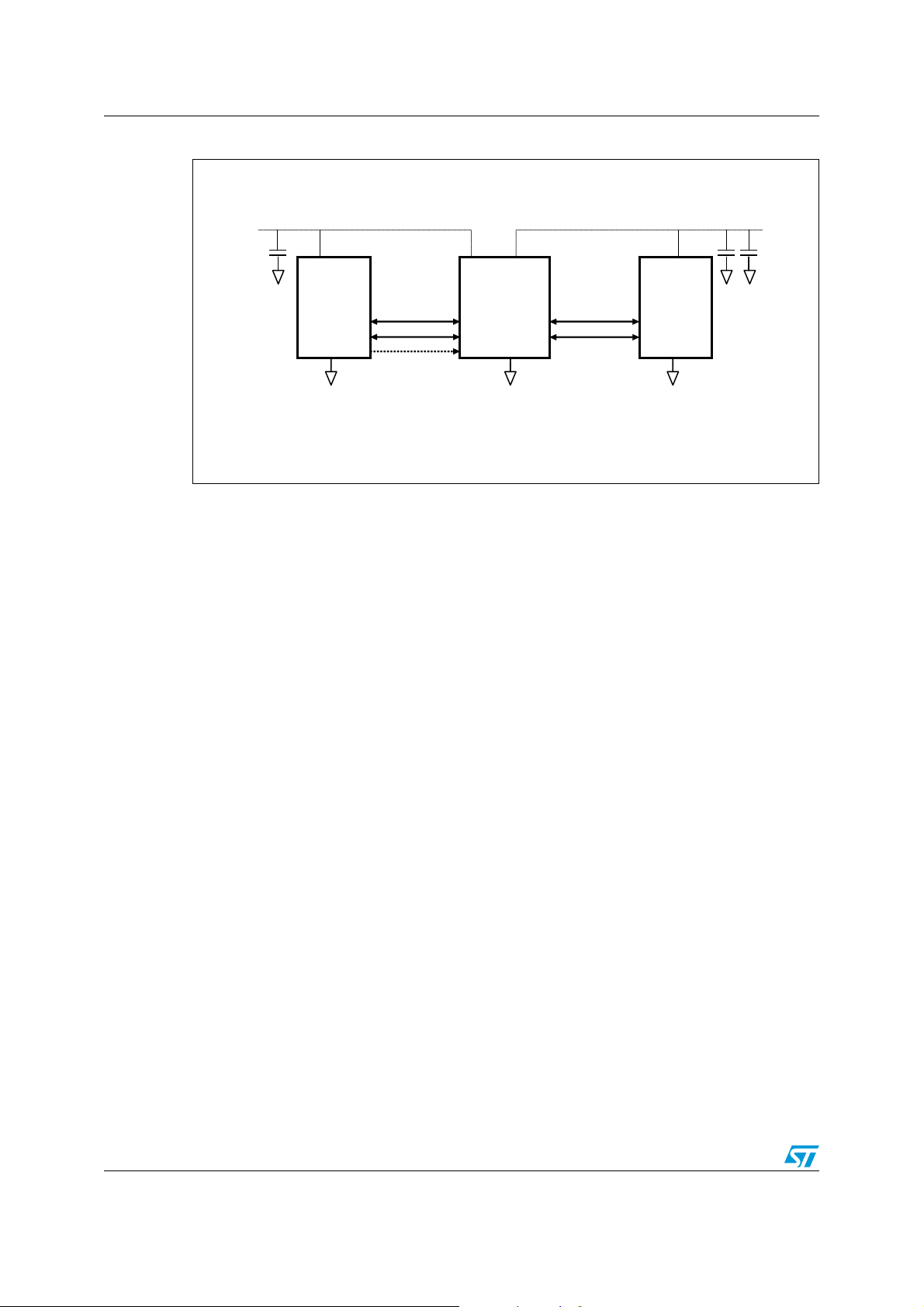

2 Logic diagram

Figure 2. Logic block diagram

2.1 Device block diagrams

Figure 3. ST2129 block diagram

Doc ID 15967 Rev 1 3/20

Logic diagram ST2129

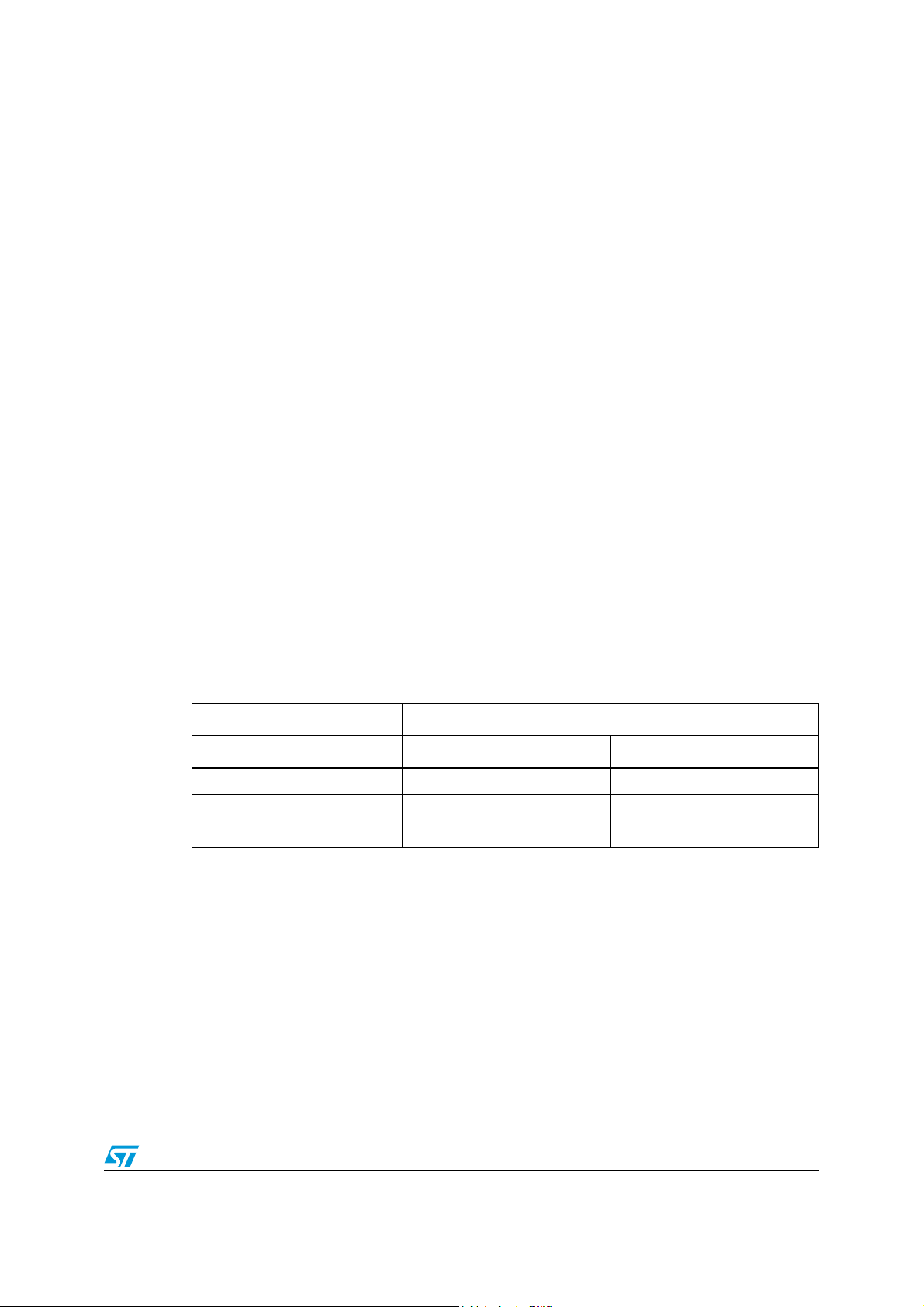

Figure 4. Application block diagram

V

V

L

0.1 μF

V

L

system

controller

VL

I/O

VL1

I/O

VL2

V

CC

V

CC

I/O

VCC1

I/O

VCC2

system

controller

F

0.1 μ

OE

1 μF

CC

AM00708V2

4/20 Doc ID 15967 Rev 1

ST2129 Supplementary notes

3 Supplementary notes

3.1 Driver requirement

For proper operation, the driver from each side of the device must have the capability to

source and sink a minimum of 1mA current. The device architecture requires the driver to

source/sink a maximum current of (V

3.2 Load driving capability

To support the architecture that allows level translation without direction pin, the one-shot

transistor is turned on only during state transition at the output side. After the one-shot

transistor is turned off, only the 4 kΩ resistor maintains the state. So, resistive load or pull-up

resistor less than 50 kΩ is not recommended for a proper operation.

3.3 Power off feature

In some applications, where it might be required to turn off one of the power supplies

powering up the level translator, the device is automatically disabled when V

turned off, even if the OE pin is set to HIGH (enabled). In this mode, all I/Os are in high

impedance state.

/4) mA to/from the weak 4 kΩ output buffer.

CC

supply is

CC

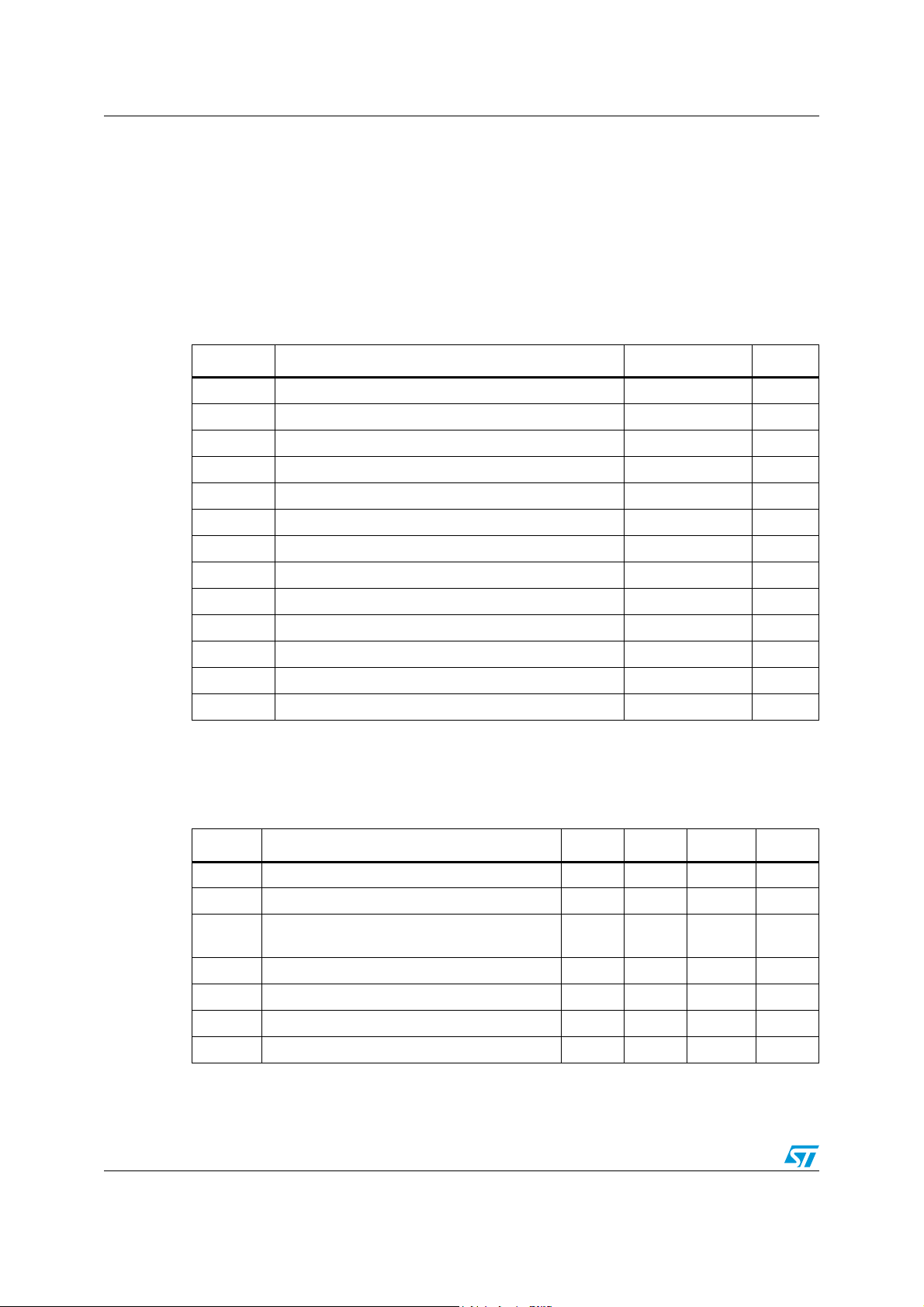

3.4 Truth table

Table 3. Truth table

Enable Bidirectional Input/Output

OE I/O

H

H

(1) High level VL power supply referred.

(2) High level V

(3) Z = High impedance.

CC

VCC

(1)

(1)

LZ

power supply referred.

(2)

H

LL

(3)

I/O

H

Z

VL

(1)

(3)

Doc ID 15967 Rev 1 5/20

Maximum ratings ST2129

4 Maximum ratings

Stressing the device above the rating listed in Tabl e 4 may cause permanent damage to the

device. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the operating sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

Table 4. Absolute maximum ratings

Symbol Parameter Value Unit

V

V

CC

V

OE

V

I/OVL

V

I/OVCC

I

IK

I

I/OVL

I

I/OVCC

I

SCTOUT

P

T

STG

T

Supply voltage -0.3 to 4.6 V

L

Supply voltage -0.3 to 6.5 V

DC control input voltage -0.3 to 6.5 V

DC I/OVL input voltage (OE = GND or VL) -0.3 to VL + 0.3 V

DC I/O

input voltage (OE = GND or VL) -0.3 to VCC + 0.3 V

VCC

DC input diode current -20 mA

DC output current ±25 mA

DC output current ±258 mA

Short circuit duration, continuous 40 mA

Power dissipation

D

(1)

Storage temperature -65 to 150

Lead temperature (10 seconds) 300

L

ESD Electrostatic discharge protection (HBM) ±2 kV

4.1 Recommended operating conditions

Table 5. Recommended operating conditions

500 mW

°

C

°

C

Symbol Parameter Min. Typ. Max. Unit

V

V

V

V

I/OVL

V

I/OVCC

T

Supply voltage 1.65 – 3.6 V

L

Supply voltage 1.65 – 5.5 V

CC

Input voltage (OE output enable pin, VL power

OE

supply referred)

I/OVL voltage 0 – V

I/O

voltage 0 – V

VCC

Operating temperature -40 – 85

OP

dt/dV Input rise and fall time 0 – 1 ns/V

6/20 Doc ID 15967 Rev 1

0–3.6V

L

CC

V

V

°

C

ST2129 Electrical characteristics

5 Electrical characteristics

Over recommended operating conditions unless otherwise noted. All typical values are at

T

= 25 °C.

A

Table 6. DC characteristics

Symbol Parameter V

Val ue

L

V

CC

Test

conditions

= 25 °C -40 to 85 °C

A

UnitT

Min Typ Max Min Max

1.65

1.16 – – 1.16 –

1.8 1.26 – – 1.26 –

V

High level input

IHL

voltage (I/OVL)

2.5 1.75 – – 1.75 –

1.65 to

5.5

V

3.0 2.10 – – 2.10 –

3.6 2.52 – – 2.52 –

1.65

– – 0.50 – 0.50

1.8 – – 0.54 – 0.54

V

Low level input

ILL

voltage (I/OVL)

2.5 – – 0.75 – 0.75

1.65 to

5.5

V

3.0 – – 0.90 – 0.90

3.6 – – 1.08 – 1.08

1.65 1.16 – – 1.16 –

1.8 1.26 – – 1.26 –

High level input

V

IHC

voltage

(I/O

VCC

)

1.65 to

3.6

2.5 1.75 – – 1.75 –

3.0 2.10 – – 2.10 –

3.6 2.52 – – 2.52 –

V

4.3 3.01 – – 3.01 –

5.5 3.85 – – 3.85 –

1.65 – – 0.50 – 0.50

1.8 – – 0.54 – 0.54

Low level input

ILC

voltage

(I/O

VCC

)

V

1.65 to

3.6

2.5 – – 0.75 – 0.75

3.0 – – 0.90 – 0.90

3.6 – – 1.08 – 1.08

V

4.3 – – 1.29 – 1.29

5.5 – – 1.65 – 1.65

Doc ID 15967 Rev 1 7/20

Electrical characteristics ST2129

Table 6. DC characteristics (continued)

Val ue

Symbol Parameter V

L

V

CC

Test

conditions

= 25 °C -40 to 85 °C

A

Min Typ Max Min Max

UnitT

V

V

V

V

V

V

IH-OE

IL-OE

OHL

OLL

OHC

OLC

High level input

voltage (OE)

Low level input

voltage (OE)

High level

output voltage

)

(I/O

VL

Low level

output voltage

)

(I/O

VL

High level

output voltage

)

(I/O

VCC

Low level

output voltage

)

(I/O

VCC

1.65

1.16 – – 1.16 –

1.8 1.26 – – 1.26 –

2.5 1.75 – – 1.75 –

1.65 to

5.5

3.0 2.10 – – 2.10 –

3.6 2.52 – – 2.52 –

1.65

– – 0.50 – 0.50

1.8 – – 0.54 – 0.54

2.5 – – 0.75 – 0.75

1.65 to

5.5

3.0 – – 0.90 – 0.90

3.6 – – 1.08 – 1.08

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

5.5

1.65 to

5.5

1.65 to

5.5

1.65 to

5.5

IO = -60µA V

- 0.4 – – VL - 0.4 – V

L

IO = +60µA – – 0.4 – 0.4 V

IO = -60µA

-

V

CC

0.4

––

VCC -

0.4

IO = +60µA – – 0.4 – 0.4

V

V

–V

V

8/20 Doc ID 15967 Rev 1

ST2129 Electrical characteristics

Table 7. DC characteristics

Val ue

Symbol Parameter V

L

V

CC

Tes t

conditions

= 25 °C -40 to 85 °C

A

Min Typ Max Min Max

UnitT

I

OE

I

IO_LKG

I

OFF

I

QVCC

I

QVL

I

Z-VCC

I

Z-VL

Control input

leakage

current (OE)

High

impedance

leakage

current (I/O

I/O

VCC

VL

)

Partial power

down current

Quiescent

supply current

V

CC

Quiescent

supply current

V

L

High

Impedance

quiescent

supply current

V

CC

High

impedance

quiescent

supply current

V

L

,

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

3.6

1.65 to

5.5

= GND or

V

I

V

L

––0.1– 1µA

OE = GND

= High

I/O

VL

= Low

I/O

1.65 to

5.5

VCC

OE = GND

I/O

= Low

VL

I/O

= High

VCC

L

or

OE = V

GND

= High

I/O

VL

= Low

I/O

0

VCC

OE = V

L

or

GND

= Low

I/O

VL

= High

I/O

VCC

1.65 to

5.5

OE = V

I/O = Hi-Z

L

1.65 to

5.5

1.65 to

5.5

OE = V

I/O = Hi-Z

0––0.1–1

OE = GND

I/O = Hi-Z

L

1.65 to

5.5

OE = GND

I/O = Hi-Z

0––0.1–1

––0.1– 1µA

––0.1– 1µA

––0.1– 1

µA

––0.1– 1

– – 3.5 – 4.5 µA

––0.1– 1

µA

––0.1– 1µA

––0.1– 1

µA

Doc ID 15967 Rev 1 9/20

AC characteristics ST2129

6 AC characteristics

Load CL = 15 pF; driver tr = t

Table 8. AC characteristics - test conditions: VL = 1.65 – 1.95 V

Symbol Parameter

≤ 2 ns over temperature range -40 °C to 85 °C.

f

VCC = 1.65 –

1.95 V

VCC = 2.3 –

2.7 V

V

CC

3.6 V

= 3.0 –

V

CC

5.5 V

= 4.5 –

Min Max Min Max Min Max Min Max

t

RVCC

t

FVCC

t

RVL

t

FVL

t

I/OVL-VCC

t

I/OVCC-VL

t

PZL tPZH

t

PLZ tPHZ

D

1. Data rate is guaranteed based on the condition that output I/O signal rise/fall time is less than 15% of period of input I/O

signal; input I/O signal is at 50% duty-cycle and output I/O signal duty-cycle deviation is less than 50% ± 10%.

Rise time I/O

Fall time I/O

Rise time I/O

Fall time I/O

Propagation delay time

I/O

VL-LH

I/O

VL-HL

Propagation delay time

I/O

VCC-LH

I/O

VCC-HL

VCC

VL

to I/O

to I/O

to I/O

to I/O

VCC

VL

VCC-LH

VCC-HL

VL-LH

VL-HL

t

PLH

t

PHL

t

PLH

t

PHL

Output enable time – 27 – 27 – 27 – 27

Output disable time – 145 – 145 – 145 – 145

R

Data rate

(1)

– 5.0 – 3.2 – 2.4 – 1.4 ns

– 1.5 – 1.4 – 1.3 – 1.2 ns

– 2.8 – 2.7 – 2.6 – 2.6 ns

– 1.5 – 1.4 – 1.4 – 1.3 ns

– 6.6 – 5.8 – 5.0 – 4.4 ns

– 4.1 – 3.8 – 3.6 – 3.4 ns

– 4.9 – 4.4 – 4.1 – 4.4 ns

– 4.6 – 4.2 – 4.0 – 3.6 ns

41 – 66 – 84 – 86 – Mbps

Unit

ns

10/20 Doc ID 15967 Rev 1

ST2129 AC characteristics

Table 9. AC characteristics - test conditions: VL = 2.3 – 2.7 V

V

Symbol Parameter

= 2.3 – 2.7 V V

CC

Min Max Min Max Min Max

= 3.0 – 3.6 V V

CC

= 4.5 – 5.5 V

CC

Unit

t

RVCC

t

FVCC

t

RVL

t

FVL

t

I/OVL-VCC

t

I/OVCC-VL

t

PZL tPZH

t

PLZ tPHZ

D

1. Data rate is guaranteed based on the condition that output I/O signal rise/fall time is less than 15% of period of input I/O

signal; input I/O signal is at 50% duty-cycle and output I/O signal duty-cycle deviation is less than 50% ± 10%.

Rise time I/O

Fall time I/O

Rise time I/O

Fall time I/O

Propagation delay

time

I/O

VL-LH

LH

I/O

VL-HL

HL

Propagation delay

time

I/O

VCC-LH

LH

I/O

VCC-HL

HL

VCC

VL

to I/O

to I/O

to I/O

to I/O

VCC

VL

VCC-

VCC-

VL-

VL-

t

PLH

t

PHL

t

PLH

t

PHL

Output enable time – 20 – 20 – 20

Output disable time – 130 – 130 – 130

R

Data rate

(1)

– 3.3 – 2.2 – 1.6 ns

– 1.7 – 1.6 – 1.4 ns

– 2.2 – 2.0 – 1.9 ns

– 1.3 – 1.2 – 1.2 ns

– 4.6 – 4.3 – 3.9 ns

– 3.6 – 3.3 – 2.9 ns

– 3.9 – 3.5 – 3.5 ns

– 3.6 – 3.0 – 2.5 ns

84 – 85 – 88 – Mbps

ns

Table 10. AC characteristics - test conditions: VL = 3.0 – 3.6 V

V

= 3.0 – 3.6 V V

Symbol Parameter

t

RVCC

t

FVCC

t

RVL

t

FVL

Rise time I/O

Fall time I/O

Rise time I/O

Fall time I/O

VCC

VCC

VL

VL

Propagation delay time

t

I/OVL-VCC

I/O

I/O

VL-LH

VL-HL

to I/O

to I/O

VCC-LH

VCC-HL

Propagation delay time

t

I/OVCC-VL

I/O

VCC-LH

I/O

VCC-HL

to I/O

to I/O

VL-LH

VL-HL

t

PLH

t

PHL

t

PLH

t

PHL

Doc ID 15967 Rev 1 11/20

CC

Min Max Min Max

–1.8– 1.7 ns

–1.3– 1.2 ns

–1.6– 1.5 ns

–1.1– 1.1 ns

–4.1– 4.1 ns

–2.6– 2.3 ns

–4.0– 4.0 ns

–2.6– 2.4 ns

= 4.5 – 5.5 V

CC

Unit

AC characteristics ST2129

Table 10. AC characteristics - test conditions: VL = 3.0 – 3.6 V (continued)

V

Symbol Parameter

= 3.0 – 3.6 V V

CC

Min Max Min Max

= 4.5 – 5.5 V

CC

Unit

t

PZL tPZH

t

PLZ tPHZ

D

1. Data rate is guaranteed based on the condition that output I/O signal rise/fall time is less than 15% of period of input I/O

signal; input I/O signal is at 50% duty-cycle and output I/O signal duty-cycle deviation is less than 50% ± 10%.

Output enable time – 15 – 15

Output disable time – 110 – 110

R

Data rate

(1)

86 – 89 – Mbps

ns

12/20 Doc ID 15967 Rev 1

ST2129 Test circuit

7 Test circuit

Figure 5. Test circuit

V

V

CC

L

V

L

V

CC

OPEN

GND

AM04077V1

Pulse

generator

D.U.T

R

1

C

L

Table 11. Test circuit switches

Tes t C

t

PLH, tPHL

t

r, tf

t

PZL, tPLZ

t

PZH, tPHZ

L

15 pF 20 kΩ Open

15 pF 20 kΩ Open

15 pF 20 kΩ VL or V

15 pF 20 kΩ GND

Table 12. Waveform symbol value

Driving I/O

Symbol

V

IH

V

IM

V

OM

V

X

V

Y

1.65V ≤ VL ≤ V

CC

≤ 2.5 V

V

L

50% V

L

50% V

CC

VOL + 0.15 V VOL + 0.3 V VOL + 0.15 V VOL + 0.3 V

VOH – 0.15 V VOH – 0.3 V VOH – 0.15 V VOH – 0.3 V

VL

3.3V ≤ V

5.5 V

50% V

50% V

≤ VCC ≤

L

V

L

L

CC

R

1

Driving I/O

1.65V ≤ VL ≤ VCC ≤

2.5V

V

CC

50% V

CC

50% V

L

Switch

CC

VCC

3.3V ≤ VL≤ VCC ≤

5.5V

V

CC

50% V

CC

50% V

L

Doc ID 15967 Rev 1 13/20

Test circuit ST2129

Figure 6. Waveform - propagation delay (f = 1 MHz, 50% duty cycle)

Figure 7. Waveform - output enable and disable time (f = 1 MHz, 50% duty cycle)

14/20 Doc ID 15967 Rev 1

ST2129 Package mechanical data

8 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

Figure 8. Package outline for QFN10 (1.8 x 1.4 x 0.5 mm) - 0.40 mm pitch

7936408 Rev.D

Doc ID 15967 Rev 1 15/20

Package mechanical data ST2129

Table 13. Mechanical data for QFN10 (1.8 x 1.4 x 0.5 mm) - 0.40 mm pitch

Millimeters

Symbol

Typ Min Max

A 0.50 0.45 0.55

A1 0.02 0 0.05

A3 0.127 – –

b 0.20 0.15 0.25

D 1.80 1.75 1.85

E 1.40 1.35 1.45

e 0.40 – –

L 0.40 0.35 0.45

Figure 9. Footprint recommendation for QFN10 (1.8 x 1.4 x 0.5 mm) - 0.40 mm

pitch

16/20 Doc ID 15967 Rev 1

ST2129 Package mechanical data

Figure 10. Carrier tape for QFN10 (1.8 x 1.4 x 0.5 mm) - 0.40 mm pitch

Figure 11. Reel information for QFN10 (1.8 x 1.4 x 0.5 mm) - 0.40 mm pitch

Back view

Doc ID 15967 Rev 1 17/20

Package mechanical data ST2129

Figure 12. Reel information for QFN10 (1.8 x 1.4 x 0.5 mm) - 0.40 mm pitch

18/20 Doc ID 15967 Rev 1

ST2129 Revision history

9 Revision history

Table 14. Document revision history

Date Revision Changes

07-Sep-2009 1 Initial release.

Doc ID 15967 Rev 1 19/20

ST2129

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

20/20 Doc ID 15967 Rev 1

Loading...

Loading...