ST SPEAr320S User Manual

for industrial and consumer applications

LFBGA289 (15 x 15 x 1.7 mm)

Features

■ ARM926EJ-S CPU core, up to 333 MHz

■ Multilayer bus matrix, up to 166 MHz

■ Internal memories: 32 KB ROM, 8 KB SRAM

■ Memory interfaces:

– DDR controller (DDR2-666, LPDDR-333),

8-/16-bit

– Serial NOR Flash controller

– Parallel NAND Flash controller, 8-/16-bit

data bus

– Parallel NOR Flash/FPGA interface,

8-/16-bit data bus

■ Connectivity:

– 2 x USB 2.0 Host ports (integrated PHY)

– 1 x USB 2.0 Device port (integrated PHY)

– 2 x Fast Ethernet ports (external MII/RMII

PHY)

– 1 x MMC-SD card/SDIO controller

– 2 x CAN 2.0 ports

–7 x UART ports

– 3 x I2C ports: master/slave

– 3 x synchronous serial ports,

SPI/Microwire/TI protocols, master/slave

– 1 x RS485 interface

– 1 x fast IrDA interface

– 1 x legacy parallel port (IEEE 1284), slave

mode

– 10-bit ADC, 8 channels, 1 Msps

– Up to 102 GPIOs with interrupt capability

■ HMI support:

– LCD display controller, up to XGA

(1024 x 768, 24 bpp)

– Resistive touchscreen interface

– JPEG codec accelerator

– 1 x I2S digital audio port

■ Security

– Cryptographic co-processor

SPEAr320S

Embedded MPU with ARM926 core

Datasheet − production data

■ Miscellaneous functions:

– System controller, vectored interrupt

controller, watchdog, real-time clock

– Dynamic power-saving features

– 8-channel DMA controller

– 6 x 16-bit general purpose timers with

prescaler and 4 capture inputs

– 4 x PWM generators

– Debug and trace interfaces: JTAG/ETM

Applications

The SPEAr320S embedded MPU is configurable

for a range of industrial and consumer

applications such as:

■ Human machine interface (HMI) terminals

■ Factory automation / PLCs

■ Medical equipment

■ Smart energy meters and gateways

■ VoIP phones

■ Small printers

The device is hardware-compliant to the support

of both real-time (RTOS) and high-level (HLOS)

operating systems, such as Linux and Windows

Embedded Compact 7.

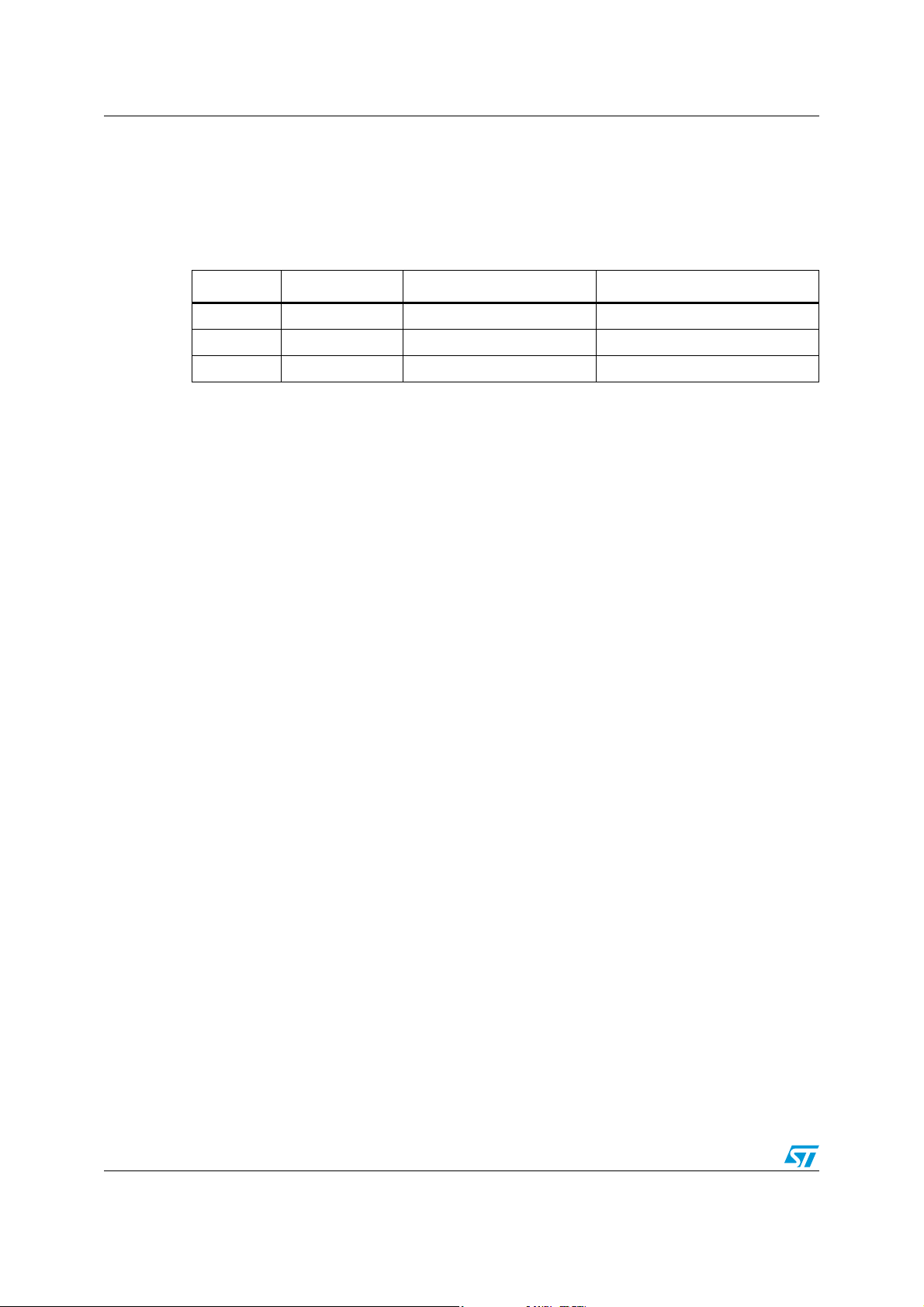

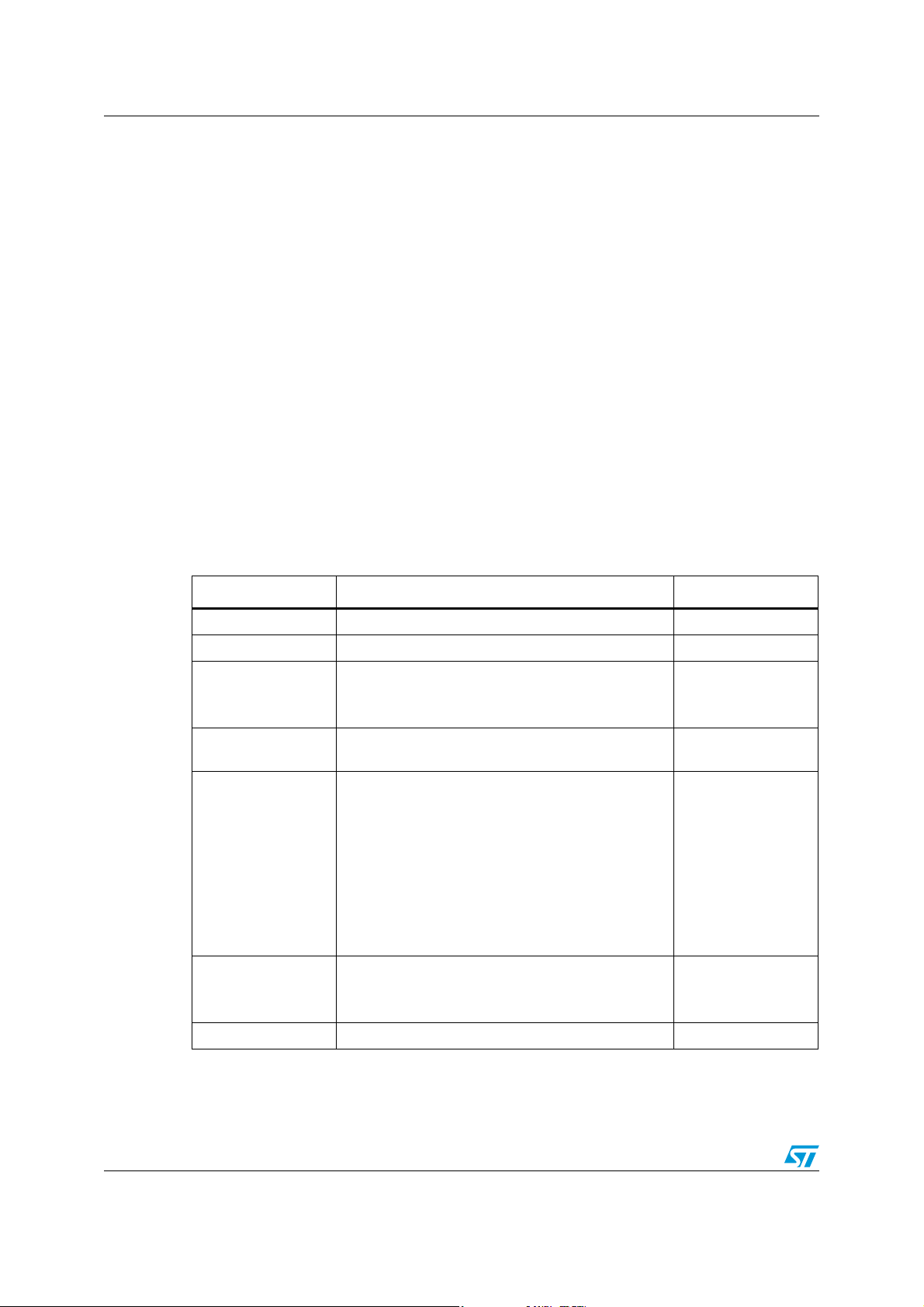

Table 1. Device summary

Order code

SPEAR320S-2 -40 to 85

Temp

range, ° C

Package Packing

LFBGA289

(15x15 mm,

pitch 0.8 mm)

Tr ay

April 2012 Doc ID 022508 Rev 1 1/97

This is information on a product in full production.

www.st.com

1

Contents SPEAr320S

Contents

1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2 Device functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 CPU subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Internal memories (BootROM/SRAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3 Multiport DDR controller (MPMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.4 Serial NOR Flash controller (SMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.5 Parallel NAND Flash controller (FSMC) . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.6 External memory interface (EMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.7 USB 2.0 Host ports (UHC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.8 USB 2.0 Device port (UDC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.9 Fast Ethernet ports (MII/RMII) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.9.1 MII0 Ethernet controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.9.2 RMII0 and MII1/RMII1 Ethernet controllers . . . . . . . . . . . . . . . . . . . . . . 16

2.10 MMC-SD card/SDIO controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.11 CAN 2.0 ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.12 Asynchronous serial ports (UART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.13 I2C bus ports (I2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.14 Synchronous serial ports (SSP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.15 RS485 port (RS485) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.16 Fast infrared port (IrDA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.17 Legacy IEEE 1284 parallel port (SPP) . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.18 A/D converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.19 General purpose I/Os (GPIO/XGPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.20 LCD display controller (CLCD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.21 Touchscreen interface (OUT_X) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.22 JPEG codec accelerator (JPGC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.23 Digital audio port (I2S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.24 Cryptographic co-processor (C3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.25 System controller (SYSCTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.25.1 Reset and clock generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2/97 Doc ID 022508 Rev 1

SPEAr320S Contents

2.26 Vectored interrupt controller (VIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.27 Watchdog timer (WDT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.28 Real-time clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.29 DMA controller (DMAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.30 General purpose timers (GPT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.31 Pulse width modulators (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.1 Pin/ball map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.2 Required external components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.3 Dedicated pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.3.1 Clock, reset and 3V3 comparator pins . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.3.2 Power supply pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.3.3 Debug pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.3.4 Non-multiplexed pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

3.4 Shared IO pins (PL_GPIOs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.4.1 PL_GPIO pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.4.2 Configuration modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.4.3 Alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.4.4 Boot pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4.5 GPIOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4.6 Multiplexing scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4.7 Multiplexed signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.5 PL_GPIO pin sharing for debug modes . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2 Maximum power consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.3 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4 Overshoot and undershoot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.5 3.3V I/O characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.6 Clocking parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.6.1 Master clock (MCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.6.2 Real-time clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.7 LPDDR and DDR2 pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Doc ID 022508 Rev 1 3/97

Contents SPEAr320S

4.8 ADC pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.9 Power-up sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.10 Power-down sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.11 Reset release . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5 Timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.1 External interrupt timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.2 Reset timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.3 CLCD timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.4 DDR2 timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.4.1 DDR2 read cycle timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.4.2 DDR2 write cycle timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.4.3 DDR2 command timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.5 EMI timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.6 Ethernet MII timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.6.1 MII transmit timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.6.2 MII receive timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.6.3 MDIO timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.7 Ethernet RMII timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.7.1 RMII transmit timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.7.2 RMII receive timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.8 FSMC timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.9 I

2

C timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.10 I2S timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.11 SD timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.12 SMI timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.13 SSP timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.13.1 SPI master mode timing characteristics (clock phase = 0) . . . . . . . . . . 88

5.13.2 SPI master mode timing characteristics (clock phase = 1) . . . . . . . . . . 89

5.14 UART timing characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

6 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Appendix A Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4/97 Doc ID 022508 Rev 1

SPEAr320S Contents

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Doc ID 022508 Rev 1 5/97

List of tables SPEAr320S

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. NAND Flash devices supported by the BootROM firmware . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 3. SPEAr320S UART capabilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 4. Pixel widths and formats available for different display types. . . . . . . . . . . . . . . . . . . . . . . 22

Table 5. Headers/abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 6. MCLK, RTC, Reset and 3.3 V comparator pins description . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 7. Power supply pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 8. Debug pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 9. SMI pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 10. USB pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 11. ADC pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 12. DDR pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 13. PL_GPIO pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 14. Boot pins description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 15. PL_GPIO multiplexing scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 16. Table shading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 17. FSMC signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 18. EMI signals description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 19. CLCD signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 20. Touchscreen signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 21. UART signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 22. CAN signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 23. MMC-SD/SDIO controller signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 24. PWM signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 25. GPT signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 26. IrDA signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 27. SSP signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 28. I2C signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 29. I2S signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 30. SPP signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 31. Ethernet signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 32. Ball sharing during debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 33. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 34. Maximum power consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 35. Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 36. Overshoot and undershoot specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 37. Low voltage TTL DC input specification (3 V< V

Table 38. Low voltage TTL DC output specification (3 V< V

Table 39. Pull-up and pull-down characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 40. DC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 41. Driver characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 42. On-die termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 43. Reference voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 44. ADC pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 45. PL_GPIO external interrupt input timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 46. Cold reset (at power-on) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 47. CLCD timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 48. DDR2 read cycle timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

<3.6 V) . . . . . . . . . . . . . . . . . . . . . . . . 66

DD

<3.6 V) . . . . . . . . . . . . . . . . . . . . . . . 66

DD

6/97 Doc ID 022508 Rev 1

SPEAr320S List of tables

Table 49. DDR2 write cycle timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 50. DDR2 command timing requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 51. EMI timing requirements for read cycle with acknowledgement on WAIT . . . . . . . . . . . . . 75

Table 52. EMI timing requirements for write cycle with acknowledgement on WAIT . . . . . . . . . . . . . 76

Table 53. EMI timing requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 54. MII TX timing requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 55. MII RX timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 56. MDC timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 57. RMII TX timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 58. RMII RX timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 59. FSMC timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 60. FSMC signals timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 61. I

Table 62. I

Table 63. I

2

C timing requirements in high-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

2

C timing requirements in fast-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

2

C timing requirements in standard-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 64. I2S timing requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 65. SD timing requirements (high-speed mode, 48 MHz). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 66. SD timing requirements (full-speed mode, 24 MHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 67. SMI timing requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 68. SSP timing requirements (all modes) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 69. SPI master mode timing requirements (clock phase = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 70. Switching characteristics over recommended operating conditions for

SPI master mode (clock phase =0 ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 71. SPI master mode timing requirements (clock phase = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 72. Switching characteristics over recommended operating conditions for

SPI master mode (clock phase = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 73. LFBGA289 (15 x 15 x 1.7 mm) mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 74. Thermal resistance characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 75. List of acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 76. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Doc ID 022508 Rev 1 7/97

List of figures SPEAr320S

List of figures

Figure 1. SPEAr320S architectural block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

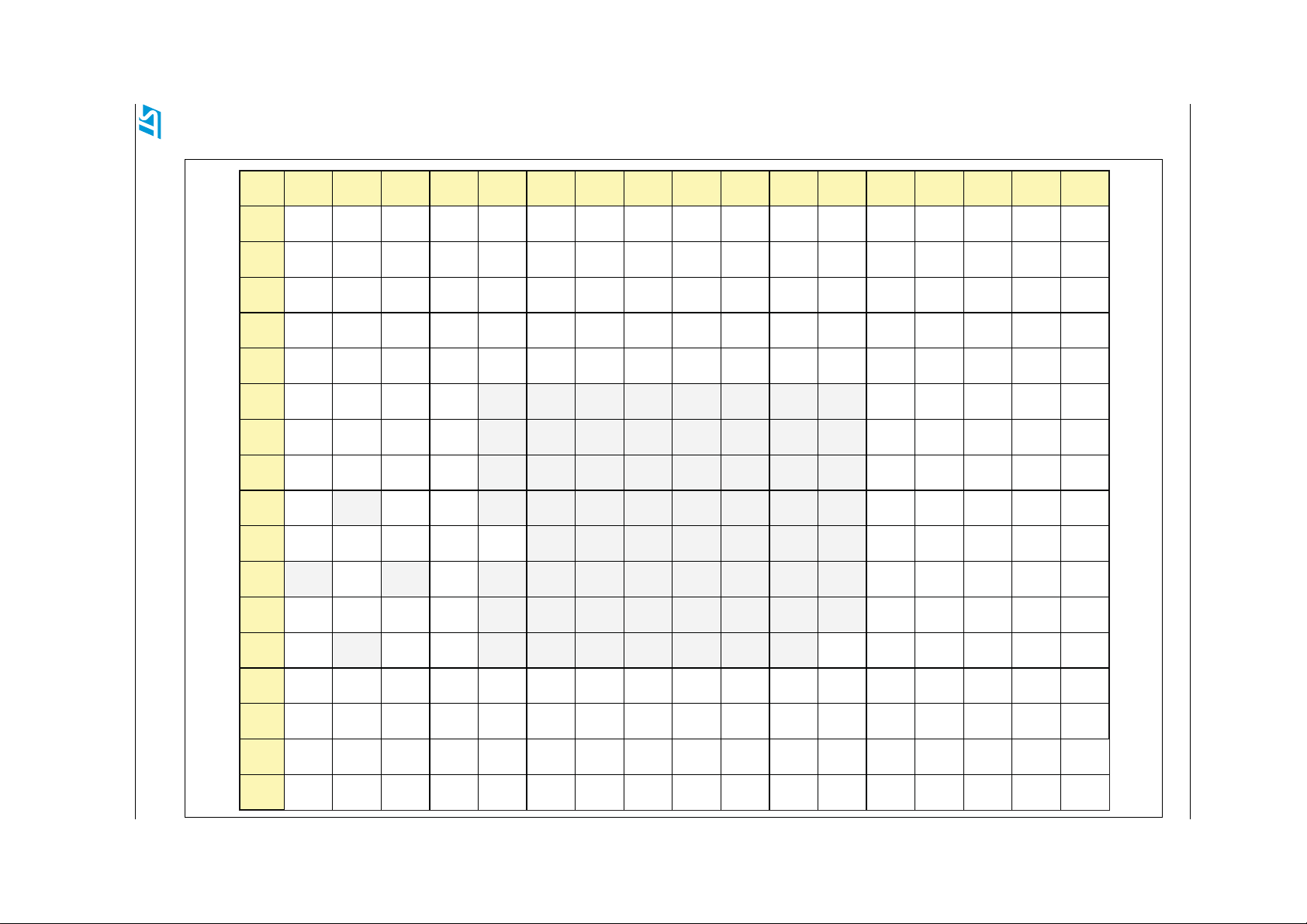

Figure 2. SPEAr320S pin/ball map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 3. Hierarchical multiplexing scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 4. MCLK crystal connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 5. RTC crystal connection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 6. Power-up sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 7. Reset release . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 8. CLCD waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 9. DDR2 read cycle waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 10. DDR2 write cycle waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 11. DDR2 command waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 12. EMI read cycle waveform with acknowledgement on EMI_WAIT. . . . . . . . . . . . . . . . . . . . 75

Figure 13. EMI write cycle waveform with acknowledgement on EMI_WAIT . . . . . . . . . . . . . . . . . . . 75

Figure 14. EMI read cycle waveform without acknowledgement on EMI_WAIT . . . . . . . . . . . . . . . . . 76

Figure 15. EMI write cycle waveform without acknowledgement on EMI_WAIT . . . . . . . . . . . . . . . . . 76

Figure 16. MII TX waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 17. MII RX waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 18. MDC waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 19. RMII TX waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 20. RMII RX waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 21. Output command signal waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 22. Output address signal waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 23. In/out data address signal waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 24. Output signal waveform for I

Figure 25. I2S waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 26. SD timing waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 27. SMI input/output waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 28. SSP_CLK waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 29. SPI master mode external timing waveform (clock phase = 0). . . . . . . . . . . . . . . . . . . . . . 88

Figure 30. SPI master mode external timing waveform (clock phase = 1). . . . . . . . . . . . . . . . . . . . . . 89

Figure 31. LFBGA289 package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

2

C signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

8/97 Doc ID 022508 Rev 1

SPEAr320S Description

1 Description

SPEAr320S is a member of the SPEAr family of embedded MPUs and is optimized for

industrial automation and consumer markets. The device is based on the ARM926EJ-S

processor (up to 333 MHz), widely used in applications where the processing performance

is required to be higher than the one achievable with microcontrollers.

SPEAr320S provides an integrated MMU (memory management unit) which enables to

support high-level operating systems (HLLs), such as Linux and Windows Embedded

Compact

HMI, cryptography) allows the device to be used in a wide range of embedded applications.

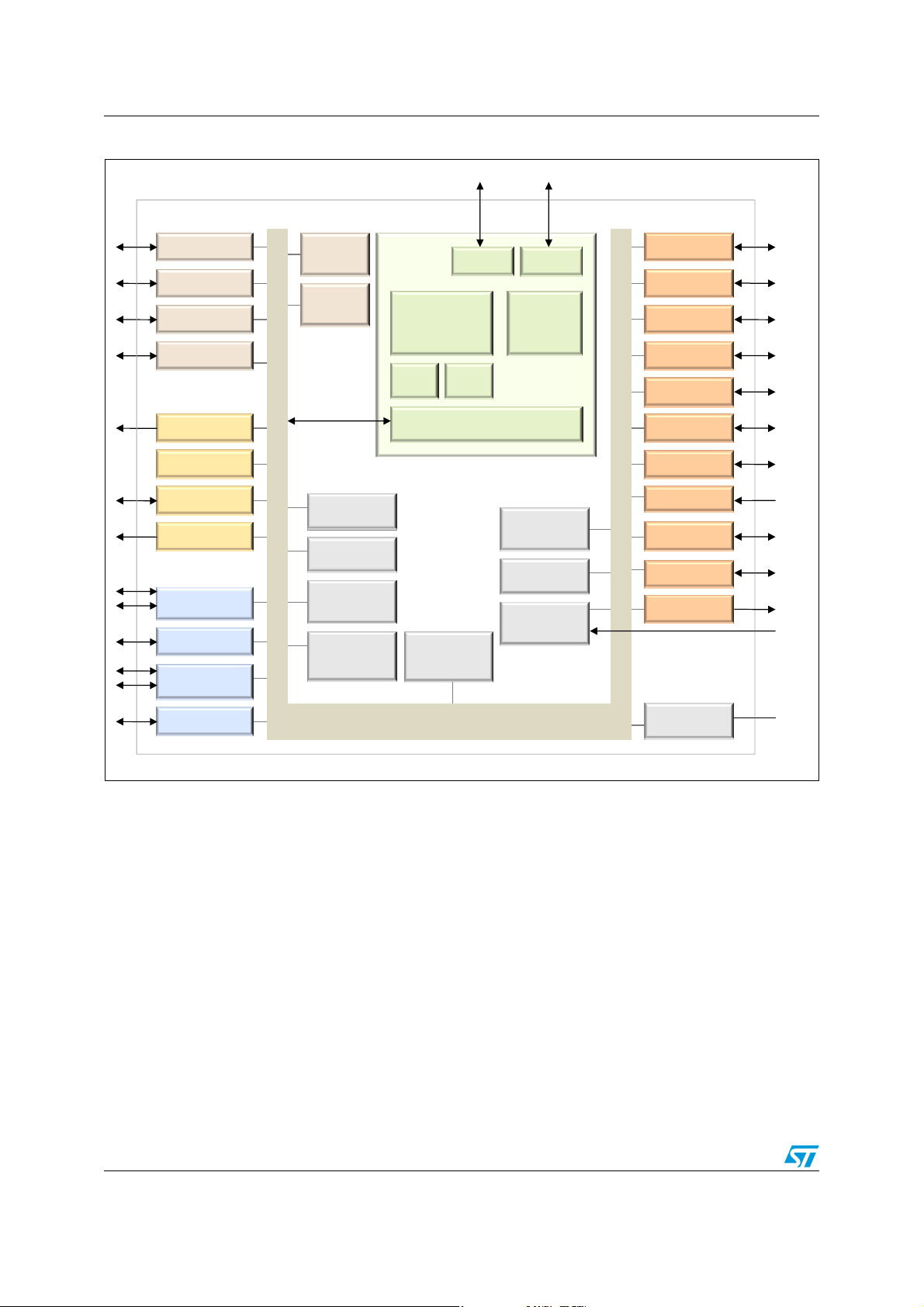

The SPEAr320S architecture is based on multiple functional blocks interacting through a

multilayer interconnection bus matrix. The switch matrix structure allows different subsystem

data flows to be executed in parallel improving the core platform efficiency. High

performance master agents are directly interconnected with the memory controller reducing

the memory access latency. The overall memory bandwidth assigned to each master port

can be programmed and optimized through an internal efficient weighted round-robin

arbitration mechanism.

The SPEAr320S device is fully backward-compatible with the previous SPEAr320 product at

both hardware and software programming levels. The extended functionality is achieved by

enhanced I/O multiplexing, preserving the same pinout and ball map, as well as by a new

software-definable configuration mode.

7. In addition, a rich set of integrated peripherals (memory interfaces, connectivity,

Doc ID 022508 Rev 1 9/97

Description SPEAr320S

MMU

ETMI/F

ARM9EJSCore

16KB

ICache

16KB

DCache

CPU

Subsystem

DisplayCtrl

JPEGCodec

I2SAudioI/F

USB2.0Host(2x)

USB2.0Device

HMIfeatures

Highspeedconnectivity

BUSMATRIXInterconnect

GPIO

XGPIO

SSP (3x)

FastIrDA

SPP

ADC

Lowspeedconnectivity

StaticMemoryCtrl

SerialFlashI/F

ExternalMemory

I/F

Memoryinterfaces

32KB

BootROM

DDR2/LPDDR

Ctrl

DMACtrl

Cryptographic

Coprocessor

Reset&clock

Generator

System

Controller

Config Regs

(MISC)

Timers(6x)

JTAG Trace

Opt.

Battery

CAN(2x)

PWM(4x)

RS485

FastEthernet

(2x)

I2C (3x)

UART (7x)

BusInterfaces

VectoredInterrupt

Controller

DebugI/F

4KB

StaticRAM

Watchdog

SDIO/MMC

Touchscreen I/F

RTC

Figure 1. SPEAr320S architectural block diagram

10/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2 Device functions

2.1 CPU subsystem

The core of the SPEAr320S is an ARM926EJ-S reduced instruction set computer (RISC)

processor.

Main features:

● Supports the 32-bit ARM and 16-bit Thumb instruction sets, enabling the user to trade

off between high performance and high code density. It also includes features for

efficient execution of Java byte codes.

● The ARM CPU can be clocked at a frequency up to 333 MHz and includes both an

instruction (16 KB) and a data cache (16 KB). In addition to the capability of running

any real-time operating system (RTOS) available for ARM9 processors, the

ARM926EJ-S subsystem also provides a memory management unit (MMU) that

enables to support high-level operating systems (HLLs) like Linux and Windows

Embedded Compact 7.

● Includes an embedded trace module (ETM Medium+) for real-time CPU activity tracing

and debugging. It supports 4-bit and 8-bit normal trace mode and 4-bit demultiplexed

trace mode, with normal or half-rate clock.

For detailed information, please refer to the following public documents available from the

ARM Ltd. website:

● CPU Core:

ARM9EJ-S, Technical Reference Manual, Revision: r1p2

http://infocenter.arm.com/help/topic/com.arm.doc.ddi0222b/DDI0222.pdf

● CPU Subsystem:

ARM926EJ-S, Technical Reference Manual, Revision: r0p5

http://infocenter.arm.com/help/topic/com.arm.doc.ddi0198e/DDI0198E_arm926ejs_r0p

5_trm.pdf

2.2 Internal memories (BootROM/SRAM)

SPEAr320S integrates two embedded memories:

● 32 KB ROM (BootROM), storing a factory-defined device bootstrap firmware.

● 8 KB Static RAM (SRAM), partly used by bootstrap firmware, but also available as

general-purpose memory after system startup.

The firmware in BootROM is automatically executed after SPEAr320S reset and supports

the following bootstrap modes:

● Boot from serial NOR Flash

● Boot from parallel NAND Flash

● Boot from parallel NOR Flash

● Boot from USB Device port

The BootROM firmware selects the boot mode from the boot pin settings (see Section 3.4.4:

Boot pins). A setting is also available to allow the BootROM execution to be bypassed.

Doc ID 022508 Rev 1 11/97

Device functions SPEAr320S

The first three modes support alternate ways of locating and starting the selected operating

system or target custom software. Such modes require a second-level boot firmware to be

stored in external Flash memory. A reference code for such boot loader (called “XLoader”) is

provided by STMicroelectronics in source and binary formats for the SPEAr320S evaluation

boards. Such code must be adapted according to the specific DDR memory components

found on target customer systems.

The fourth mode can be used for installing and updating the software on external Flash

memories through a PC-based software utility provided by STMicroelectronics exploiting a

USB link between a PC and a target SPEAr320S board.

2.3 Multiport DDR controller (MPMC)

SPEAr320S integrates a high-performance controller able to manage DDR2 (double data

rate) and LPDDR (low power DDR) external dynamic memory devices.

Main features:

● Support for DDR2 up to 333 MHz (666 MT/sec)

● Support for LPDDR up to 166 MHz (333 MT/sec)

● Support for 8-/16-bit external data bus

● Support for up to 1 GByte DDR2/LPDDR memory address space

● Full initialization of memories on controller reset

● 6 independent internal ports: five of them are used to access the external memory

while one is reserved for programming the controller configuration registers

● Programmable built-in port arbitration scheme to ensure high memory bandwidth

utilization

● Fully pipelined read and write commands

● Self-refresh mode for power saving

● Integrated physical layer (PHY) and delay locked loops (DLLs) for fine tuning of the

timing parameters, maximizing the data valid windows at different frequencies

2.4 Serial NOR Flash controller (SMI)

SPEAr320S integrates a Flash memory controller able to manage serial, SPI-compatible,

NOR Flash and EEPROM external memory devices.

Main features:

● Support for up to 32 MByte external serial memory storage capacity (2 x 16 MB

addressable banks by independent chip select signals)

● SMI clock up to 50 MHz (fast read mode) or 20 MHz (normal mode), with software

configurable 7-bit prescaler

The bootstrap requires that the external serial Flash is located at bank 0 (enabled after

power-on reset). During the boot phase, a sequence of instructions is automatically sent to

bank 0. Refer to SPEAr320S reference manuals for more details.

12/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

The BootROM firmware has been tested with the following external serial memory

components:

● Micron M25P and M45P families (SPI Flash)

● Micron M95 family (SPI EEPROM), except for M95040, M95020 and M95010

● ATMEL AT25F family (SPI Flash)

● YMC Y25F family (SPI Flash)

● Microchip/SST SST25LF family (SPI Flash)

2.5 Parallel NAND Flash controller (FSMC)

SPEAr320S integrates a flexible static memory controller able to manage external parallel

NAND Flash memories.

Main features:

● 8-/16-bit external data bus; 16-bit only supported when Mode 3 (expanded automation

mode) chip configuration is selected by software.

● Support for up to 4 memory banks

● Independent timing configuration and chip select signal for each memory bank

● Fully programmable timings:

– wait states (up to 31)

– bus turnaround cycles (up to 15)

– output enable and write enable delays (up to 15)

● External asynchronous wait control

● Internal AHB bus burst transfer support to reduce Flash memory access time

The BootROM firmware directly supports the external NAND Flash components shown in

Ta bl e 2.

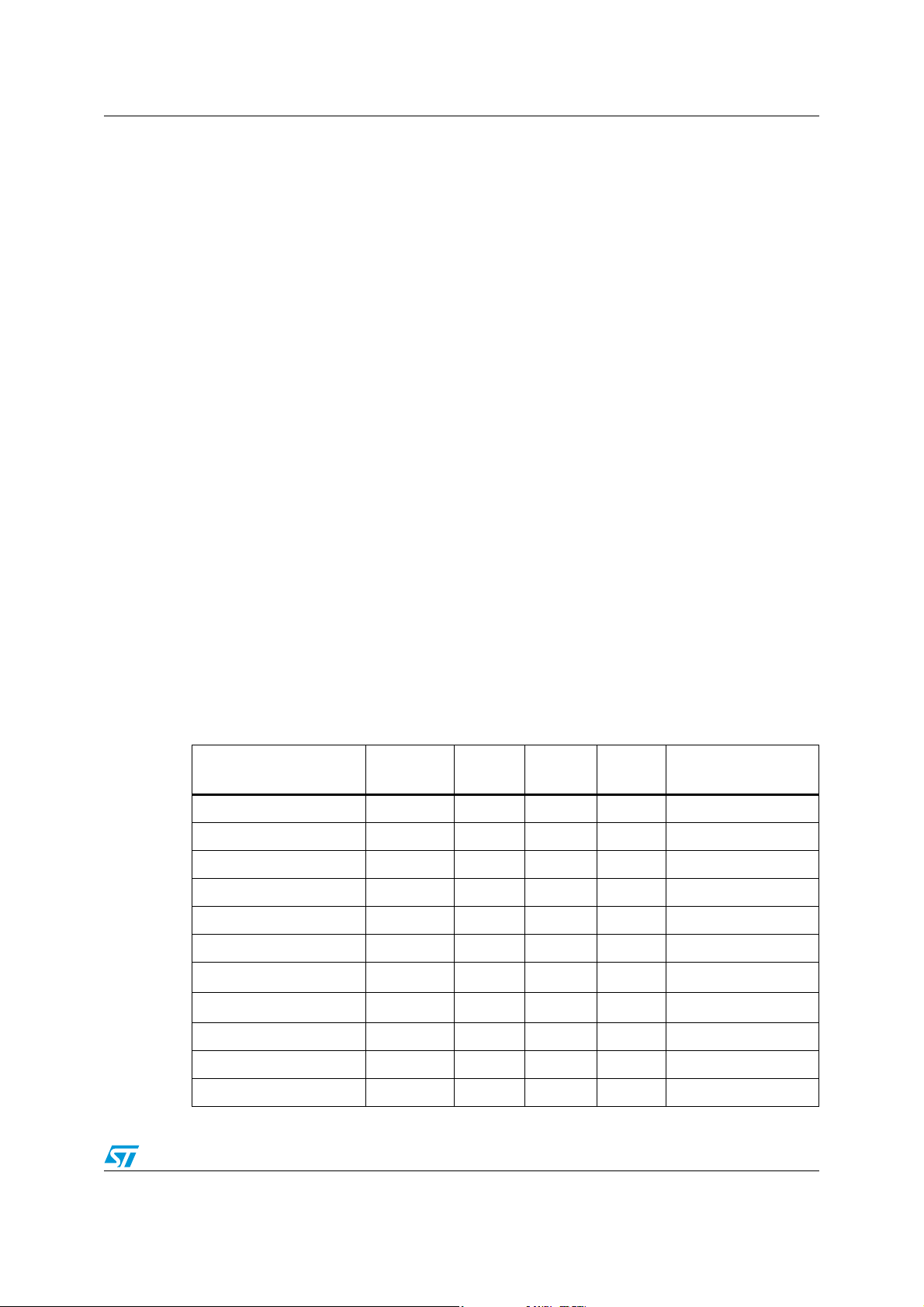

Table 2. NAND Flash devices supported by the BootROM firmware

Part number Vendor Density Capacity

K9F1208V0A Samsung 64 Mb 8 MB x8 512 + 16 bytes

NAND128W3A28N6 Micron 128 Mb 16 MB x8 512 + 16 bytes

NAND256W3A2BN6 Micron 256 Mb 32 MB x8 512 + 16 bytes

KM29U256 Samsung 256 Mb 32 MB x8 512 + 16 bytes

NAND512W3A2C2A6 Micron 512 Mb 64 MB x8 512 + 16 bytes

NAND01GW3B2BN6 Micron 1 Gb 128 MB x8 2048 + 64 bytes

NAND01GW4B2AN6 Micron 1 Gb 128 MB x16 1024 words + 32 bytes

K9F1G16U0M Samsung 1 Gb 128 MB x16 1024 words + 32 bytes

NAND01GR3B Micron 1 Gb 128 MB x8 2048 + 64 bytes

NAND02GW3B2CN6 Micron 2 Gb 256 MB x8 2048 + 64 bytes

NAND02GW3A Micron 2 Gb 256 MB x8 2048 + 64 bytes

Bus

width

Page size

Doc ID 022508 Rev 1 13/97

Device functions SPEAr320S

Table 2. NAND Flash devices supported by the BootROM firmware (continued)

Part number Vendor Density Capacity

K9F2G08V0A Samsung 2 Gb 256 MB x8 512 + 16 bytes

NAND04GW3B2BN6 Micron 4 Gb 512 MB x8 2048 + 64 bytes

K9F4G08V0A Samsung 4 Gb 512 MB x8 512 + 16 bytes

NAND08GW3B2CN6 Micron 8 Gb 1 GB x8 2048 + 64 bytes

K9K8G08V0A Samsung 8 Gb 1 GB x8 512 + 16 bytes

K9F8G08V0M Samsung 8 Gb 1 GB x8 512 + 16 bytes

2.6 External memory interface (EMI)

SPEAr320S integrates an additional external memory interface that can be used to manage

external parallel NOR Flash memories as well as FPGA devices. This interface is available

only when Mode 3 (expanded automation mode) chip configuration is selected by software.

Main features:

● 24-bit address bus

● 16-bit data bus

● 4 chip select signals

● Support for single asynchronous transfers

● Support for peripherals using Byte Lane procedure

Bus

width

Page size

The external Flash component must be in read mode at reset. Usually, this is true for most

parallel NOR devices.

2.7 USB 2.0 Host ports (UHC)

SPEAr320S provides two USB 2.0 Host ports with integrated PHYs.

Main features:

● Each port can be independently configured for high-speed mode (USB 2.0, up to

480 Mbps); in this case, the corresponding controller is programmed according to

standard EHCI specifications.

● Each port can be independently configured for full-speed mode (USB 1.1, up to

12 Mbps) or low-speed mode (USB 1.1, up to 1.5 Mbps); in this case, the

corresponding controller is programmed according to standard OHCI specifications.

● Internal 2 KB FIFO queues

● Internal DMA support

● Dedicated output control signals to manage external power switches

● Dedicated input signals to sense any over-current condition detected by external power

switches

14/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2.8 USB 2.0 Device port (UDC)

SPEAr320S provides a USB 2.0 Device port with integrated PHY.

Main features:

● Support for all standard modes:

– high-speed mode (USB 2.0, up to 480 Mbps)

– full-speed mode (USB 1.1, up to 12 Mbps)

– low-speed mode (USB 1.1, up to 1.5 Mbps)

● Up to 16 physical endpoints, configurable as different logical endpoints

● Internal 4 KB FIFO queue (shared among all the endpoints)

● DMA mode, with descriptor-based structures in application memory

● Slave-only mode

● Support for 8-, 16- and 32-bit wide data transactions on the internal bus

● Support for USB plug detection (UPD)

2.9 Fast Ethernet ports (MII/RMII)

SPEAr320S features three multiplexed Ethernet MACs, supporting up to two ports

concurrently.

The three controllers are named:

● MII0

● RMII0

● MII1/RMII1

2.9.1 MII0 Ethernet controller

Main features:

● Media independent interface (MII) to an external PHY as defined in the IEEE 802.3u

specification

● Support for 10 and 100 Mbps data transfer rates

● Support for both full-duplex and half-duplex (CSMA/CD protocol) operating modes

● Integrated FIFO queues (4 KB RX, 2 KB TX)

● Native DMA with single-channel transmit and receive engines, providing 32-/64-/128-bit

data transfers; DMA provides ring-buffer or linked-list descriptor options.

● Programmable Ethernet frame length to support both standard and jumbo frames (with

size up to 16 KB)

● Flexible address filtering modes

● Statistics counter registers for RMON/MIB

● Support for 802.1Q VLAN tagging

● Wake-on-LAN support

● Automatic padding and CRC generation on transmitted frames

Doc ID 022508 Rev 1 15/97

Device functions SPEAr320S

2.9.2 RMII0 and MII1/RMII1 Ethernet controllers

These functional blocks extend Ethernet capability by covering the Media independent

interface (MII) and Reduced media independent interface (RMII) standards.

They can be used in two ways:

● as a single additional MAC controller with Media independent interface (MII1)

● as two MAC controllers with Reduced media independent interface (RMII0, RMII1)

In RMII configuration, each controller has an independent set of data and control lines. The

reference clock (50

Main features:

● Compatible with IEEE Standard 802.3

● UNH tested

● 10 and 100 Mbit/s operation

● Full and half duplex operation

● Statistics counter registers for RMON/MIB

● Automatic pad and CRC generation on transmitted frames

● Automatic discard of frames received with errors

● Address checking logic supports up to four specific 48-bit addresses

● Supports promiscuous mode where all valid received frames are copied to memory

● Hash matching of unicast and multicast destination addresses

● External address matching of received frames

● Supports serial network interface operation

● Half-duplex flow control by forcing collisions on incoming frames

● Full-duplex flow control with recognition of incoming pause frames and hardware

generation of transmitted pause frames

● Support for 802.1Q VLAN tagging with recognition of incoming VLAN and priority

tagged frames

● Multiple buffers per receive and transmit frame

● Jumbo frames of up to 10240 bytes supported

MHz) is shared by the controllers.

2.10 MMC-SD card/SDIO controller

The MMC-SD card /SDIO controller conforms to the SD Host Controller Standard

Specification, version 2.0. It handles SD/SDIO protocol at transmission level by packing

data, adding cyclic redundancy check (CRC) and start/end bit as well as checking for

transaction format correctness.

The controller is designed to work with I/O cards, read-only cards and read/write cards, and

can operate either in SD mode (1-bit, 4-bit, 8-bit) or in SPI mode.

16/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

The interface is compliant to the following standards:

● SD Host Controller Standard Specification, version 2.0

● SDIO Card Specification, version 2.0

● SD Memory Card Specification Draft, version 2.0

● SD Memory Card Security Specification, version 1.01

● MMC Specification, version 3.31 and 4.2

Main features:

● Up to 100 Mbps data rate using 4 parallel data lines (SD4 bit mode)

● Up to 416 Mbps data rate using 8-bit parallel data lines (SD8 bit mode)

● DMA-based and non-DMA modes of operation

● Support for MMC Plus and MMC Mobile

● Card detection (insertion / removal)

● Card password protection

● Host clock rate variable between 0 and 48 MHz

● Multimedia card interrupt mode

● Cyclic redundancy check: CRC7 (command) and CRC16 (data integrity)

● Error correction code (ECC) support for MMC4.2 cards

● Supports for Read Wait Control and Suspend/Resume

● FIFO overrun and under-run handling by stopping SD clock

2.11 CAN 2.0 ports

SPEAr320S provides two independent CAN (controller area network) bus ports, typically

used in automotive, industrial and medical applications. For the connection to the physical

layer, an additional transceiver per port is required.

For communication on a CAN network, the controller enables to configure individual

message objects. The message objects and identifier masks for acceptance filtering of

received messages are stored in an integrated message RAM. All functions concerning the

handling of messages are implemented by a message handler. Those functions are the

acceptance filtering, the transfer of messages between the CAN core and the message

RAM, the handling of transmission requests as well as the generation of interrupts.

Main features:

● Support for CAN protocol, version 2.0 part A and B

● Transfer rate up to 1 Mbps

● Internal RAM storage for up to 16 message objects (16 x 136 bytes memory)

● Identifier mask per message object

● Maskable interrupts

● Programmable loop-back mode for self-test operation

● Disabled automatic retransmission mode for time triggered CAN applications

Doc ID 022508 Rev 1 17/97

Device functions SPEAr320S

2.12 Asynchronous serial ports (UART)

The SPEAr320S has 7 UART ports. The actual number of concurrently exploitable ports

depends on the selected chip operating mode. The different capabilities of each port are

summarized in

Table 3. SPEAr320S UART capabilities

Port Speed Hardware flow control Modem signals

UART0 Up to 3 Mbps Yes Yes (as alternate function)

UART1 Up to 7 Mbps Yes (except for Mode 1 and 2) Yes (except for Mode 1 and 2)

UART2 - 6 Up to 7 Mbps No No

Main features:

● Programmable baud rate generator

● Transmit FIFO queue (8-bit data, 16 entries) and receive FIFO queue (12-bit

data/status, 16 entries) with disabling option (1-byte buffer depth)

● Supports for DMA operation

● Hardware flow control (RTS,CTS) for some ports and configurations

● Modem control signals (DCD, DSR, DTS, RI) for some ports and configurations

● Fully programmable serial interface with following parameters:

– data bits: 5, 6, 7 or 8

– parity: even, odd, stick or none (generation and detection)

– stop bits: 1 or 2

– line break handling (generation and detection)

● Flexible interrupt handing and masking

Ta bl e 3 below.

18/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2.13 I2C bus ports (I2C)

The SPEAr320S provides three independent I2C bus ports. Each port can be configured as

I2C bus master or slave.

Main features:

● Compliant to the I2C bus specification (Philips)

● Support for the 3 standard speeds:

– Standard (100 Kbps)

– Fast (400 kbps)

– High-speed

● Support for direct memory access (DMA)

● Clock synchronization

● Multimaster mode (bus arbitration)

● 7-bit or 10-bit addressing

● 7-bit or 10-bit combined format transfers

● Slave bulk transfer mode

● Transmit and receive buffers

● Interrupt or polled-mode operation

● Handling of bit and byte waiting at all bus speeds

● Digital filter for the received SDA and SCL lines

● Filtering out of legacy CBUS addresses

2.14 Synchronous serial ports (SSP)

SPEAr320S provides three independent synchronous serial ports. Each port can be

configured as master or slave.

Main features:

● Support for the following protocols:

– SPI (Motorola)

– Microwire (National Semiconductor)

– SSI (Texas Instruments)

● Programmable parameters:

– Clock bit rate and prescale

– Data frame size (from 4 to 16 bits)

● Separate transmit and receive FIFO queues (8 x 16-bit entries)

● Independent masking of transmit FIFO, receive FIFO, and receive overrun interrupts

● Internal loopback test mode available

● DMA interface

Doc ID 022508 Rev 1 19/97

Device functions SPEAr320S

2.15 RS485 port (RS485)

SPEAr320S provides an additional UART port specialized for the RS485 standard.

Main features:

● Transmit FIFO queue (8-bit data, 16 entries) and receive FIFO queue (12-bit

data/status, 16 entries) with disabling option (1-byte buffer depth)

● Speed up to 7 Mbps

2.16 Fast infrared port (IrDA)

SPEAr320S provides an infrared interface compliant to the IrDA (Infrared Data Association)

standard specification. An external infrared transceiver is assumed. The Fast IrDa controller

performs the modulation and demodulation of the infrared signals as well as the wrapping of

IrDA link access protocol (IrLAP) frames.

Main features:

● Support for the following standards:

– IrDA serial infrared physical layer specification (IrPHY), version 1.3

– IrDA link access protocol (IrLAP), version 1.1

● Support for the following modes and baud rates:

– Serial infrared (SIR): 9.6 Kbps, 19.2 Kbps, 38.4 Kbps, 57.6 Kbps, 115.2 Kbps

– Medium infrared (MIR): 576 Kbps, 1152 Kbps

– Fast infrared (FIR): 4 Mbps

● Support for half-duplex infrared frame transmission and reception

● Interface compliant to all IrDA transceivers with configurable polarity of TX and RX

signals

● Integrated CRC algorithm: 16-bit (SIR, MIR), 32-bit (FIR)

● Automatic generation of preamble, start and stop flags

● RZI (return-to-zero inverted) modulation/demodulation scheme for SIR and MIR modes

● 4PPM (4-pulse position modulation) modulation/demodulation scheme for FIR mode

● Synchronization by DPLL in FIR mode

● Payload data transfer controllable by either CPU or DMA controller

● Two clock domains:

– Dedicated clock (IRDA_CLK signal) for accurate signal generation (48 MHz)

– Independent and variable clock for the bus interface (13 MHz)

2.17 Legacy IEEE 1284 parallel port (SPP)

SPEAr320S provides a parallel port (slave mode only) compliant to the legacy IEEE 1284

standard.

Main features:

● Unidirectional 8-bit data transfer from SPEAr320S slave to external host

● Additional 9th bit for parity/data/command

● Maskable interrupts for data, device reset, auto line feed

20/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2.18 A/D converter (ADC)

SPEAr320S provides an integrated analog-to-digital converter.

Main features:

● Successive approximation conversion method

● 8 x analog input channels, ranging from 0 to 2.5 V

● 10-bit resolution

● Sampling rate up to 1 Msamples/s

● Support for 13.5-bit resolution at 8 Ksamples/s by oversampling and accumulation

● INL ± 1 LSB, DNL ± 1 LSB

● Programmable conversion speed (minimum conversion time is 1 µs)

● Programmable averaging of multiple values from 1 (no averaging) up to 128

● Programmable auto scan for all the 8 channels

2.19 General purpose I/Os (GPIO/XGPIO)

Up to 102 GPIOs are available in SPEAr320S when some embedded IPs are not needed in

the customer application (see

Section 3.4: Shared IO pins (PL_GPIOs)).

SPEAr320S provides two mechanisms:

● a basic GPIO module (called “basGPIO”): this functional block provides 6 pins, each

one programmable by software with the following features:

– direction: input (default at reset) or output

– interrupt triggering mode

● the possibility to configure and use any PL_GPIO pin as alternative to the

corresponding predefined signal purpose (called extended GPIO or “XGPIO”). XGPIOs

have the same capability of basic GPIOs, while the register programming model is

different.

Doc ID 022508 Rev 1 21/97

Device functions SPEAr320S

2.20 LCD display controller (CLCD)

SPEAr320S has an integrated display controller able to directly interface a variety of color

and monochrome LCD panels.

Main features:

● Programmable resolution up to 1024 x 768 (XGA)

● Programmable timing parameters

● Support for TFT (thin film transistor) color displays

● Supports for STN (super twisted nematic) displays (single and dual panel) with 4- or 8-

bit interfaces

● AC bias signal for STN and data enable signal for TFT panels

● Gray scaling algorithm

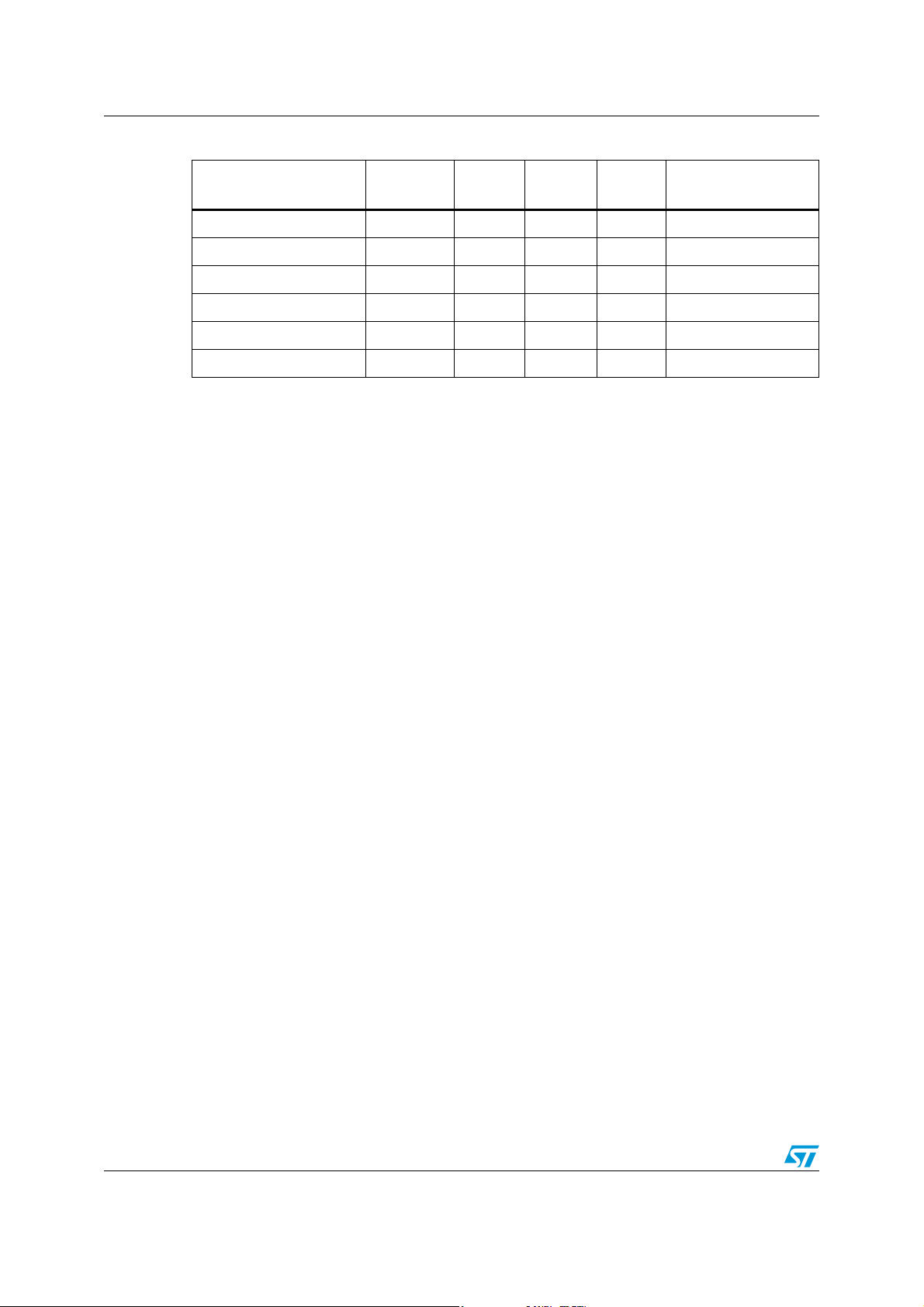

The set of supported pixel widths and formats for each display type is shown in Ta b le 4.

Table 4. Pixel widths and formats available for different display types

Display 1 bpp 2 bpp 4 bpp 8 bpp 16 bpp 24 bpp

Palette of 16

colors over

64K

Palette of 16

colors over

3375

Palette of 16

gray levels over

15

Color TFT

Color STN

Mono STN

Palette of 2

colors over 64K

Palette of 2

colors over 3375

Palette of 2 gray

levels over 15

Palette of 4

colors over 64K

Palette of 4

colors over 3375

Palette of 4 gray

levels over 15

2.21 Touchscreen interface (OUT_X)

SPEAr320S provides a toggling output signal (OUT_X) that can be connected to an external

touchscreen panel. This interface operates in combination with the A/D converter (ADC).

Two coordinates can be read by software from the ADC: one at the end of the high period

and one at the end of the low period of OUT_X signal.

Palette of

256 colors

over 64K

Palette of

256 colors

over 3375

Palette of

256 colors

over 3375

RGB 5:5:5 +

intensity

(64K colors)

RGB 4:4:4

(4096 colors)

--

RGB 8:8:8

(16M colors)

-

22/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2.22 JPEG codec accelerator (JPGC)

SPEAr320S provides an integrated hardware accelerator for decoding and encoding

standard JPEG images.

JPEG data streams to be decoded must be compliant with the interchange format syntax

specified in the ISO/IEC 10918-1. The JFIF image file format is also supported through

header processing.

The output format for decoding (and input format for encoding) is a MCU stream, not a

conventional bitmap format like RGB. Displaying a decoded JPEG still picture would require

further steps and algorithms like color space conversion and scaling.

Main features:

● Compliance with the baseline JPEG standard (ISO/IEC 10918-1)

● Single-clock per pixel encoding/decoding

● Support for up to four channels of component color

● 8-bit/channel pixel depths

● Programmable quantization tables (up to four)

● Programmable Huffman tables (two AC and two DC)

● Programmable minimum coded unit (MCU)

● Configurable JPEG header processing

● Support for restart marker insertion

● Use of two DMA channels and two 8 x 32-bit FIFOs (local to the JPEG) for efficient

transferring and buffering of encoded/decoded data from/to the Codec core.

2.23 Digital audio port (I2S)

The SPEAr320S integrates a digital audio port compliant to standard I2S (Philips)

specifications.

Main features:

● I2S master mode

● Stereo (2.0) playback and recording

● Support for standard sampling rates (8, 16, 32, 44.1, 48, 96, 192 kHz); the clock input is

24 MHz, so the rate precision depends on the chosen rate and divider.

● Support of a range of audio samples: 12 / 16 / 20 / 24/ 32 bits

● Programmable thresholds for internal FIFO queues

● Capability of using DMA transfer

2.24 Cryptographic co-processor (C3)

SPEAr320S provides an embedded cryptographic co-processor (C3). C3 is a high-

performance instruction-driven DMA-based engine that can be used to accelerate the

processing of security algorithms.

After its initial configuration by the main CPU, it runs in a completely autonomous way (DMA

data in, data processing, DMA data out), until the completion of all the requested operations.

C3 firmware is fetched from system memory.

Doc ID 022508 Rev 1 23/97

Device functions SPEAr320S

Main features:

● Supported cryptographic algorithms:

– Advanced encryption standard (AES) cipher in ECB, CBC, CTR modes

– Data encryption standard (DES) cipher in ECB and CBC modes

– SHA-1, HMAC-SHA-1, MD5, HMAC-MD5 digests

● Hardware chaining of cryptographic stages for optimized data flow when multiple

algorithms are required to process the same set of data (for example, encryption and

hashing on the fly)

2.25 System controller (SYSCTR)

The system controller provides an interface for controlling the operation of the overall

system.

Main features:

● Power saving system mode control

● Crystal oscillator and PLL control

● Configuration of system response to interrupts

● Reset status capture and soft reset generation

● Watchdog and timer module clock enable

Using three mode control bits, the system controller switches the SPEAr320S to any of the

four different modes: DOZE, SLEEP, SLOW and NORMAL.

● SLEEP mode: in this mode, the system clocks, HCLK and CLK, are disabled and the

system controller clock, SCLK, is driven by a low-speed oscillator (nominally

32768 Hz). When either a FIQ or an IRQ interrupt is generated (through the VIC), the

system enters DOZE mode. Additionally, the operating mode setting in the system

control register automatically changes from SLEEP to DOZE.

● DOZE mode: in this mode, the system clocks, HCLK and CLK, and the system

controller clock are driven by a low-speed oscillator. The system controller moves into

SLEEP mode from DOZE mode only when none of the mode control bits are set and

the processor is in wait-for-interrupt state. If SLOW mode or NORMAL mode is

required, the system moves into the XTAL control transition state to initialize the crystal

oscillator.

● SLOW mode: during this mode, both the system clocks and the system controller clock

are driven by the crystal oscillator. If NORMAL mode is selected, the system goes into

the “PLL control” transition state. If neither the SLOW nor the NORMAL mode control

bits are set, the system goes into the “Switch from XTAL” transition state.

● NORMAL mode: in NORMAL mode, both the system clocks and the system controller

clock are driven by the PLL output. If the NORMAL mode control bit is not set, then the

system goes into the “Switch from PLL” transition state.

24/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2.25.1 Reset and clock generator

The reset and clock generator is a fully programmable block that generates all the clocks

necessary to the chip.

The default operating clock frequencies are:

● Clock @ 333 MHz for the CPU.

● Clock @ 166 MHz for AHB bus and AHB peripherals.

● Clock @ 83 MHz for, APB bus and APB peripherals.

● Clock @ 333 MHz for DDR memory interface.

The default values give the maximum allowed clock frequencies. The clock frequencies are

fully programmable through dedicated registers.

The reset and clock generator consists of 2 main parts:

● a multiclock generator block

● two internal PLLs

The multiclock generator block receives a reference signal (which is usually delivered by the

PLL) and generates all clocks for SPEAr320S IPs according to dedicated programmable

registers.

Each PLL uses an oscillator input of 24 MHz to generate a clock signal at a frequency

corresponding at the highest of the group. This is the reference signal used by the multiclock

generator block to obtain all the other requested clocks for the group. Its main feature is the

electromagnetic interference reduction capability.

You can set up the PLL in order to modulate the VCO with a triangular wave. The resulting

signal has a spectrum (and power) spread over a small programmable range of frequencies

centered on F0 (the VCO frequency), obtaining minimum electromagnetic emissions. This

method replaces all the other traditional methods of EMI reduction, such as filtering, ferrite

beads, chokes, adding power layers and ground planes to PCBs, metal shielding and so on.

This offers important cost savings.

In sleep mode, SPEAr320S runs with the PLL disabled, so the available frequency is

24

MHz or a sub-multiple (/2, /4, /8).

2.26 Vectored interrupt controller (VIC)

SPEAr320S integrates a vectored interrupt controller which provides a software interface to

the interrupt system. In any system with an interrupt controller, the software has to

determine the source that requests service and where its service routine is loaded. The VIC

inside SPEAr320S does both of these in hardware. It supplies the starting address, or vector

address, of the service routine corresponding to the highest priority requesting interrupt

source.

As in any ARM9-based system, two levels of interrupts are available:

● fast interrupt requests (FIQ), for fast, low latency interrupt handling

● normal interrupt requests (IRQ), for more general interrupts

The interrupt inputs must be level sensitive, active HIGH, and held asserted until the

interrupt service routine clears the interrupt. Edge-triggered interrupts are not compatible.

The interrupt inputs do not have to be synchronous to HCLK. The VIC does not handle

interrupt sources with transient behavior. For example, an interrupt is asserted and then de-

Doc ID 022508 Rev 1 25/97

Device functions SPEAr320S

asserted before software can clear the interrupt source. In this case, the CPU acknowledges

the interrupt and obtains the vectored address for the interrupt from the VIC, assuming that

no other interrupt has occurred to overwrite the vectored address. However, when a

transient interrupt occurs, the priority logic of the VIC is not set, and lower priority interrupts

can interrupt the transient interrupt service routine, assuming interrupt nesting is permitted.

There are 32 interrupt lines. The VIC uses a bit position for each different interrupt source.

The software can control each request line to generate software interrupts. There are 16

vectored interrupts. These interrupts can only generate an IRQ interrupt. The vectored and

non-vectored IRQ interrupts provide an address for an interrupt service routine (ISR). The

FIQ interrupt has the highest priority, followed by interrupt vector 0 to interrupt vector 15.

Non-vectored IRQ interrupts have the lowest priority.

The specific interrupt map for the SPEAr320S device is documented in the companion

reference manuals.

2.27 Watchdog timer (WDT)

The ARM watchdog module consists of a 32-bit down counter with a programmable time-out

interval that has the capability to generate an interrupt and a reset signal on timing out. The

watchdog module is intended to be used to apply a reset to a system in the event of a

software failure.

2.28 Real-time clock (RTC)

The real-time clock provides an 1-second resolution clock. This keeps time when the system

is inactive and can be used to wake the system up when a programmed alarm time is

reached. RTC has a clock trimming feature to compensate for the accuracy of the 32.768

kHz crystal and a secured time update.

Main features:

● Time-of-day clock in 24 hour mode

● Calendar

● Alarm capability

● Isolation mode, allowing RTC to work even if power is not supplied to the rest of the

device.

2.29 DMA controller (DMAC)

SPEAr320S provides one DMA controller.

Main features:

● Able to service up to 8 independent DMA channels for serial data transfers between

single source and destination (for instance, memory-to-memory, memory-to-peripheral,

peripheral to- memory, and peripheral-to-peripheral).

● Each DMA channel can support a unidirectional transfer, with internal four-word FIFO

per channel.

26/97 Doc ID 022508 Rev 1

SPEAr320S Device functions

2.30 General purpose timers (GPT)

SPEAr320S provides 6 general purpose timers.

Main features:

● Each timer provides a programmable 16-bit counter and a dedicated 4-bit prescaler

able to perform a clock division by 1 up to 256 (different input frequencies can be

chosen through configuration registers, in the range from 3.96 Hz to 48 MHz)

● Operating modes:

– Auto-reload mode: when a software-defined value is reached, an interrupt is

triggered and the counter automatically restarts from zero

– Single-shot mode: when a software-defined value is reached, an interrupt is

triggered, the counter is stopped and the timer is disabled

● Capture capability (only for 4 timers)

2.31 Pulse width modulators (PWM)

SPEAr320S integrates 4 PWM (pulse width modulation) signal generators.

Main features:

● Prescaler to define the input clock frequency to each timer

● Programmable duty cycle from 0% to 100%

● Programmable pulse length

Doc ID 022508 Rev 1 27/97

Pin description SPEAr320S

3 Pin description

This chapter provides a full description of the ball characteristics and the signal multiplexing

of SPEAr320S device.

Section 3.1 shows the pin/ball map of SPEAr320S.

Section 3.2 lists the required external components to connect.

Section 3.3 describes some dedicated pins, such as:

● Clock, reset and 3V3 comparator pins

● Power supply pins

● Debug pins

● Non-multiplexed pins

Section 3.4 provides a complete description of the shared IO pins (PL_GPIOs) and their

configuration modes, as well as detailed information on all multiplexed signals, grouped by

IP.

Section 3.5 explains the available debug modes.

The following table defines the table headers and abbreviations used in this chapter.

Table 5. Headers/abbreviations

Header Description Abbreviations

Group Grouping of signals of the same type/functional block. –

Signal name Name of signal multiplexed on each ball. –

I= Input

Direction (Dir.) Indicates the direction of the signal.

PL_GPIO_# /Ball

Configuration mode

Pin type Pad type information

Val ue Indicates the electrical value on the ball. –

PL_GPIO and ball number associated with each

signal on the package.

Indicates the available configuration mode among the

following ones:

– Mode 1

– Mode 2

– Mode 3

– Mode 4

– Alternate function

– Extended mode

See Section 3.4.2 for the description of each mode.

O= Output

IO= Input/output

–

–

PU= Pull Up

PD= Pull Down

GND= Ground

28/97 Doc ID 022508 Rev 1

3.1 Pin/ball map

_

_

_

DIGITAL_

REXT

digital_vdde

3v3

gnd gnd gnd gnd gnd gnd vdd PL_GPIO _87 PL_GPIO_90 PL_GPIO_91 PL_GPIO _92 PL_GPIO_93

H

vdd gnd gnd gnd gnd gnd gnd v dd PL_G PIO_94PL_GPIO_95PL_GPIO_96PL_GPIO_97PL_CLK4

J

gnd

vdd gnd gnd gnd gnd gnd gnd digital_vdde

3v3

DDR2_EN BOOT_SEL T EST_4 PL_CLK3 PL_CLK2

K

USB_TXR

TUNE

gnd gnd gnd gnd gnd gnd digital_vdde

3v3

TEST_3 TEST_2 TEST_1 TEST_0 PL_CLK1

L

gnd

gnd

G

_

_

dith_vdd2v5 DDR_v dde1v8 vdd vdd gnd gnd gnd vdd digital_vdde

3v3

SMI_DATAIN

SMI_DATAO UT

SMI_CS_0 SMI_CS_1 MRESET

N

gnd

ADC_VREF P AIN_4 AIN_3 AIN _2

R

MCLK_VDD MCLK_

VDD2V5

P

DDR_MEM_

WE

DDR_MEM_

DQ_8

U

DDR_MEM_

DQ_10

Figure 2. SPEAr320S pin/ball map

123 45678 9 10111213 14 15 16 17

PL_GPIO_13 PL_GPIO _14 PL_GPIO_19 PL_GPIO_23 PL_GPIO _26 PL_GPIO_28 PL_G PIO_29 PL_GPIO_38 PL_GPIO_39 PL_GPIO _44 PL_GPIO_46 PL_GPIO_50 PL_G PIO_55 PL_GPIO_60 PL_GPIO_62 PL_GPIO_69 PL_G PIO_73

A

PL_GPIO_6 PL_GPIO_9 PL_GPIO _15 PL_GPIO_20 PL_GPIO_24 PL_G PIO_27 PL_GPIO_30 PL_GPIO_37 PL_GPIO_40 PL_GPIO _45 PL_GPIO_48 PL_GPIO_52 PL_G PIO_59 PL_GPIO _65 PL_GPIO _68 PL_GPIO_72 PL_G PIO_77

B

PL_GPIO_4 PL_GPIO_8 PL_GPIO _10 PL_GPIO_17 PL_GPIO_21 PL_G PIO_25 PL_GPIO_31PL_GPIO_36 PL_GPIO_41 PL_G PIO_47 PL_GPIO_49 PL_GPIO_56 PL_GPIO_63 PL_G PIO_67 PL_ GPIO_70 PL_GPIO _74 PL_G PIO_81

C

PL_GPIO_3 PL_GPIO_5 PL_G PIO_7 PL_GPIO_12 PL_GPIO_18 PL_G PIO_22 PL_GPIO_32 PL_GPIO_35 PL_GPIO_42 PL_GPIO_51 PL_GPIO_53 PL_GPIO _58 PL_GPIO_64 PL_GPIO_71 PL_G PIO_78 PL_GPIO _80PL_GPIO_84

D

RTC_XO RTC_XI PL_GPIO_1 PL_GPIO_2 PL_GPIO_11 PL_GPIO_16 PL_GPIO _33 PL_GPIO_34 PL_GPIO_43 PL_G PIO_54 PL_GPIO_57 PL_GPIO_61 PL_GPIO_66 PL_GPIO _75 PL_GPIO_82PL_GPIO_83 PL _GPIO_86

E

SPEAr320S Pin description

Doc ID 022508 Rev 1 29/97

RTC_vdd1v 5 RTC_gnd PL_GPIO_0

F

DITH _pll_vss

G

ana

USB_HOST1_DPUSB_HOST1_DMUSB_HOST1_

USB_HOST1_

vdd3v3

USB_HOST0_DPUSB_HOST0_DMUSB_HOST1_

USB_DEVICE

M

DP

USB_DEVICE

_vdd2v5

MCLK_XI MCLK_XO MCLK_G ND

P

DDR_MEM_

T

ADDR_1

DDR_MEM_

ADDR_2

DITH _pll_vd d

ana

USB_HOST0_

vdd2v5

USB_DEVICE

DM

DDR_MEM_

ADDR_0

DDR_MEM_

ADDR_3

USB_DEVICE

VBUS

VBUS

USB_HOST0_

VBUS

vdd2v5

USB_HOST1_

HOST0_

DEVICE_

Dvdd1v2

USB_DEVICE

_vdd3v3

MCLK_

GNDSUB

DDR_MEM_

ODT_0

DDR_MEM_

ADDR_4

DIGITAL_

GNDBG

COMP

USB_HOST0_

OVERCUR

USB_HOST1_

OVERCUR

USB_HOST0_

vdd3v3

USB_ANALO

TEST

dith_vss2v5 DDR_v dde1v8 DDR_vdde1v8 D DR_vdde1v8 DDR_vdde1v 8DDR_v dde1v8 DDR_vdde1v 8D DR_vdde1v8 ADC_agnd ADC_avdd ADC_VREFN AIN_1 AIN_0 SMI_CLK

DDR_MEM_

COMP2V5_

DDR_MEM_

COMP2V5_

GNDBGCOM

DDR_MEM_

ODT_1

DDR_MEM_

ADDR_5

digital_vdde

3v3

gnd gnd gnd gnd gnd gnd vdd digital_vdde

DDR_MEM_

ADDR_9

DDR_MEM_

ADDR_8

DDR_MEM_

ADDR_7

DDR_MEM_

ADDR_6

digital_vdde

3v3

DDR_MEM_

ADDR_10

DDR_MEM_

ADDR_11

DDR_MEM_

ADDR_12

DDR_MEM_

ADDR_13

digital_vdde

3v3

DDR_MEM_

BA_0

DDR_MEM_

ADDR_14

DDR_MEM_

CLKEN

vdd vdd digital_vdd e

DDR_MEM_

BA_1

DDR_MEM_

BA_2

DDR_MEM_

CAS

DDR_MEM_

RAS

DDR_MEM_

CS_0

DDR_MEM_

CS_1

DDR_MEM_

CLKP

DDR_MEM_

CLKN

3v3

DDR_MEM_

VREF

DDR_MEM_

GATE_OPEN

_0

nDDR_MEM_

DQS_0

DDR_MEM_

DQS_0

digital_vdde

3v3

DDR_MEM_

DQ_0

DDR_MEM_

DQ_1

DDR_MEM_

DQ_2

DDR_MEM_

DQ_3

digital_vdde

3v3

3v3

DDR_MEM_

DQ_6

DDR_MEM_

DQ_5

DDR_MEM_

DQ_4

DDR_MEM_

DM_0

PL_GPIO_76 PL_GPIO _79 PL_GPIO_85PL_GPIO_88 PL _GPIO_89

TMS TDI TDO nTRSTTCK

DDR_MEM_

DQ_7

DDR_MEM_

DQ_15

DDR_MEM_

DQ_14

DDR_MEM_

DQ_13

DDR_MEM_

GATE_OPEN

_1

DDR_MEM_

DM_1

DDR_MEM_

DQ_12

AIN_7 AIN_ 6 AIN_5

nDDR_MEM_

DQS_1

DDR_MEM_

DQS_1

DDR_MEM_

DQ_9

DDR_MEM_

DQ_11

Pin description SPEAr320S

3.2 Required external components

Some pads require the use of an external component. Please follow the instructions below

to ensure the proper functioning of the device:

1. DDR_COMP_1V8: place an external 121 kΩ resistor between ball P4 and ball R4

2. USB_TX_RTUNE: connect an external 43.2 Ω pull-down resistor to ball K5

3. DIGITAL_REXT: place an external 121 kΩ resistor between ball G4 and ball F4

4. DITH_VDD_2V5: add a ferrite bead to ball M4

3.3 Dedicated pins description

3.3.1 Clock, reset and 3V3 comparator pins

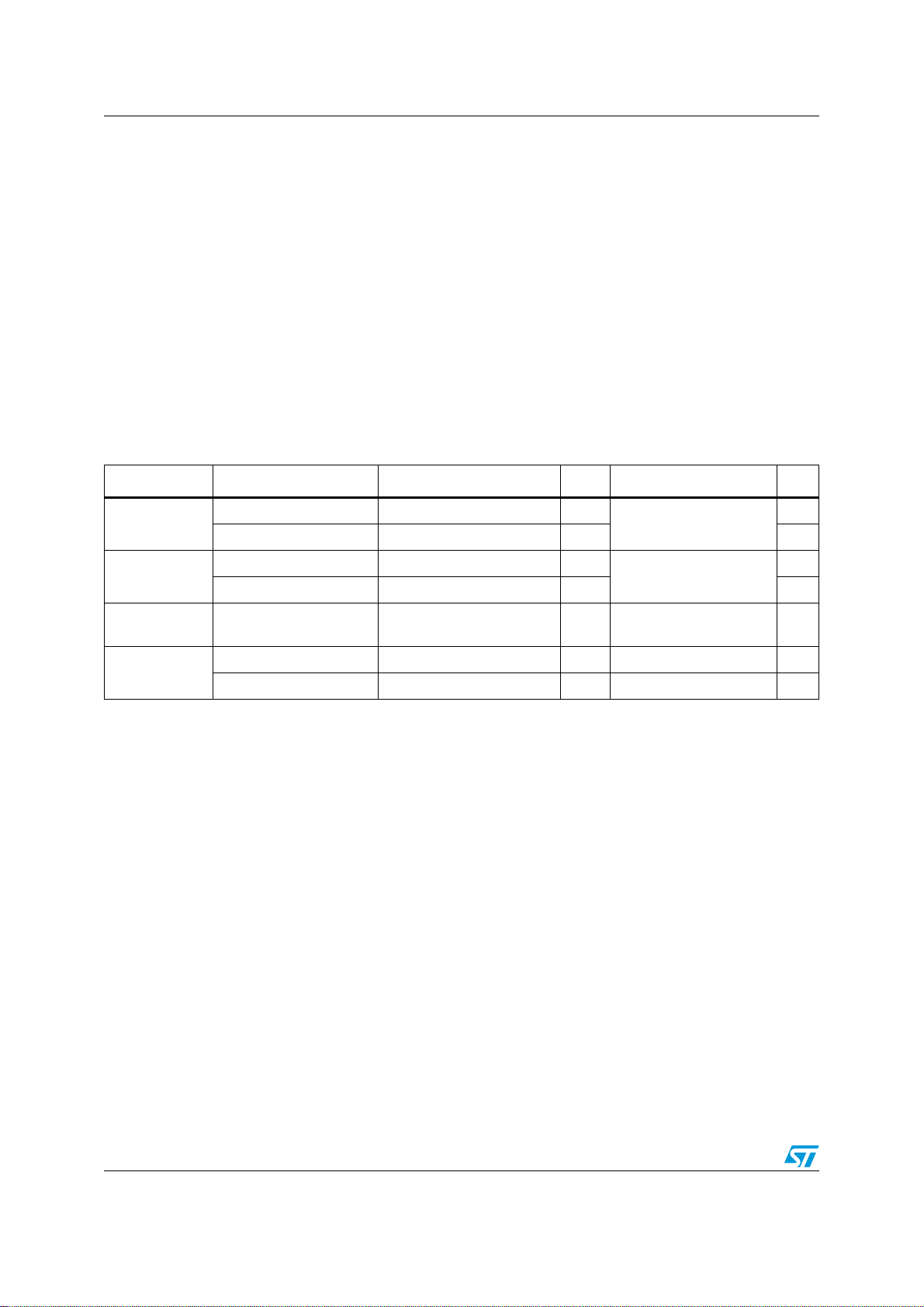

Table 6. MCLK, RTC, Reset and 3.3 V comparator pins description

Group Signal name Description Dir. Pin type Ball

Master clock

(MCLK)

Real-time clock

(RTC)

Reset MRESET Main reset I

3.3 V

comparator

MCLK_XI 24 MHz (typical) crystal in I

Oscillator 2.5 V capable

MCLK_XO 24 MHz (typical) crystal out O P2

RTC_XI 32 kHz crystal in I

Oscillator 1V5 capable

RTC_XO 32 kHz crystal out O E1

TTL Schmitt trigger input

buffer, 3.3 V tolerant

DIGITAL_REXT Configuration O Analog, 3.3 V capable G4

DIGITAL_GNDBGCOMP Power Power Power F4

P1

E2

M17

30/97 Doc ID 022508 Rev 1

Loading...

Loading...