ST L9903 User Manual

L9903

MOTOR BRIDGE CONTROLLER

1 FEATURES |

Figure 1. Package |

■OPERATING SUPPLY VOLTAGE 8V TO 20V, OVERVOLTAGE MAX. 40V

■OPERATING SUPPLY VOLTAGE 6V WITH IMPLEMENTED STEPUP CONVERTER

■QUIESCENT CURRENT IN STANDBY MODE LESS THAN 50µA

■ISO 9141 COMPATIBLE INTERFACE

■CHARGE PUMP FOR DRIVING A POWER MOS AS REVERSE BATTERY PROTECTION

■PWM OPERATION FREQUENCY UP TO 30KHZ

■PROGRAMMABLE CROSS CONDUCTION PROTECTION TIME

■OVERVOLTAGE, UNDERVOLTAGE, SHORT CIRCUIT AND THERMAL PROTECTION

■REAL TIME DIAGNOSTIC

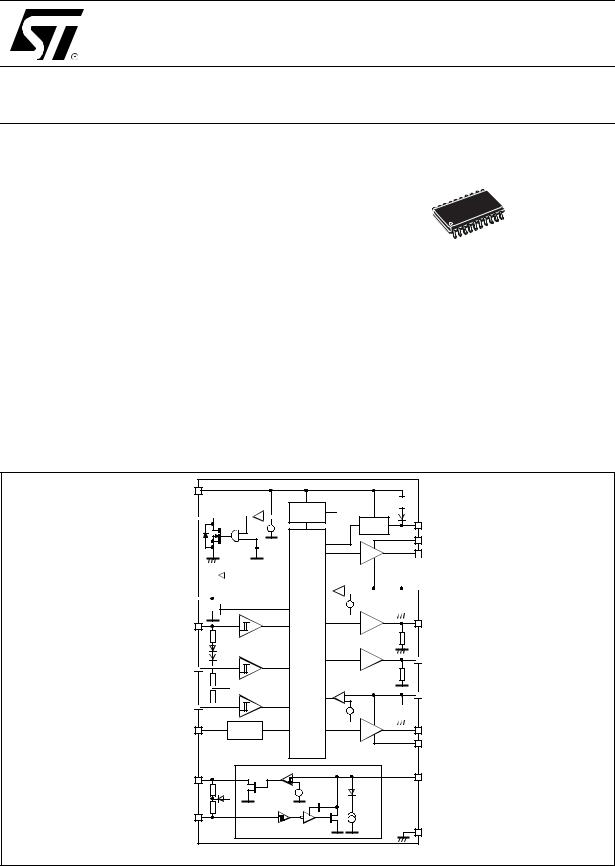

Figure 2. Block Diagram

SO20 |

|

|

|

|

|

Table 1. Order Codes |

|

|

|

|

|

Part Number |

|

Package |

|

|

|

L9903 |

|

SO20 |

|

|

|

L9903TR |

|

Tape & Reel |

|

|

|

2 DESCRIPTION

Control circuit for power MOS bridge driver in automotive applications with ISO 9141bus interface.

VS |

10 |

ST |

|

1 |

|

|

- |

|

|

|

|

+ |

|

||

= VSTH

fST

fST

|

|

|

|

|

|

VCC |

Overvoltage |

|

|

|

|

|

|

|

|

|

|

|

|

DG |

|

|

|

2 |

RDG |

Undervoltage |

|

||

|

|

|

Thermal shutdown |

|

|||||

|

|

|

|

|

|

|

|

|

|

EN |

4 |

REN

DIR

5

5

RDIR

VCC

VCC

RPWM

PWM

3

3

PR |

6 |

|

Timer |

||

|

RX |

7 |

|

RRX

VCC

RTX

TX |

8 |

|

Reference

BIAS

Control Logic

ISO-Interface

= 0.5 • VVS

RCP

RCP

VCC

Charge 11 CP pump

13 |

CB1 |

12 |

GH1 |

|

|

|

|

|

|

14 |

|

|

|

|

S1 |

V |

S1TH |

= |

|

RS1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

19 GL1

RGL1

18 GL2

GL2

RGL2

17

17 S2

S2

V S2TH = |

|

RS2 |

|

|

|||

|

|

|

|

15 |

GH2 |

16 |

CB2 |

|

9 |

K |

|

|

I KH |

|

20 |

GND |

|

|

REV. 4 |

|

October 2005 |

1/17 |

|

|

|

|

L9903

Table 2. Pin Function

N° |

Pin |

Description |

|

|

|

1 |

ST |

Open Drain Switch for Stepup converter |

|

|

|

2 |

DG |

Open drain diagnostic output |

|

|

|

3 |

PWM |

PWM input for H-bridge control |

|

|

|

4 |

EN |

Enable input |

|

|

|

5 |

DIR |

Direction select input for H-bridge control |

|

|

|

6 |

PR |

Programmable cross conduction protection time |

|

|

|

7 |

RX |

ISO 9141 interface, receiver output |

|

|

|

8 |

TX |

ISO 9141 interface, transmitter input |

|

|

|

9 |

K |

ISO 9141 Interface, bidirectional communication K-line |

|

|

|

10 |

VS |

Supply voltage |

|

|

|

11 |

CP |

Charge pump for driving a power MOS as reverse battery protection |

|

|

|

12 |

GH1 |

Gate driver for power MOS highside switch in halfbridge 1 |

|

|

|

13 |

CB1 |

External bootstrap capacitor |

|

|

|

14 |

S1 |

Source/drain of halfbridge 1 |

|

|

|

15 |

GH2 |

Gate driver for power MOS highside switch in halfbridge 2 |

|

|

|

16 |

CB2 |

External bootstrap capacitor |

|

|

|

17 |

S2 |

Source/drain of halfbridge 2 |

|

|

|

18 |

GL2 |

Gate driver for power MOS lowside switch in halfbridge 2 |

|

|

|

19 |

GL1 |

Gate driver for power MOS lowside switch in halfbridge 1 |

|

|

|

20 |

GND |

Ground |

|

|

|

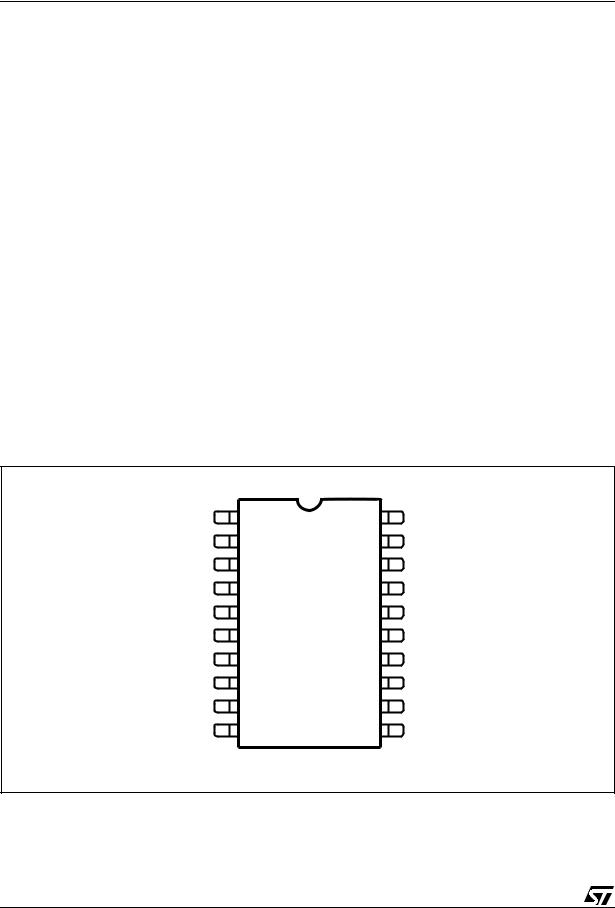

Figure 3. Pin Connection (Top view)

ST |

1 |

20 |

GND |

DG |

2 |

19 |

GL1 |

PWM |

3 |

18 |

GL2 |

EN |

4 |

17 |

S2 |

DIR |

5 |

16 |

CB2 |

PR |

6 |

15 |

GH2 |

RX |

7 |

14 |

S1 |

TX |

8 |

13 |

CB1 |

K |

9 |

12 |

GH1 |

VS |

10 |

11 |

CP |

|

|

SO20 |

|

2/17

|

|

|

L9903 |

Table 3. Absolute Maximum Ratings |

|

|

|

|

|

|

|

Symbol |

Parameter |

Value |

Unit |

|

|

|

|

VCB1 , VCB2 |

Bootstrap voltage |

-0.3 to 40 |

V |

ICB1 , ICB2 |

Bootstrap current |

-100 |

mA |

VCP |

Charge pump voltage |

-0.3 to 40 |

V |

ICP |

Charge pump current |

-1 |

mA |

VDIR ,VEN |

Logic input voltage |

-0.3 to 7 |

V |

,VPWM ,VTX |

|

|

|

IDIR ,IEN |

Logic input current |

±1 |

mA |

,IPWM ,ITX |

|

|

|

VDG ,VRX |

Logic output voltage |

-0.3 to 7 |

V |

IDG ,IRX |

Logic output current |

-1 |

mA |

VGH1, VGH2 |

Gate driver voltage |

-0.3 to VSX + 10 |

V |

IGH1 , IGH2 |

Gate driver current |

-1 |

mA |

VGL1 , VGL2 |

Gate driver voltage |

-0.3 to 10 |

V |

IGL1 , IGL2 |

Gate driver current |

-10 |

mA |

VK |

K-line voltage |

-20 to VS |

V |

VPR |

Programming input voltage |

-0.3 to 7 |

V |

IPR |

Programming input current |

-1 |

mA |

VS1 , VS2 |

Source/drain voltage |

-2 to VVS + 2 |

V |

IS1 , IS2 |

Source/drain current |

-10 |

mA |

VST |

Output voltage |

-0.3 to 40 |

V |

IST |

Step up output current |

-1 |

mA |

VVSDC |

DC supply voltage |

-0.3 to 27 |

V |

VVSP |

Pulse supply voltage (T < 500ms) |

40 |

V |

IVS |

DC supply current |

-100 |

mA |

For externally applied voltages or currents exceeding these limits damage of the device may occur!

All pins of the IC are protected against ESD. The verification is performed according to MIL883C, human body model with R=1.5kΩ, C=100pF and discharge voltage ±2kV, corresponding to a maximum discharge energy of 0.2mJ.

Table 4. Thermal Data

Symbol |

Parameter |

Value |

Unit |

|

|

|

|

TJ |

Operating junction temperature |

-40 to 150 |

°C |

TJSD |

Junction temperature thermal shutdown threshold |

min 150 |

°C |

TJSDH |

Junction thermal shutdown hysteresis |

typ 15 |

°C |

Rth j-amb |

Thermal resistance junction to ambient 1) |

85 |

°C/W |

1. see application note 110 for SO packages.

.

3/17

L9903

Table 5. Electrical Characteristcs |

|

|

|

|

|

|

(8V < VVS < 20V, VEN = HIGH, -40°C ≤ TJ |

≤ 150°C, unless otherwise specified. The voltages are refered to |

|||||

GND and currents are assumed positive, when current flows into the pin |

|

|

|

|

||

|

|

|

|

|

|

|

Symbol |

Parameter |

Test Condition |

Min. |

Typ. |

Max. |

Unit |

|

|

|

|

|

|

|

Supply (VS) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VVS OVH |

Overvoltage disable HIGH |

|

20 |

22 |

24 |

V |

|

threshold |

|

|

|

|

|

|

|

|

|

|

|

|

VVS OVh |

Overvoltage threshold hysteresis 2) |

|

|

1.6 |

|

V |

VVS UVH |

Undervoltage disable HIGH |

|

6 |

|

7 |

V |

|

threshold |

|

|

|

|

|

|

|

|

|

|

|

|

VVS UVh |

Undervoltage threshold |

|

|

0.66 |

|

V |

|

hysteresis 2) |

|

|

|

|

|

IVSL |

Supply current |

VEN = 0 ; VVS = 13.5V; TJ< 85°C |

|

|

50 |

µA |

IVSH |

Supply current, pwm-mode |

VVS= 13.5V; VEN= HIGH; |

|

8.1 |

13 |

mA |

|

|

VDIR= LOW; S1 = S2 = GND |

|

|

|

|

|

|

fPWM = 20kHz; CCBX = 0.1µF; |

|

|

|

|

|

|

CGLX = 4.7nF; CGHX = 4.7nF; |

|

|

|

|

|

|

RPR = 10kΩ; CPR = 150pF |

|

|

|

|

IVSD |

Supply current, dc-mode |

VVS= 13.5V; VEN= HIGH; |

|

5.8 |

10 |

mA |

|

|

VDIR= LOW; S1 = S2 = GND |

|

|

|

|

|

|

VPWM = LOW; CGHX = 4.7nF |

|

|

|

|

|

|

RPR = 10kΩ; CPR = 150pF |

|

|

|

|

Enable input (EN) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VENL |

Low level |

|

|

|

1.5 |

V |

VENH |

High level |

|

3.5 |

|

|

V |

VENh |

Hysteresis threshold 2) |

|

|

1 |

|

V |

REN |

Input pull down resistance |

VEN = 5V |

16 |

50 |

100 |

kΩ |

H-bridge control inputs (DIR, PWM) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDIRL |

Input low level |

|

|

|

1.5 |

V |

VPWML |

|

|

|

|

|

|

VDIRH |

Input high level |

|

3.5 |

|

|

V |

VPWMH |

|

|

|

|

|

|

VDIRh |

Input threshold hysteresis 2) |

|

|

1 |

|

V |

VPWMh |

|

|

|

|

|

|

RDIR |

Internal pull up resistance |

VDIR = 0; VPWM = 0 |

16 |

50 |

100 |

kΩ |

RPWM |

to internal VCC 3) |

|

|

|

|

|

DIAGNOSTIC output (DG) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VDG |

Output drop |

IDG = 1mA |

|

|

0.6 |

V |

RDG |

Internal pull up resistance |

VDG = 0V |

10 |

20 |

40 |

kΩ |

|

to internal VCC 3) |

|

|

|

|

|

Programmable cross conduction protection 4) |

|

|

|

|

||

NPR |

Threshold voltage ratio VPRH/ |

RPR = 10kΩ |

1.8 |

2 |

2.2 |

|

|

VPRL |

|

|

|

|

|

IPR |

Current capability |

VPR = 2V |

-0.5 |

|

|

mA |

ISO interface, transmission input (TX) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VTXL |

Input low level |

|

|

|

1.5 |

V |

4/17 |

|

|

|

|

|

|

|

|

|

|

|

|

L9903 |

Table 5. Electrical Characteristcs (continued) |

|

|

|

|

||

(8V < VVS < 20V, VEN = HIGH, -40°C ≤ TJ |

≤ 150°C, unless otherwise specified. The voltages are refered to |

|||||

GND and currents are assumed positive, when current flows into the pin |

|

|

|

|

||

|

|

|

|

|

|

|

Symbol |

Parameter |

Test Condition |

Min. |

Typ. |

Max. |

Unit |

|

|

|

|

|

|

|

VTXH |

Input high level |

|

3.5 |

|

|

V |

|

|

|

|

|

|

|

VTXh |

Input hysteresis voltage 2) |

|

|

1 |

|

V |

RTX |

Internal pull up resistance to |

VTX = 0 |

10 |

20 |

40 |

kΩ |

|

internal VCC 3) |

|

|

|

|

|

|

|

|

|

|

|

|

ISO interface, receiver output (RX) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VRXL |

Output voltage high stage |

TX = HIGH; IRX = 0; VK = VVS |

4.5 |

|

5.5 |

V |

RRX |

Internal pull up resistance |

TX = HIGH; |

5 |

10 |

20 |

kΩ |

|

to internal VCC 3) |

VRX = 0V |

|

|

|

|

RRXON |

ON resistance to ground |

TX = LOW; |

|

40 |

90 |

Ω |

|

|

IRX = 1mA |

|

|

|

|

tRXH |

Output high delay time |

Fig. 1 |

|

0.5 |

|

µs |

tRXL |

Output low delay time |

|

|

0.5 |

|

µs |

ISO interface, K-line (K) |

|

|

|

|

|

|

|

|

|

|

|

|

|

VKL |

Input low level |

|

-20V |

|

0.45 · |

|

|

|

|

|

|

VVS |

|

VKH |

Input high level |

|

0.55 · |

|

VVS |

|

|

|

|

VVS |

|

|

|

VKh |

Input hysteresis voltage 2) |

|

|

0.025· |

0.8V |

|

|

|

|

|

VVS |

|

|

IKH |

Input current |

VTX = HIGH |

-5 |

|

25 |

µA |

RKON |

ON resistance to ground |

VTX = LOW; IK=10mA |

|

10 |

30 |

Ω |

IKSC |

Short circuit current |

VTX = LOW |

40 |

|

130 |

mA |

fK |

Transmission frequency |

|

60 |

100 |

|

kHz |

2.not tested in production: guaranteed by design and verified in characterization

3.Internal VVCC is 4.5V ... 5.5V

4.see page 18 for calculation of programmable cross conduction protection time

tKr |

Rise time |

VVS = 13.5V; Fig. 1 |

|

2 |

6 |

µs |

|

|

External loads at K-line: |

|

|

|

|

|

|

RK = 510Ω pull up |

|

|

|

|

|

|

to VVS |

|

|

|

|

|

|

CK = 2.2nF to GND |

|

|

|

|

tKf |

Fall time |

|

|

2 |

6 |

µs |

|

|

|

|

|

|

|

tKH |

Switch high delay time |

|

|

4 |

17 |

µs |

tKL |

Switch low delay time |

|

|

4 |

17 |

µs |

tSH |

Short circuit detection time |

VVS = 13.5V; |

10 |

|

40 |

µs |

|

|

TX = LOW |

|

|

|

|

|

|

VK > 0.55 · VVS |

|

|

|

|

Charge pump |

|

|

|

|

|

|

|

|

|

|

|

|

|

VCP |

Charge pump voltage |

VVS = 8V |

VVS |

|

VVS |

|

|

|

|

+7V |

|

+14V |

|

|

|

VVS = 13.5V |

VVS |

|

VVS |

|

|

|

|

+10V |

|

+14V |

|

|

|

VVS = 20V |

VVS |

|

VVS |

|

|

|

|

+10V |

|

+14V |

|

|

|

|

|

|

|

|

5/17

L9903

Table 5. Electrical Characteristcs (continued) |

|

|

|

|

|||

(8V < VVS < 20V, VEN = HIGH, -40°C ≤ TJ |

≤ 150°C, unless otherwise specified. The voltages are refered to |

||||||

GND and currents are assumed positive, when current flows into the pin |

|

|

|

|

|||

|

|

|

|

|

|

|

|

Symbol |

Parameter |

Test Condition |

Min. |

Typ. |

Max. |

Unit |

|

|

|

|

|

|

|

|

|

ICP |

Charging current |

VVS = 13.5V |

-50 |

-75 |

|

µA |

|

|

VCP= VVS + 8V |

|

|

|

|

|

|

tCP |

Charging time 2) |

VVS = 13.5V |

|

1.2 |

4 |

ms |

|

|

VCP= VVS + 8V |

CCP = 10nF |

|

|

|

|

|

fCP |

Charge pump frequency |

VVS = 13.5V |

250 |

500 |

750 |

kHz |

|

Drivers for external highside power MOS |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

VCB1 |

Bootstrap voltage |

VVS = 8V; ICBX = 0; VSX = 0 |

7.5 |

|

14 |

V |

|

VCB2 |

|

|

VVS =13.5V; ICBX = 0; VSX = 0 |

10 |

|

14 |

V |

|

|

|

VVS = 20V; ICBX = 0; VSX = 0 |

10 |

|

14 |

V |

RGH1L |

ON-resistance of SINK stage |

VCBX = 8V; VSX = 0 |

|

|

10 |

Ω |

|

RGH2L |

|

|

IGHX = 50mA; TJ = 25°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCBX = 8V; VSX = 0 |

|

|

20 |

Ω |

|

|

|

IGHX = 50mA; TJ = 125°C |

|

|

|

|

RGH1H |

ON-resistance of SOURCE stage |

IGHX = -50mA; TJ = 25°C |

|

|

10 |

Ω |

|

RGH2H |

|

|

IGHX = -50mA; TJ = 125°C |

|

|

20 |

Ω |

VGH1H |

Gate ON voltage (SOURCE) |

VVS= VSX = 8V; IGHX = 0; |

VVS |

|

VVS |

|

|

VGH2H |

|

|

CCBX = 0.1µF |

+6.5V |

|

+14V |

|

|

|

|

VVS = VSX = 13.5V; IGHX = 0; |

VVS |

|

VVS |

|

|

|

|

CCBX = 0.1µF |

+10V |

|

+14V |

|

|

|

|

VVS = VSX = 20V; IGHX = 0; |

VVS |

|

VVS |

|

|

|

|

CCBX = 0.1µF |

+10V |

|

+14V |

|

RGH1 |

Gate discharge resistance |

EN = LOW |

10 |

100 |

|

kΩ |

|

RGH2 |

|

|

|

|

|

|

|

RS1 |

Sink resistance |

|

10 |

100 |

|

kΩ |

|

RS2 |

|

|

|

|

|

|

|

Drivers for external lowside power MOS |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

RGL1L |

ON-resistance of SINK stage |

IGLX = 50mA; TJ = 25°C |

|

|

10 |

Ω |

|

RGL2L |

|

|

IGLX = 50mA; TJ = 125°C |

|

|

20 |

Ω |

RGL1H, |

ON-resistance of SOURCE stage |

IGLX = -50mA; TJ = 25°C |

|

|

10 |

Ω |

|

RGL2H |

|

|

IGLX = -50mA; TJ = 125°C |

|

|

20 |

Ω |

VGL1H, |

Gate ON voltage (SOURCE) |

VVS = 8V; IGLX = 0 |

7V |

|

VVS |

|

|

VGL2H |

|

|

VVS = 13.5V; IGLX = 0 |

10V |

|

VVS |

|

|

|

|

VVS = 20V; IGLX = 0 |

10V |

|

14V |

|

RGL1 |

Gate discharge resistance |

EN = LOW |

10 |

100 |

|

kΩ |

|

RGL2 |

|

|

|

|

|

|

|

2. not tested in production: guaranteed by design and verified in characterization |

|

|

|

|

|||

|

|

|

|

|

|

|

|

Timing of the drivers |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

tGH1LH |

Propagation delay time |

Fig. 2 |

|

|

500 |

ns |

|

tGH2LH |

|

|

VVS = 13.5V |

|

|

|

|

|

|

|

VS1 = VS2 =0 |

|

|

|

|

|

|

|

CCBX = 0.1µF |

|

|

|

|

|

|

|

RPR= 10kW |

|

|

|

|

|

|

|

|

|

|

|

|

6/17

Loading...

Loading...