■

WIDE OPERATING SUPPLY VOLTAGE

RANGE FROM 4.5V UP TO 32V FOR

TRANSIENT 45V

■

VERY LOW STANDBY QUIESCENT

CURRENT TYPICALLY < 2µA

■ INPUT TO OUTPUT SIGNAL TRANSFER

FUNCTION PROGRAMMABLE

■

HIGH SIGNALRANGEFROM -14V UP TO45V

FOR ALL INPUTS

■

3.3V CMOS COMPATIBLE INPUTS

■ DEFINED OUTPUT OFF STATE FOR OPEN

INPUTS

■

FOUR OPEN DRAINDMOS OUTPUTS, WITH

R

■ OUTPUT CURRENT LIMITATION

■ CONTROLLED OUTPUT SLOPE FOR LOW EMI

■ OVERTEMPERATURE PROTECTION FOR

= 1.5ΩFOR VS>6VAT25°C

DSon

EACH CHANNEL

■

INTEGRATED OUTPUT CLAMPING FOR FAST

INDUCTIVE RECIRCULATION V

FB

>45V

L9333

QUAD LOW SIDE DRIVER

PRODUCT PREVIEW

MULTIPOWERBCD TECHNOLOGY

SO20 & SO20 (12+4+4)

ORDERING NUMBER:

L9333MD (SO20 12+4+4)

L9333 (SO20)

■

STATUS MONITORING FOR

- OVERTEMPERATURE

- DISCONNECTED GROUND OR SUPPLY

VOLTAGE

DESCRIPTION

The L9333 is a monolithic integrated quad low side

driver. It is intended to drive lines, lamps or relais in

automotive or industrial applications.

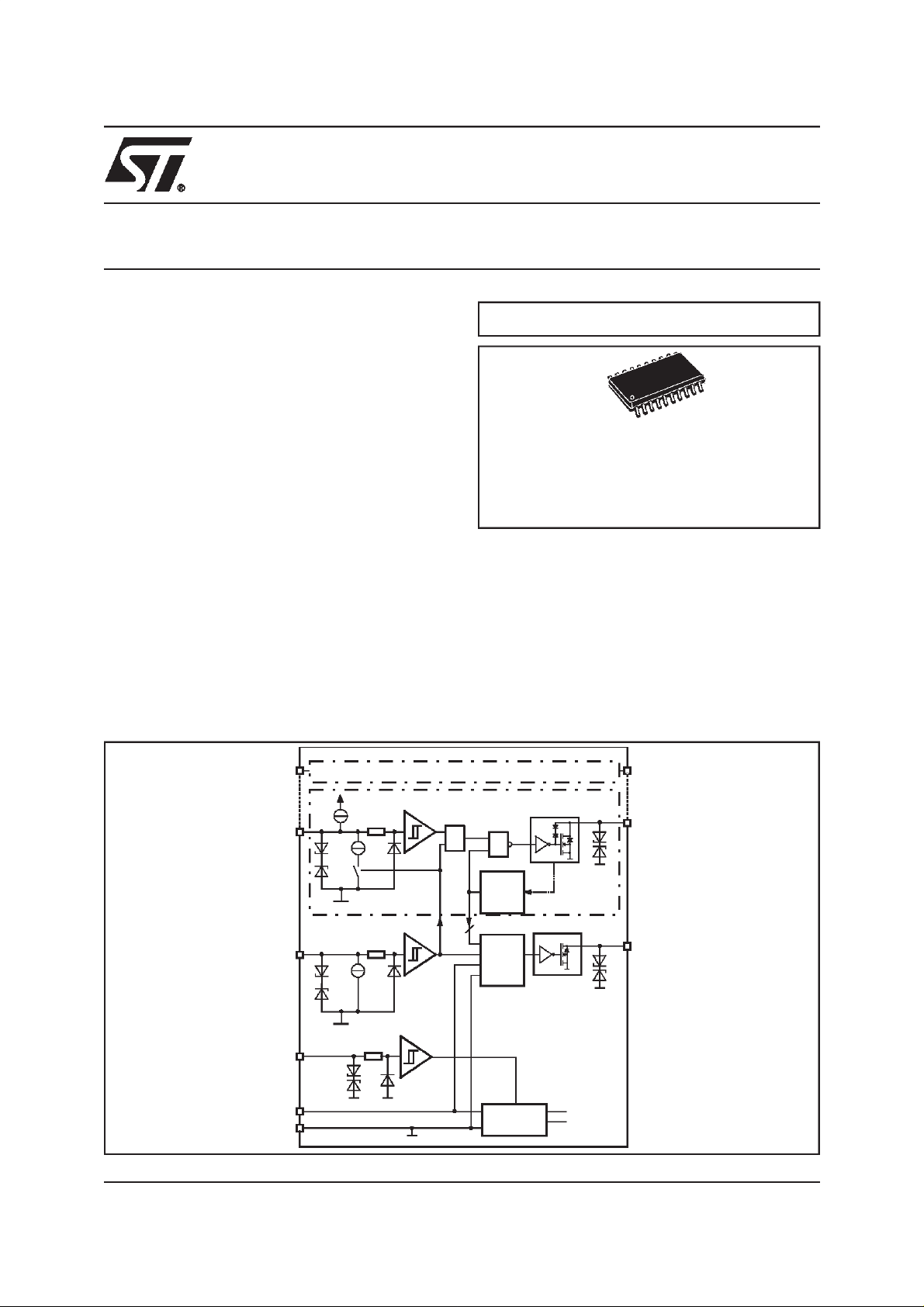

BLOCK DIAGRAM

IN 4

IN 1

PRG

EN

VS

GND

January 2000

This ispreliminary information on a new product now in development. Details are subject to change without notice.

CHANNEL4

VS

R

IN

PRG

R

IN

R

EN

=

THERMAL

SHUTDOWN

4

DIAG-

NOSTIC

LOGIC

REFERENCE

&

CHANNEL1

Vint

Vlogic

OUT 4

OUT 1

DIAG

1/13

L9333

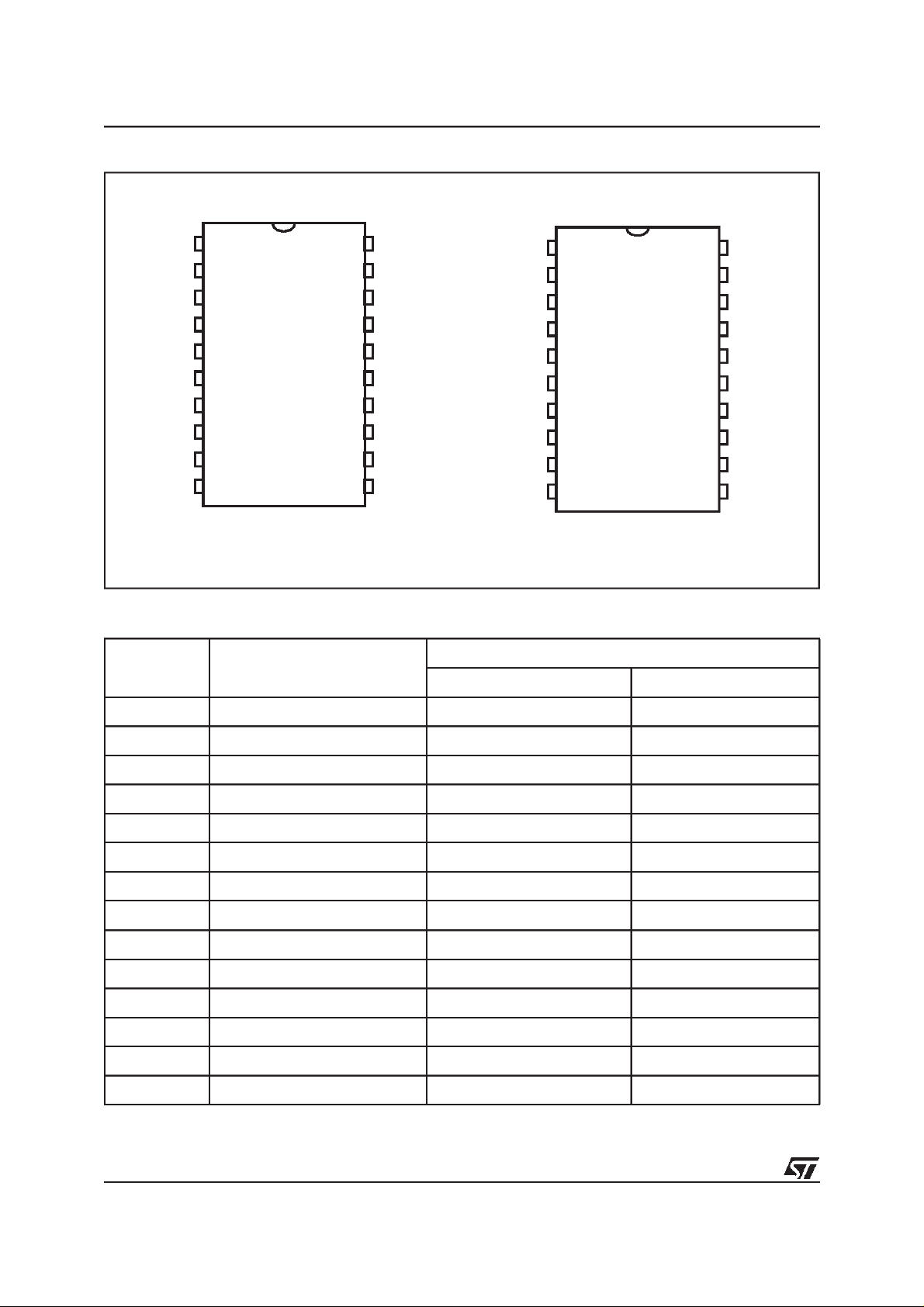

PIN CONNECTION (Top view)

1

NC

2

VS

3

NC

4

IN3

5

IN4

6

EN

OUT4

OUT3

GND

7

813

9

10 11

NC

SO 20 STD

PIN FUNCTION

Pin Name Description

20

NC

19

DIAG

18

NC

17

IN2

16

IN1

15

PRG

14

OUT1

DIAG

GND

GND

GND

GND

OUT2

12

NC

NC

1

IN1

2

IN2

3

4

5

6

7

VS

813

IN3

9

10 11

IN4

So 12+4+4

20

PRG

19

OUT1

18

OUT2

17

GND

16

GND

15

GND

14

GND

Med. Power

OUT3

12

OUT4

EN

Package

SO20 SO20 (SO 12+4+4)

VS Supply Voltage 2 8

GND Ground 9 4, 5, 6, 7, 14, 15, 16, 17

EN Enable 6 11

PRG Programming 15 20

DIAG Diagnostic 19 3

IN 1 Input 1 16 1

IN 2 Input 2 17 2

IN 3 Input 3 4 9

IN 4 Input 4 5 10

OUT 1 OUTPUT 1 14 19

OUT 2 OUTPUT 2 13 18

OUT 3 OUTPUT 3 8 13

OUT4 OUTPUT4 7 12

NC Not Connected 1,3,10,11,12,18,20 -

2/13

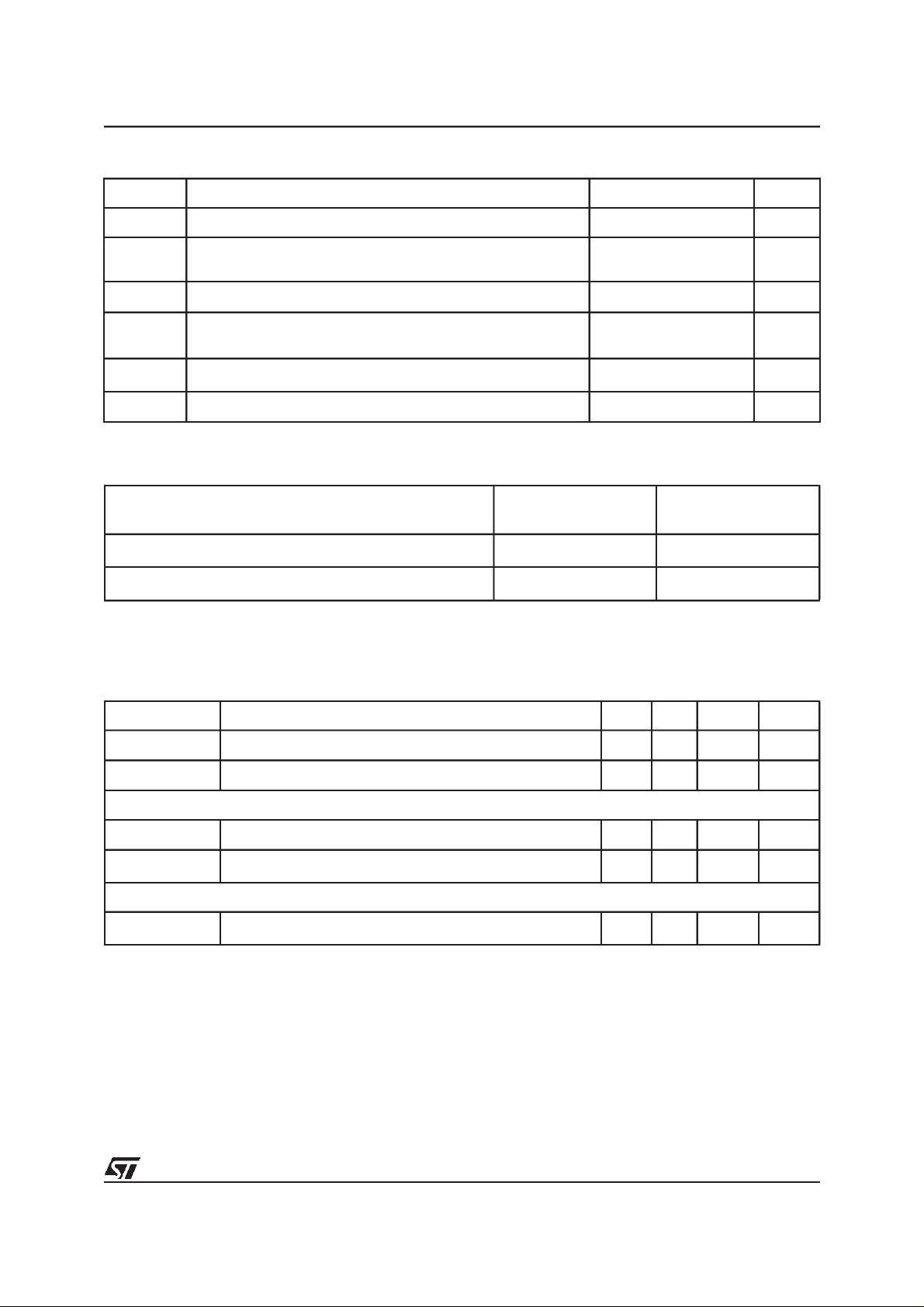

ABSOLUTEMAXIMUM RATINGS

Symbol Parameter Value Unit

L9333

V

dV

S

V

IN,VEN

V

PRG

V

OUT

V

DIAG

Notes: 1. In flybackphase the output voltage can reach 60V.

Supply voltage DC

S

Supply voltage Pulse (T = 400ms)

-0.3 to 32

-0.3 to 45

/dt Supply voltage transient -10 to +10 V/µs

,

Input, Enable, Programming

-14to 45 V

Pin voltage

Output voltage

-0.3 to 45

1)

Diagnostic output voltage -0.3 to 45 V

V

V

V

ESD - PROTECTION

Parameter

Supply pins and signal pins ± 2KV

Output pins ± 4KV

Note: Human-Body-Model according to MIL 8832. The device widthstand ST1 classlevel.

Value

against GND

Unit

THERMAL DATA

Symbol Parameter Min Typ Max Unit

T

T

JSDhys

JSD

Temperature shutdown threshold 175 220 °C

Temperature shutdown hysteresis 20 K

SO 12+4+4

R

th (j-p)

R

th (j-a)

Thermal resistance junction to pins 15 °C/W

Thermal resistance junction to ambient

SO 20

R

th (j-a)

2. With 6cm2on board heat sink area.

3. Mounted on SMPCB2board

Thermal resistance junction to ambient

2)

3)

50 °C/W

97 °C/W

3/13

L9333

LIFE TIME

Symbol Parameter Condition Value Unit

t

B

useful life time VS≤ 14V

20 years

EN = low

t

b

operating life time 4.5V ≤ VS≤ 32V

5000 hours

EN = high

OPERATINGRANGE:

Within the operating range the IC operates as described in the circuit description, including the diagnostic table.

Symbol Parameter Condition Min Max Unit

V

V

IN,VEN

V

PRG

V

OUT

S

Supply voltage 4.5 32 V

,

Input voltage -14 45 V

Output voltage Voltage will be limited by internal Z-

-0.3 60 V

Diode clamping

V

DIAG

T

J

Diagnostic output voltage -0.3 45 V

Junction temperature -40 150 °C

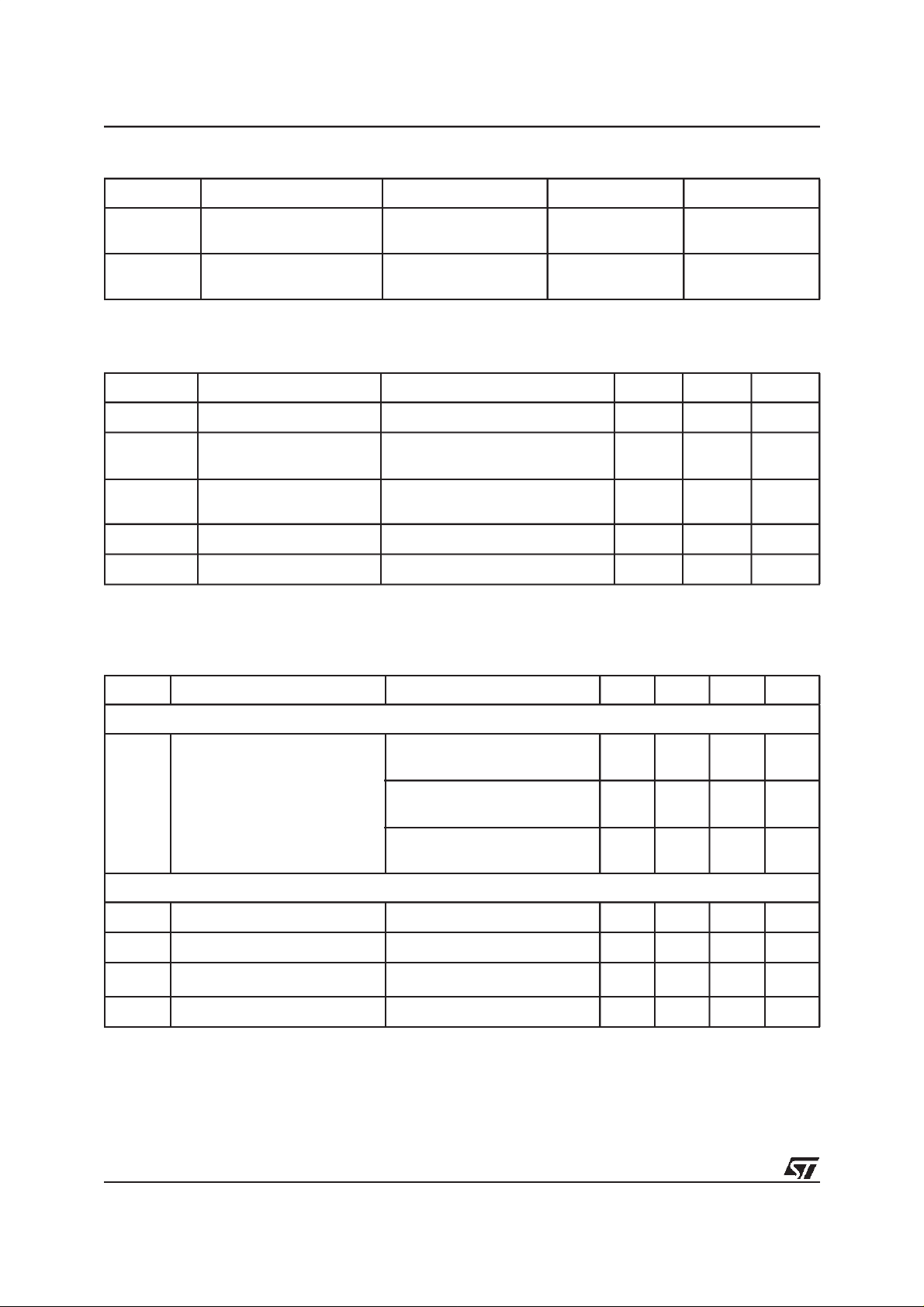

ELECTRICAL CHARACTERISTCS

The electrical characteristics are valid within the defined Operating Conditions, unless otherwise specified.

The function is guaranteed by design until T

Symbol Parameter Test Condition Min. Typ. Max. Unit

switch-on-threshold.

JSDon

SUPPLY

Quiescent current VS≤ 14V; VEN≤ 0.3V

I

Q

85 °C

T

amb

V

14V; V

≤

S

150°C

T

a

V

14V;EN = high, Output = off

≤

S

EN

≤

0.3V

<2 10 µA

12

EN = high, Output = on

Inputs, IN1 - IN4;Programming, PRG

V

V

INhigh

R

INlow

Input voltage LOW -14 1 V

Input voltage HIGH 2 45 V

I

Input current

IN

Input impedance VIN< 0V; VIN>V

IN

4. Current direction depends on the programming setting (PRG=high leads into a positive current see also Blockdiagram page 1)

0V ≤ V

IN

≤ 45V

4)

S

-25 50 µA

10 60 kΩ

50 µA

mA

3.5

mA

4/13

L9333

ELECTRICAL CHARACTERISTCS

(continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

Enable EN

V

ENlow

V

ENhigh

R

I

Input voltage LOW -14 1 V

Input voltage HIGH 2 45 V

Input impedance -14V < VEN< 1.5V 5 k

EN

Input current 1.5V < VEN< 45V 5 80 µA

EN

Outputs OUT1- OUT4

R

DSon

I

OLeak

V

OClamp

I

OSC

C

Output ON-resistor VS>6V,IO= 0.3A 1.7 3.8

Leakage current VO=VS= 14V;Ta< 125°C15µA

V

=VS= 14V;Ta< 150°C25µA

O

Output voltage during clamping EFB≤ 2mJ; 10 mA < IO< 0.3A 45 52 60 V

Short-circuit current VS> 6V 400 700 1000 mA

internal output capacities VO> 4.5V 100 pF

O

Diagnostic Output DIAG

V

Output voltage LOW IDL= 0.6mA 0.8 V

Dlow

Ω

Ω

I

Dmax

I

DLeak

Timing Characteristics

t

d,on

t

d,off

t

t

d,DIAG

S

Note : All parameters are measured at 125°C.

Max. output current internal current limitation; VD=

Leakage current VD=VS=14V;Ta<125°C 0.1 1 µA

5)

On delay time VS=14V

Off delaytime 3 4.5 µs

Enable settling time 20 µs

set

ON or OFF Diagnostic delay time 10 µs

Output voltage slopes 2.5 9 16 V/µs

out

5. See also Fig.3 TimingCharacteristics

14V

V

C

=14V;Ta<150°C5µA

D=VS

ext

= 0F; L

ext

=0H

only testing condition

10mA ≤ I

≤ 200mA

0

1515mA

2 3.5 µs

5/13

L9333

Figure 1. Timing Characteristics

V

EN

Active

V

PR G

V

0.8 V

V

IN

OUT

V

t

Non-Inverting Mode Inverting Mode

t

t

S

S

6)

0.2 V

S

t

set

t

d,off

6. Output voltage slope not controlled for enable low!

6/13

t

d,on

t

t

set

L9333

FUNCTIONAL DESCRIPTION

The L9333 is a quad low side driver for lines, lamps or inductive loads in automotive and industrial applications.

The logic input levels are 3.3V CMOS compatible. This allows the device to be driven directly by a microcon-

troller. For the noise immunity, all input thresholds have a hysteresis of typ. 100mV. Each input (IN, EN and

PRG) is protected towithstand voltages from-14Vto 45V. The device is activated with a’high’ signal on ENable.

ENable ’low’ switches the device into the sleep mode. In this mode the quiescent current is typically less than

2µA. A high signalon PRoGramming input changes the signaltransferpolarity from noninverting to the inverting

mode. This pin can be connected either to V

PRG and EN pin is low. For packaged applications it is still recommended to connect all input pins to ground

respective VS to avoid EMC influence. The forced condition leads to a mode change if the PRG pin was high

before the interruption. Independent of the PRoGramminginput, the OUTput switches off, if the signal INput pin

is not connected. This function is verified using a leakage current of 5µA (sink for PRG=high; source for

PRG=low) during circuit test.

Each output driver has a current limitation of min 0.4A and an independent thermal shut-down. The thermal

shut-down deactivates that output, whichexceeds temperature switch off level. When the junction temperature

decreases 20K below this temperature threshold the output will be activated again. This 20K is the hysteresis

of the thermal shutdown function. The Gates, of the output DMOS transistors are charged and discharged with

a current source. Therefore the output slope is limited. This reduces the electromagnetic radiation. For inductive loads an output voltage clamp of typically 52V is implemented.

The DIAGnostic is an open drain output. The logic status depends on the PRoGramming pin. If the PRG pin is

’low’ the DIAG output becomes low, if the device works correctly.At thermal shut-down of one channel or if the

ground is disconnected the DIAGnostic output becomes high. If the PRG pin is ’high’ this output is switched off

at normal function and switched on at overtemperature. For the fault condition of interrupted ground, the potential of VS and Diagnostic should be equal.

or GND. If these pins are not connected, the forced status of the

S

DIAGNOSTICTABLE

Pins EN PRG IN OUT DIAG

Normal function H L L L (on) L (on)

H L H H (off) L (on)

H H L H (off) H (off)

H H H L(on) H (off)

L X X H (off) H (off)

Overtemperature,

disconnected ground or

supply voltage

Overtemperature H H X

X = not relevant

* selective for each channel at overtemperature

HLX

H (off)

H(off)

*

*

H (off)

L(on)

7/13

L9333

Figure 2. Application for Inverting Transfer Polarity

BOARD VOLTAGE 14 V

VCC = 5V or 3.3V

33µF

VCC

MICROCONTROLLER

GND

INT

D0

D1

D2

D3

AdressdecoderA 0:8

8

PRG

EN

IN 1

IN 2

IN 3

IN 4

VS

DIAG

L9333

OUT 1

OUT 2

OUT 3

OUT 4

GND

Figure 3. Application for non Inverting Transfer Polarity

BOARD VOLTAGE 14 V

33µF

2 W 12 mH

50 kHz

M

10µH

250 mA

240Ω

50pF

VCC = 5V

VCC

IN

GND

VS

PRG

L9333

GND

DIAG

2 W 12 mH

OUT 1

OUT 2

OUT 3

OUT 4

EN

IN 1

IN 2

IN 3

IN 4

Note Werecommend to use the device for driving inductive loads with flyback energy EFB≤ 2mJ.

8/13

10µH

M

250mA

240Ω

50pF

VCC = 5V

VCC

IN

GND

L9333

EMC SPECIFICATION

EMS (electromagneticsusceptibility)

Measurement setup:

DUT mounted on a specific application board is driven in a typical application circuit (see below). Two devices

are stimulated by a generator to read and write bus signals. They will be monitored externally to ensure proper

function.

Figure 4. PCB layout

TOPSIDE

BACKSIDE

Measurementmethod:

a) The two bus lines are transferred 2m under a terminated stripline.That’s where they were exposed to the

RF-field. Stripline setup and measurement method is described in DIN 40839-4 or ISO 11452-5.

b) DUT mounted on the same application board is exposed to RF through the tophole of a TEM-cell. Mea-

surement method according SAE J1752.

c) The two bus lines are transferred into a BCI current injection probe. Setup and measurement method is

described in ISO 11452-4.

Failure criteria:

Failure monitoring is done by envelope measurement of the logic signals with a LeCroy oscilloscope with acceptance levels of 20% in amplitude and 2% time.

Limits:

The device is measured within the described setup and limitswithout fail function.

The Electromagnetic Susceptivity is not tested in production.

a) Field strength under stripline of > 250V/m in the frequency range 1 - 400MHz modulation:AM 1kHz 80%.

b) Field strength in TEM-cell of > 500V/m in the frequency range 1 - 400MHz modulation: AM 1kHz 80%.

c) RF-currents with BCI of > 100mA in the frequency range 1 - 400MHz modulation: AM 1kHz 80%.

9/13

L9333

Measured Circuit

The EMS of the device was verified in the below described setup.

Figure 5.

Ω

11

100

∗

optional

4

Ω

20k

Ω

10k

Jumper

Ω

10k

4.7nF 4.7nF

ANECHOIC CHAMBER

10nF

33µF

SM6T39A

SMBYW01-200

1

19

Jumper

DIAG

VS EN PRG

4 ∗ 10kΩ

14

16

OUT1

IN1

8

13

OUT2

L9333

IN2

4

17

7

4 ∗ 1nF

optional

OUT3

IN3

4.7nF

OUT4

GND

IN4

4 ∗ 4.7n

5

9

10/13

2m

Stripline

Flat cable

11

1

9

14

13

8

7

16

125Hz

17

2

f

U(t)

4

250Hz

500Hz

2

f

14V

-

+

5

1kHzf2

L9333

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.35 2.65 0.093 0.104

A1 0.1 0.3 0.004 0.012

B 0.33 0.51 0.013 0.020

C 0.23 0.32 0.009

D 12.6 13 0.496 0.512

E 7.4 7.6 0.291 0.299

e 1.27 0.050

H 10 10.65 0.394 0.419

h 0.25 0.75 0.010 0.030

L 0.4 1.27 0.016 0.050

K0°(min.)8°(max.)

mm inch

0.013

OUTLINE AND

MECHANICAL DATA

SO20

B

e

D

1120

110

L

hx45°

A

K

A1 C

H

E

SO20MEC

11/13

L9333

PAD

L9333

12/13

L9333

Information furnished is believed tobe accurate and reliable. However,STMicroelectronics assumes no responsibility for the consequences

of useof such information nor for any infringementof patents or other rightsof third partieswhich may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products arenot

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

2000 STMicroelectronics - All Rights Reserved

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta- Morocco - Singapore - Spain

STMicroelectronics GROUP OF COMPANIES

- Sweden- Switzerland - United Kingdom - U.S.A.

http://www.st.com

13/13

Loading...

Loading...