Features

SO-16

DIP-

16

■ High-voltage rail up to 600 V

■ dV/dt immunity ±50 V/nsec in full temperature

range

■ Driver current capability:

– 290 mA source

– 430 mA sink

■ Switching times 75/35 nsec rise/fall with 1 nF

load

■ 3.3 V, 5 V TTL/CMOS inputs with hysteresis

■ Integrated bootstrap diode

■ Operational amplifier for advanced current

sensing

■ Comparator for fault protection

■ Smart shutdown function

■ Adjustable deadtime

■ Interlocking function

■ Compact and simplified layout

■ Bill of material reduction

■ Effective fault protection

■ Flexible, easy and fast design

Applications

L6390

High-voltage high/low-side driver

Datasheet − production data

Description

The L6390 is a high-voltage device manufactured

with BCD™ “offline” technology. It is a single-chip

half bridge gate driver for N-channel Power

MOSFETs or IGBT.

The high-side (floating) section is designed to

stand a voltage rail up to 600 V. The logic inputs

are CMOS/TTL compatible down to 3.3 V for easy

microcontroller/DSP interfacing.

The IC embeds an operational amplifier suitable

for advanced current sensing in applications such

as field oriented motor control.

An integrated comparator is available for

protection against overcurrent, overtemperature,

etc.

■ Motor driver for home appliances, factory

automation, industrial drives

■ HID ballasts, power supply units

Table 1. Device summary

Order code Package Packaging

L6390N DIP-16 Tube

L6390D SO-16 Tube

L6390DTR SO-16 Tape and reel

July 2012 Doc ID 14493 Rev 7 1/26

This is information on a product in full production.

www.st.com

26

Contents L6390

Contents

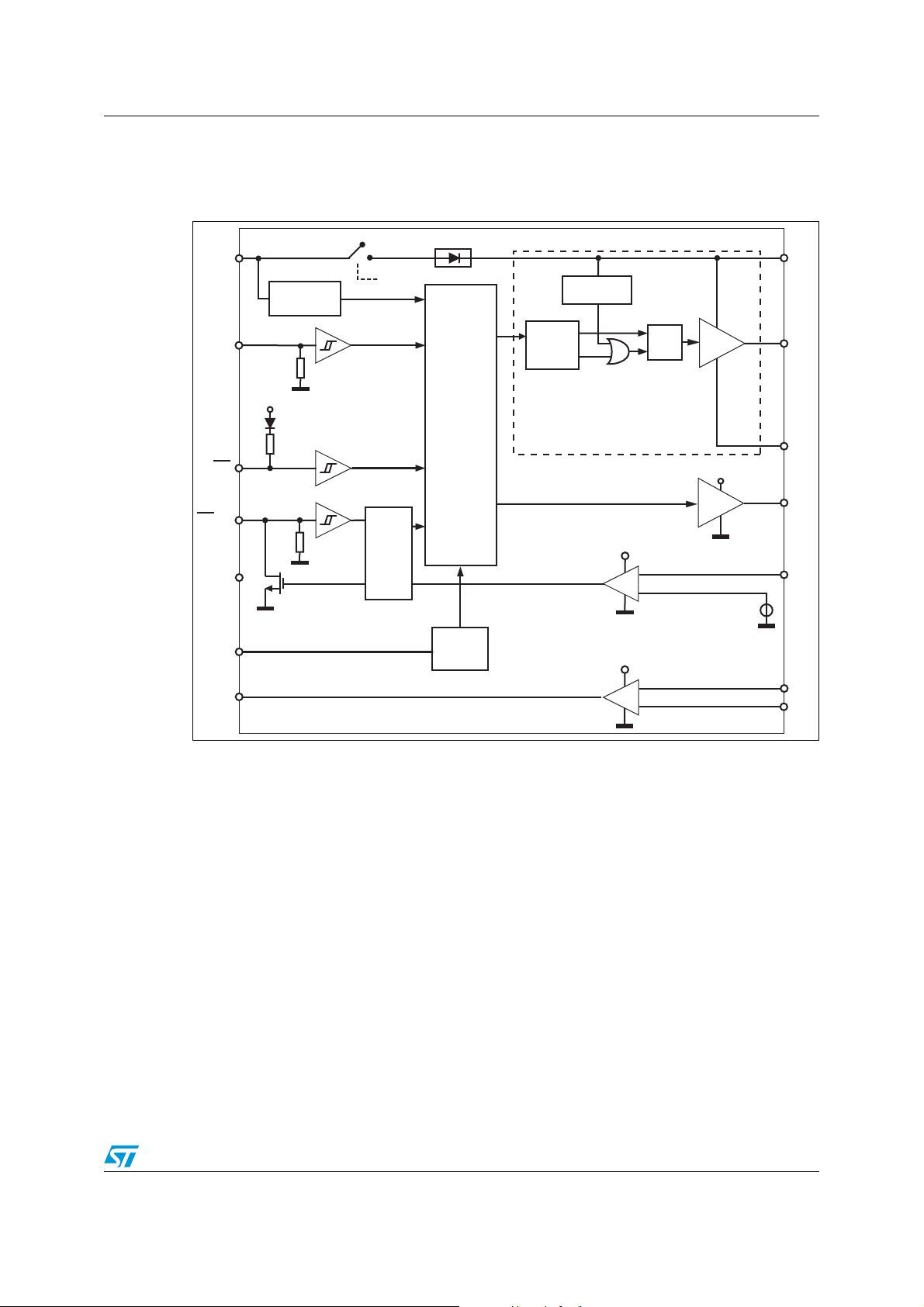

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

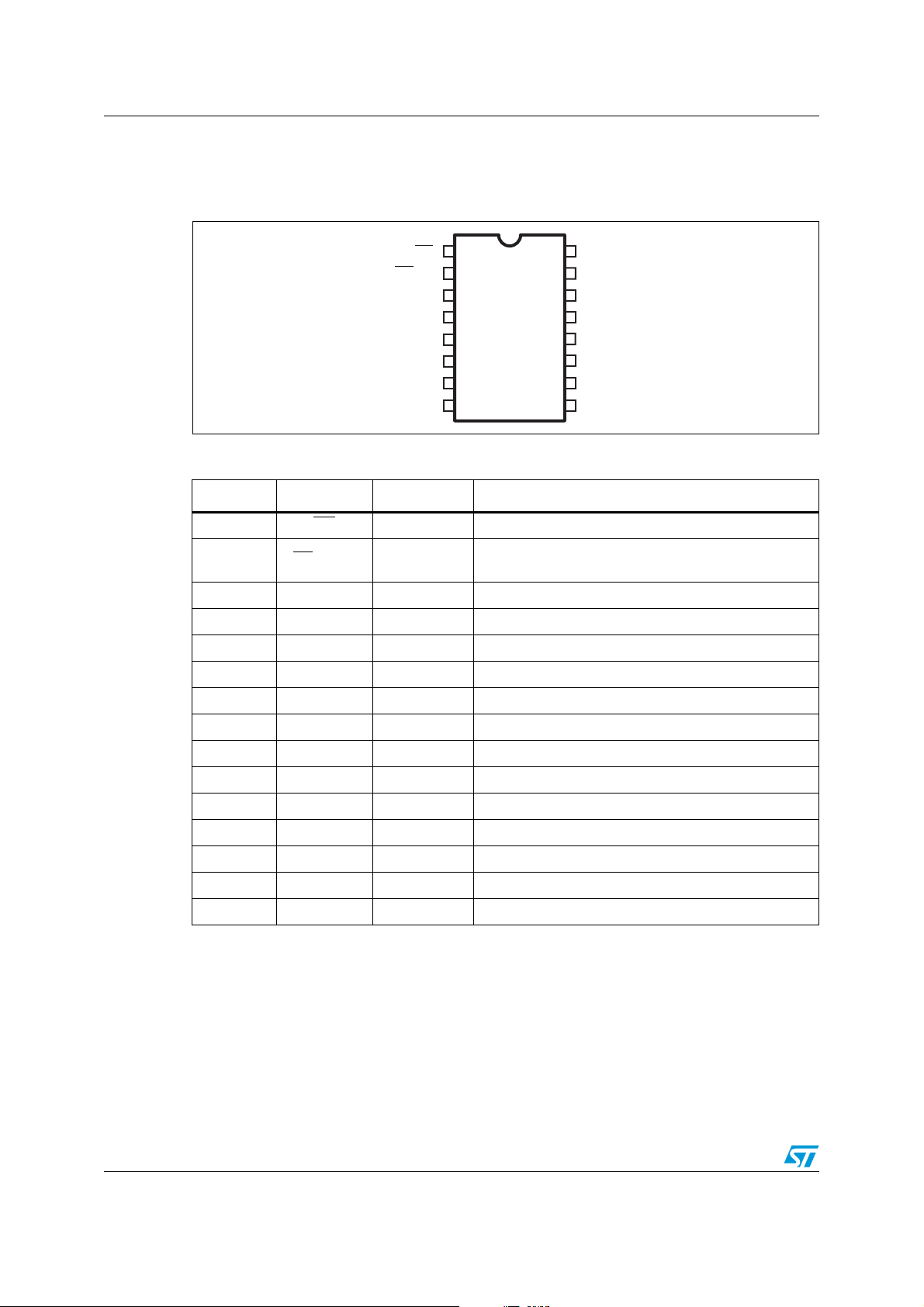

2 Pin connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

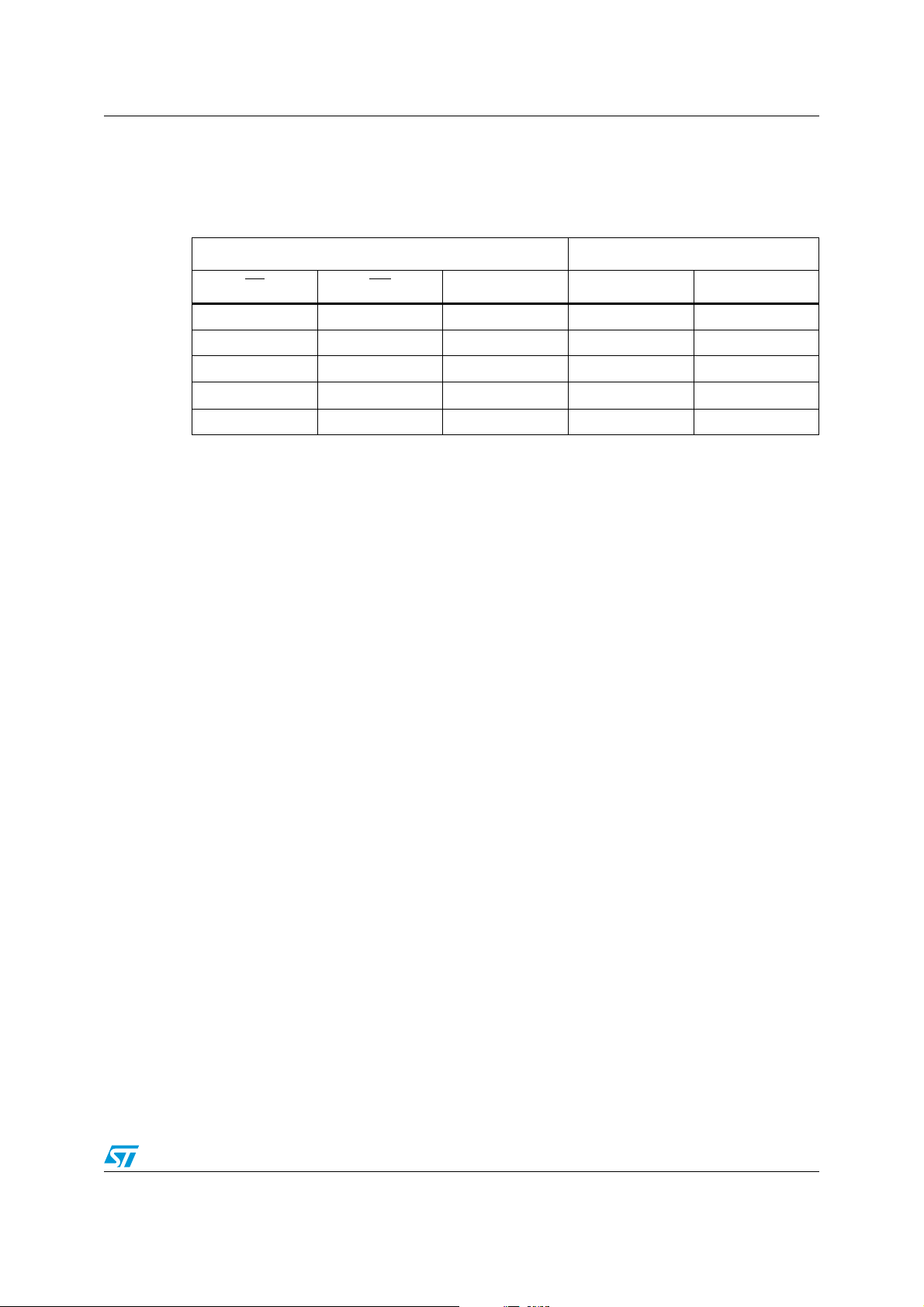

3 Truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4 Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.3 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

5 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

5.1 AC operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

5.2 DC operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6 Waveforms definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

7 Smart shutdown function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

8 Typical application diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

9 Bootstrap driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

9.1 CBOOT selection and charging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

10 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

11 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2/26 Doc ID 14493 Rev 7

L6390 Block diagram

UV

DETECTION

LEVEL

SHIFTER

BOOTSTRAP DRIVER

S

V

CC

LVG

DRIVER

HIN

LIN

HVG

DRIVER

HVG

BOOT

OUT

LVG

UV

DETECTION

OP+

OP-

GND

OPOUT

SD/OD

DT

OPAMP

DEAD

TIME

R

LOGIC

SHOOT

THROUGH

PREVENTION

SD

LATC H

FLOATING STRUCTURE

COMPARATOR

+

V

REF

CP+

1

2

11

14

15

16

7

5

8

3

4

10

9

6

SMART

SD

from LVG

VCC

VCC

5V

+

-

+

-

5V

1 Block diagram

Figure 1. Block diagram

Doc ID 14493 Rev 7 3/26

Pin connection L6390

T

2 Pin connection

Figure 2. Pin connection (top view)

LIN

SD/OD

HIN

VCC

DT

OP-

OPOUT

GND

1

2

3

4NC

5

6

7

8

16

15

14

13

11

10

BOO

HVG

OUT

NC12

LVG

CP+

OP+

9

Table 2. Pin description

Pin n # Pin name Type Function

1LIN I Low-side driver logic input (active low)

2SD

/OD

(1)

I/O

3 HIN I High-side driver logic input (active high)

4 VCC P Lower section supply voltage

5 DT I Deadtime setting

6 OP- I Op amp inverting input

7 OPOUT O Op amp output

Shutdown logic input (active low)/open drain

(comparator output)

8 GND P Ground

9 OP+ I Op amp non inverting input

10 CP+ I Comparator input

11 LVG

(1)

O Low-side driver output

12, 13 NC Not connected

14 OUT P High-side (floating) common voltage

15 HVG

(1)

O High-side driver output

16 BOOT P Bootstrap supply voltage

1. The circuit provides less than 1 V on the LVG and HVG pins (@ Isink = 10 mA), with VCC > 3 V. This allows

the omission of the “bleeder” resistor connected between the gate and the source of the external MOSFET

normally used to hold the pin low; the gate driver assures low impedance also in SD condition.

4/26 Doc ID 14493 Rev 7

L6390 Truth table

3 Truth table

Table 3 . Truth t able

Input Output

SD

LXXLL

HHL L L

HLHLL

HLLHL

HHHLH

Note: X: don't care.

LIN HIN LVG HVG

Doc ID 14493 Rev 7 5/26

Electrical data L6390

4 Electrical data

4.1 Absolute maximum ratings

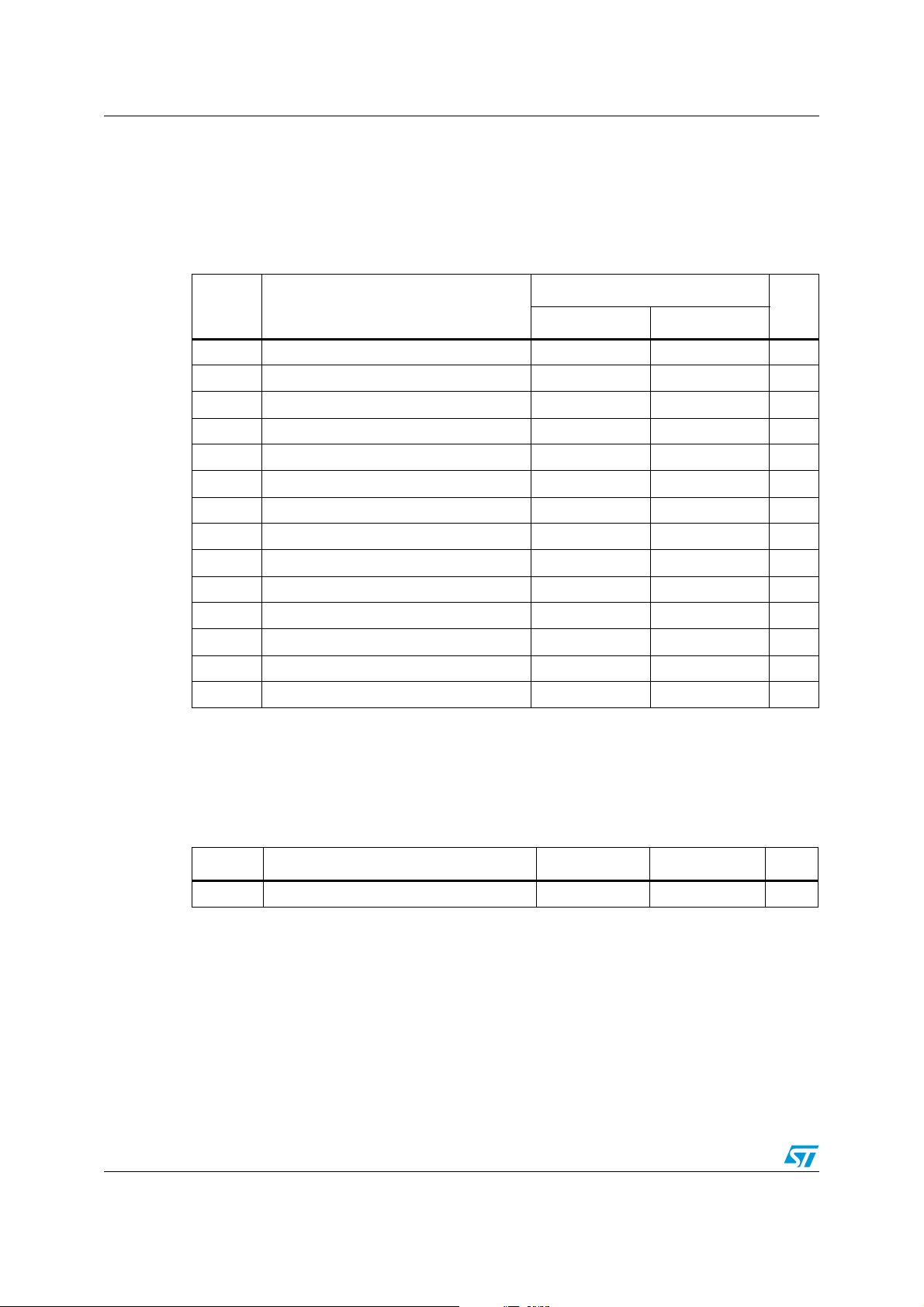

Table 4. Absolute maximum ratings

Value

Symbol Parameter

Min. Max.

Unit

dV

V

V

V

V

V

V

V

V

V

out

P

T

T

Supply voltage - 0.3 21 V

cc

Output voltage V

out

Bootstrap voltage - 0.3 620 V

boot

High-side gate output voltage V

hvg

Low-side gate output voltage - 0.3 Vcc + 0.3 V

lvg

Op amp non-inverting input - 0.3 Vcc + 0.3 V

op+

Op amp inverting input - 0.3 Vcc + 0.3 V

op-

Comparator input voltage - 0.3 Vcc + 0.3 V

cp+

V

Logic input voltage - 0.3 15 V

i

Open drain voltage - 0.3 15 V

od

- 21 V

boot

- 0.3 V

out

+ 0.3 V

boot

+ 0.3 V

boot

/dt Allowed output slew rate 50 V/ns

Total power dissipation (TA = 25 °C) 800 mW

tot

Junction temperature 150 °C

J

Storage temperature -50 150 °C

stg

Note: ESD immunity for pins 14, 15 and 16 is guaranteed up to 1 kV (human body model).

4.2 Thermal data

Table 5. Thermal data

Symbol Parameter SO-16 DIP-16 Unit

R

th(JA)

6/26 Doc ID 14493 Rev 7

Thermal resistance junction-to-ambient 155 100 °C/W

L6390 Electrical data

4.3 Recommended operating conditions

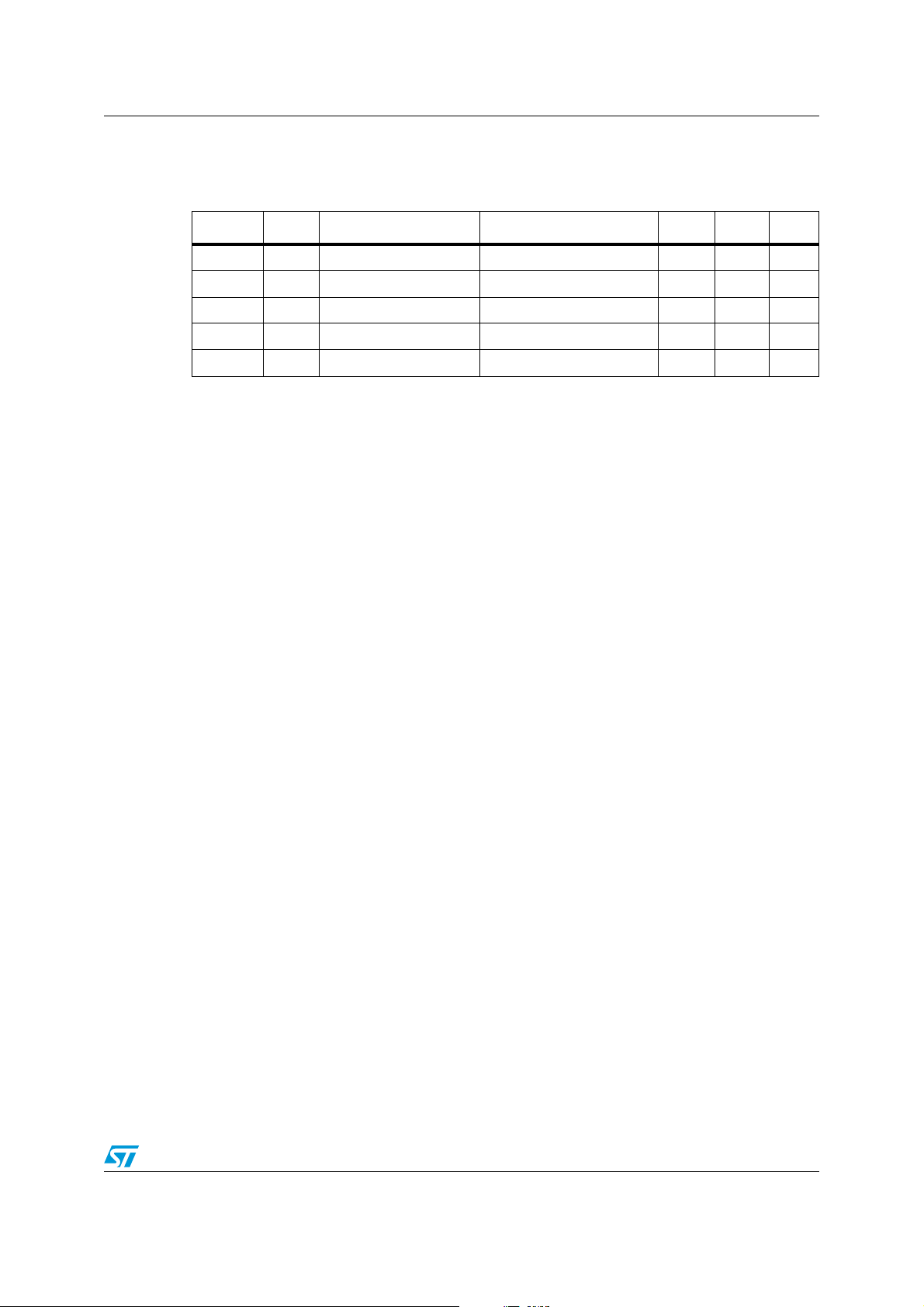

Table 6. Recommended operating conditions

Symbol Pin Parameter Test condition Min. Max. Unit

V

cc

(1)

V

BO

V

out

f

sw

T

J

1. VBO = V

2. LVG off. Vcc = 12.5 V. Logic is operational if V

4 Supply voltage 12.5 20 V

16-14 Floating supply voltage 12.4 20 V

14 DC output voltage - 9

Switching frequency HVG, LVG load CL = 1 nF 800 kHz

Junction temperature -40 125 °C

- V

out

.

boot

> 5 V. Refer to AN2738 for more details.

boot

(2)

580 V

Doc ID 14493 Rev 7 7/26

Electrical characteristics L6390

5 Electrical characteristics

5.1 AC operation

Table 7. AC operation electrical characteristics (VCC = 15 V; TJ = +25 °C)

Symbol Pin Parameter Test condition Min. Typ. Max. Unit

t

on

1 vs. 11

3 vs. 15

t

off

t

sd

t

isd

2 vs.

11, 15

MT

DT 5 Deadtime setting range

High/low-side driver turn-on

propagation delay

High/low-side driver turn-off

propagation delay

Shutdown to high/low-side

driver propagation delay

Comparator triggering to

high/low-side driver turn-off

propagation delay

Delay matching, HS and LS

turn-on/off

(1)

V

= 0 V

out

V

= V

boot

CL = 1 nF

cc

50 125 200 ns

50 125 200 ns

Vi = 0 to 3.3 V

See Figure 3.

Measured applying a voltage

step from 0 V to 3.3 V to pin CP+.

R

= 0, CL = 1 nF 0.1 0.18 0.25 μs

DT

R

= 37 kΩ, CL = 1 nF,

DT

CDT = 100 nF

R

= 136 kΩ, CL = 1 nF,

DT

CDT = 100 nF

R

= 260 kΩ, CL = 1 nF,

DT

CDT = 100 nF

50 125 200 ns

50 200 250 ns

0.48 0.6 0.72 μs

1.35 1.6 1.85 μs

2.6 3.0 3.4 μs

30 ns

MDT Matching deadtime

t

r

11, 15

t

f

1. See Figure 4 on page 9.

2. MDT = | DT

Rise time C

Fall time CL = 1 nF 35 70 ns

- DTHL | see Figure 5 on page 13.

LH

(2)

R

= 0, CL = 1 nF 80 ns

DT

R

= 37 kΩ, CL = 1 nF,

DT

C

= 100 nF

DT

= 136 kΩ, CL = 1 nF,

R

DT

C

= 100 nF

DT

R

= 260 kΩ, CL = 1 nF,

DT

C

= 100 nF

DT

= 1 nF 75 120 ns

L

120 ns

250 ns

400 ns

8/26 Doc ID 14493 Rev 7

L6390 Electrical characteristics

HIN

HVG

50%

10%

90%

50%

tr tf

ton

toff

90%

10%

LIN

LVG

50%

10%

90%

50%

tr tf

ton

toff

90%

10%

LVG/H VG

SD

90%

50%

tf

tsd

10%

Figure 3. Timing

Figure 4. Typical deadtime vs. DT resistor value

'7XV

$SSUR[LPDWHGIRUPXODIRU

5GWFDOFXODWLRQW\S

5GW>Nȍ@ Â'7>V@

Doc ID 14493 Rev 7 9/26

5GWN2KP

Electrical characteristics L6390

5.2 DC operation

Table 8. DC operation electrical characteristics (VCC = 15 V; TJ = + 25 °C)

Symbol Pin Parameter Test condition Min. Typ. Max. Unit

Low supply voltage section

V

cc_hys

V

cc_thON

V

cc_thOFF

Vcc UV hysteresis 1200 1500 1800 mV

Vcc UV turn-ON threshold 11.5 12 12.5 V

Vcc UV turn-OFF threshold 10 10.5 11 V

Vcc = 10 V

SD

= 5 V; LIN = 5 V;

HIN = GND;

RDT = 0 Ω;

90 120 150 μA

I

qccu

Undervoltage quiescent

supply current

4

CP+=OP+=GND; OP-=5 V

= 15 V

V

cc

SD

= 5 V; LIN = 5 V;

I

qcc

Quiescent current

HIN = GND;

300 720 1000 μA

RDT = 0 Ω;

CP+=OP+=GND; OP-=5 V

V

ref

Bootstrapped supply voltage section

Internal reference voltage 500 540 580 mV

(1)

V

BO_hys

V

BO_thON

V

BO_thOFF

I

QBOU

I

QBO

I

LK

R

DS(on)

V

V

V

BO

BO

BO

Undervoltage VBO

quiescent current

16

VBO quiescent current

High-voltage leakage

current

Bootstrap driver onresistance

Driving buffers section

I

so

I

si

High/low-side source shortcircuit current

11,

15

High/low-side sink shortcircuit current

UV hysteresis 1200 1500 1800 mV

UV turn-ON threshold 11.1 11.5 12.1 V

UV turn-OFF threshold 9.8 10 10.6 V

VBO = 9 V

SD = 5 V; LIN and

HIN = 5 V;

R

= 0 Ω;

DT

30 70 110 μA

CP+=OP+=GND; OP-=5 V

= 15 V

V

BO

SD

= 5 V; LIN and

HIN = 5 V;

R

= 0 Ω;

DT

30 150 210 μA

CP+=OP+=GND; OP-=5 V

= V

= V

= 600 V 10 μA

boot

< 10 μs) 200 290 mA

< 10 μs) 250 430 mA

(2)

V

hvg

out

LVG ON 120 Ω

V

= V

IN

ih (tp

= V

V

IN

il (tp

10/26 Doc ID 14493 Rev 7

L6390 Electrical characteristics

Table 8. DC operation electrical characteristics (VCC = 15 V; TJ = + 25 °C) (continued)

Symbol Pin Parameter Test condition Min. Typ. Max. Unit

Logic inputs

1. V

2. R

V

il

Low level logic threshold

voltage

1, 2, 3

V

V

il_S

I

HINh

ih

High level logic threshold

voltage

1, 3

Single input voltage

HIN logic “1” input bias

current

3

I

HINl

I

LINl

HIN logic “0” input bias

current

LIN logic “0” input bias

current

1

I

LINh

I

SDh

LIN logic “1” input bias

current

SD

current

2

I

SDl

BO = Vboot

DSON

where I

- V

is tested in the following way: R

is pin 16 current when V

1

SD logic “0” input bias

current

.

out

logic “1” input bias

DSON

= V

CBOOT

= [(VCC - V

CBOOT1, I2

0.8 1.1 V

1.9 2.25 V

LIN and HIN connected

together and floating

0.8 V

HIN = 15 V 110 175 260 μA

HIN = 0 V 1 μA

LIN = 0 V 3 6 20 μA

= 15 V 1 μA

LIN

= 15 V 10 40 100 μA

SD

SD

= 0 V 1 μA

CBOOT1

when V

) - (VCC - V

= V

CBOOT

CBOOT2

CBOOT2

)] / [I1(VCC,V

.

CBOOT1

) - I2(VCC,V

CBOOT2

)]

Doc ID 14493 Rev 7 11/26

Electrical characteristics L6390

(1)

Table 9. Op amp characteristics

Symbol Pin Parameter Test condition Min. Typ. Max. Unit

(VCC = 15 V, TJ = +25 °C)

V

io

I

io

I

ib

V

icm

V

OPOUT

I

o

SR Slew rate

GBWP Gain bandwidth product V

A

vd

SVR Supply voltage rejection ratio vs. V

CMRR

1. Operational amplifier is disabled when VCC is in UVLO condition.

2. The direction of input current is out of the IC.

Input offset voltage Vic = 0 V, Vo = 7.5 V 6 mV

Input offset current

V

= 0 V, Vo = 7.5 V

6, 9

Input bias current

(2)

ic

Input common mode voltage

range

Output voltage swing OPOUT = OP-; no load 0.07 V

7

Source, V

Output short-circuit current

Sink,V

id

Vi = 1 ÷ 4 V; CL = 100 pF;

unity gain

= 7.5 V 8 12 MHz

o

Large signal voltage gain RL = 2 kΩ 70 85 dB

CC

Common mode rejection

ratio

Table 10. Sense comparator characteristics

(1)

(VCC = 15 V, TJ = +25 °C)

440nA

100 200 nA

0V

= +1; Vo = 0 V 16 30 mA

id

= -1; Vo = V

CC

50 80 mA

-4 V

CC

-4 V

CC

2.5 3.8 V/μs

60 75 dB

55 70 dB

Symbol Pin Parameter Test condition Min. Typ. Max. Unit

I

ib

V

ol

t

d_comp

10 Input bias current V

Open drain low-level output

2

voltage

Comparator delay

SR 2 Slew rate C

1. Comparator is disabled when VCC is in UVLO condition.

= 1 V 1 μA

CP+

Iod = - 3 mA 0.5 V

/OD pulled to 5 V

SD

through 100 kΩ resistor

= 180 pF; Rpu = 5 kΩ 60 V/μs

L

90 130 ns

12/26 Doc ID 14493 Rev 7

L6390 Waveforms definition

G

6 Waveforms definition

Figure 5. Deadtime and interlocking waveforms definition

LIN

CONTROL SIGNAL EDGES

OVERLAPPED:

INTERLOCKING + DEAD TIME

CONTROL SIGNALS EDGES

SYNCHRONOUS (*):

DEAD TIME

CONTROL SIGNALS EDGES

NOT OVERLAPPED,

BUT INSIDE THE DEAD TIME:

DEAD TIME

HIN

LVG

HVG

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

LIN

HIN

LVG

HVG

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

LIN

HIN

LVG

HVG

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

INTERLOCKING

DTLH

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

DTLH DTHL

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

DTLH DTHL

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

INTERLOCKING

DTHL

CONTROL SIGNALS EDGES

NOT OVERLAPPED,

OUTSIDE THE DEAD TIME:

DIRECT DRIVING

LIN

HIN

LVG

HVG

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

DTLH

gate driver outputs OFF

(HALF-BRIDGE TRI-STATE)

(*) HIN and LIN can be connected togheter and driven by just one control signal

DTHL

Doc ID 14493 Rev 7 13/26

Smart shutdown function L6390

SD/OD

FROM/TO

CONTROLLER

V

BIAS

C

SD

R

SD

SMART

SD

LOGIC

RON_OD

SHUT DOWN CIRCUIT

RPD_SD

An approximation of the disable time is given by:

where:

HIN/LIN

HVG/LVG

open drain gate

(internal)

comp Vref

CP+

PROTECTION

Fast shut down

:

the driver outputs are set in SD state immediately after the comparator

triggering even if the SD signal has not yet reach the lower input threshold

disable time

SD/OD

AM12947v1

7 Smart shutdown function

The L6390 integrates a comparator committed to the fault sensing function. The comparator

has an internal voltage reference V

inverting input is available on pin 10. The comparator input can be connected to an external

shunt resistor in order to implement a simple overcurrent detection function. The output

signal of the comparator is fed to an integrated MOSFET with the open drain output

available on pin 2, shared with the SD input. When the comparator triggers, the device is set

in shutdown state and both its outputs are set to low level leaving the half-bridge in tri-state.

Figure 6. Smart shutdown timing waveforms

connected to the inverting input, while the non-

ref

14/26 Doc ID 14493 Rev 7

L6390 Smart shutdown function

In common overcurrent protection architectures the comparator output is usually connected

to the SD input and an RC network is connected to this SD/OD line in order to provide a

mono-stable circuit, which implements a protection time that follows the fault condition.

Differently from the common fault detection systems, the L6390 smart shutdown

architecture allows immediate turn-off of the outputs of the gate driver in the case of fault, by

minimizing the propagation delay between the fault detection event and the actual output

switch-off. In fact, the time delay between the fault detection and the output turn-off is no

longer dependent on the value of the external RC network connected to the SD/OD pin. In

the smart shutdown circuitry the fault signal has a preferential path which directly switches

off the outputs after the comparator triggering. At the same time the internal logic turns on

the open drain output and holds it on until the SD voltage goes below the SD logic input

lower threshold. When such threshold is reached, the open drain output is turned off,

allowing the external pull-up to recharge the capacitor. The driver outputs restart following

the input pins as soon as the voltage at the SD/OD pin reaches the higher threshold of the

SD logic input. The smart shutdown system provides the possibility to increase the time

constant of the external RC network (that determines the disable time after the fault event)

up to very large values without increasing the delay time of the protection.

Any external signal provided to the SD pin is not latched and can be used as control signal

in order to perform, for instance, PWM chopping through this pin. In fact when a PWM signal

is applied to the SD input and the logic inputs of the gate driver are stable, the outputs

switch from the low level to the state defined by the logic inputs and vice versa.

In some applications it may be useful to latch the driver in the shutdown condition for an

arbitrary time, until the controller decides to reset it to normal operation. This may, for

example, be achieved with a circuit similar to the one shown in Figure 7. When the open

drain starts pulling down the SD/OD pin, the external latch turns on and keeps the pin to

GND, preventing it from being pulled up again once the SD logic input lower threshold is

reached and the internal open drain turns off. One pin of the controller is used to release the

external latch, and one to externally force a shutdown condition and also to read the status

of the SD/OD pin.

Figure 7. Protection latching example circuit

L6390

AM12949v1

VBOOT

HVG

OUT

LVG

CP+

OP+

OP-

3.3 / 5 V

VDD

GND

µC

SD_reset

SD_force/sense

2.2 K

20 K

R3

R4

Ω

Ω

3.3 / 5 V

R1

20 K

R2

1.5 K

HIN

LIN

+

VCC

-

Ω

Ω

VCC

+

GND

DT

SD/OD

OPOUT

To other driver/devices

In applications using only one L6390 for the protection of several different legs (such as a

single-shunt inverter, for example) it may be useful to implement the resistor divider shown

in Figure 8. This simple network allows the pushing of the SD pins of the other devices to a

voltage lower than L6390 V

, so that each device can reach its low logic level regardless of

il

part-to-part variations of the thresholds.

Doc ID 14493 Rev 7 15/26

Smart shutdown function L6390

SD_sense

SD_force

GND

VDD

µC

VDD

VCC

R1

9*R

R3

2*R

HVG

OUT

LVG

VBOOT

OP+

OP-

OPOUT

DT

CP+

L6390

SD/OD

GND

VCC

HIN

LIN

+

+

-

VCC

HV BUS

L639x

L639x

SD/OD

SD/OD

C2

C3

C1

C2, C3: small noise filtering capacitors

C1: disable time setting capacitor

R2

R

AM12948v1

Figure 8. SD level shifting example circuit

16/26 Doc ID 14493 Rev 7

L6390 Typical application diagram

8 Typical application diagram

Figure 9. Application diagram

+

V

CC

FROM CONTROLLER

VCC

HIN

4

3

UV

DETECTION

BOOTSTRAP DRIVER

from LVG

FLOATING STRUCTURE

UV

DETECTION

LEVEL

SHIFTER

S

R

HVG

DRIVER

16

BOOT

H.V.

Cboot

HVG

15

FROM CONTROLLER

FROM/TO

CONTROLLER

TO ADC

SMART

SD

LOGIC

SHOOT

THROUGH

PREVENTION

SD

LATCH

DEAD

TIME

COMPARATOR

OPAMP

VCC

14

OUT

V

CC

LVG

DRIVER

LVG

11

5V

+

-

+

-

10

CP+

+

V

REF

V

BIAS

9

OP+

OP-

6

TO LOAD

5V

LIN

V

1

BIAS

SD/OD

2

8

GND

DT

5

OPOUT

7

Doc ID 14493 Rev 7 17/26

Bootstrap driver L6390

C

EXT

Q

gate

V

gate

--------------- -=

V

dropIch eargRdsonVdrop

→

Q

gate

T

ch earg

---------------------

R

dson

==

9 Bootstrap driver

A bootstrap circuitry is needed to supply the high-voltage section. This function is normally

accomplished by a high-voltage fast recovery diode (Figure 10.a). In the L6390 a patented

integrated structure replaces the external diode. It is realized by a high-voltage DMOS,

driven synchronously with the low-side driver (LVG), with diode in series, as shown in

Figure 10.b. An internal charge pump (Figure 10.b) provides the DMOS driving voltage.

9.1 C

To choose the proper C

capacitor. This capacitor C

Equation 1

The ratio between the capacitors C

It must be:

Equation 2

E.g.: if Q

300 mV.

If HVG must be supplied for a long time, the C

quiescent losses into account.

E.g.: HVG steady-state consumption is lower than 150 μA, so if HVG T

must supply 0.75 μC to C

V.

BOOT

selection and charging

value the external MOS can be seen as an equivalent

BOOT

is related to the MOS total gate charge:

EXT

and C

EXT

C

BOOT

is 30 nC and V

gate

is 10 V, C

gate

. This charge on a 1 μF capacitor means a voltage drop of 0.75

EXT

EXT

is proportional to the cyclical voltage loss.

BOOT

>>> C

EXT

is 3 nF. With C

selection must also take the leakage and

BOOT

= 100 nF the drop would be

BOOT

is 5 ms, C

ON

BOOT

18/26 Doc ID 14493 Rev 7

The internal bootstrap driver offers important advantages: the external fast recovery diode

can be avoided (it usually has a high leakage current).

This structure can work only if V

LVG is on. The charging time (T

is close to GND (or lower) and, at the same time, the

OUT

charge

) of the C

is the time in which both conditions are

BOOT

fulfilled and it must be long enough to charge the capacitor.

The bootstrap driver introduces a voltage drop due to the DMOS R

(typical value: 120

DSon

Ω). This drop can be neglected at low switching frequency, but it should be taken into

account when operating at high switching frequency.

The following equation is useful to compute the drop on the bootstrap DMOS:

Equation 3

L6390 Bootstrap driver

V

drop

30nC

5μs

-------------- -

120Ω 0.7V∼⋅=

TO LOAD

D99IN1067

H.V.

HVG

ab

LVG

HVG

LVG

C

BOOT

TO LOAD

H.V.

C

BOOT

D

BOOT

BOOT

V

CC

V

CC

OUT

OUT

BOOT

where Q

the bootstrap DMOS and T

is the gate charge of the external Power MOSFET, R

gate

is the charging time of the bootstrap capacitor.

charge

is the on-resistance of

dson

For example: using a Power MOSFET with a total gate charge of 30 nC, the drop on the

bootstrap DMOS is about 1 V, if the T

is 5 μs. In fact:

charge

Equation 4

V

should be taken into account when the voltage drop on C

drop

is calculated: if this drop

BOOT

is too high, or the circuit topology doesn’t allow a sufficient charging time, an external diode

can be used.

Figure 10. Bootstrap driver

Doc ID 14493 Rev 7 19/26

Package mechanical data L6390

10 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of

®

ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

Table 11. DIP-16 mechanical data

mm

Dim.

Min. Typ. Max.

a1 0.51

B0.77 1.65

b 0.5

b1 0.25

D 20

E 8.5

e 2.54

e3 17.78

F 7.1

I 5.1

L 3.3

Z 1.27

20/26 Doc ID 14493 Rev 7

L6390 Package mechanical data

0#

Figure 11. DIP-16 package dimensions

Doc ID 14493 Rev 7 21/26

Package mechanical data L6390

Table 12. SO-16 narrow mechanical data

mm

Dim.

Min. Typ. Max.

A 1.75

A1 0.10 0.25

A2 1.25

b0.31 0.51

c0.17 0.25

D 9.80 9.90 10.00

E5.806.006.20

E1 3.80 3.90 4.00

e1.27

h0.25 0.50

L0.40 1.27

k0 8°

ccc 0.10

22/26 Doc ID 14493 Rev 7

L6390 Package mechanical data

0016020_F

Figure 12. SO-16 narrow package dimensions

Doc ID 14493 Rev 7 23/26

Package mechanical data L6390

Figure 13. SO-16 narrow footprint

24/26 Doc ID 14493 Rev 7

L6390 Revision history

11 Revision history

Table 13. Document revision history

Date Revision Changes

29-Feb-2008 1 First release

09-Jul-2008 2

17-Sep-2008 3 Updated test condition values on Table 8 and Tab le 9

17-Feb-2009 4

11-Aug-2010 5

10-Jul-2012 6

Updated: Cover page, Table 2 on page 4, Table 3 on page 5,

Section 4 on page 6, Section 5 on page 8, Section 9.1 on page 18

Updated Table 7 on page 8, Table 8 on page 10, Table 9 on page 12

Added Table 4 on page 6

Updated Table 1 on page 1, Table 7 on page 8, Table 9 on page 12,

Table 10 on page 12

Ta bl e 7 changed test conditions of DT and MDT values.

Ta bl e 8 added minimum values to I

Ta bl e 8 changed V

values.

Ta bl e 9 and Ta bl e 1 0 added footnote to the title of the tables.

Changed HVG values on page 17.

Updated SO-16 narrow mechanical data.

Changed Section 7 and added Figure 7 and Figure 8.

BO_thON

and V

qccu-Iqcc-IQBOU

BO_thOFF

- I

QBO.

minimum and maximum

25-Jul-2012 7

Content reworked in Section 9: Bootstrap driver to improve

readability, no technical changes.

Doc ID 14493 Rev 7 25/26

L6390

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2012 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

26/26 Doc ID 14493 Rev 7

Loading...

Loading...