ST L4962 User Manual

®

1.5A POWER SWITCHING REGULATOR

1.5A OUTPUT CURRENT

5.1V TO 40V OUTPUT VOLTAG E RANG E

PRECISE (± 2%) ON-CHIP REFERENCE

HIGH SWITCHING FREQUENCY

VERY HIGH EFFICIENCY (UP TO 90%)

VERY FEW EXTERNAL COMPONENTS

SOFT START

INTERNAL LIMITING CURRENT

THERMAL SHUTDOWN

DESCRIPTION

The L4962 is a monolithic power switching regulator delivering 1.5A at a voltage variable from 5V to

40V in step down configuration.

Features of the device include current limiting, soft

start, thermal protection and 0 to 100% duty cycle

for continuous operating mode.

L4962

POWERDIP

(12 + 2 + 2)

ORDERING NUMBERS

: L4962/A (1 2 + 2 + 2 P ower di p)

L4962E/A (Heptawatt

Vertical)

L4962EH/A (Horizontal

Heptawatt)

The L4962 is mounted in a 16-lead Powerdip plastic

package and Heptawatt package and requires very

few external components.

Efficient operation at switching frequencies up to

150KHz allows a reduction in the size and cost of

external filter components.

HEPTAWATT

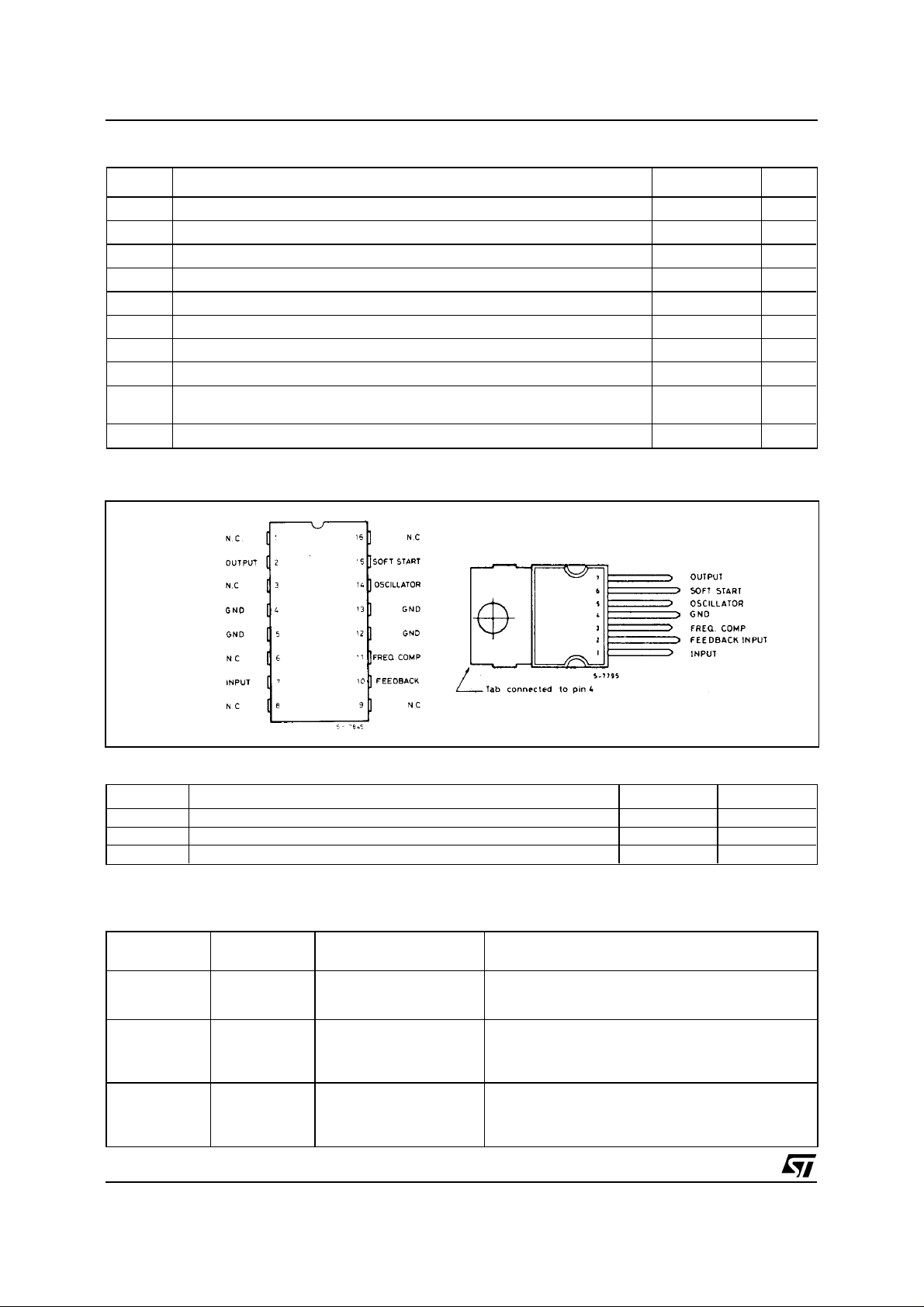

BLOCK DIAGRAM

June 2000

Pin X = Powerdip

Pin (X) = Heptawatt

1/16

L4962

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Val ue Unit

V

Input voltage 50 V

7

V7 - V2Input to output voltage difference 50 V

V

Negative output DC voltage -1 V

2

Output peak voltage at t = 0.1µs; f = 100KHz -5 V

V11, V15Voltage at pin 11, 15 5.5 V

V

I

I

P

, T

T

j

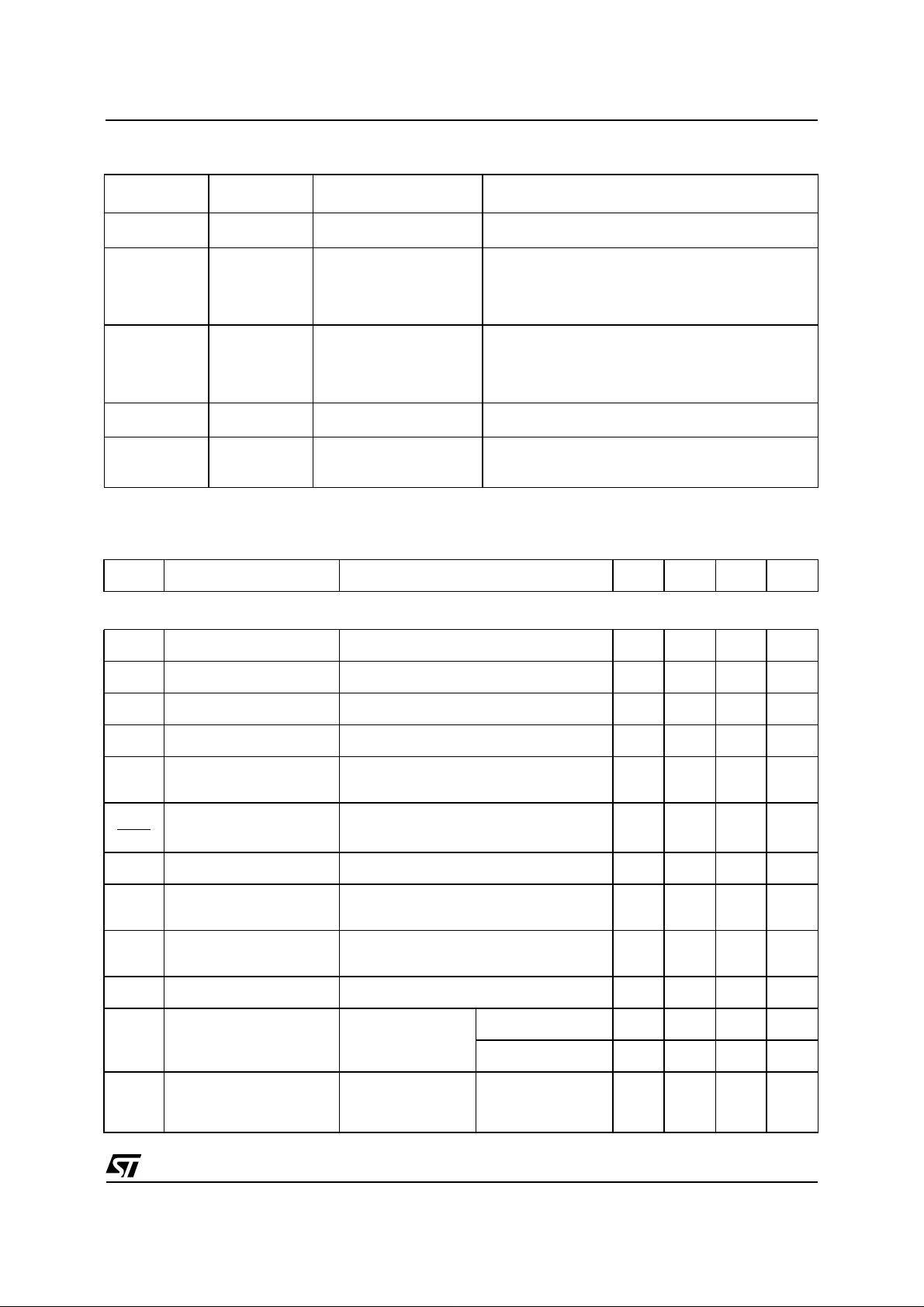

PIN CONNECTION

Voltage at pin 10 7 V

10

Pin 11 sink current 1 mA

11

Pin 14 source current 20 mA

14

Power dissipation at T

tot

T

Junction and storage temperature -40 to 150

stg

≤ 90°C (Powerdip)

pins

≤ 90°C (Heptawatt)

case

(Top view)

4.3

15

W

W

C

°

THERMAL DATA

Symbol Parameter Heptawatt Powerdip

R

th j-case

R

th j-pins

R

th j-amb

* Obtained with the GND pins soldered to printed circuit with minimized copper area.

Thermal resistance junction-case max 4°C/W Thermal resistance junction-pins max - 14°C/W

Thermal resistance junction-ambient max 50°C/W 80°C/W*

PIN FUNCTIONS

HEPTAWATT POWERDIP NAME

1 7 SUPPL Y VOLTAGE Unregulated voltage input. An in ternal re gulator po wers

the internal logic.

2 10 FEEDBACK INPUT The feedback terminal of the regulation loop. The output

is connected directly to this terminal for 5.1V operation;

it is connected via a divider for higher voltages.

3 11 FREQUENCY

COMPENSATION

A series R C network connected between this terminal

and ground determines the regulation loop gain

characteristics.

2/16

FUNCTION

L4962

PIN FUNCTIONS

HEPTAWATT POWERDIP NAME

(cont’d)

FUNCTION

4 4, 5, 12, 13 GROUND Common ground terminal.

5 14 OSCILLATOR A parallel RC network connected to this terminal

determines the switching frequency. This pin must be

connected to pin 7 input when the internal oscillator is

used.

6 15 SOFT STAR T Soft start time constant. A capacitor is connected

between this terminal and ground to define the soft start

time constant. This capacitor also determines the

average short circuit output current.

7 2 OUTPUT Regulator output.

1, 3, 6,

N.C.

8, 9, 16

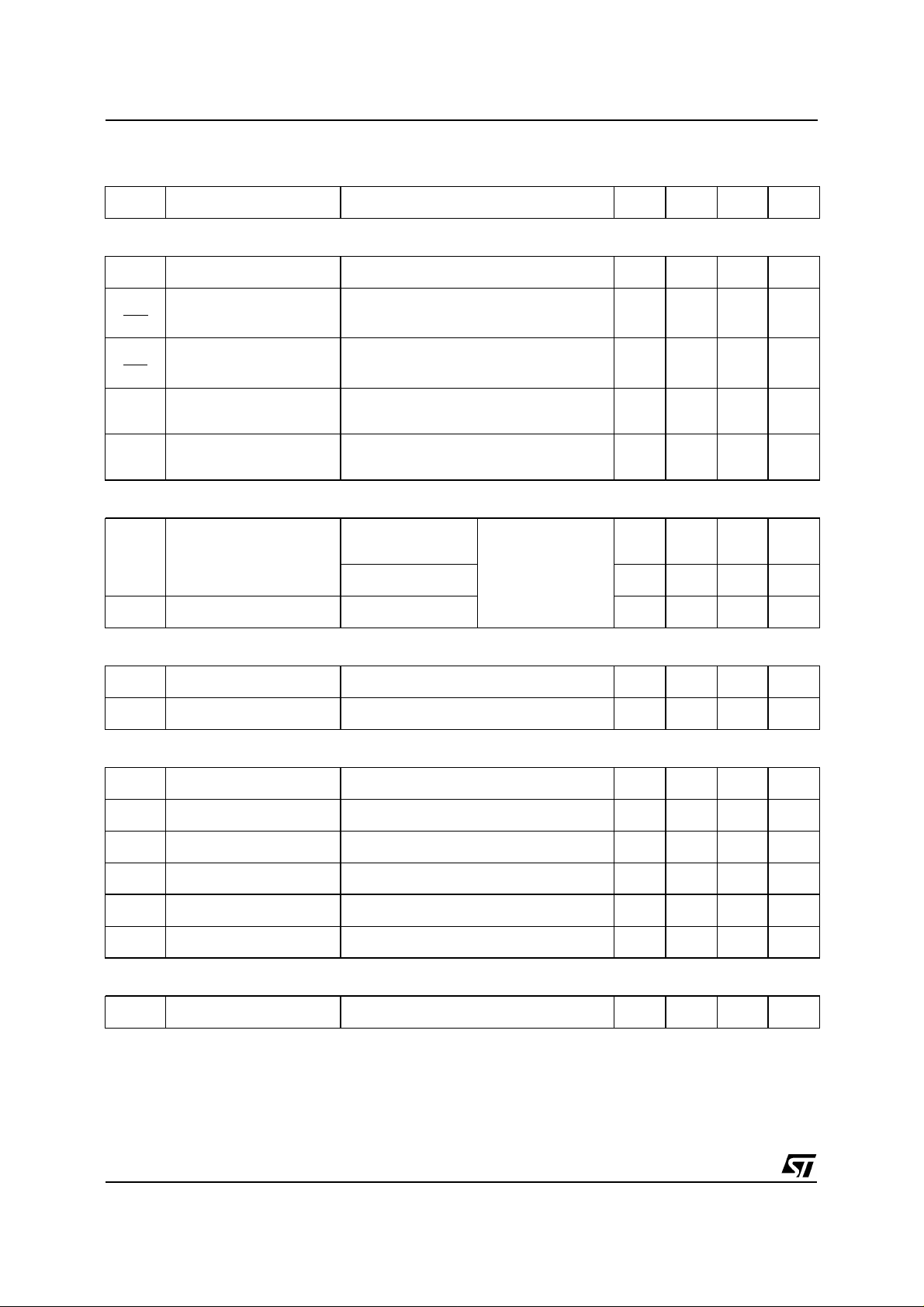

ELECTRICAL CHARACTERISTICS

(Refer to the test circuit, T

= 25 °C, Vi = 35V, unless otherwise

j

specified)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

DYNAMIC CHARACTERISTICS

V

Output voltage range Vi = 46V Io = 1A V

o

Input voltage range Vo = V

V

i

Line regulation Vi = 10V to 40V Vo = V

V

∆

o

Load regulation Vo = V

V

∆

o

V

∆

∆

I

I

I

V

V

I

Internal reference voltage

ref

Vi = 9V to 46V Io = 1A 5 5.1 5.2 V

(pin 10)

ref

Average temperature

coefficient of refer. voltage

T

Dropout voltage Io = 1.5A 1.5 2 V

d

Maximum operating load

om

current

Current limiting threshold

2L

(pin 2)

Input average current Vi = 46V; output short-circuit 15 30 mA

SH

Efficiency f = 100KHz V

η

Tj = 0°C to 125°C

= 1A

I

o

Vi = 9V to 46V

= V

V

o

Vi = 9V to 46V

= V

V

o

= 1A Vo = 12V 80 %

o

ref

to 36V Io = 1.5A 9 46 V

ref

Io = 1A 15 50 mV

ref

ref

Io = 0.5A to 1.5A 8 20 mV

1.5

to 36V

ref

to 36V

ref

= V

o

ref

2

70 %

40 V

0.4

3.3 A

mV/°C

A

SVR Supply voltage ripple

rejection

V

∆

fripple

V

o

= V

= 2V

i

rms

= 100Hz

ref

Io = 1A

50 56

dB

3/16

L4962

ELECTRICAL CHARACTERISTICS

(continued)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

DYNAMIC CHARACTE RISTICS

(cont’d)

f Switching frequency 85 100 115 KHz

f

∆

Voltage stability of

switching frequency

V

∆

i

f

∆

Temperature stability of

switching frequency

T

∆

j

f

Maximum operating

max

Vi = 9V to 46V 0.5 %

Tj = 0°C to 125°C1%

Vo = V

ref

Io = 1A 120 150 KHz

switching frequency

T

Thermal shutdown

sd

150

junction temperature

DC CHARACTERISTICS

I

Quiescent drain current 100% duty cycle

7Q

pins 2 and 14 open

V

= 46V

i

0% duty cycle 15 20 mA

30 40 mA

C

°

-I

Output leakage current 0% duty cycle 1 mA

2L

SOFT START

I

15SO

I

Source current 100 140 180

Sink current 50 70 120

15SI

ERROR AMPLIFIER

V

V

I

-I

High level output voltage V10 = 4.7V I11 = 100µA 3.5 V

11H

Low level output voltage V10 = 5.3V I11 = 100µA 0.5V

11L

Sink output current V10 = 5.3V 100 150

11SI

Source output current V

11SO

I

Input bias current V10 = 5.2V 2 10

10

DC open loop gain V11 = 1V to 3V 46 55 dB

G

v

OSCILLATOR

-I

Oscillator source current 5 mA

14

= 4.7V 100 150

10

A

µ

A

µ

A

µ

A

µ

A

µ

4/16

L4962

CIRCUIT OPERA TION

(refer to the block diagram)

The L4962 is a monolithic stepdown switching regulator providing output voltages from 5.1V to 40V and

delivering 1.5A.

The regulation loop consists of a sawtooth oscillator, error amplifier, comparator and the output

stage. An error signal is produced by comparing the

output voltage with a precise 5.1V on-chip r eference (zener zap trimmed to ± 2%).

This error signal is then compared with the sawtooth

signal to generate the fixed frequency pulse width

modulated pulses which drive the output stage.

The gain and frequency stability of the loop can be

adjusted by an external RC network connected to

pin 11. Closing the loop directly gives an output

voltage of 5.1V. Higher voltages are obtained by

inserting a voltage divider.

Output overcurrents at switch on are prevented by

the soft start function. The error amplifier output is

initially clamped by the ext ernal capacit or C

ss

and

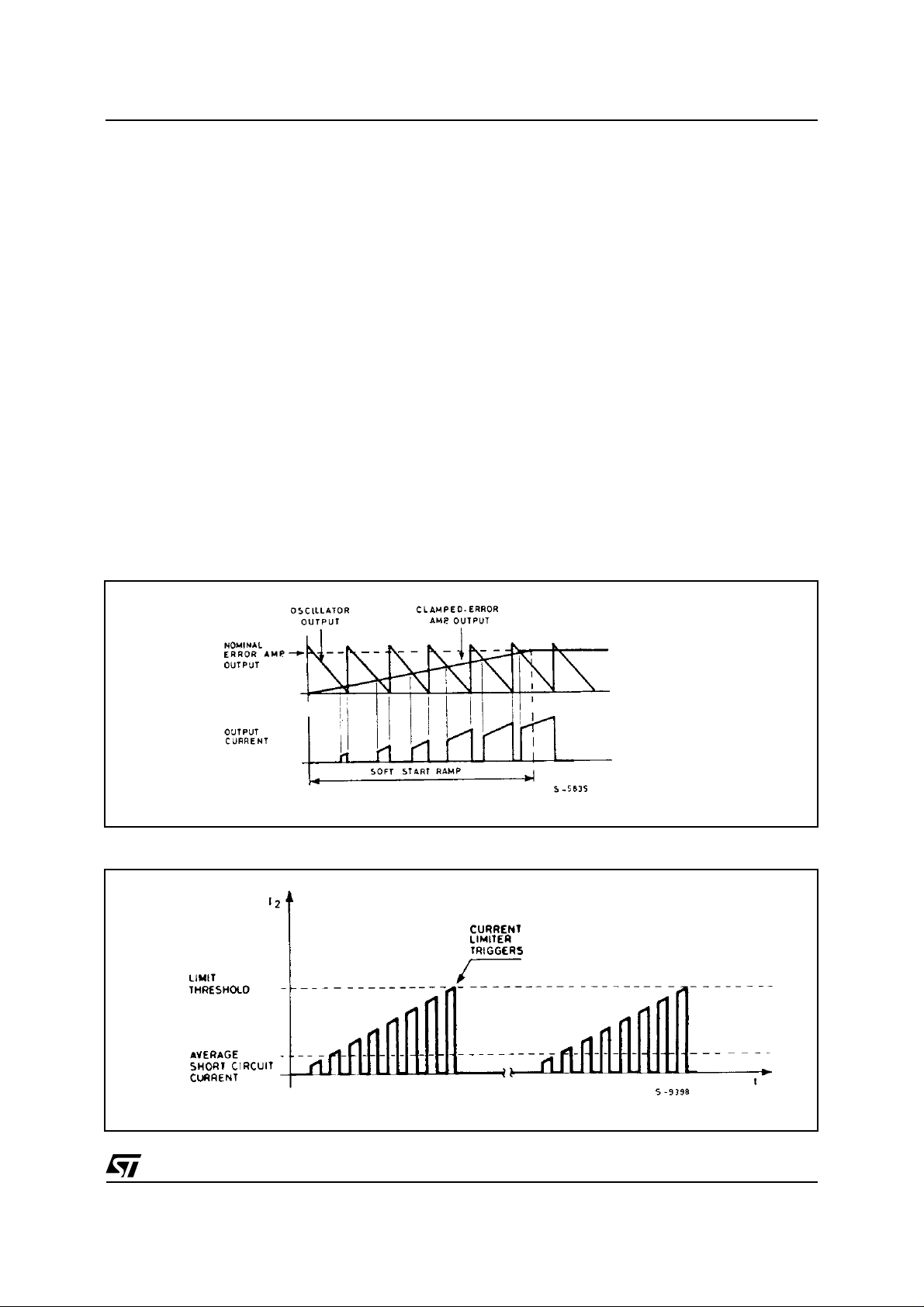

Figure 1. Soft start waveforms

allowed to rise, linearly, as this capacitor is charged

by a constant current source. Output overload protection is provided in the form of a current limiter.

The load current is sensed by an internal metal

resistor connected to a comparator. When the load

current exceeds a preset threshold this comparator

sets a flip flop which disables the output stage and

discharges the soft start capacitor. A second comparator resets the flip flop when the voltage across

the soft start capacitor has fallen to 0.4V.

The output stage is thus re-enabled and the out put

voltage rises under control of the soft start network.

If the overload condition is still present the limiter

will trigger again when the threshold current is

reached. The average short circuit current is lim ited

to a safe value by the dead time introduced by the

soft start network. The thermal overload circuit disables circuit operation when the junction temperature reaches about 150°C and has hysteresis to

prevent unstable conditions.

Figure 2. Current limiter waveforms

5/16

Loading...

Loading...