Sony svf14n Schematics

A

www.Vinafix.vn

Page

Title of schematic page Rev. Date

01

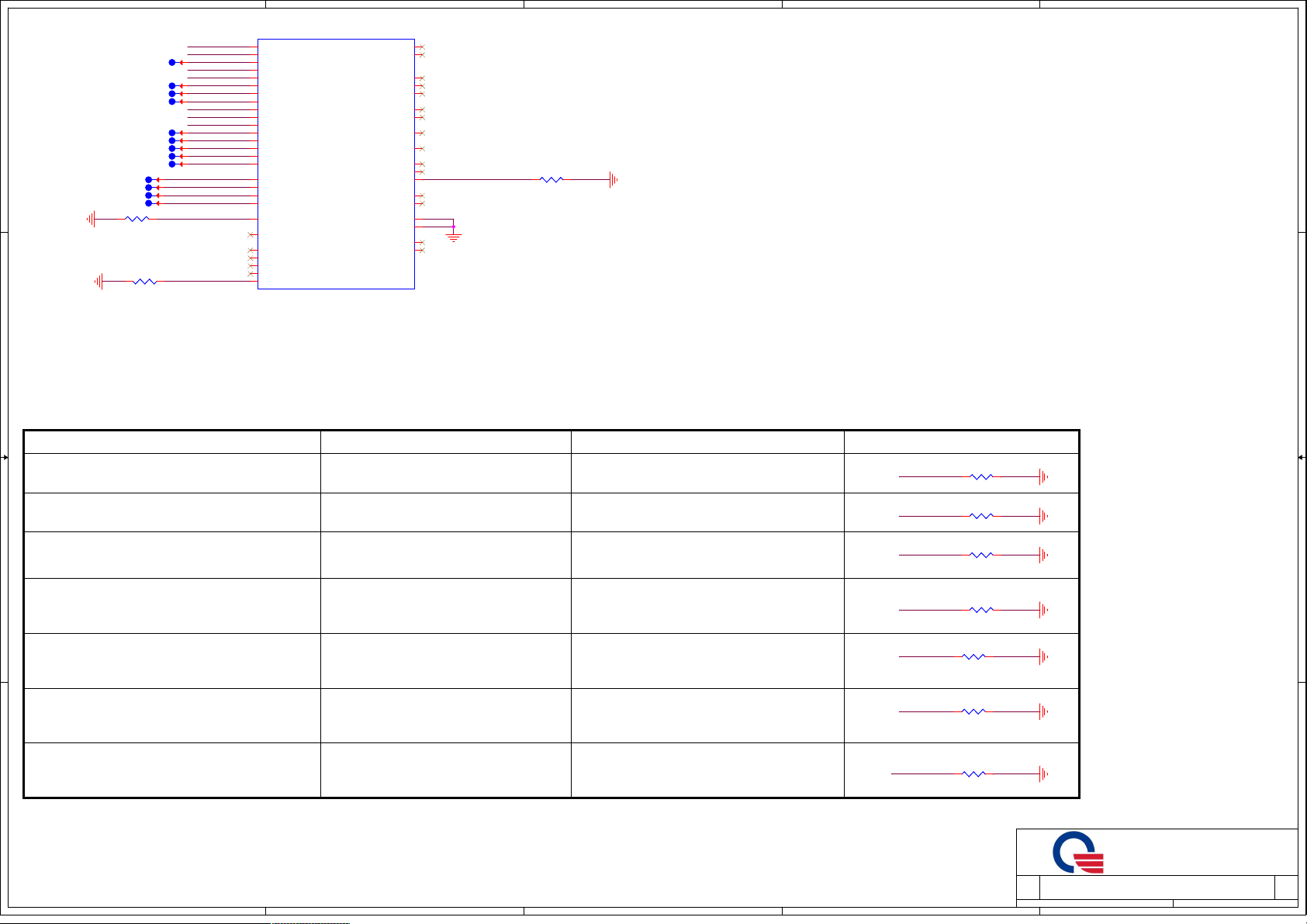

Page List

02

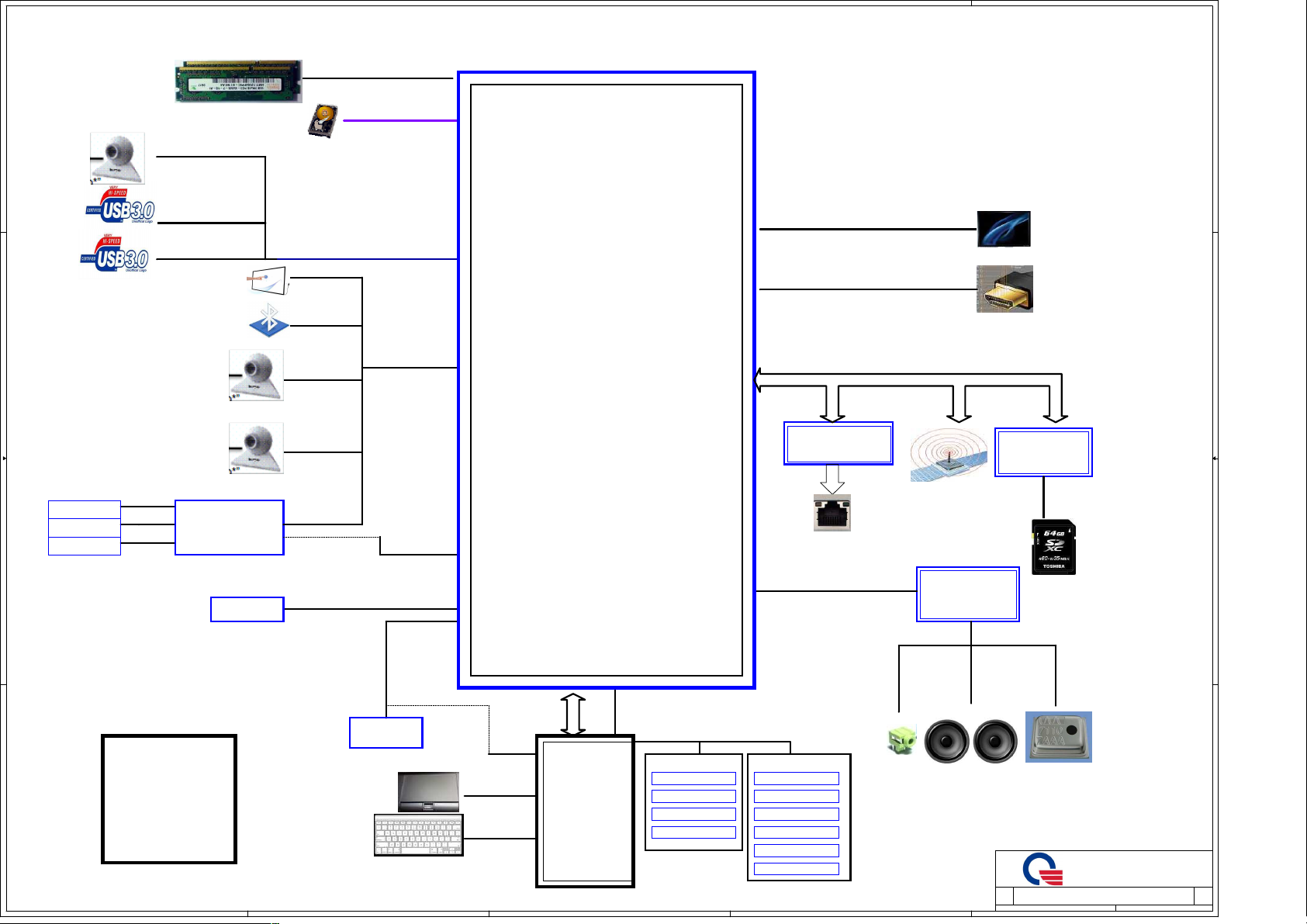

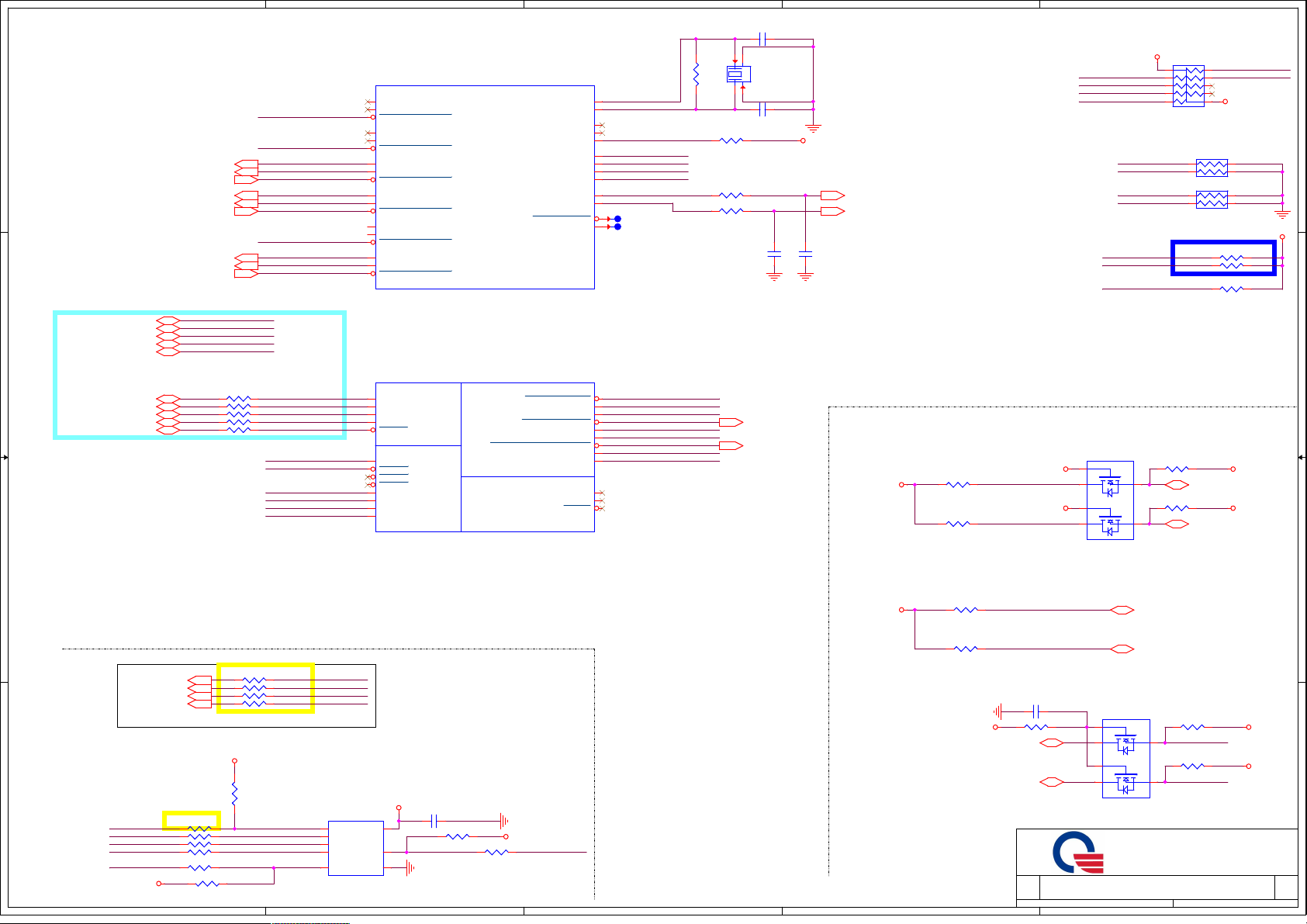

Block Diagram

03

Change List

04

4 4

3 3

2 2

HSW MCP(DISPLAY/Sideband)

05

HSW MCP(MEMORY/GND)

06

HSW MCP(CFG/PwrMGT)

HSW MCP(POWER)

07

08

HSW PCH(RTC/HDA/SATA)

09

HSW PCH(PCIE/USB)

10

HSW PCH(CLK/LPC/SPI/SMB)

11

HSW PCH(GPIO/LPIO/MISC)

12

HSW PCH(POWER)

13

DDR3L DIMM1-STD 4H (CH-A)

14

HOLE/EMI/KB

15

WPCE985L & FLASH

16

LVDS\TS\NFC

17

HDD/Gsensor/TP/FAN

18

HDMI/THERMAL

19

USB Charger/IO connector

20

WLAN/KB-BL

21

LED

22

Sensors Hub & Sensors

23

POWER +VCC_CORE (NCP81101)

24

POWER 3VPCU&RVCC5(TPS51427)

25

POWER 1.35VSUS/VTT_MEM

26

POWER +1.05V(G5602R41U)

27

POWER VCC1.5/Thermal

28

POWER(BAT IN / ADA IN/ UL)

29

POWER CHARGER (ISL88732)

30

IO PORT LIST

31

SMBUS

32

Power Table

Power Sequence

33

B

C

D

E

Page Title of schematic page Rev. Date

1

1A

1A

1A

1A

1A

1A

1A

* : No mount

L@ : For LVDS output

D@ : For eDP output

E@ : For DIS GFX

I@ : For UMA

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1A

1 1

A

B

C

D

E

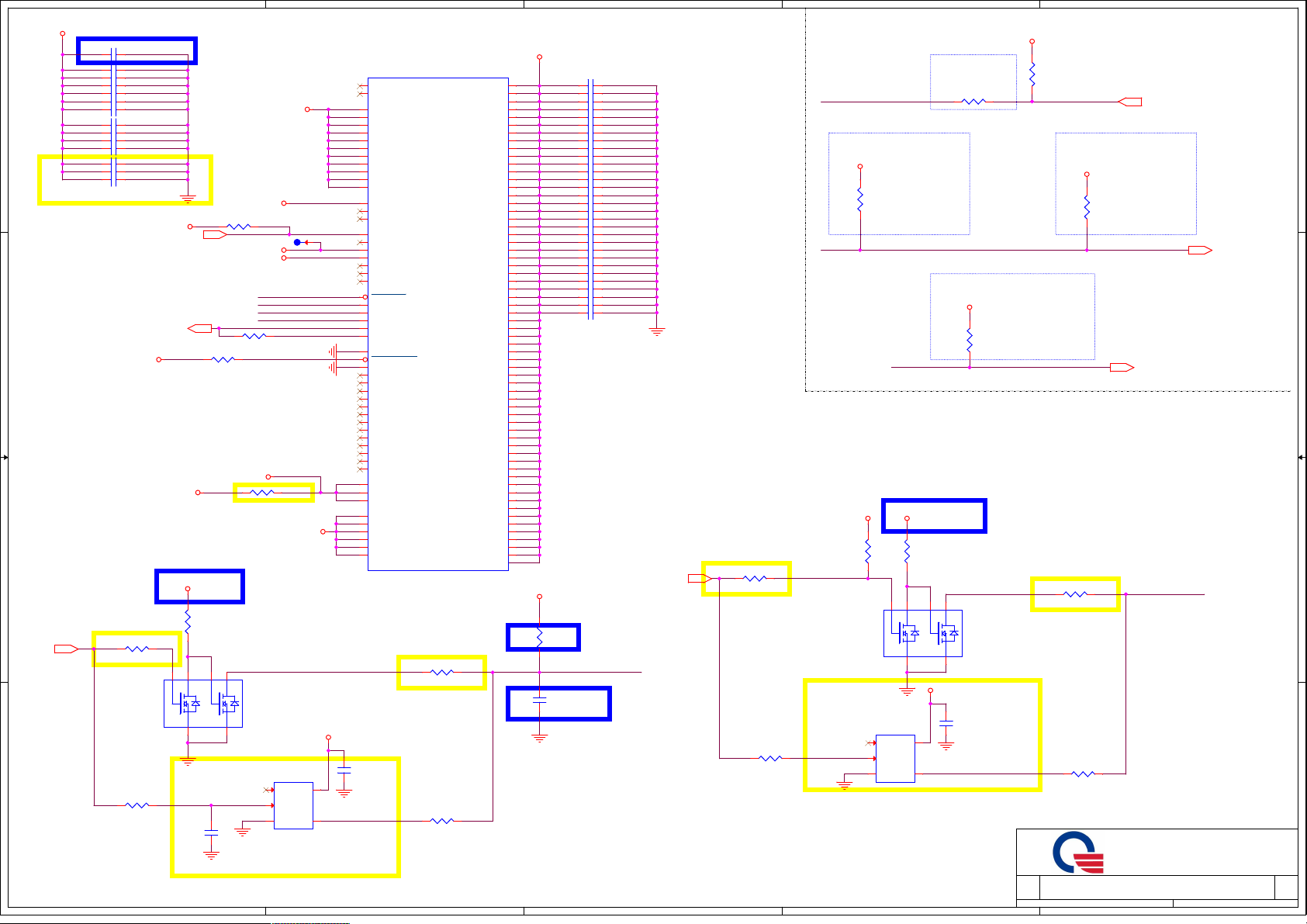

FI2 BLOCK

www.Vinafix.vn

DIAGRAM

5

4

3

2

1

02

Memory(Channel A)

DDR3L-1600

CH-A SO-DIMM

D D

Rear CAMERA

USB3.0 PORT4

HDD SATA0

6Gb/s

PCI-E

X4

Intel Shark Bay

USB3.0 PORT2

USB3.0 PORT1

PORT4

PORT3

C C

Light Sensor

CM3218

A+M Sensor

LSM303DLHCTR

Gyro Sensor

L3GD20TR

B B

I2C

I2C

I2C

Sensor HUB

STM32F103CBU6TRC44

BT

PORT7

Front CAMERA

PORT3

Rear CAMERA

PORT6

NFC

USB 3.0

USB 2.0

I2C

SMBUS

SPI

Haswell ULT

+

Lynx

Point-LP

BGA1168

(40mm X 24mm)

eDP 14"eDP

HDMI

2.5GT/s

PCIE4

(1920x1080)

PCI-Express Gen1

Giga-LAN

RTL8111GUS

RJ45

HD-AUDIO

PCIE3

WLAN/BT

P20

Audio CODEC

ALC233-CG

PCIE6

Card Reader

RTS5227E

SD-XC

SPK

PCB STACK UP 6L

LAYER 1 : TOP

SPI ROM

8MB

SPI

LPC

LAYER 2 : SVCC

A A

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : SGND

LAYER 6 : BOT

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green

Partners.

5

4

Touch Pad

P17

Keyboard

P20

EC

NPCE985L

PECI

LEDs

Power/Sleep LED

HDD Status LED

Caps Lock LED

3

Buttons

Power

AssitCharger LED

Volume Up

Volume Down

Windows

Battery Detach

Combo Jack

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

DMIC

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

FI2

FI2

FI2

233

233

1

233

1A

1A

1A

5

www.Vinafix.vn

Change List

EVT->DVT

PAGE04 :<1>, EC_A20GATE change to R_CAM_ON

<2>, R_CAM_ON change to GPIO78

<3>, Change the netname of GPIO77 from EC_EXT_SMI# to GPIO77

<4>, R271, R272, R273, R274, R275, R276, R277 ,R14,R15 change to 100K from 10K for power saving.

PAGE07 :<1>, R42 change to 100K from 10K for power saving.

<2>, SCH add U34/U35 to colay VCCST_PWRGD&IMVP_PWRGD

<3>, R41/R44 change +3V_S5 from +3V for timing issue

<4>, C49 add 680PF for timing issue

<5>, +1.35V_SUS add a C2376( 3.3pF ) capacitance to GND for RF solution

PAGE08 :<1>, RTC CNN change to DFHD02MS107

<2>, Y1 change to BG332768224

<3>, Change the netname of GPIO35 from GPIO35 to EC_EXT_SMI#

<4>, R278, R279, R280, R281 change to 100K from 10K for power saving.

PAGE09: <1>, USB3 support rear CAM solution

<2>, CAM-Front change port7 from port5 from sony request

<3>, Sensor hub change port6 from port4 from sony request

<4>, BT change port5 from port3 from sony request

<5>, Touch change port4 from port2 from sony request

<6>, Rear CAM change to port3 from port2 from Sony request

<7>, PCH GPIO29 use for WLAN_PW_EN

<8>, R73, R282 change to 100K from 10K for power saving.

<9>, SLP_A add test point for ME compliancy test

<10>, SCH un-mount R282

<11>, SCH add R24520 for PCI_PLTRST#

PAGE10: <1>, Remove RP4 , Add R24465 10 K ohm for CCD_PWR_EN without mount , add R24466 10K ohm for GPIO11 with mount .

<2>, R24456 change to 100K from 10K for power saving.

D D

PAGE11 :<1>, PCH GPIO27 add SIO_WAKE_GPIO27#

<2>, PCH GPIO08 change to LAN_RST#

<3>, PCH GPIO24 add PCH_LAN_WAKE#

<4>, PCH GPIO12 add LAN_ISOLATE#

<5>, Change R293,R304,R310,R308,R297,R306 from mount to un-mount

<6>, Change R118 from NC to mount

<7>, Change HDD_PW_EN from GPIO90 to GPIO13

<8>, Change R302 from 10k ohm pull high to 100k ohm pull down

<9>, Add R24462 100K pull down for CR_PW_EN

<10>, PCH GPIO16 add DB_DET#

<11>, R283, R285, R292, R295, R300, R315, R313, R317, R311, R289, R296, R298, R299, R301, R303, R305, R307, R309, R312,R314, R318, R319, R320, R290, R291, R294, R284, R112, R288, R115, R287,

R116, R117, R118, R119, R286, R122, , R114

, R126, R127, R130,R132, R134 change to 100K from 10K for power saving.

<12>, SCH mount R310

<13>, SCH no-mount R288 for NFC_RST#

PAGE12 :<1>, DSW add 0.47UF(C2362) for Inrush issue

<2>, Q8 change to NTTFS4C10N from 2N7002W for DSW inrush issue

PAGE13 :<1>, R165,R166 change footprint to RC0402

<2>, +1.35V_SUS add two 3.3pF(R2377/R2378) capacitances to GND for RF solution

<3>, +3V add a 3.3pF(C2381) capacitance to GND for RF solution

<4>, +0.675V_DDR_VTT add two 3.3pF(R2379/R2380) capacitances to GND for RF solution

PAGE14 :<1>, SCH add RP11-16 for KB ESD protection

<2>, H10 footprint change to H-C256D138P2

<3>, Add H20/H21

<4>, CON4 change new material and footprint

PAGE15 :<1>, EC GPIO84 add EC_WLAN_PWR_EN

<2>, EC GPIO55 add SIO_WAKE_GPIO27#

<3>, BOM delete KD5

<4>, Add KC16,KD5

<5>, KR2, KR4, KR19, KR27, KR28, KR29 change to 100K from 10K for power saving.

<6>, EC_WLAN_PWR_EN add KR30 for external P/H

PAGE16 :<1>, CON6 reassign PIN definition and cable can connect well with FPC

<2>, CON6 add MODE_LID-2#

<3>, Add R24457,R24458,R24459 100K ohm pull down

<4>, Remove reserve resistor , R180,R258,R259,R2435,R2435,R2436

<5>, Change U5,U18,U26 load switch with discharge function

<6>, CON6 change new material and footprint

<7>, SCH add R24519/U36 for NFC reset buffer circuit.

<8>, +3V add a 3.3pF(C2382) capacitance to GND for RF solution

<9>, LCDVCC add two 3.3pF(R2383/R2384) capacitances to GND for RF solution

PAGE17: <1>, HDD support USB3 for rear CAM solution

<2>, HDD support USB2 for rear CAM solution

<3>, SCH delete Q21/Q24/Q22/Q23/R2448/R248/R251/R249/R250/C276

<4>, SCH add rear CAM LDO solution

<5>, SCH add power switch for NGFF&HDD

<6>, USB3 RX4 add decap parts(C2360/C2361) to prevent short GND with HDD

<7>, USB3 TX4 add decap parts(C2363/C2364) to prevent short VCC with HDD

<8>, +5V_HDD_+3V_SSD add F25 for Polyswitch

<9>, SCH mount R2440

PAGE18: <1>, HR16,HR18 change to 4.7Kohm, HR17,HR19 change to 2.2Kohm

PAGE19 :<1>, SCH reserve R24454 to support TPS2543

<2>, CON9 change 30PINs from 28PINs

<3>, Change CON22 pin5 from +3V_WAKE_1 to USBPWR_P1

<4>, CON9 change new material and footprint

<5>, SCH add AR13/AR14 for LC circuit for EMI request

<6>, CON22 PIN#29 change to PCH_LAN_WAKE#

C C

<7>, CON22 PIN#31 change to LAN_RST#

<8>, CON22 PIN#30 change to LAN_ISOLATE#

<9>, CON9 PIN#28 change to ACZ_BITCLK

<10>, CON9 PIN#29 change to DMIC_CLK

<11>, CON9 PIN#30 change to DMIC_DATA

<12>, CON22 PIN#28 change to ACZ_SDOUT

<13>, EMI LC solution change to DMIC

<14>, F13-15 change footprint from SMT request

<15>, SCH reserve C2374/C2375 for FI1 S3 resume issue

<16>, CON22 change 44PINs from 40PINs

PAGE20 :<1>, BOM add R2447

<2>, WLAN add U30 to control power from Sony request

<3>, BOM delete R2444/D5 and add R2442 for WLAN reset circuit

<4>, R236 change to +3V_S5_DSW for P/H

<5>, CON13 change to DFHD52MS059

<6>, Change U27 from TPS2557DRBR to G547E1P81U and remove R24444, R2454 100Kohm

<7>, R24445, R2446 change to 100K from 10K for power saving.

<8>, SCH un-mount R2442, R2443, U28, U30, R2451, R2446, Q35, Q34

<9>, SCH mount R24510, R2444

<10>, CON14 change new material and footprint

<11>, SCH un-mount R2441

PAGE22 :<1>, BOM add R24447 and delete R2450

<2>, Add R24460 ,R24461 100K ohm pull down

<3>, Remove reserve resistor , R2450 ,R2384

<4>, Change U29 load switch with discharge function

<5>, SH_ALS_INT# add external P/H with 100K from vendor suggestion.

<6>, U29 PIN1 change +3V_SENSORHUB for optional non CS design

<7>, R24448 PIN2 change +3V_S5 for optional non CS design

<8>, R24447 remove it from SCH

<9>, SCH un-mount U29, C2337, R24453 , C2338

<10>, SCH mount R24448

<11>, SCH un-mount R24460

<12>, R2359, R2361, R2363, R2365, R2367, R2369 mount 10K from vendor suggestion

PAGE23 :<1>, PC17 change to 470p and stuff

<2>, PR25 change to 24.3K

<3>, EC1 and EC2 are added for RF solution

PAGE24 :<1>, SCH delete PG1/PG2 for short PADs

<2>, EC3 /EC4/EC5/EC6 are added for RF solution

PAGE25 :<1>, SCH delete PG3 for short PAD

<2>, SCH delete PR101/PR102/PC65/PQ29/PR98 for fixed 1.35V

<3>, PR99 change to 30.1K for fixed 1.35V

<4>, PC61 no-mount for tCPU13 timing

<5>, EC7 and EC8 are added for RF solution

PAGE26 :<1>, SCH delete PG4 for short PAD

<2>, EC9 and EC10 are added for RF solution

PAGE27 :<1>, SCH add PR230,PR229 for +3V&+5V Load switch thermal protect

<2>, One Shot circuit modify design

PAGE28 : <1>, Change PR231 to 499Kohm

<2>, PR171 change 0 ohm from 6.98K

<3>, SCH add PR232

PAGE29 : <1>, Change PR214 to 113K from 95.3K

<2>, Change PR216 to 33K from 34.8K

DVT->PVT

PAGE07 :<1>BOM remove U34/U35/C2371/C2372/C2373

<2> R40/R24513/R24514/R24511/R24512 change short pad

B B

<3> SCH add C2388/C2389/C2390 for RF request

PAGE08 :SCH add Q46/R24522 for no power on issue

PAGE10 :R95/R96/R97/R98/R2358 change short pad

PAGE11 :R308/R306 change non-mount

PAGE12 :R137/R138/R139 change short pad

PAGE13 :<1> R161/R163/R2431 change short pad

<2> SCH add C2391/C2392 for RF request

PAGE14 :<1> H2/H3 delete them

<2> SCH add C2393 for RF request

PAGE15 :<1>KR25 change short pad

<2> EC GPIO85 add EC_RTC_RST for workaround solution

<3> SCH delete KR28 and EC delete MODE_LID# signal

PAGE16 :<1> Change footprint of F2 to "CC1812" due to SMT issue

<2> R24449/R329/R2438 change short pad

<3> SCH delete F6/C296/C297 for old D-MIC power circuit

<4> SCH add R24523/R24524/R24525/U37/C2385/C2386/C2387 for new D-MIC power circuit

<5> CON6. PIN21 delete MODE_LID# signal

<6> CON6. PIN25 delete Vin

<7> R24457/R24459 mount them

<8> SCH reserve D13

<9> C294/C295 change non-mount for DIM noise issue

PAGE17: <1> RUN_ON_5V add R24526 for P/D

<2> C2355 change 4700PF

PAGE19: CON9 fooitprint change 50506-03041-001-30p-l from 50528-03001-v01-30p-l

PAGE20: R2447 change short pad

PAGE21: <1> R261/R264 change 120 ohm

<2> R263 change 220 ohm

<3> R262 change 100 ohm

PAGE22: R2374/R2385 change short pad

PAGE23: PR3/PR227/PR5/PR24/PR26 change short pad

PAGE24: PR39/PR228/PR53/PR86/PR47/PR54/PR37/PR48 change short pad

PAGE25: <1> SCH add C2394 for RF request

<2> PR95/PR97/PR100 change short pad

PAGE26: PR106/PR114 change short pad

PAGE27: <1> PR117 change short pad

<2> PR149 change 330K from 374K

PAGE28: PR167 change 680K from 470K

PAGE29: SCH add PC132

PVT->MP

PAGE08 :<1>Q46&R24522 stuff them

PAGE10 :<1>Add damping resistors(R24527~R24531) on LPC signal

<2>Add LPC_A0_1, LPC_A1_1, LPC_A2_1, LPC_A3_1, LPC_FRAME#_1

PAGE12 :<1>Change the QPN of C2362 to CH4473Z3B00

PAGE16 :<1>Change the footprint of F2 (same as DVT)

<2>VIN_LVDS reserve C2403/C2404 for ADP power noise test

PAGE17 :<1>Change C2360, C2361, C2363, C2364 from 0.01uf to 0.1uf

<2>Change location from R24486, R24488, R24490, R24491 to C2399~C2402

<3>Reserve R24532~R24535 for co-layout PS8713

<4>Change value of R24498 & R24499 from 0ohm to 4.99K

<5>Change value of R24532 from 4.99K to 4.32K & R24499 unstuff, R24497 stuff, R24507 unstuff, R24536 unstuff for PS8713 setting

<6>Change U33 from SN65LVPE502ARGER to PS8713BTQFN24GTR2-A1

<7>Change the QPN of CON16 to DFHS22FR406

PAGE18 :<1>Change R212 from 10K/F to 24.25K/F, Change R208 from 68K/F to 57.51K/F

<2>Change R218 from 10K/F to 33.09K/F, Change R216 from 113K/F to 78.94K/F

PAGE19 :<1>Change the footprint of CON9 (same as DVT)

A A

PAGE20 :<1>Add LPC_A0_1, LPC_A1_1, LPC_A2_1, LPC_A3_1, LPC_FRAME#_1

PAGE21 :Change pins of CON23 from 8pins to 15pins due to place the e-compass sensor on LED/B

PAGE22 :Move U23 from MB to LED/B

4

3

2

1

03

5

4

3

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

FI2

PROJECT :

FI2

PROJECT :

FI2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Change List

Change List

Change List

Date: Sheet of

Friday, August 23, 2013

Friday, August 23, 2013

Friday, August 23, 2013

333

333

333

1

Date: Sheet of

Date: Sheet of

1A

1A

1A

5

www.Vinafix.vn

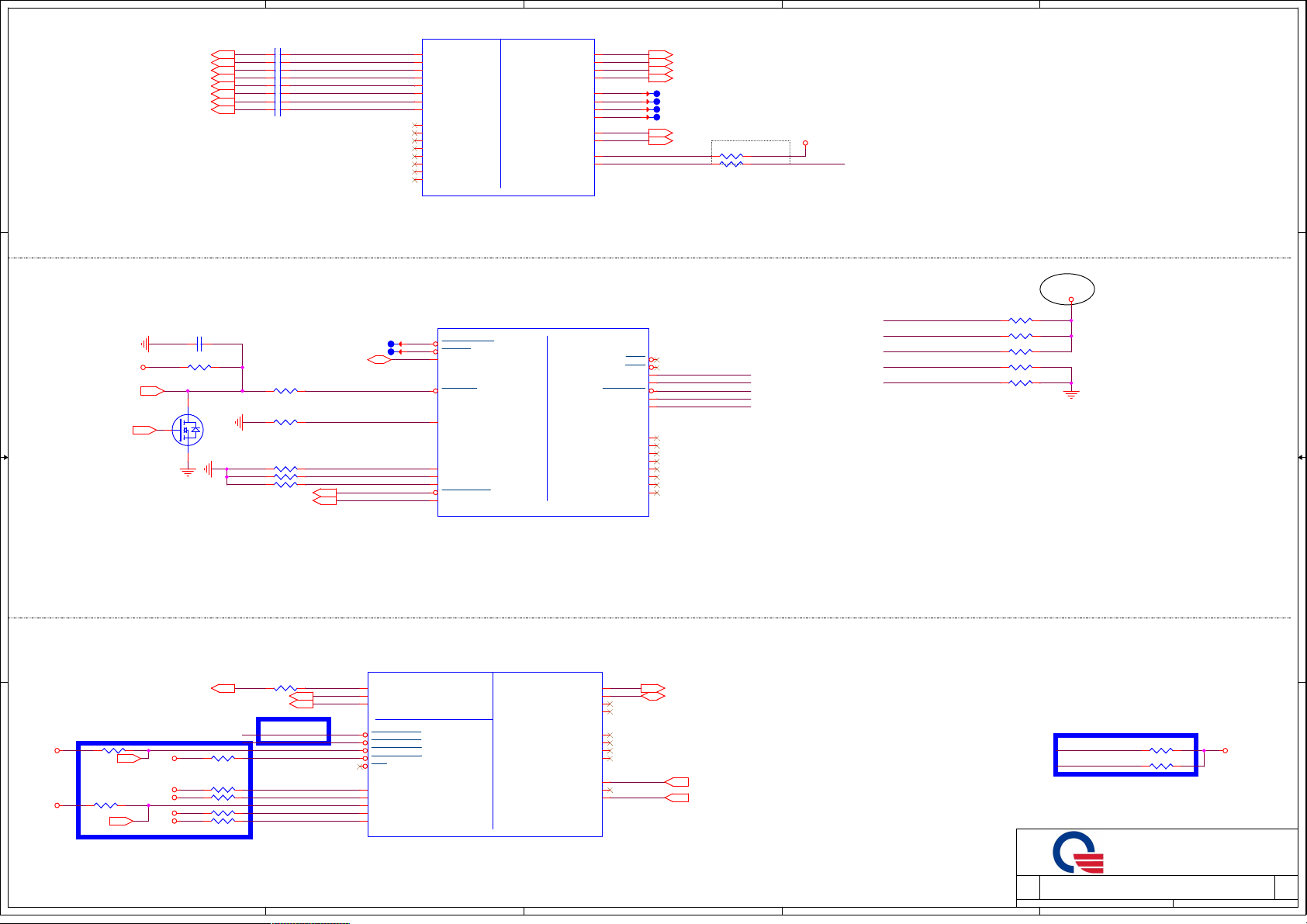

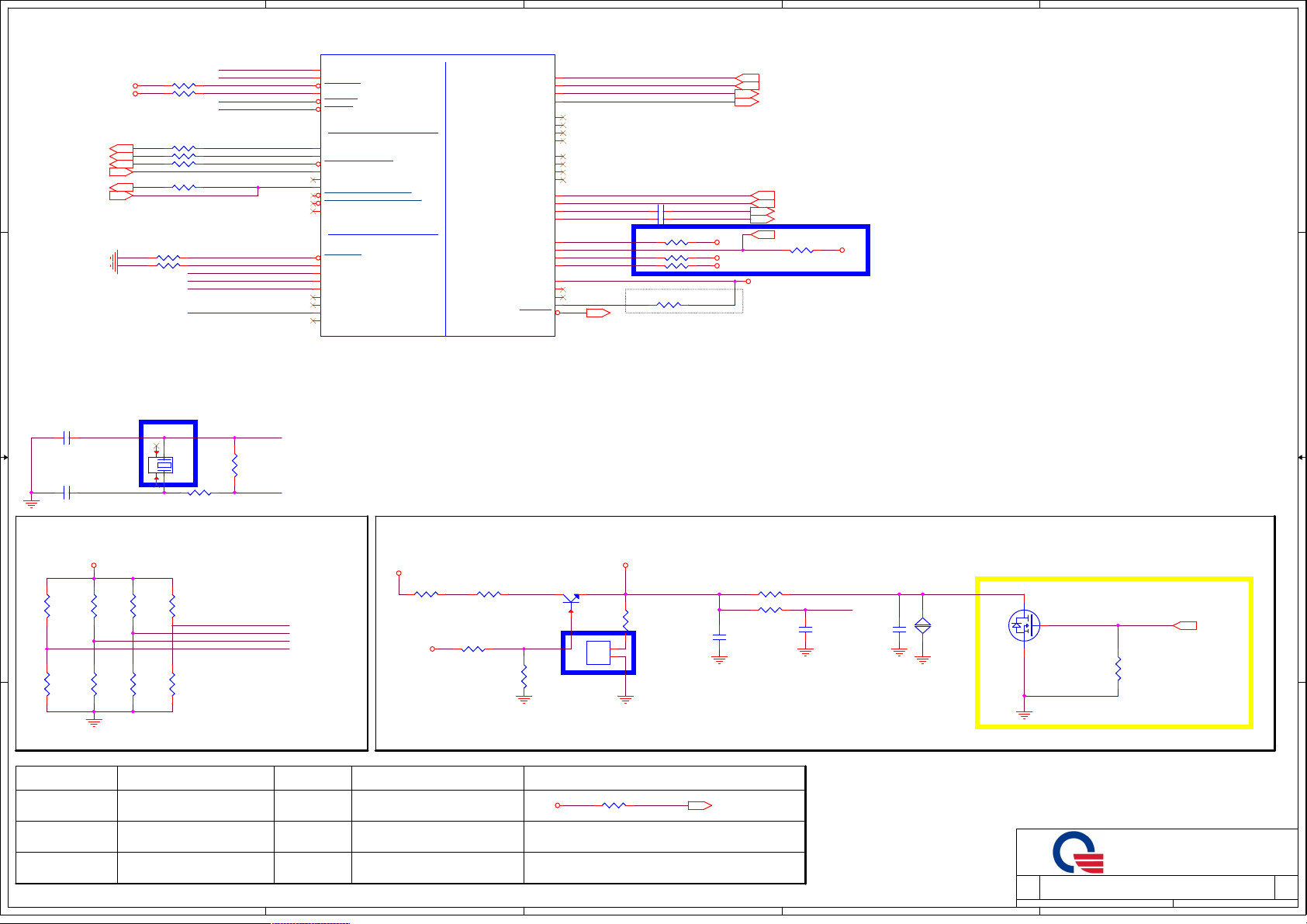

INT. HDMI

INT_ HDMI_T XDN2(18)

INT_ HDMI_T XDP2(18)

INT_ HDMI_T XDN1(18)

INT_ HDMI_T XDP1(18)

INT_ HDMI_T XDN0(18)

INT_ HDMI_T XDP0(18)

INT_ HDMI_T XCN(18)

+1.05V

INT_ HDMI_T XCP(18 )

C312 47P/50V/NPO_4

R8 62_4

3

2

2N7002W(SOT323)

1

D D

C C

H_PROCHOT#(23,27)

PROCHOT(15)

C1 0.1U/10V/X5R_4

C2 0.1U/10V/X5R_4

C3 0.1U/10V/X5R_4

C4 0.1U/10V/X5R_4

C5 0.1U/10V/X5R_4

C6 0.1U/10V/X5R_4

C7 0.1U/10V/X5R_4

C8 0.1U/10V/X5R_4

12

R9 56_4

R10 10K_4

Q1

R11 200/F_4

R12 121/F_4

R13 100/F_4

SM_DRAMRST#(13)

DDR_PG_CTRL(13)

1 2

EC_PECI(15)

CPU_PROCHOT#

H_CPUPWRGD

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

HDMI_TXDN2_C

HDMI_TXDP2_C

HDMI_TXDN1_C

HDMI_TXDP1_C

HDMI_TXDN0_C

HDMI_TXDP0_C

HDMI_TXCN_C

HDMI_TXCP_C

TP2

TP3

DDR_PG_CTRL

4

Haswell ULT (DISPLAY)

U1A

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

U1B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

EDPDDI

MISC

THERMAL

PWR

DDR3L

DSW

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

JTAG

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

PROC_TRST

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

3

TP147

TP148

TP149

TP150

EDP_COMP

DP_UTIL

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

EDP_TX0# (16)

EDP_TX0 (16)

EDP_TX1# (16)

EDP_TX1 (16)

EDP_AUX# (16)

EDP_AUX (16)

R6 24.9/F_4

R2411 *0_4

XDP_TCK0

XDP_TMS_CPU

XDP_TRST_CPU_N

XDP_TDI_CPU

XDP_TDO_CPU

+VCCIOA_OUT

INT_ LVDS_ BRIGHT

2

XDP_TDO_CPU

XDP_TDI_CPU

XDP_TMS_CPU

XDP_TCK0

XDP_TRST_CPU_N

1

4

+1.05V

R1 51/F_4

R2 *51_4

R3 *51_4

R4 51/F_4

R5 51/F_4

B B

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

U1I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

4

+3V

+3V

+3V

+3V

+3V

eDP

SIDEBAND

+3V

+3V

+3V

+3V

PCIE

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

INT_ HDMI_S CL (18)

INT_ HDMI_S DA (18)

INT_ HDMI_H PD_Q (18)

EDP_HPD (16)

3

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

2

DVTDVT

GPIO78

GPIO77

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Wednesday, August 14, 2013

R14 100K_4

R15 100K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

HSW MCP(Display/eDP)

HSW MCP(Display/eDP)

HSW MCP(Display/eDP)

1

+3V

FI2

FI2

FI2

433

433

433

1A

1A

1A

INT_ LVDS_ BRIGHT(16)

EDP_BKLCTL: abnormal 2V when power on.

INT_ LVDS_ BLON(15)

INT_ LVDS_ VDDEN(16)

R2412 0_4

DVT

R271 100K_4

+3V

CR_RST#(19)

A A

R275 100K/F_4

+3V

CR_WAKE#(19)

5

R272 100K_4

+3V

R273 100K_4

+3V

R274 100K_4

+3V

R276 100K_4

+3V

R277 100K_4

+3V

GPIO77

GPIO78

CR_RST#

GPIO80

GPIO55

GPIO52

CR_WAKE#

GPIO51

GPIO53

LCD_PWM

5

www.Vinafix.vn

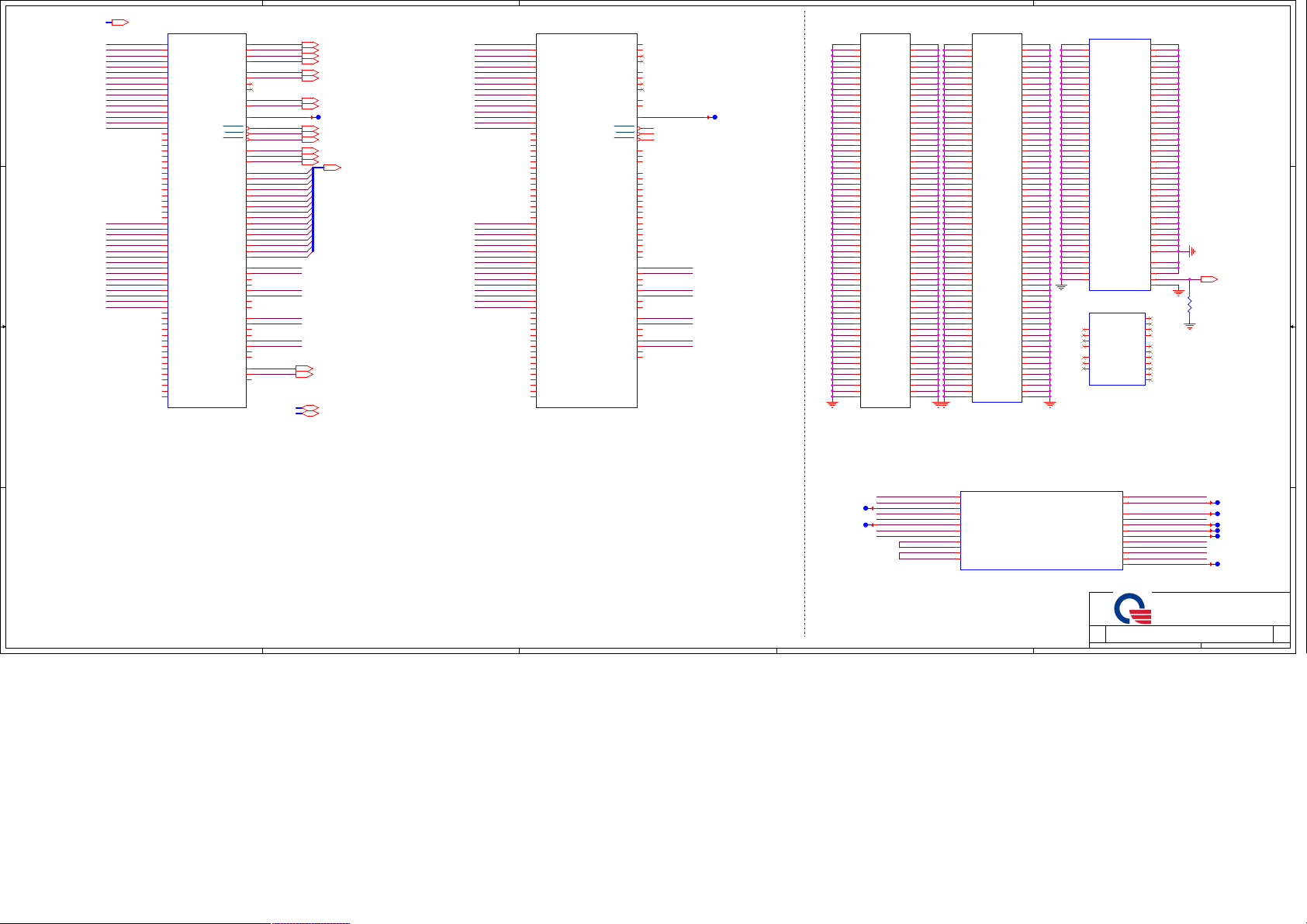

M_A_DQ[63:0] (13)

U1C

AH63

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

D D

C C

B B

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

AW58

AW56

AW54

AW52

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AY56

AV58

AU58

AV56

AU56

AY54

AY52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

DDR CHANNEL A

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

Haswell ULT (DDR3L)

AU37

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_CLKN0

M_A_CLKP0

M_A_CLKN1

M_A_CLKP1

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_ODT0_CPU

M_A_RAS#

M_A_WE#

M_A_CAS#

M_A_BS#0

M_A_BS#1

M_A_BS#2

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_CLKN0 (13)

M_A_CLKP0 (13)

M_A_CLKN1 (13)

M_A_CLKP1 (13)

M_A_CKE0 (13)

M_A_CKE1 (13)

M_A_CS#0 (13)

M_A_CS#1 (13)

M_A_RAS# (13)

M_A_WE# (13)

M_A_CAS# (13)

M_A_BS#0 (13)

M_A_BS#1 (13)

M_A_BS#2 (13)

SM_VREF_CA (13)

SM_VREF_DQ0 (13)

M_A_DQSN[7:0] (13)

M_A_DQSP[7:0] (13)

TP26

M_A_A[15:0] (13)

4

U1D

AY31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AW31

AW29

AW27

AW25

AM29

AM26

AW23

AW21

AW19

AW17

AM22

AM20

AY29

AV31

AU31

AV29

AU29

AY27

AY25

AV27

AU27

AV25

AU25

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AK25

AL25

AY23

AY21

AV23

AU23

AV21

AU21

AY19

AY17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

DDR CHANNEL

B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

3

M_B_ODT0_CPU

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

2

U1N

A11

VSS

A14

VSS

A18

VSS

A24

VSS

A28

VSS

A32

VSS

A36

VSS

A40

VSS

A44

VSS

A48

VSS

A52

VSS

A56

VSS

AA1

VSS

TP27

AA58

AB10

AB20

AB22

AC61

AD21

AD63

AE10

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

AB7

VSS

VSS

VSS

AD3

VSS

VSS

VSS

AE5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

VSS

AJ39

VSS

AJ41

VSS

AJ43

VSS

AJ45

VSS

AJ47

VSS

AJ50

VSS

AJ52

VSS

AJ54

VSS

AJ56

VSS

AJ58

VSS

AJ60

VSS

AJ63

VSS

AK23

VSS

AK3

VSS

AK52

VSS

AL10

VSS

AL13

VSS

AL17

VSS

AL20

VSS

AL22

VSS

AL23

VSS

AL26

VSS

AL29

VSS

AL31

VSS

AL33

VSS

AL36

VSS

AL39

VSS

AL40

VSS

AL45

VSS

AL46

VSS

AL51

VSS

AL52

VSS

AL54

VSS

AL57

VSS

AL60

VSS

AL61

VSS

AM1

VSS

AM17

VSS

AM23

VSS

AM31

VSS

AM52

VSS

AN17

VSS

AN23

VSS

AN31

VSS

AN32

VSS

AN35

VSS

AN36

VSS

AN39

VSS

AN40

VSS

AN42

VSS

AN43

VSS

AN45

VSS

AN46

VSS

AN48

VSS

AN49

VSS

AN51

VSS

AN52

VSS

AN60

VSS

AN63

VSS

AN7

VSS

AP10

VSS

AP17

VSS

AP20

VSS

HSW ULT(GND)

U1O

AP22

VSS

AP23

VSS

AP26

VSS

AP29

VSS

AP3

VSS

AP31

VSS

AP38

VSS

AP39

VSS

AP48

VSS

AP52

VSS

AP54

VSS

AP57

VSS

AR11

VSS

AR15

VSS

AR17

VSS

AR23

VSS

AR31

VSS

AR33

VSS

AR39

VSS

AR43

VSS

AR49

VSS

AR5

VSS

AR52

VSS

AT13

VSS

AT35

VSS

AT37

VSS

AT40

VSS

AT42

VSS

AT43

VSS

AT46

VSS

AT49

VSS

AT61

VSS

AT62

VSS

AT63

VSS

AU1

VSS

AU16

VSS

AU18

VSS

AU20

VSS

AU22

VSS

AU24

VSS

AU26

VSS

AU28

VSS

AU30

VSS

AU33

VSS

AU51

VSS

AU53

VSS

AU55

VSS

AU57

VSS

AU59

VSS

AV14

VSS

AV16

VSS

AV20

VSS

AV24

VSS

AV28

VSS

AV33

VSS

AV34

VSS

AV36

VSS

AV39

VSS

AV41

VSS

AV43

VSS

AV46

VSS

AV49

VSS

AV51

VSS

AV55

VSS

AU44

AV44

U1P

D33

VSS

D34

VSS

D35

VSS

D37

VSS

D38

VSS

D39

VSS

D41

VSS

D42

VSS

D43

VSS

D45

VSS

D46

VSS

D47

VSS

D49

VSS

D5

VSS

D50

VSS

D51

VSS

D53

VSS

D54

VSS

D55

VSS

D57

VSS

D59

VSS

D62

VSS

D8

VSS

E11

VSS

E17

VSS

F20

VSS

F26

VSS

F30

VSS

F34

VSS

F38

VSS

F42

VSS

F46

VSS

F50

VSS

F54

VSS

F58

VSS

F61

VSS

G18

VSS

G22

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

H13

VSS

U1R

AT2

RSVD

RSVD

RSVD

D15

RSVD

F22

RSVD

H22

RSVD

J21

RSVD

AV59

VSS

AV8

VSS

AW16

VSS

AW24

VSS

AW33

VSS

AW35

VSS

AW37

VSS

AW4

VSS

AW40

VSS

AW42

VSS

AW44

VSS

AW47

VSS

AW50

VSS

AW51

VSS

AW59

VSS

AW60

VSS

AY11

VSS

AY16

VSS

AY18

VSS

AY22

VSS

AY24

VSS

AY26

VSS

AY30

VSS

AY33

VSS

AY4

VSS

AY51

VSS

AY53

VSS

AY57

VSS

AY59

VSS

AY6

VSS

B20

VSS

B24

VSS

B26

VSS

B28

VSS

B32

VSS

B36

VSS

B4

VSS

B40

VSS

B44

VSS

B48

VSS

B52

VSS

B56

VSS

B60

VSS

C11

VSS

C14

VSS

C18

VSS

C20

VSS

C25

VSS

C27

VSS

C38

VSS

C39

VSS

C57

VSS

D12

VSS

D14

VSS

D18

VSS

D2

VSS

D21

VSS

D23

VSS

D25

VSS

D26

VSS

D27

VSS

D29

VSS

D30

VSS

D31

VSS

VSS_SENS E

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

1

5

H17

VSS

H57

VSS

J10

VSS

J22

VSS

J59

VSS

J63

VSS

K1

VSS

K12

VSS

L13

VSS

L15

VSS

L17

VSS

L18

VSS

L20

VSS

L58

VSS

L61

VSS

L7

VSS

M22

VSS

N10

VSS

N3

VSS

P59

VSS

P63

VSS

R10

VSS

R22

VSS

R8

VSS

T1

VSS

T58

VSS

U20

VSS

U22

VSS

U61

VSS

U9

VSS

V10

VSS

V3

VSS

V7

VSS

W20

VSS

W22

VSS

Y10

VSS

Y59

VSS

Y63

VSS

V58

VSS

AH46

VSS

V23

VSS

E62

AH16

VSS

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

100/F_4

R17

VSS_SENS E (23)

U1Q

DC_TEST_B62_B63

DC_TEST_C1_C2

2

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

TP_DC_TEST_AY60

TP29

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_B2

TP145

DC_TEST_A3_B3

DC_TEST_A61_B61

A A

1.Level 1 Environment-related Substances Should Never be Used.

5

4

3

2.Recycled Resin and Coated Wire should be procured from Green Partners.

A3

DC_TEST_A3_B3

A4

TP_DC_TEST_A4

A60

TP_DC_TEST_A60

A61

DC_TEST_A61_B61

A62

TP_DC_TEST_A62

AV1

TP_DC_TEST_AV1

AW1

TP_DC_TEST_AW 1

AW2

DC_TEST_AY2_AW2

AW3

DC_TEST_AY3_AW3

AW61

DC_TEST_AY61_AW61

AW62

DC_TEST_AY62_AW62

AW63

TP_DC_TEST_AW 63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument Number Rev

Size D ocument Number Rev

Size D ocument Number Rev

Date: Sheet of

Wednesday, August 14, 2013

Date: Sheet of

Wednesday, August 14, 2013

Date: Sheet of

Wednesday, August 14, 2013

PROJECT :

HSW MCP(MEMORY/GND)

HSW MCP(MEMORY/GND)

HSW MCP(MEMORY/GND)

1

TP28

TP30

TP32

TP33

TP34

TP35

FI2

FI2

FI2

533

533

533

1A

1A

1A

5

www.Vinafix.vn

4

3

2

1

U1S

AC60

CFG0

CFG1

TP38

TP41

TP42

TP43

D D

C C

TP47

TP48

TP49

TP50

TP51

TP52

TP53

TP54

TP55

R19 49.9/F_4

R20 8.2K/F_4

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

NOA_STBN_0

NOA_STBN_1

NOA_STBP_0

NOA_STBP_1

NOA_RCOMP

TD_IREF

AC62

AC63

AA63

AA60

AA62

AA61

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

U63

U62

V63

H18

B12

A5

E1

D1

J20

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

RESERVED

PROC_OPI_RCOMP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

PROC_OPI_COMP

R18 49.9/F_4

6

Processor Strapping

1

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE

SELECTION

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

B B

CFG4

DISPLAY PORT PRESENCE STRAP

CFG 8

ALLOW THE USE OF NOA

ON LOCKED UNITS

CFG9

NO SVID PROTOCOL CAPABLE VR

CONNECTED

(DEFAULT) NORMAL OPERATION; NO STALL STALL

(DEFAULT) NORMAL OPERATION

DISABLED

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE,

NOA WILL BE DISABLED IN LOCKED

UNITS AND ENABLED IN UN-LOCKED

UNITS

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

PCH-LESS MODE

ENABLED

SET DFX ENABLED BIT IN DEBUG

INTERFACE MSR

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF

THE UNIT

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

0

CFG0

R21 *1K_4

CFG1

R22 *1K_4

CFG3

R23 *1K_4

CFG4

R24 1K_4

CFG8

R25 *1K_4

CFG9

R26 *1K_4

CFG10

SAFE

MODE

BOOT

A A

5

POWER FEATURES ACTIVATED

DURING RESET

4

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green

3

Partners.

CFG10

2

R27 *1K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Wednesday, August 14, 2013

PROJECT :

HSW MCP(CFG/PwrMGT)

HSW MCP(CFG/PwrMGT)

HSW MCP(CFG/PwrMGT)

FI2

FI2

FI2

633

633

633

1

1A

1A

1A

5

www.Vinafix.vn

2.2uF *4

+1.35V_SUS

D D

PVT

VR_EN(1.05V): Output to disable VR in C10

VR_Ready(1.05v):

C C

B B

EC_PWROK

A A

10uF *6

DVT

C2376 3.3P/50V_4

C11 10/u/6.3V/X5R_6

C13 10/u/6.3V/X5R_6

C15 10/u/6.3V/X5R_6

C17 10/u/6.3V/X5R_6

C19 10/u/6.3V/X5R_6

C21 10/u/6.3V/X5R_6

C24 2.2u/6.3V/X5R_4

C26 2.2u/6.3V/X5R_4

C28 2.2u/6.3V/X5R_4

C30 2.2u/6.3V/X5R_4

C2388 3.3P/50V_4

C2390 3.3P/50V_4

C2389 3.3P/50V_4

+VCC_CORE

H_VR_ENABLE_MCP(23)

+V1.05S_VCCST

VCCST_PWRGD(O/D Input):

VCC/VDDQ/CLK stable

PVT

R24513 *SHORT_6

R24517 *0_4

5

VCC_SENSE(23)

R39 150/F_4

+1.05V

DVT

+3V_S5

R41

100K_4

5

4 3

C2373

*0.1U/10V _4

+1.35V_SUS

(VDDQ : 4.2A)

+VCC_CORE

R35 100/F_4

+VCCIO_OUT

+VCCIOA_OUT

R36 10K_4

+V1.05S_VCCST

R40 *SHORT_6

PVT

6

2

Q2

2N7002DW

1

TP90

H_CPU_SVIDALRT_N

VR_SVID_CLK

VR_SVID_DATA

VCCST_PWRGD

VR_READY

FIVR_EN_BUF

+VCC_CORE

U35

VCC

NC

IN

GND3OUT

*74LVC1 G07GW

5

4

1

2

Haswell ULT MCP(POWER)

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

VCCST_PWRGD_C

+3V_S5

U1L

L59

RSVD

J58

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

F59

VCC

N58

RSVD

RSVD

E63

VCC_SENSE

RSVD

A59

VCCIO_OUT

E20

VCCIOA_OUT

RSVD

RSVD

RSVD

L62

VIDALERT

N63

VIDSCLK

L63

VIDSOUT

B59

VCCST_PWRGD

F60

VR_EN

C59

VR_READY

D63

VSS

H59

PWR_DEBUG

P62

VSS

P60

RSVD_TP

P61

RSVD_TP

N59

RSVD_TP

N61

RSVD_TP

T59

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

U59

RSVD

V59

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

C24

VCC

C28

VCC

C32

VCC

C2372

*0.1U/10V _4

4

HSW ULT

POWER

PVT

R24514 *SHORT_6

R24518 *0_4

PVT

4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

+VCC_CORE

Haswell ULT 15W : 32A

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

+V1.05S_VCCST

C9 22u/6.3V/X5R_6

C10 22u/6.3V/X5R_6

C14 22u/6.3V/X5R_6

C16 *22u/6.3V/X5R_6

C18 22u/6.3V/X5R_6

C20 22u/6.3V/X5R_6

C22 22u/6.3V/X5R_6

C23 *22u/6.3V/X5R_6

C25 22u/6.3V/X5R_6

C27 22u/6.3V/X5R_6

C29 22u/6.3V/X5R_6

C31 22u/6.3V/X5R_6

C32 22u/6.3V/X5R_6

C33 *22u/6.3V/X5R_6

C34 22u/6.3V/X5R_6

C35 *22u/6.3V/X5R_6 R33

C36 *22u/6.3V/X5R_6

C37 22u/6.3V/X5R_6

C38 22u/6.3V/X5R_6

C39 22u/6.3V/X5R_6

C40 22u/6.3V/X5R_6

C41 22u/6.3V/X5R_6

C42 22u/6.3V/X5R_6

C43 *22u/6.3V/X5R_6

C44 22u/6.3V/X5R_6

C45 22u/6.3V/X5R_6

C46 22u/6.3V/X5R_6

C47 22u/6.3V/X5R_6

C48 *22u/6.3V/X5R_6

23 X 22UF(0805 MLCC)

DVT

R42

100K_4

VCCST_PWRGD

C49

680P/50V/X5R_4

DVT

3

H_CPU_SVIDALRT_N

close to CPU

+1.05V

12

R31

130_4

2

SVID ALERT

close to CPU

R30 43_4C12 22u/6.3V/X5R_6

VR_SVID_DATA

+1.05V

R28

75_4

SVID DATA

1

7

VR_SVID_ALERT# (23)

close to VR

+1.05V

12

130_4

VR_SVID_DATA (23)

close to VR

+1.05V

R37

54.9/F_4

VR_SVID_CLK

VR_SVID_CLK (23)

DVT

+3V +3V_S5

5

VCC5NC

IN

GND3OUT

R44

100K_4

PVT

VR_READY_C

6

2

Q3

2N7002DW

1

4 3

+3V_S5

C2371

*0.1U/10V _4

4

R24512 *SHORT_6

R24516 *0_4

VR_READY

R43

PVT

IMVP _PWR GD(23)

R24511 *SHORT_6

R24515 *0_4

100K_4

U34

1

2

*74LVC1 G07GW

PVT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

1.Level 1 Environment-related Substances Should Never be Used.

3

2.Recycled Resin and Coated Wire should be procured from Green Partners.

2

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Wednesday, August 14, 2013

PROJECT :

HSW MCP(Power)

HSW MCP(Power)

HSW MCP(Power)

FI2

FI2

FI2

733

733

733

1

1A

1A

1A

5

www.Vinafix.vn

Haswell ULT (RTC, HDA, JTAG, SATA)

U1E

RTC_X1

RTC_X2

+3V_RTC

+3V_RTC

D D

ACZ_BITCLK(19)

ACZ_SYNC(19)

ACZ_RST#(19)

ACZ_SDIN0(19)

ACZ_SDOUT(19)

ACZ_SDOUT_R(15)

C C

R45 1M_4

R46 330K_4

R47 33_4

R48 33_4

R49 33_4

R50 33_4

R51 *51__4

R52 51__4

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BITCLK_C

HDA_SYNC_C

HDA_RST#_C

ACZ_SDOUT_R

PCH_TRST

PCH_XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

XDP_TMS

PCH_JTAGX

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RX D

AU12

HDA_SDI1/I2S1_RX D

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_T XD

AV10

HDA_DOCK_RST/I2S1_ SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

RTC

4

3

2

1

8

RSVD

RSVD

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

PCIE_TXN6_C

PCIE_TXP6_C

GPIO34

EC_EXT_SMI#

GPIO36

GPIO37

SATA_RCOMP

SATA_ACT# (21)

C63 0.1u/10V/X5R_4

C64 0.1u/10V/X5R_4

R278 100K_4

R280 100K_4

R281 100K_4

1 2

R54 3.01K/F_4

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

AUDIO

JTAG

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

+3V

SATA0GP/GPIO34

+3V

SATA1GP/GPIO35

+3V

SATA2GP/GPIO36

+3V

SATA3GP/GPIO37

SATA_RCOMP

SATA_IREF

+3V

+3V

+3V

SATA_RXN0 (17)

SATA_RXP0 (17)

SATA_TXN0 (17)

SATA_TXP0 (17)

PCIE_RXN6 (19)

PCIE_RXP6 (19)

PCIE_TXN6 (19)

PCIE_TXP6 (19)

EC_EXT_SMI# (15)

R279 100K_4

+V1.05S_ASATA3PLL

HDD

Card Reader

+3V

DVT

DVT

C54 15P/50V/_4

41

Y1

32.768KHZ

2 3

R324 0_4C55 15P/50V/_4

RTC_X1

R55

10M_4

RTC_X2RTC_X2_R

PCH JTAG Debug (CLG)

R58

*210/F_4

R63

*100/F_4

+3V_S5

R59

210/F_4

R64

100/F_4

R60

210/F_4

R65

100/F_4

B B

R61

210/F_4

R66

100/F_4

MP remove(Intel)

PCH_JTAG_TDO

XDP_TMS

XDP_TDI

PCH_JTAGX

RTC Circuitry (RTC)

(Rechargable BATT)

6237LDO5

R24450

2.2K/F_4

6237LDO5

R368

2.2K/F_4

MMBT3904-7-F/40V/200MA

R366 4.7K_4

VCCRTC_1

R367

15K_4

Q32

13

2

CON1

50271-00201-001

Battery

+3V_RTC

1

2

J1

*SHORT_ PAD1

PVT

3

2N7002W(SOT323)

Q46

2

1

EC_RTC_RST

R24522

100K_4

EC_RTC_RST (15)

RTC Power trace width 20mils.

20MIL

R369

330/F_4

20MIL

1

2

1u/6.3V/X5R_4

R56 20K/F_4

R57 20K/F_4

C56

1u/6.3V/X5R_4C58

RTC_RST#

SRTC_RST#

C57

1u/6.3V/X5R_4

12

DVT

PCH Strap Table

Pin Name Strap description

A A

SPKR

HDA_SDO

INTVRMEN

No reboot mode setting PWROK

Flash Descriptor Security

Override / Intel ME Debug

Mode

Integrated 1.05V VRM enable ALWAYS

5

Sampled

PWROK

Configuration note

0 = Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = Security Effect (Int PD)

1 = Can be Override

Should be always pull-up

4

+3V

R67 *1K_4

SPKR (11,19)

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

1.Level 1 Environment-related Substances Should Never be Used.

3

2.Recycled Resin and Coated Wire should be procured from Green Partners.

2

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, August 21, 2013

Wednesday, August 21, 2013

Wednesday, August 21, 2013

PROJECT :

HSW PCH(RTC/HDA/SATA)

HSW PCH(RTC/HDA/SATA)

HSW PCH(RTC/HDA/SATA)

FI2

FI2

FI2

833

833

833

1

1A

1A

1A

5

www.Vinafix.vn

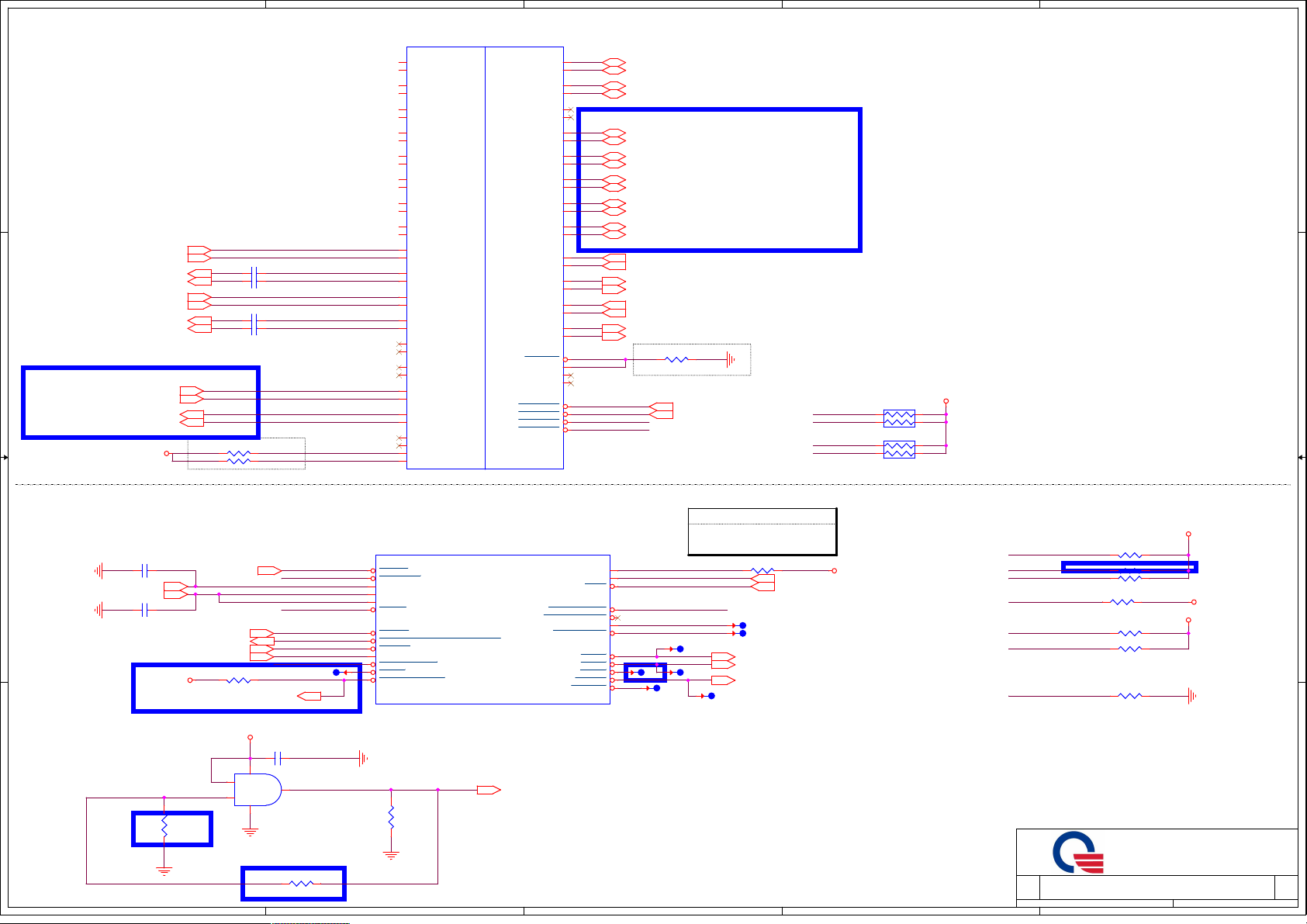

D D

PCIE_RXN3(20)

WiFi/BT NGFF

LAN

C C

PCIE_RXP3(20 )

PCIE_TXN3(20)

PCIE_TXP3(20)

PCIE_RXN4(19)

PCIE_RXP4(19 )

PCIE_TXN4(19)

PCIE_TXP4(19)

C59 0.1u/10V/X5R_4

C60 0.1u/10V/X5R_4

C61 0.1u/10V/X5R_4

C62 0.1u/10V/X5R_4

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_TXN4_C

PCIE_TXP4_C

DVT

USB3_RX4-(17)

USB3_RX4+(17)

Rear CAMERA

USB3_TX4-(1 7)

USB3_TX4+(17)

+V1.05S_AUSB3PLL

1 2

R69 3.01K/F_4

1 2

R70 0_4

PCIE_RCOMP

PCIE_IREF

4

Haswell ULT (PCIE,USB)

U1K

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

PCIE

USB

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_BIAS

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

3

USBP0- (19)

USBP0+ (19)

USBP1- (19)

USBP1+ (19)

USBP3- (17)

USBP3+ (17)

USBP4- (16)

USBP4+ (16)

USBP5- (20)

USBP5+ (20)

USBP6- (22)

USBP6+ (22)

USBP7- (16)

USBP7+ (16)

USB3_RX1- (19)

USB3_RX1+ (19)

USB3_TX1- (19)

USB3_TX1+ (19)

USB3_RX2- (19)

USB3_RX2+ (19)

USB3_TX2- (19)

USB3_TX2+ (19)

R68 22.6/F_4

USB_OC0# (19)

USB_OC1# (19)

USB3.0 Port 1 with Charge

USB3.0 Port 2

CAMERA (Rear)

Touch Screen (Full Speed)

BT (Combo)

Sensor Hub

CAMERA (Front)

USB3.0 Port 1

USB3.0 Port 2

USB_OC3#

USB_OC1#

USB_OC2#

USB_OC0#

DVT

RP7 10K_x2

4

2

RP8 10K_x2

4

2

2

1

9

+3V_S5

3

1

3

1

Haswell ULT (SYSTEM POWER MANAGEMENT)

U1H

B B

C304 220P_4

PCH_PWROK_EC(15)

EC_PWROK(7,15)

C305 220P_4

+3V_S5_DSW

SUSACK#(15)

RSMRST#(15)

SUSWARN#(15)

EC_PWRBTN#(15)

AC_PRESENT(1 5)

R282 *100K_4

WLAN_PW_EN(20)

SYS_RESET#

PCH_PWROK_EC

PCI_PLTRST#

SUSWARN#

EC_PWRBTN#

AC_PRESENT

PM_BATLOW#

WLAN_PW_EN

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/ GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPI O72

AF3

TP88 TP80

SLP_S0

AM5

SLP_WLAN/GPI O29

SYSTEM POWER

MANAGEMENT

DSW

DSW

DSW

+3V

+3V_S5

+3V_S5

DSW

+3V_S5

DSW

DSWVRMEN

DSW

DSW

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

DSW

DSW

DSW

DSW

DSW

PWRBTN# and SUSACK# internal PU

+3V

C65 0.1U/10V/X5R_4

2

A A

PCI_PLTRST#

DVT

R24520

100K/J_4

1

U2

3 5

TC7SH08FU

4

R79

100K/J_4

PLTRST# (16,19,20)

DPWROK

WAKE

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

DVT

DSWVRMEN

PCIE_WAKE#

TP154

On Die DSW VR Enable

High = Enable (Default)

Low = Disable

R72 330K_4

CLKRUN#

TP79

TP81

TP82

DPWROK (15)

PCIE_WAKE# (19,20)

TP77

TP78

SLP_S4# (15)

SLP_S3# (15)

SLP_SUS# (15)

+3V_RTC

DVT

R24521 *0R_4

5

4

3

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

2

PCH Pull-high/low(CLG)

+3V_S5_DSW

PCIE_WAKE#

AC_PRESENT

PM_BATLOW#

SUSWARN#

CLKRUN#

SYS_RESET#

PCH_PWROK_EC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Wednesday, August 14, 2013

R71 1K_4

R73 100K_4

R74 10K_4

R75 10K_4

R76 10K_4

R77 10K_4

R78 100K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

HSW PCH(PCIE/USB)

HSW PCH(PCIE/USB)

HSW PCH(PCIE/USB)

1

+3V

FI2

FI2

FI2

DVT

+3V_S5

933

933

933

1A

1A

1A

5

www.Vinafix.vn

4

3

2

1

C67 12P_4

4

Haswell ULT (CLK)

U1F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

D D

WiFi/BT(NGFF)

LAN

CLK_PCIE_WIFIN(20)

CLK_PCIE_WIFIP(20)

PCIE_CLK_REQ2#(2 0)

CLK_PCIE_LANN(19)

CLK_PCIE_LANP(19)

PCIE_CLK_REQ3#(1 9)

GFX

CLK_PCIE_CRDN(19)

Card Reader

CLK_PCIE_CRDP(19)

PCIE_CLK_REQ5#(1 9)

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

U2

PCIECLKRQ0/GPIO1 8

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO1 9

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO2 0

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO2 1

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO2 2

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO2 3

+3V

+3V

+3V

CLOCK

+3V

+3V

+3V

XTAL24_OUT

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

XTAL24_IN

RSVD

RSVD

A25

XTAL24_IN

B25

XTAL24_OUT

K21

M21

C26

DIFFCLK_BIASREF

C35

TESTLOW_0

C34

TESTLOW_1

AK8

TESTLOW_2

AL8

TESTLOW_3

AN15

LPC_CLK_0

AP15

LPC_CLK_1

B35

TP83

A35

TP84

3

1

1 2

1 2

1 2

*10P/50V _4

Y2

24MHz

2

C68 12P_4

C69

R82

1M_4

R83 3.01K/F_4

R84 22_4

R85 22_4

+1.05V

C70

*10P/50V _4

CLK_PCI_EC (15)

CLK_PCI_LPC (20)

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

Do not short

the testlow pins together.

CCD_PWR_EN

GPIO11

SENSOR_HDR_SMALERT1

TESTLOW_0

TESTLOW_1

TESTLOW_2

TESTLOW_3

+3V

RP1

10

9

8

7 4

10K_x8

DVT

RP2 10K_x2

1

3

RP3 10K_x2

3

1

R24455 *100K_4

R24456 100K_4

R86 10K_4

1

PCIE_CLK_REQ4#

2

PCIE_CLK_REQ5#

3

56

+3V

2

4

2

4

10

+3V_S5

MP

LPC_AD0_1(20)

LPC_AD1_1(20)

LPC_AD2_1(20)

C C

LPC_AD3_1(20)

LPC_FRAME#_1(20)

LPC_AD0(15 )

LPC_AD1(15 )

LPC_AD2(15 )

LPC_AD3(15 )

LPC_FRAME#(15)

LPC_AD0_1

LPC_AD1_1

LPC_AD2_1

LPC_AD3_1

LPC_FRAME#_1

R24527 33_4

R24528 33_4

R24529 33_4

R24530 33_4

R24531 33_4

Haswell ULT (LPC/SPI/SMB/CLINK)

U1G

LPC_AD0_1

LPC_AD1_1

LPC_AD2_1

LPC_AD3_1

LPC_FRAME#_1

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

AU14

AW12

AY12

AW11

AV12

AA3

AC2

AA2

AA4

AF1

Y7

Y4

Y6

LAD0

LAD1

LAD2

LAD3

LFRAME

SPI_CLK

SPI_CS0

SPI_CS1

SPI_CS2

SPI_MOSI

SPI_MISO

SPI_IO2

SPI_IO3

LPC

SPI

+3V_S5

SMBUS

+3V_S5

+3V_S5

SML1ALERT/PCHHOT/GPIO7 3

+3V_S5

+3V_S5

C-LINK

SMBALERT/GPIO11

SML0ALERT/GPIO60

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

SMBCLK

SMBDATA

SML0CLK

CL_CLK

CL_DATA

CL_RST

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

GPIO11

SMB_PCH_CLK

SMB_PCH_DAT

CCD_PWR_EN

SMB_NFC_CLK

SMB_NFC_DAT

SENSOR_HDR_SMALERT1

SMB_ME1_CLK

SMB_ME1_DAT

SPD

CCD_PWR_EN (16)

NFC

SENSOR_HDR_SMALERT1 (22)

EC

+3V_S5

R88 2.2K_4

R90 2.2K_4

SMBus/Pull-up(CLG)

Q4

5

SMB_PCH_CLK

2

SMB_PCH_DAT

6

R87 4.7K/J_4

43

R89 4.7K/J_4

1

SMB_RUN_CLK (13,17)

SMB_RUN_DAT (13,17)

+3V+3V

+3V+3V

2N7002DW

B B

+3V_S5

PVT

F_CS0#_PCH(15)

F_SDI_PCH(1 5)

SCK_PCH(15)

SD0_PCH(15)

R95 *SHORT_6

R96 *SHORT_6

R97 *SHORT_6

R98 *SHORT_6

For NPCE985L Using

+3V_S5

R102

A A

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

+3V_S5

5

PVT

R2358 *SHORT_6

R103 15_4

R105 15_4

R106 15_4

R108 15_4

R110 1K_4

*10K_4

PCH_SPI_CS0#_RPCH_SPI_CS0#

PCH_SPI_CLK_R

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_WP#

PCH_SPI_CS0#_R

PCH_SPI_SO_R

PCH_SPI_CLK_R

PCH_SPI_SI_R

U3

1

CE#

6

SCK

5

SI

2

SO

3

WP#

W25Q64FVSSIQ

VDD

HOLD#

VSS

SPI FLASH

+3V_S5

C72 0.1u/10V/X5R_4

8

R104 1K_4

7

PCH_SPI_IO3_R

4

4

+3V_S5

R107 15_4

PCH_SPI_IO3

1.Level 1 Environment-related Substances Should Never be Used.

2.Recycled Resin and Coated Wire should be procured from Green Partners.

3

R91 1K_4

R93 1K_4

2

SMB_NFC_CLK (16)

SMB_NFC_DAT (16)

C71 0.1U/10V/X5R_4

R99 10K/J_4

MBCLK(15,1 8)

MBDATA(15,18)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Wednesday, August 14, 2013

Q6

5

2

6

2N7002DW

HSW PCH(CLK/LPC/SPI/SMB)

HSW PCH(CLK/LPC/SPI/SMB)

HSW PCH(CLK/LPC/SPI/SMB)

R100 2.2K_4

43

SMB_ME1_CLK

R101 2.2K_4

1

SMB_ME1_DAT

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

FI2

FI2

FI2

10 33

10 33

10 33

+3V_S5+3V_S5

+3V_S5

1A

1A

1A

Loading...

Loading...