Page 1

MDCC-2000

SERVICE MANUAL

Ver 1.0 2001. 05

US and foreign patents licensed from Dolby

Laboratories Licensing Corporation

SPECIFICATIONS

US Model

Model Name Using Similar Mechanism NEW

MD Mechanism Type CCMD-2000

Optical Pick-up Mechanism Type KMS-250A

Laser diode properties

Material: GaAlAs

Wavelength: 780 nm

Emission duration: Continuous

Laser output: Less than 44.6 µW

(This output is the value measured at a distance of

about 200 mm from the lens surface on the optical

pick-up block with 7 mm aperture.)

Revolutions

400 rpm to 1800 rpm (CLV)

Error correction

Advanced Cross Interleave Reed Solomon Code (ACIRC)

Sampling frequency

44.1 kHz

Coding

ATRAC 3 (Adaptive TRansform Acoustic Coding 3)

Modulation system

EFM (Eight to Fourteen Modulation)

Number of channels

2 or 4 monaural channels

Frequency response

50–10,000 Hz

Speaker

Approx. 5.0 cm (2 inches) dia.

Power output

600 mW (at 10% distortion)

Input

MIC: Canon XLR-3-31 type 0.44 mV (-65 dB)

LINE IN 1-4: mini jack 0.49 V (-4 dB)

Output

EAR (minijack)

for 8–300 Ω earphones

LINE OUT 1,2 (minijack) 0.22 V (-11 dB) load inpedance 47 kΩ

ADA (minijack) 0.22 V (-11 dB) load inpedance 10 kΩ

PA (minijack) 0.22 V (-11 dB) load inpedance 47 kΩ

PC (9 pin D-sub)

DISPLAY (modular)

Other connector

CONTROL UNIT connector

REMOTE jack

Power requirements

12 V DC

DC IN 12V jack accepts the supplied AC power

adaptor for use on 120 V AC, 60 Hz

Dimensions

Approx. 320 x 280 x 118 mm (w/h/d)

5

(12

⁄8 x 111⁄8 x 43⁄4 inches)

including projecting parts and controls

Mass

Approx. 4.5 kg (9 lb 15 oz)

Accessories supplied

AC power adaptor (1)

AC power cord (1)

Sony CR2032 lithium battery (1)

MiniDisc (2)

Design and specifications are subject to change without notice.

9-873-111-11

2001E1600-1

© 2001.5

MD CONFER-CORDER

Sony Corporation

Personal Audio Company

Shinagawa Tec Service Manual Production Group

Page 2

MDCC-2000

TABLE OF CONTENTS

1. GENERAL ·································································· 3

2. DISASSEMBLY

2-1. Cabinet (Upper) Section··············································· 6

2-2. Switch Section······························································ 7

2-3. LCD Section································································· 7

2-4. I/O Section ···································································8

2-5. Volume Section ···························································· 8

2-6. Main Board ·································································· 9

2-7. Connector Section ························································ 9

2-8. Door ··········································································· 10

2-9. MD Board ·································································· 10

2-10. Base Unit Section······················································· 11

2-11. BUM-F1 Board ·························································· 11

2-12. REC/PB Head Assy (HR901) Section ······················· 12

2-13. Holder Assy, Cartridge Section ·································· 12

2-14. Holder Assy, Cartridge Installation ···························· 13

2-15. Optical Pick-up (KMS-250A) Section ······················· 13

3. TEST MODE ···························································· 14

4. ELECTRICAL ADJUSTMENTS ··························· 27

5. DIAGRAMS

5-1. Circuit Boards Location ············································· 29

5-2. Block Diagrams MD Section ···································· 30

I/O Section ·································································31

FIFO Section ······························································ 32

CPU Section ······························································· 33

LCD Section······························································· 34

5-3. Printed Wiring Board MD Section ···························· 35

5-4. Schematic Diagram MD Section (1/4) ······················ 36

5-5. Schematic Diagram MD Section (2/4) ······················ 37

5-6. Schematic Diagram MD Section (3/4) ······················ 38

5-7. Schematic Diagram MD Section (4/4) ······················ 39

5-8. Schematic Diagram BUM Section ···························· 40

5-9. Printed Wiring Board BUM Section ························· 41

5-10. Schematic Diagram Main Section (1/12) ·················· 42

5-11. Schematic Diagram Main Section (2/12) ·················· 43

5-12. Schematic Diagram Main Section (3/12) ·················· 44

5-13. Schematic Diagram Main Section (4/12) ·················· 45

5-14. Schematic Diagram Main Section (5/12) ·················· 46

5-15. Schematic Diagram Main Section (6/12)·················· 47

5-16. Schematic Diagram Main Section (7/12)·················· 48

5-17. Schematic Diagram Main Section (8/12)·················· 49

5-18. Schematic Diagram Main Section (9/12)·················· 50

5-19. Schematic Diagram Main Section (10/12)················ 51

5-20. Schematic Diagram Main Section (11/12)················ 52

5-21. Schematic Diagram Main Section (12/12)················ 53

5-22. Printed Wiring Board Main Section ·························· 54

Main Section (1/4) ····················································· 55

Main Section (2/4) ····················································· 56

Main Section (3/4) ····················································· 57

Main Section (4/4) ····················································· 58

5-23. Printed Wiring Board Mute Section ·························· 59

5-24. Schematic Diagram AUDIO Section························· 60

5-25. Printed Wiring Board Audio Section························· 61

5-26. Schematic Diagram Level Meter Section·················· 62

5-27. Printed Wiring Board Level Meter Section··············· 63

5-28. Schematic Diagram LCD Section ····························· 64

5-29. Printed Wiring Board LCD Section ··························65

5-30. Schematic Diagram Switch Section ·························· 66

5-31. Printed Wiring Board Switch Section ······················· 67

5-32. Schematic Diagram Foot Switch Section·················· 68

5-33. Printed Wiring Board Foot Switch Section ··············· 69

5-34. Schematic Diagram Volume/Serial I/O Section ········ 70

5-35. Printed Wiring Board Volume/Serial I/O Section ·····71

5-36. Schematic Diagram Line Selector Section················ 72

5-37. Printed Wiring Board Line Selector Section ············· 73

5-38. IC Pin Function Description ······································ 74

5-39. IC Block Diagrams····················································· 77

6. EXPLODED VIEWS

6-1. Cabinet Section ·························································· 85

6-2. Key Section ································································ 86

6-3. LCD Section······························································· 87

6-4. Connector Section ······················································ 88

6-5. MD Mechanism Section

(CCMD-2000) (Deck-A/Deck-B) ······························ 89

7. ELECTRICAL PARTS LIST ·································· 90

Flexible Circuit Board Repairing

• K eep the temperature of the soldering iron around 270°C during

repairing.

• Do not touch the soldering iron on the same conductor of the

circuit board (within 3 times).

• Be careful not to apply force on the conductor when soldering or

unsoldering.

Notes on chip component replacement

• Never reuse a disconnected chip component.

• Notice that the minus side of a tantalum capacitor may be damaged by heat.

2

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK ! OR DOTTED LINE WITH

MARK !ON THE SCHEMATIC DIAGRAMS AND IN THE PARTS

LIST ARE CRITICAL TO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY PARTS WHOSE

PART NUMBERS APPEAR AS SHOWN IN THIS MANUAL OR IN

SUPPLEMENTS PUBLISHED BY SONY.

Page 3

MDCC-2000

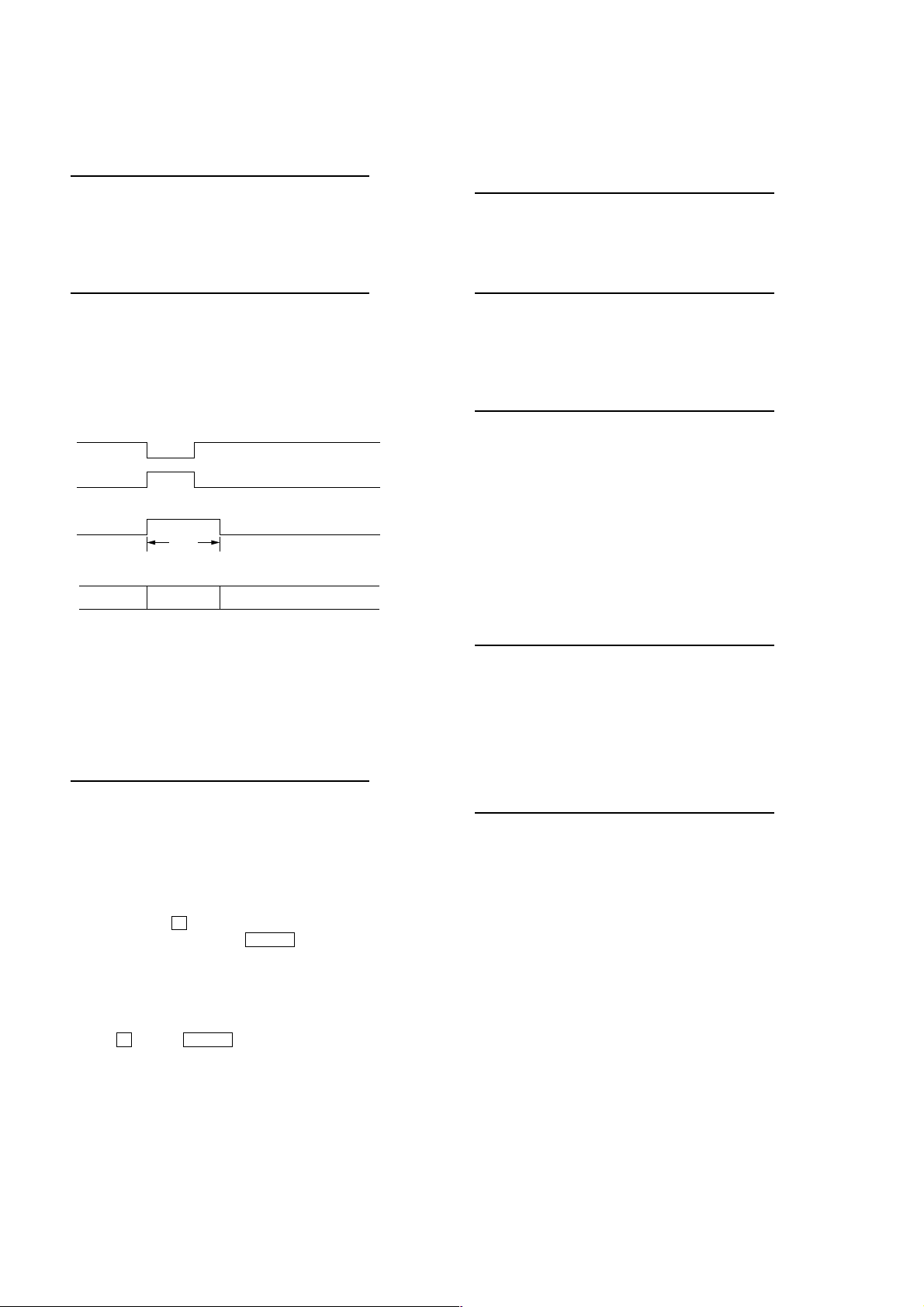

Unleaded solder

Boards requiring use of unleaded solder are printed with the leadfree mark (LF) indicating the solder contains no lead.

(Caution: Some printed circuit boards may not come printed with

the lead free mark due to their particular size.)

: LEAD FREE MARK

Unleaded solder has the following characteristics.

• Unleaded solder melts at a temperature about 40°C higher than

ordinary solder.

Ordinary soldering irons can be used but the iron tip has to be

applied to the solder joint for a slightly longer time.

Soldering irons using a temperature regulator should be set to

about 350°C.

Caution: The printed pattern (copper foil) may peel away if the

heated tip is applied for too long, so be careful!

• Strong viscosity

Unleaded solder is more viscous (sticky, less prone to flo w) than

ordinary solder so use caution not to let solder bridges occur such

as on IC pins, etc.

• Usable with ordinary solder

It is best to use only unleaded solder but unleaded solder may

also be added to ordinary solder.

NOTES ON HANDLING THE OPTICAL PICK-UP

BLOCK OR BASE UNIT

The laser diode in the optical pick-up block may suffer electrostatic

break-down because of the potential difference generated by the

charged electrostatic load, etc. on clothing and the human body.

During repair, pay attention to electrostatic break-down and also

use the procedure in the printed matter which is included in the

repair parts.

The flexible board is easily damaged and should be handled with

care.

NOTES ON LASER DIODE EMISSION CHECK

Never look into the laser diode emission from right above when

checking it for adjustment. It is feared that you will lose your sight.

CAUTION

Use of controls or adjustments or performance of

procedures other than those specified herein may result in

hazardous radiation exposure.

3

Page 4

MDCC-2000

SECTION 1

GENERAL

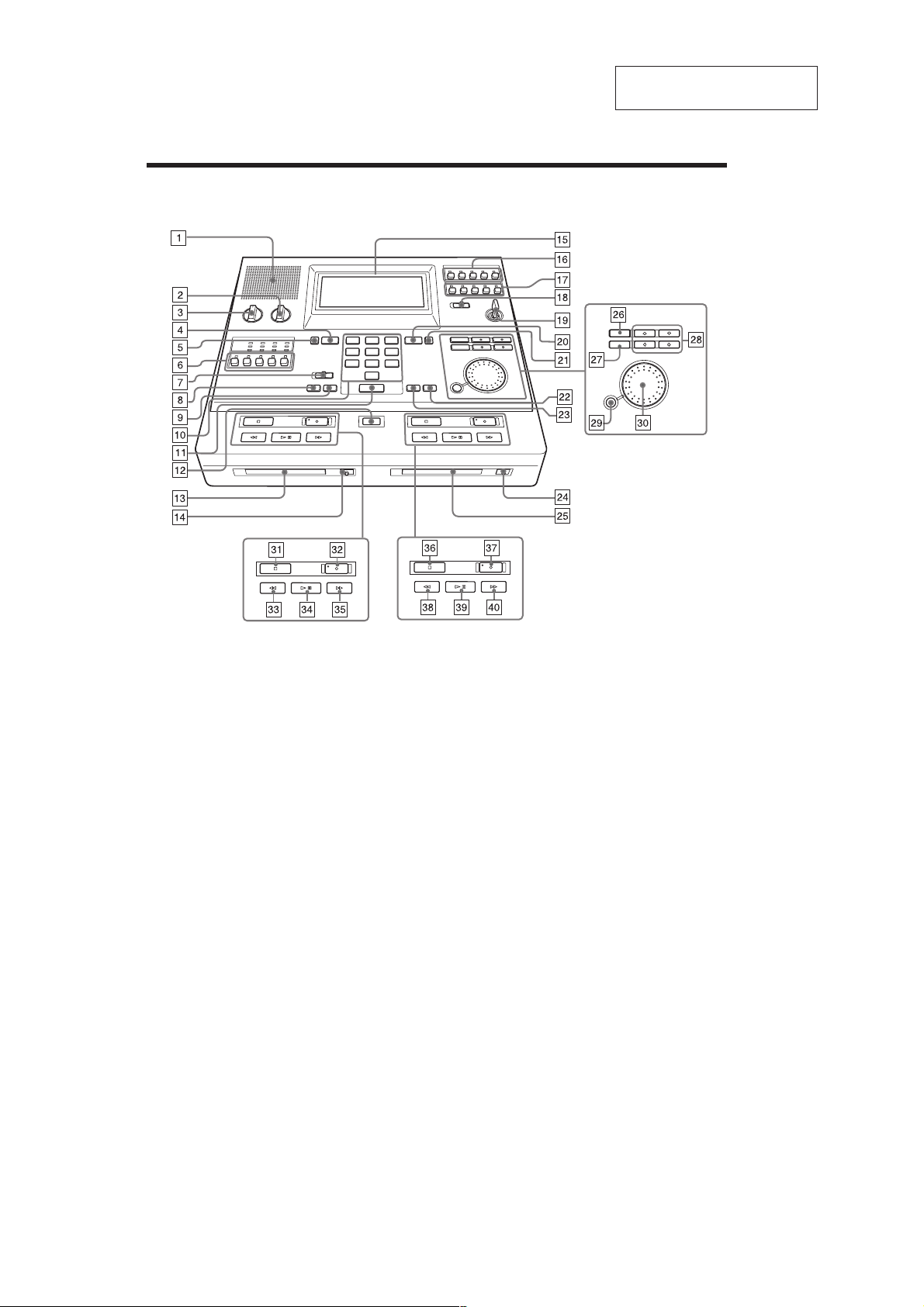

Location and Function of Controls

For details, refer to the pages indicated in ( ).

This section is extracted from

instruction manual.

1 Built-in speaker

2 LCD CONTRAST control

Adjusts the contrast of the display.

3 MONITOR VOL control

4 DECK A button (17, 18)

5 DISPLAY MODE A button (21)

6 MONITOR select buttons (ALL/1/2/3/4)

7 SEARCH selector (17, 18)

(INDEX SEARCH/TIME SEARCH)

8 POINT SEARCH·POINT button (deck A) (20)

9 POINT SEARCH·RESET button (deck A) (20)

q; Number buttons

qa SEARCH button (17, 18)

qs INDEX button (14)

qd MD insertion slot (deck A)

qf Z EJECT button (deck A)

qg LCD display

qh LINE OUT 1 select buttons (ALL/1/2/3/4) (31)

qj LINE OUT 2 select buttons (ALL/1/2/3/4) (31)

qk PA/ADA selector (OFF/ON [ADA/PA]) (30)

Switches the output to the PA/ADA jacks on

or off.

ql STANDBY switch

Introduction

4

w; DECK B button (17, 18)

wa DISPLAY MODE B button (21)

ws POINT SEARCH·RESET button (deck B) (20)

wd POINT SEARCH·POINT button (deck B) (20)

wf Z EJECT button (deck B)

wg MD insertion slot (deck B)

wh FUNCTION button

wj DELETE button

wk Arrow buttons

wl ENTER button

e; Jog dial

ea x STOP button (deck A)

es z REC button (deck A)

ed m REW/BS button (deck A)

ef u PLAY/PAUSE button (deck A)

eg M FF/FS button (deck A)

eh x STOP button (deck B)

ej z REC button (deck B)

ek m REW/BS button (deck B)

el u PLAY/PAUSE button (deck B)

r; M FF/FS button (deck B)

4

Page 5

6

Introduction

1 A: display (deck A)

Indicates the disc inserted in deck A or the

status of deck A as follows:

BLANK: a blank disc

NO DISC: no disc

PB ONLY: a commercially available recorded

disc (for playback only)

PROTECTED: a protected disc (3)

RECORDED: a recorded disc

2 TIME display (deck A)

Indicates the recorded time at the current

location for each index item. It blinks during

time search. (18)

3

(copied) display (deck A)

Indicates that a disc digitally copied with the

Copy function is inserted. (26)

4 INDEX counter (deck A)

Lights up when a disc is inserted.

Blinks during an index search. (17)

5 END display (deck A)

This shows the end of the disc.

6 Disc status display (deck A)

Indicates the status of the disc with pictures.

7 DECK A/DECK B display

Indicates various data by characters and various

error messages. (38)

8 Disc position display

Indicates the current playback/recording location

on the disc by a white box. Already recorded

parts are indicated in black. The further it is to

the right, the closer the disc is to the end.

Depending on the condition of the disc, the black

part might not reach the far right even if the disc

is full.

9 DATE/TIME display

Indicates the current date and time.

0 B: display (deck B)

Indicates the same contents as deck A.

qa TIME display (deck B)

qs

(copied) display (deck B)

qd Disc status display (deck B)

qf END display (deck B)

qg INDEX counter (deck B)

qh REC MODE display

Indicates the recording mode (2ch/4ch) currently

selected.

Display Window (Information screen)

1

2

3

4

5

6

7

8

9

0

qa

qs

qd

qf

qg

qh

9

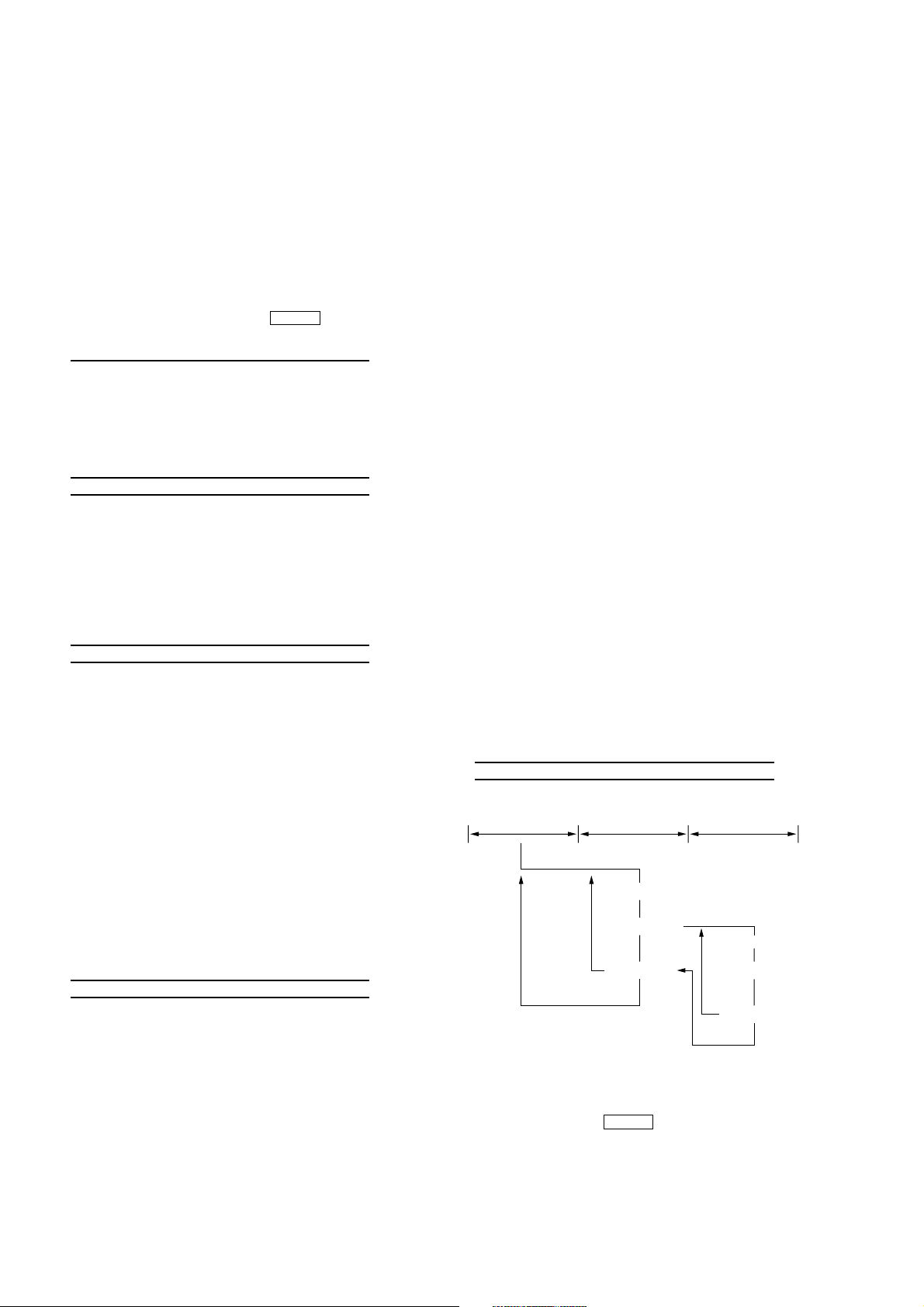

Setting Up

1

Carry out steps 2 and 3 of “Setting the Date”.

You will see the CALENDER or CLOCK INPUT screen.

2

Select CLOCK using the jog dial or the arrow buttons, and

press ENTER.

You will see the SET HOUR (hh) and MINUTE (mm) screen with the

hours and AM/PM blinking.

3

Set the hour using the jog dial or J/j buttons, and press

ENTER.

You will see the minutes blinking.

4

Set the minutes in the same way as step 3.

The display will return to the information screen and the clock will

start.

blink

Note

You cannot use the K/k buttons

when setting the hour and minute.

Setting the Time

2, 3, 4

Left side

Rear

ra CONTROL UNIT connector (32)

rs TRANSCRIBE selector (33)

rd REMOTE jack (15)

rf EAR jack (16)

rg PC connector (RS-232C type)

rh DISPLAY connector

Used for connection of an external

counter unit.

rj ADA jack

Allows the unit to be connected to a

separately purchased amplifier

system.

rk PA (public address) jack (30)

rl LINE OUT jacks

t; LINE IN jacks

ta DC IN 12V

ts Microphone connectors

(Canon XLR-3-31 type)

MDCC-2000

Setting the Date and Time

To record the date and time

etc. on MiniDiscs when you

record, be sure to set the Date

and Time.

Note

You cannot use the K/k buttons

when setting the month, day and

year.

Setting the Date

1 Insert the key and set it to ON.

You will see the initial screen in a few seconds.

2 Press FUNCTION.

3 Select CALENDAR,CLK using the jog dial or the arrow

buttons, and press ENTER.

You will see the CALENDAR or CLOCK INPUT screen.

4 Select CALENDAR using the jog dial or the arrow buttons,

5 Set the month using the jog dial or J/j buttons, and

and press ENTER.

You will see the SET MONTH (mmm) and DAY (dd) and YEAR (yy)

screen with the name of a month blinking.

blink

press ENTER.

You will see “01” of the day blinking.

Introduction

1

2

3, 4, 5, 6

5

8

Setting Up

6 Set the day and the year in the same way as step 5.

When the year is set, the display will return to the information screen.

5

Page 6

MDCC-2000

)

SECTION 2

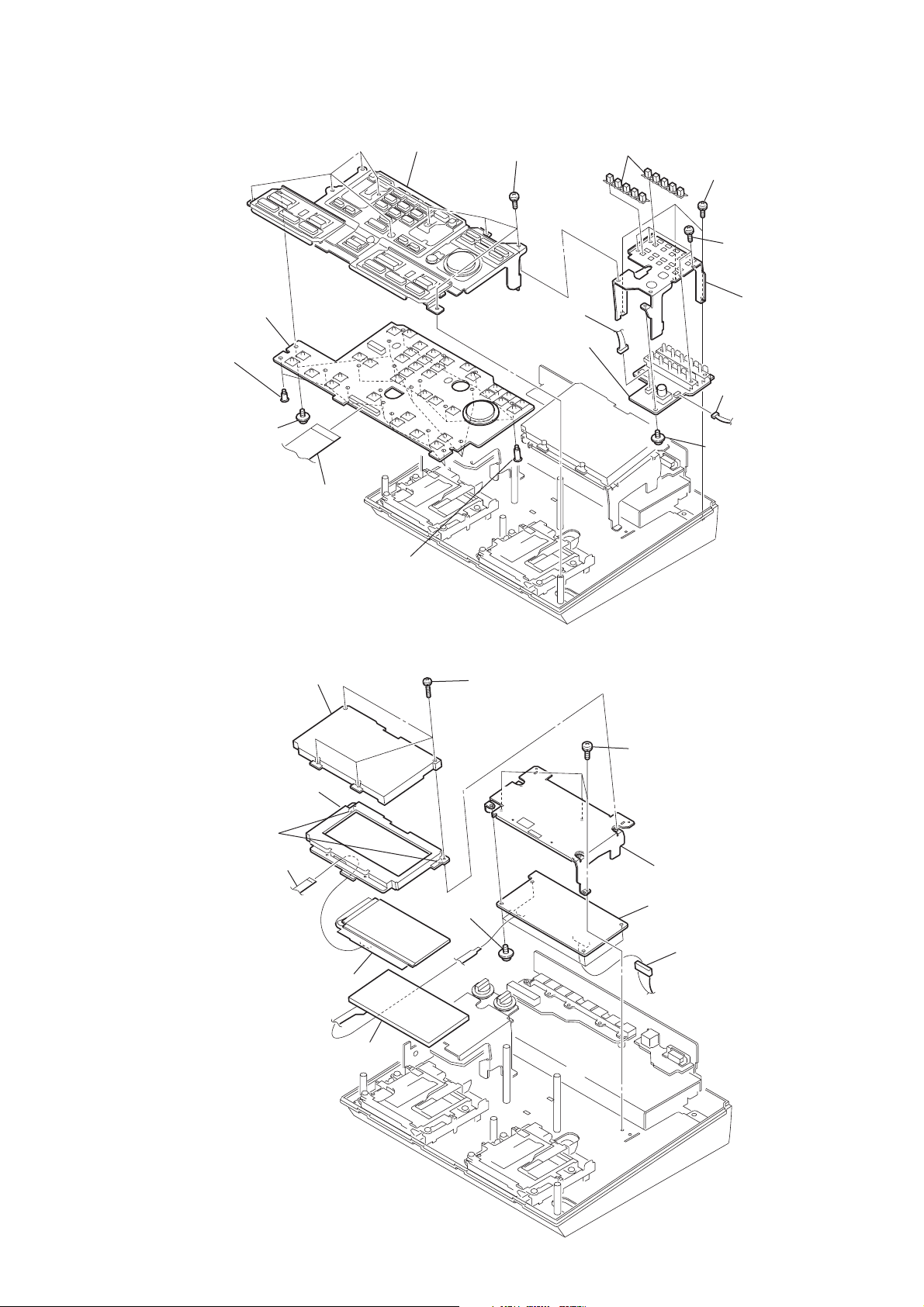

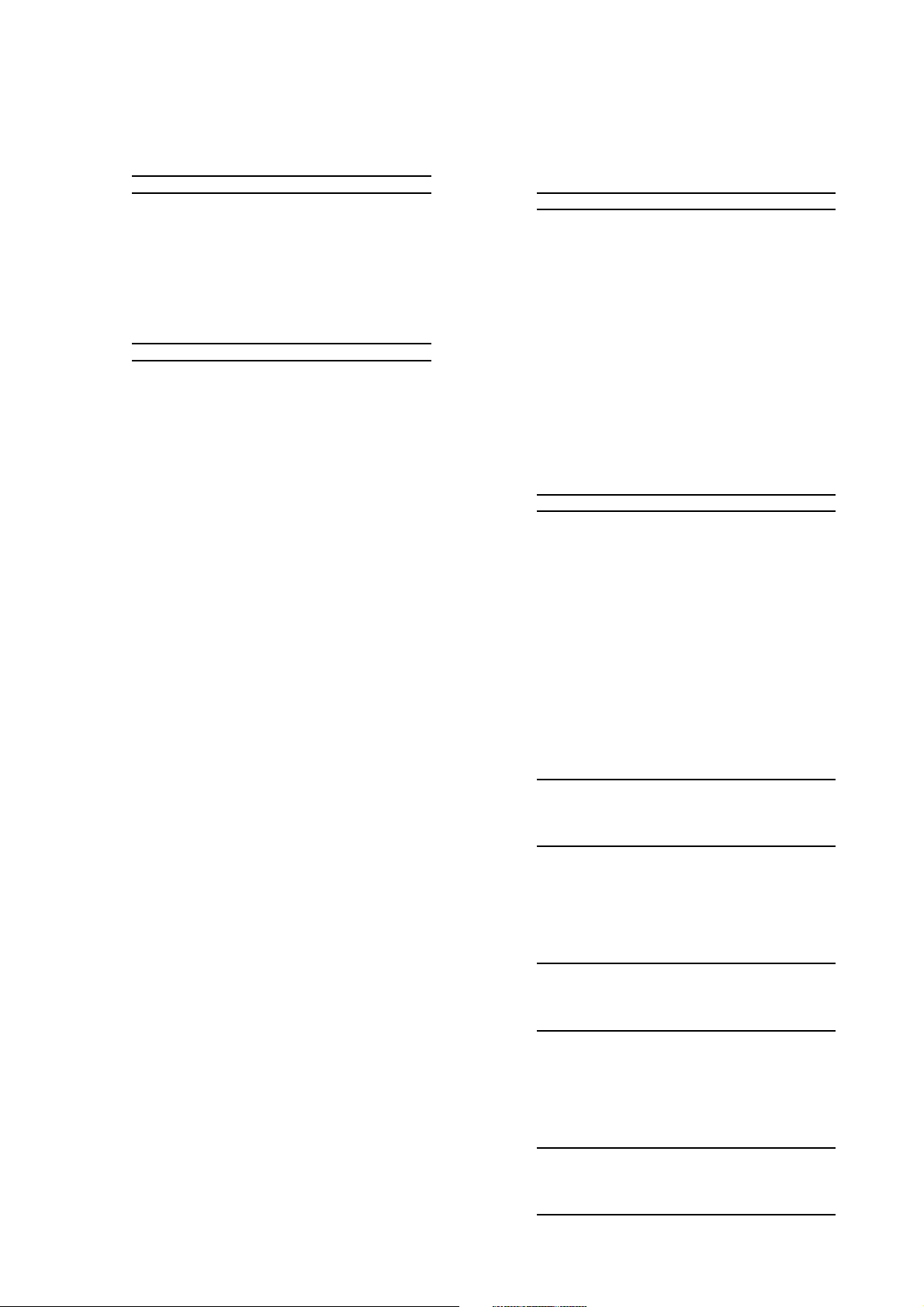

DISASSEMBLY

• The equipment can be removed using the following procedure. • Disassemble the unit in the order as shown below.

Set

Cabinet (upper) section

Switch section

LCD section

I/O section

Door

MD board

Base unit section

BUM-F1 board

REC/PB head assy (HR901) section

Holder assy, cartridge installation Optical pick-up (KMS-250A) section

Note : Follow the disassembly procedure in the numerical order given.

2-1. CABINET(UPPER) SECTION

Main board

Volume section

Connector section

Holder assy, cartridge section

Cabinet (upper) assy

3

Four claws

4

Connector

(CN9102)

2

Three s

crews (+PSW4

× 1

6)

1

Two s

crews (+PSW4

× 1

6

6

Page 7

2-2. SWITCH SECTION

7

SWITCH board

5

Eight s

(STEP M2)

6

(+PSW 3

crews

Five screws

×

MDCC-2000

3

Key switch

block assy

qa

6)

2

Nine

screws

(+PS 3

Connector (CN9301)

qg

LINE SELECTOR

board

×

qs

Button (5 GANG)

6)

9

Three

(+PS 3

qd

Four

(+PS 3

q;

bracket

8

Connector

(CN9401)

qf

Screw

(+PSW 3

screws

×

6)

screws

×

6)

Selector

×

6)

2-3. LCD SECTION

4

3

Cable, flexible flat

(20 core)

1

Flat cable (90mm)

4

(STEP M2)

2

Plat (LCD), transparent

5

Holder (LCD)

Claws

Eight s

crews

0

Four

(+PSW 3

1

screws

×

Four

6)

screws (+PS 2

×

8)

9

three

screws (+PS 3

qa

LCD bracket

qd

LCD board

×

6)

6

LCD

8

Light unit, back

7

qs

Connector

(CN4001)

7

Page 8

MDCC-2000

d

2-4. I/O SECTION

3

(+PS 3

7

MD mechanism

(Deck-B)

Three screws

×

6)

4

MD mechanism

(Deck-A)

1

Cable, flexible

flat (17 core)

6

Four screws

(+PS 3

×

6)

2

Screw

(+PS 3

5

×

Cable,

flexible

flat

(17 core)

6)

8

Connector(CN9101)

q;

AUDIO I/O board

9

Five screws

(+PSW 3

qd

S

qf

SERIAL I/O boar

× 8

)

crew (M2 × 3)

qa

Connector

(CN7001)

qs

Two s

crews

2-5. VOLUME SECTION

7

Two spacers (CABINET UPPER)

qg

Screw

(+PSW 3

qd

(CN9001)

qh

×

Connector

FOOT SWITCH board

6

Two nuts (PUSH 1.5)

9

Two screws (+PS 3

qf

Two screws

8)

(+PSW 3

5

Knob(VOL)

4

Level meter blacket

2

Connector

(CN9201)

×

6)

×

6)

qs

Connector

(CN8001)

3

Three screws (+PS 3

1

Connector(CN6002)

qa

LEVEL METER board

0

Screw

(+PSW 3

×

×

8

VOLUME board

6)

6)

8

Page 9

s

2-6. MAIN BOARD

8

7

Four screws

(+PSW 3

MAIN board

×

6)

3

Connector

(CN1007)

MDCC-2000

2

6

Connector(CN111)

5

Four connectors

(CN101,CN102,CN103,CN104)

2-7. CONNECTOR SECTION

7

Eight connectors

(RECEPTACLE) 3p

4

Two flexible

flat cable

(17 core)

5

Indication plate

(CANON)

1

4

Three screws

(M 2 × 3)

Cabinet (lower)

6

Sixteen

(M 2

×

6)

screw

2

Three

(M 2 × 3)

screws

1

Three

(M 2

screws

×

3)

3

Shield plate

8

Sheet, Insulating

9

Page 10

MDCC-2000

d

2-8. DOOR

2-9. MD BOARD

spring, door return

1

Release the hook.

5

Tw o

screws

(M 2

×

3

Door

2

Release the boss.

6

MD board

4

Tw o

screws

(M 2

×

3)

3)

10

1

Frexible wire

(18 core, CN5)

2

Frexible board

(CN3)

3

Frexible boar

(CN1)

Page 11

2-10. BASE UNIT SECTION

3

Two screws (step)

5

Base unit

4

Two screws (step)

1

S

crew

(toothd lock M 2

MDCC-2000

×

3.5)

2-11. BUM-F1 BOARD

4

Two s

(precision +M 1.7

crews

5

claw

×

2.2)

7

BUM-F1 board

2

6

Lug, 2

claw

3

Flexible board

(CN302)

2

Frexible board

(CN304)

1

Plam flexible board

(CN303)

11

Page 12

MDCC-2000

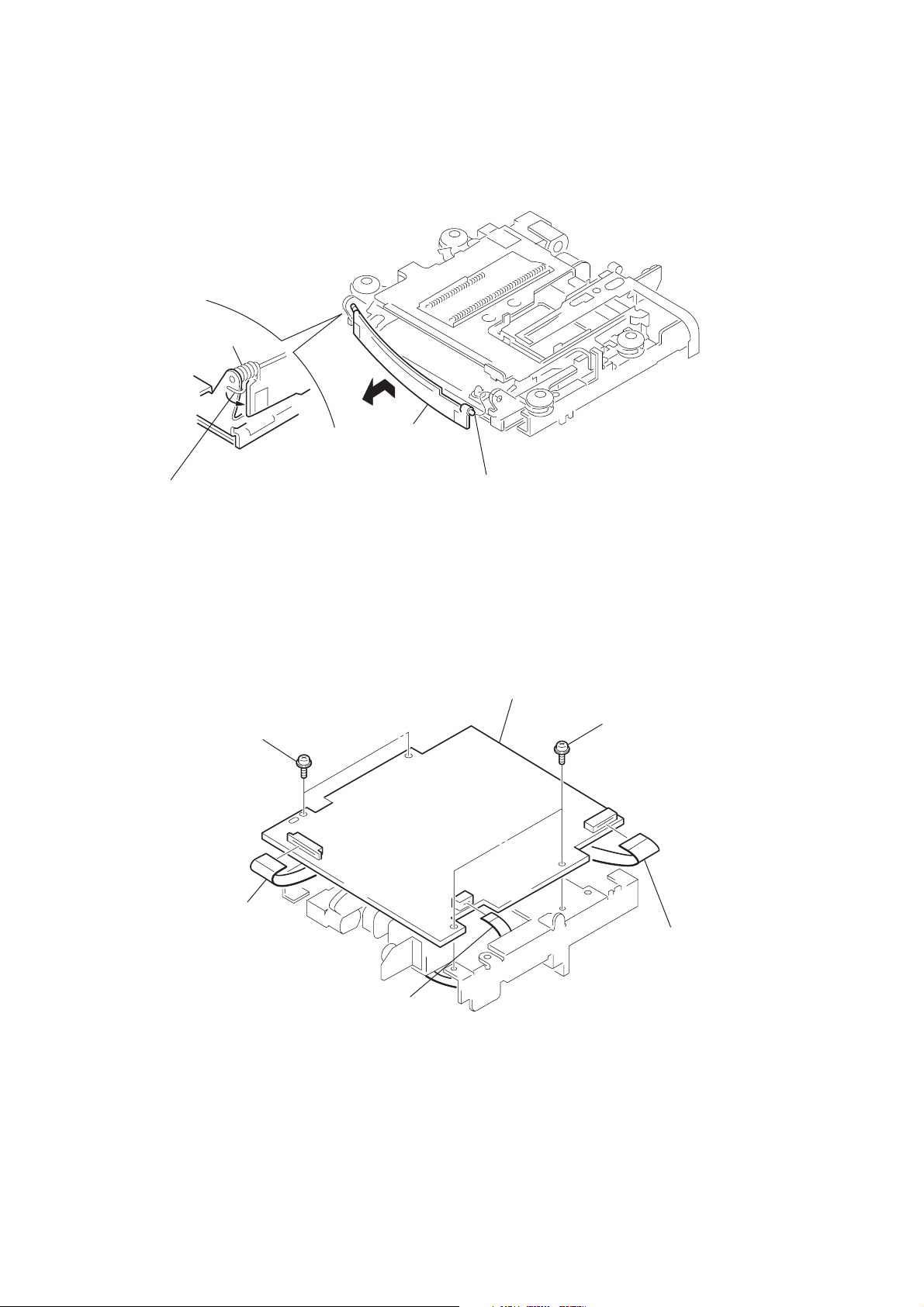

2-12. REC/PB HEAD ASSY (HR901) SECTION

2

Lug, 2

1

S

crew

(toothd lock M 2

×

3.5)

5

G

uide, screw

4

S

crew

(toothed lock M 1.4)

6

Tw o

screws

(M 1.7

×

2.8)

3

Motor, DC geared

(M903)

2-13. HOLDER ASSY, CARTRIDGE SECTION

2

While releasing the four bosses, remove

the cartridge holder assembly in the

direction of the arrow

C

.

Boss

8

REC/PB head assy

(HR901)

1

the arrows

7

removed hook

Push it in the direction of

A

and B with fingers.

A

B

12

Boss

Boss

C

Boss

Page 13

)

2-14. HOLDER ASSY, CARTRIDGE INSTALLATION

When installing the cartridge holder, coat

the portion A shown in the illustration with

grease (EM-30L).

A

Position

A

Position

MDCC-2000

2-15. OPTICAL PICK-UP (KMS-250A) SECTION

4

Spring, g

uide shaft retainer

3

Two screws

(precision, +P 1.7

×

2.2)

A

Position

5

(M 1.7

Two screws

×

4.5)

6

Two washers

2

Motor, stepping

(M902)

1

Two screws

(precision, +P 1.7

×

2.2)

7

Optical pick-up (KMS-250A

13

Page 14

MDCC-2000

SECTION 3

TEST MODE

3-1. Description

3-1-1. How to Enter the Test Mode

After pressing the numeric keys in the order starting from 1 , 2

, 3 , 5 , 8 up to 0 , press the F button.

3-1-2. How to Exit the Test Mode

1. While pressing the G button, rotate the JOG dial and set

“k_test_h” to “0”.

2. After pressing the numeric keys in the order starting from 0 ,

8 , 5 , 3 , 2 up to 1 , press the F button.

3-1-3. How to Cancel the ENTER key

The numeric keys that have been input up to the moment can be

canceled at the following so that the machine does not enter the

test mode unless otherwise needed.

1. When the interval of pressing the previous numeric key and

the next key exceeds one second or more.

2. When the deck select key is pressed.

3. When the k_mode changes.

4. When the selected deck has changed.

5. When the test mode is set.

3-1-4. How to Select the Test Item

The test item can be selected by “k_test_h” and “k_test_l”.

1. Displaying the selected item

The selected item is displayed on LCD as follows.

Value of “k_test_h” (Displayed in hexadecimal number)

Value of “k_test_l” (Displayed in hexadecimal number)

3-1-5. T est Display

01 - 00 (Top menu)

00 - 00 EXIT (Exit)

01 - 00 THIS MENU (Top menu)

02 - 00 AUDIO (Audio firmware test)

03 - 00 MECH (Mechanism test)

04 - 00 DISPLAY (Display system test)

05 - 00 KEY (Key test)

06 - 00 COMMUNICATION (Communication test)

07 - 00 AUDIO HW (Audio hardware test)

08 - 00 DIGITAL HW (Digital hardware test)

09 - 00 NVRAM (NVRAM test)

3-1-6. Communication with Mechanism Deck

Communication with the mechanism deck is performed using

programs such as “Hyper terminal” or the like that have been

started up on a PC.

Refer to 3-3-3. “Selecting the Terminal”.

(Communication control with the log system or trace monitor is

not possible.)

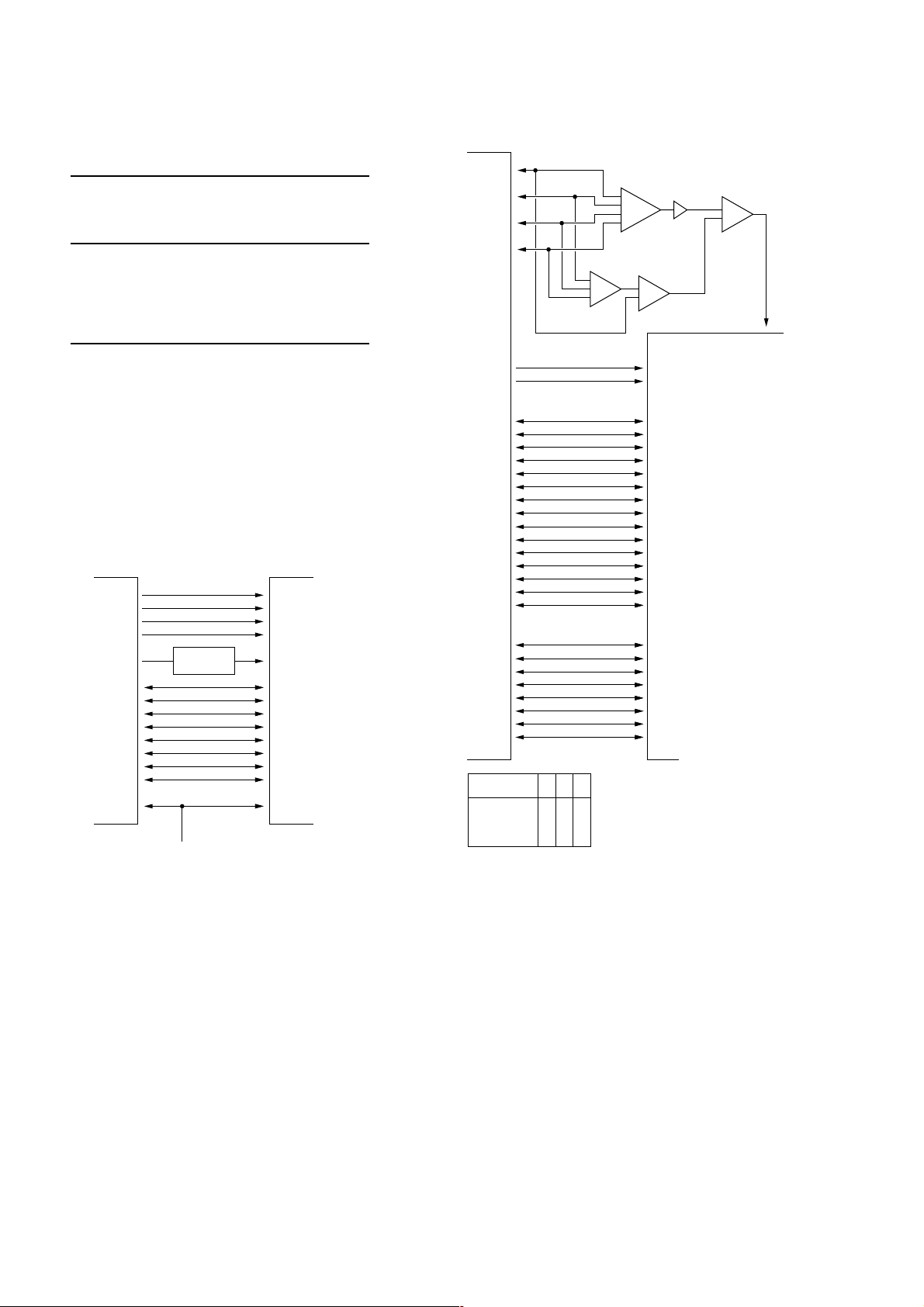

3-1-7. Circuit Block

General purpose port

KEY

CPU

CPU bus

NVRAM

ROM

CLOCK

SRAM

DRAM

05 - 01

/* KEY INCREMENT TEST */

2. How to select the test item using the JOG dial

1. While pressing G b utton, rotate the JOG dial. “k_test_h”

changes.

When “k_test_h” changes, “k_test_l” is set to “0”.

Select the desired test category using “k_test_h”.

2. While pressing g button, rotate the JOG dial. “k_test_l”

changes.

Select the desired test item using “k_test_l”.

3. Sets the selected test item either by pressing g button

after selecting “k_test_l” or by pressing the ENTER

button.

3. How to select the test item with the use of the PC remote

command

The desired test item can be selected by sending the remote

command of rewriting “k_test_h” and “k_test_l” from the PC

to the machine.

When the “k_test_h/l” change command is sent from a PC to

the machine while the “k_test_h/l” change inhit bit is being

set, the machine returns NAK and the machine does not chanage

“k_test_h/l”.

1809

DECK A DECK B

CODEC

FIFO8655

LCD

AD/DA

3-2. Audio Firmware Test: [AUDIO]

SF data storage method in the DRAM.

• Test program is stored as shown below.

(Operations start in the order starting from channel 1, channel 2,

channel 3, and up to channel 4 under the ordinary operation

conditions but the test mode starts from channel 1, channel 3,

channel 2, and channel 4 in this order.)

0123

1chSF

3ch 2ch 4ch

FIF012 CXD1858 1.2ch

FIF034 CXD1858 3.4ch

LCD: Types, conditions and others of the test are displayed on

the LCD during each test.

Channel selector and channel selector LED: Select the channel

selector by manual operation.

Voice mirror: Change the input level by manual operation.

14

• Perform the following tests after the machine is set in the “STOP”

mode.

02-00 /* AUDIO-F TEST MENU */

02-00 AUDIO-F MENU

Page 15

MDCC-2000

3-2-1. Audio Recording and Playback Test without Disc

• The audio signal (up to the full memory capacity of the DRAM

at a maximum) is recorded in the ATRAC data recording area in

the DRAM and is played back.

• Note: If the audio sources of channel 1 to channel 4 are all the

same,

• Playback is slower than normal if the 4 channels are recorded

and 2 channels are played back.

(The pitch of the playback remains unchanged and the

playback speed of it is half of normal.)

• Playback is faster than normal if the 2 channels are recorded

and 4 channels are played back.

(The pitch of the playback remains unchanged and the speed

of it is double of normal.)

02-01 4ch-REC on DRAM

02-02 4ch-PLAY on DRAM

02-03 2ch-REC on DRAM

02-04 2ch-PLAY on DRAM

02-05 reserve

02-06 reserve

3-2-2. Microphone Sound Monitoring from Speaker during Stop

• Application: For testing “ripping” sound of speak er (Sweep sound

is input from external source.)

• Application: For testing the voice mirror LED (sound is input

from external source.)

02-07 REC_MONI, SP, 1-4ch

3-2-5. Audio Muting T est

• ROM_PB (990Hz, -0.2dB, 1 to 4ch)

02-19 XMUTE=on, MODE=00, (During ROM_PB, circuit playback + mute)

02-1A XMUTE=on, MODE=01, (During ROM_PB, circuit recording + mute)

02-1B XMUTE=on, MODE=10, (During ROM_PB, circuit STOP + mute)

02-1C XMUTE=on, MODE=11, (During ROM_PB, circuit STANDBY + mute)

02-1D XMUTE=off, MODE=00, (During ROM_PB, circuit is in playback.)

02-1E XMUTE=off, MODE=01, (During ROM_PB, circuit is in record.)

02-1F XMUTE=off, MODE=10, (During ROM_PB, circuit is STOP.)

02-20 XMUTE=off, MODE=11, (During ROM_PB, circuit is STANDBY.)

3-3. Mechanism Deck: [MECH]

03-00 /* MD TEST MENU */

01-0E .....etc

10-1F DECK-A Only (Check & Setting)

20-2F DECK-B Only (Check & Setting)

30-3F DECK-A Only (Display Log)

40-4F DECK-B Only (Display Log)

50-57 Laser Check

3-3-1. Displaying the Number of Times of Using the Lasers

The number of times of using the lasers of the deck-A and deckB is displayed.

The number of times of using the lasers is stored in the NVRAM,

and the number of times that the laser power has entered the MO

write (number of clusters), is displayed.

3-2-3. ROM Playback 1

• The pseudo ATRAC data on the EPROM is copied to the 1SG

area on the DRAM and is played back repeatedly.

• Application: Level/Frequency response test

02-08 990Hz, -0.2db, 1-4ch (For playback of the reference level)

02-09 43Hz, -0.2db, 1-4ch

02-0A 10KHz, -0.2db, 1-4ch

02-0B 990Hz, -12db, 1-4ch

02-0C Infinity, 0, 1-4ch (For S/N test)

3-2-4. ROM Playback 2

• The pseudo ATRAC data on the EPROM is copied to the 1SG

area on the DRAM and is played back repeatedly.

• Application: Separation/Frequency response test

• Other channels : No sound

02-0D 990Hz, -0.2db, 1ch

02-0E 990Hz, -0.2db, 2ch

02-0F 990Hz, -0.2db, 3ch

02-10 990Hz, -0.2db, 4ch

02-11 43Hz, -0.2db, 1ch

02-12 43Hz, -0.2db, 2ch

02-13 43Hz, -0.2db, 3ch

02-14 43Hz, -0.2db, 4ch

02-15 10KHz, -0.2db, 1ch

02-16 10Hz, -0.2db, 2ch

02-17 10Hz, -0.2db, 3ch

02-18 10Hz, -0.2db, 4ch

03-01

DECK-A Laser Cnt = xxxxxxxx

DECK-B Laser Cnt = xxxxxxxx

3-3-2. Displaying Temperature of Mechanism

The temperatures of the mechanism of deck-A and deck-B are

displayed.

The temperature of mechanism indicates the temperature inside

the RF amplifier mounted on this machine. However, use this

temperature as a reference value because it is not highly accurate.

03-02

Thermo

DECK-A 35˚C

[Result] = [55] [0B] [58] [62] [07] [09] [09]

DECK-B 31˚C

[Result] = [55] [0B] [58] [5F] [06] [06] [06]

3rd byte of the above [Result] data string : Initial value of the

temperature sensor at 25˚C

4th byte of the above [Result] data string : Present temperature

sensor value

3-3-3. Selecting the Terminal

Select the PC terminals (RS-232C) on the rear of this machine.

Either one of the two patterns “Other” and “Mech”, can be

selected.

Other : For checking contents, etc of the system memory

Mech : For checking status of the mechanism operation

03-0A

Terminal Mode = Mech

15

Page 16

MDCC-2000

The PC should use the terminal software (such as Hyper-T erminal

or Tera-Term).

Sets the communication as follows.

Baud rate : 9600 bps

Data length : 8 bits

Parity : None

Stop bit : 1

Flow control : None

3-3-4. Dump List

Displays the Dump-List of the specified address.

Sets the address value (Adrr) and number (Num) of display bytes

by rotating the JOG dial and pressing ENTER button.

03-0D

Adrr = 00000000 Num = 00

3-3-5. Deleting (Deck-A/Deck-B)

Performs deletion of the disc data.

03-14 (DECK-A)

03-24 (DECK-B)

3-3-6. OA (Inner track, Middle track and Outer track) (Deck-A/

Deck-B)

Performs the OA (overall) test against the inner track (UTOC

area)/Middle track/Outermost track.

Performs “Write”, “Read”, and “Verify” for every 1 cluster as

many as 10 clusters in each area.

03-15 (DECK-A)

03-25 (DECK-B)

Result display

When the OA test of each area has ended with success, the

following message appears on the LCD.

When the “Mech” position of the terminal is selected, the test

status can be checked as follows.

Description of the contents displaying the test status

Example of display

$$ TEST-drv [CNT] (W/R/D/S) (TW/TR) (Result)

drv : Drive No.

CNT : Number of times of test

W : Number of times of “Write” error

Number of times of the write failure for the single

write command (“Seek” error is not included.)

R : Number of times of “Read” error

Number of times of the read failure for the single

read command (“Seek” error is not included.)

D : Number of times of alternation

Number of times of giving-up to write into the

specified cluster

S : Number of times of “Seek” error

Number of times that “Seek” error has occurred

TW : Number of times of TOC “Write” error

Number of times of the TOC write failure for the

single TOC “Write” command (“Seek” error is no

included.)

TR : Number of times of TOC “Read” error

Number of times of the TOC read failure for the

single TOC “Read” command (“Seek” error is no

included.)

Result : Test result up to present (1 : OK, 0 : NG)

Result display

When the OA test has ended with success, the following

message appears on the LCD.

***

Total OK

***

3-3-8. Checking Operations of Mechanism (Deck-A/Deck-B)

Operations of the mechanism are checked using the terminal.

***

Total OK

***

• After the above message appears with normal end, the disc is

ejected automatically.

3-3-7. OA (Overall Test for Normal Recording ) (Deck-A/Deck-B)

The OA test in the same operation as the normal recording is

performed.

The process of “Write”, “Read” and “Verify” is performed for

every 1 cluster starting from the innermost track of the recording

area to the outermost track. Then the “UTOC Write” is performed

for every 10 clusters.

03-16 (DECK-A)

03-26 (DECK-B)

03-17 (DECK-A)

03-27 (DECK-B)

y

Dedicated for

mechanism

Waiting for ’ . ’

y

>>

Mechanism test Prompt

:MON>

Waiting for mdmon

n

Waiting for exit Waiting for command

ny

Operation step

Step 1 : Enters the test mode of the mechanism.

Step 2 : Type in “mdmon” against “MON>” and set it.

Step 3 : Press the ENTER button several times until the

machine enters the test mode dedicated for

mechanism.

Step 4 : Performs the operation check in accordance with

the display output.

Step 5 : Type in “.” to return to “Prompt”.

Step 6 : Type in “exit” to set the operation and exit the

test mode of the mechanism.

n

16

Page 17

MDCC-2000

3-3-9. Eject (Deck-A/Deck-B)

Ejects the disc.

03-18 (DECK-A)

03-28 (DECK-B)

3-3-10. Clearing the Number of Times of Using the Laser

(Deck-A/Deck-B)

The number of times of using the laser is stored, and is cleared as

follows.

It is necessary to clear the number of times data of using the laser

whenever the laser is replaced.

03-19 (DECK-A)

03-29 (DECK-B)

DECK-B Laser Count Clear

NV-RAM Save OK

3-3-11. OA (Overall Test for Random Recording )

(Deck-A/Deck-B)

The (OA) overall test is performed using the same operation as

that of the normal recording.

The “write”, “read”, and “verify” are performed at every cluster

at random within the recording area. The “UTOC write” is

performed at every ten clusters.

The test ends after the specified time has passed.

When the “Mech” position of the terminal is selected, the test

status can be checked as follows.

Description of the contents displaying the test status

Example of display

$$ TEST-drv [CNT] (W/R/D/S) (TW/TR) (Result)

drv : Drive No.

CNT : Number of times of test

W : Number of times of “Write” error

Number of times of the write failure for the single

write command (“Seek” error is not included.)

R : Number of times of “Read” error

Number of times of the read failure for the single

read command (“Seek” error is not included.)

D : Number of times of alternation

Number of times of giving-up to write into the

specified cluster

S : Number of times of “Seek” error

Number of times that “Seek” error has occurred

TW : Number of times of TOC “Write” error

Number of times of the TOC write failure for the

single TOC “Write” command (“Seek” error is no

included.)

TR : Number of times of TOC “Read” error

Number of times of the TOC read failure for the

single TOC “Read” command (“Seek” error is no

included.)

Result : Test result up to present (1 : OK, 0 : NG)

3-3-12. Rescue (2-channel Mode) (Deck-A/Deck-B)

When the UTOC information shows error, the disc can be

recovered as follows.

03-1E (DECK-A)

03-2E (DECK-B)

DECK-A Rescue 2Ch Mode

Disc-Input!!

Result display

Index structure : Only 1 index is used over the entire area

of a disc.

Recording mode : 2-channel mode

Original : Original

Name information : Invalid

Time information : Invalid

3-3-13. Rescue (4-channel Mode) (Deck-A/Deck-B)

When the UTOC information shows error, the disc can be

recovered as follows.

03-1F (DECK-A)

03-2F (DECK-B)

DECK-A Rescue 4Ch Mode

Disc-Input!!

Contents of recovery

Index structure : Only 1 index is used over the entire area

of a disc.

Recording mode : 4-channel mode

Original : Original

Name information : Invalid

Time information : Invalid

3-3-14. Laser Power OFF (Deck-A/Deck-B)

Turns off the laser power.

03-50 (DECK-A)

Laser Power (DECK-A) = OFF

[Result] = [01] [1D] [00] [00] [00] [00] [00]

03-54 (DECK-B)

Laser Power (DECK-B) = OFF

[Result] = [01] [1D] [00] [00] [00] [00] [00]

3-3-15. Laser Power MO-WRITE (Deck-A/Deck-B)

Sets the laser power to the “MO-WRITE”.

03-51 (DECK-A)

Laser Power (DECK-A) = MO-WRITE

[Result] = [01] [1D] [00] [18] [00] [01] [00]

03-55 (DECK-B)

Laser Power (DECK-B) = MO-WRITE

[Result] = [01] [1D] [00] [18] [00] [01] [00]

Result display

When the OA test has ended with success, the following

message appears on the LCD.

***

Total OK

***

3-3-16. Laser Power CD-READ (Deck-A/Deck-B)

Sets the laser power to the “CD-READ”.

03-52 (DECK-A)

Laser Power (DECK-A) = CD READ

[Result] = [01] [1D] [00] [08] [00] [02] [00]

03-56 (DECK-B)

Laser Power (DECK-B) = CD READ

[Result] = [01] [1D] [00] [08] [00] [02] [00]

17

Page 18

MDCC-2000

3-3-17. Laser Power MO-READ (Deck-A/Deck-B)

Sets the laser power to the “MO-READ”.

03-53 (DECK-A)

Laser Power (DECK-A) = MO READ

[Result] = [01] [1D] [00] [08] [00] [03] [00]

03-57 (DECK-B)

Laser Power (DECK-B) = MO READ

[Result] = [01] [1D] [00] [08] [00] [03] [00]

3-4. Display System Test: [DISPLAY]

04-00 /* DISPLAY TEST MENU */

04-01 [LCD_cntr] - [u_com] : connection check

[LCD_cntr] - [h_sram] : connection check

[LCD_cntr] - [LCD] : connection check

04-02 LCD DOT all set

04-03 LCD DOT all clear

04-04 character check on h_sram (SAG1) [1]

04-05 character check on h_sram (SAG1) [2]

04-06 [u_com - [LCD_cntr] : test signal

04-07 transmission of character data

04-08... content of global_area_address

• Connecting the Microprocessor with LCD Controller

Microprocessor

AO

XRD

XHWR

XCS4

16MHz

D15

D14

D13

D12

D11

D10

D9

D8

XRES

Divide-by-2

Reset IC

LCD controller

AO

XRD

XWR

XCS

8MHz

XRES

• Connecting the LCD Controller with SRAM

LCD controller

VA15

VA14

VA13

VA12

VWR

VRD

VA14

VA13

VA12

VA11

VA10

VA9

VA8

VA7

VA6

VA5

VA4

VA3

VA2

VA1

VA0

D7

D6

D5

D4

D3

D2

D1

D0

ADDRESS

0000 to 6FFF

7000 to EFFF

F000 to FFFF

123

H

L

L

H

H

H

L

H

L

AND

AND OR

1

Buff

2

[SRAM]

• 1st layer (Character screen)

0 (0000h) to 9999 (270Fh)

• 2nd layer (Graphic screen)

10000 (2710h) to 19999 (4E1Fh)

• SAG1 (Character storage)

61440 (F000h) to (FFFFh)

3

AND

VCE

18

Page 19

MDCC-2000

• Connecting the LCD Controller with LCD

LCD controller LCD

WF

LP

XSCL

YDIS

YD

D0

D1

D2

D3

XRES

Reset IC

PA4 (Microprocessor)

LP

DELAY

AND

OR

DF

LOAD

CP

FRAME

DISP

3-4-1. Connection Check between Microprocessor and LCD

Controller, and between LCD Controller and SRAM

• Check the checksum of the font and the graphic data that are

transferred to SAG1 (F000h to FFFFh) of the SRAM for display

when releasing the STANDBY mode.

[Calculation is under way.]

04-01

(data read from LCD cntr) = ????????

• When [OK] appears:

Connection between the microprocessor and LCD controller and

the connection between LCD controller and SRAM are correct.

04-01

(data read from LCD cntr) = xxxxxxxx

3-4-2. LCD Dot Check (Lighting All Dots)

Lighting all dots of LCD (Graphic data: By 0xff transfer)

04-02

3-4-3. Checking the LCD Dot (Turning off all dots)

All dots of LCD are turned off. (Graphic data : By 0x00 transfer)

04-03

3-4-4. Test Signal Output from Microprocessor to LCD Controller

Test signal output is under preparation.

04-06

NOW test signal loading...

Test signal is under preparation.

0xff and 0x00 are output repeatedly to the microprocessor ports

D15 to D8 as follows.

About 0.25 S 0.25 0.25 0.25

About 30 seconds

The test signal output ends.

04-06

finished test signal output

3-5. Key Test: [KEY]

05-00

/* KEY TEST MANU */

05-01 KEY INCREMENT TEST

05-02 ANY KEY TEST

05-03 K_mode LOG

[OK]

• When [NG] appears:

1. If the following *NG display is recognized, “XRD” is

suspected.

2. If the following *NG display is not recognized (upon

confirmation through trace monitor), either one of the

connections between microprocessor and LCD controller or

the connection between LCD controller and SRAM or the

connection between LCD controller and LCD is defective.

(At this time, if the test signal is output from the microprocessor

to LCD controller in step 04-06, whether the connection is OK

or NG can be confirmed, and also which of the connections

between LCD controller and SRAM or the connection between

LCD controller and LCD is NG.)

04-01

(data read from LCD cntr) = KKKKKKKK

[NG]

Mabye read pattern NG. or.

[LCD_cntr]-[u_com],[h_sram]: connect NG

3-5-1. Key Test by Pressing Keys in Order

05-01

/* KEY INCREMENT TEST */

Turn ON

⇒ DISPLAY(A)

When the specified “DISPLAY (A)” key is pressed correctly, the

following messages appear.

05-10

/* KEY INCREMENT TEST */

⇒ DISPLAY(A)

OK

Turn OFF

19

Page 20

MDCC-2000

When releasing your finger from the key , the next ke y to be pressed

is specified.

When an incorrect key that is different from the specified one is

pressed, following messages appear.

05-10

/* KEY INCREMENT TEST */

⇒ DISPLAY(A)

NG

Turn OFF

The test cannot be advanced unless the correct key is pressed.

The “Key Test by Pressing Keys in Order” is complete.

(Normally end)

When all of the key pressings are correct,

“COMPLETE”

appears on the LCD screen and type in 05-42.

(Abnormally end)

When the incorrect key is pressed more than once,

“xxxxx

at FAULT”

appears on the LCD screen.

An incorrect key that was detected at first in the order of pressing keys,

is displayed in “xxxxx”.

3-5-2. Key Test by Pressing Arbitrary Key

05-02

/* KEY TEST */

PUSH KEY : OFF (FF/F5-FF)

AD CODE : FF FF FF FF FF FF FF

TRANSCRIBE : A POW : ON

SEARCH MODE : INDEX JOG : 00

Displays the name of the pressed key.

Example : When the STOP button of the deck-A is pressed,

05-05

PUSH KEY : STOP (A) (00/00-09)

appears.

The first 2-digit “00” of (00/00-09) indicate the value that the

pressed key after it is conv erted by AD con verter. The digits “00-

09” indicate the range when the key is judged as “STOP (A)”.

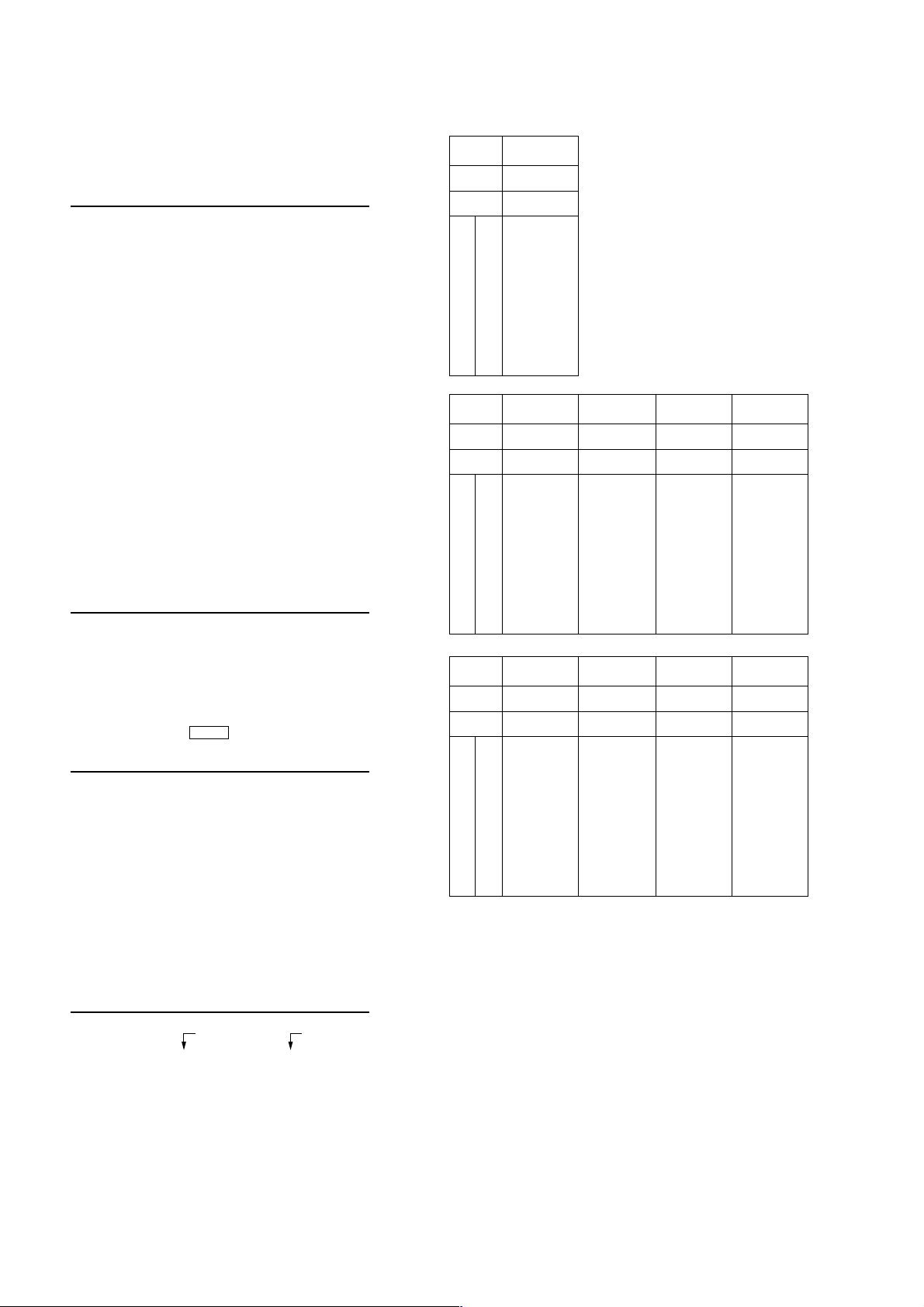

Allocation of key groups and keys

Application

Type

Group

Allocation of Kn

Application

Type

Group

Allocation of Kn

Application

Type

Group

Allocation of Kn

Foot switch

operation

0

FS_PLAY

1

FS_FS

2

FS_BS

3

4

5

6

7

8

9

10

Operation of the

mechanism

0

STOP(A)

1

STOP(B)

2

PLAY/PAUSE(A)

3

REW/REV(A)

4

FF/CUE(A)

5

MARK(A)

6

MARK_OFF(A)

7

8

9

10

FUNCTION

0

f

1

F

2

DEL

3

<(LEFT)

4

>(RIGHT)

5

6

7

8

9

10

ANALOG

0

ANALOG

1

Function

ANALOG

5

Operation of the

mechanism

ANALOG

2

REC(A)

REC(B)

PLAY/PAUSE(B)

REW/REV(B)

FF/CUE(B)

MARK(B)

MARK_OFF(B)

Function

ANALOG

6

ENTER

DISP_MODE(A)

DISP_MODE(B)

Operation of the

mechanism

ANALOG

3

INDEX

EJECT(A)

EJECT(B)

DECK_A

DECK_B

SEARCH

Function

ANALOG

7

REC_PAUSE

Search

ANALOG

4

0

1

2

3

4

5

6

7

8

9

10

Power supply,

etc.

DIGITAL

8

Use is prohibited

Use is prohibited

A/B(FS)

INDEX/TIME

STANDBY/ON

AD CODE

Displays values when the key inputs are converted by AD

converter, in the order starting from 0 up to 7 from the left of

the LCD screen.

05-05

Group 0

AD CODE : FF FF FF FF FF FF FF

Group 7

20

Page 21

MDCC-2000

3-6. Communication Test: [COMMUNICATION]

• RS232-C connector

When the pin-2 and pin-3 of the RS232-C connectors are

connected, two values are displayed in the 2-digit hexadecimal

values respectively on the LCD screen, one is the send data and

the other is data that have been received by the loop-back.

Display example

Tx DATA 57 ← Send data.

Rx DATA 57 ← Received data.

The value of the receiv ed data follows a little bit delayed after the

send data.

The send data increments at every about 0.5 seconds.

• Modular jack

When pin-2 and pin-3 of the modular jack are connected to pin3 of the RS232-C connector, the same test can be done.

• Communication packet

The status packet is used.

Packet size = 38 bytes

06-00

/* PC_I/F LOOP BACK */

Tx DATA = xx

Rx DATA = xx

3-7. Audio Hardware Test: [AUDIO HW]

• The following test should be performed while the machine is set

in the “STOP” mode.

07-00 /* AUDIO-H TEST MENU */

07-00 AUDIO-H MENU

07-01 RESERVE

3-7-1. Testing the Alarm Sound

07-02 XMUTE=on, MODE=00 (During alarm, circuit playback + mute)

07-03 XMUTE=on, MODE=01 (During alarm, circuit recording + mute)

07-04 XMUTE=on, MODE=10 (During alarm, circuit STOP + mute)

07-05 XMUTE=on, MODE=11 (During alarm, circuit STANDBY + mute)

07-06 XMUTE=off, MODE=00 (During alarm, circuit is in playback.)

07-07 XMUTE=off, MODE=01 (During alarm, circuit is in record.)

07-08 XMUTE=off, MODE=10 (During alarm, circuit is STOP)

07-09 XMUTE=off, MODE=11 (During alarm, circuit is STANDBY)

3-7-2. T esting LED

07-0A LED=4ch, LED=on

07-0B LED=2ch, LED=off

3-7-3. Stopping FINT Information

07-0C FINT INFORMATION

3-8. Digital Hardware System Test: [DIGITLAL HW]

• Performs the menu display of the digital system test items.

• SRAM test

Write/read test of the SRAM area is performed at the startup when

the main power is turned on.

0x5555, 0xAAAA and 0x0000 are used as the write data.

After completion of the writing the respective data, the data are

read-out and are collated.

The test area is 0x200000 to 0x207FFF in the area 1.

When an error occurs during reading and collating, the REC LED

on the deck-A will blink permanently.

(The REC LED on the deck-A is connected to the pin-11 (PC0)

of the IC1077 HD64003TF16.

• DRAM test

Write/read test of the DRAM area is performed at the startup

when the main power is turned on.

0x5555, 0xAAAA and 0x0000 are used as the write data.

After completion of the writing the respective data, the data are

read-out and are collated.

The test area is 0x600000 to 0x7FFFFF in the area 3. The test is

performed at every 257 bytes.

When an error occurs during reading and collating, the REC LED

on the deck-B will blink permanently.

(The REC LED on the deck-B is connected to the pin-12 (PC1)

of the IC1077 HD64003TF16.)

3-8-1. The Menu Display

08-01

/* DIGITAL HW TEST */

08-01 THIS MENU

08-02 ROM VERSION & DATE

08-03 ROM CHECK SUM

08-04 JOG INPUT

08-05 PULSE 10 mSEC

08-06 CXD-8655 WRITE/READ

08-07 CLOCK IC

08-08 CLOCK IC (power on)

08-09 LED ON/OFF

08-0A NMI

08-0B MODEL

08-0C LOCAL

3-8-2. ROM Version

Displays the release version of the programmed ROM.

08-02

/* ROM VERSION & DATE */

ROM: Ver No.0017 DATE: 2001.02.21

DECK A ROM : V 2.33

DECK B ROM : V 2.33

3-8-3. Check Sum of the ROM

Checksum of the programmed ROM is calculated.

The checksum area is 0x00000 to 0x07FFFF in the area 0.

Displays the address under calculation in hexadecimal number.

08-03

/* ROM CHECK SUM */

CHECK SUM = xxxx

21

Page 22

MDCC-2000

Displays the calculation result in the 2 bytes hexadecimal number .

The result indicates the value which is the same as checksum

calculated by the ROM writer.

08-FF

/* ROM CHECK SUM */

CHECK SUM = 9375

COMPLETED

3-8-4. Entry by JOG Operation

The input data of the JOG operation is sampled by 1 msec. cycle.

When the input data agree twice continuously, the data are

confirmed as the input data. The confirmed input data pass through

the chattering processing. Then the resultant input data is

displayed.

08-04

/* JOG INPUT */

JOG-1 = 1

JOG-2 = 0 or 1

Displays the input status of the pin-2 of the CPU in the JOG-1.

Displays the input status of the pin-3 of the CPU in the JOG-2.

The JOG-1 is the input at pin-2 (PB0) connector of the IC1077

HD64003TF16.

The JOG-2 is the input at pin-3 (PB1) connector of the IC1077

HD64003TF16.

3-8-5. PULSE Output

• Connection between the CXD-1809 and the CPU bus can be

checked by this test.

08-05

/* PULSE 10mSEC */

The pulse for confirming the clock oscillation of the microprocessor is output.

This pulse is output to pin-73 (RA03) terminal TP1058 of the

IC1033 CXD-1809.

The pulse width is 10 msec and the tolerance is less than 1/100.

10 mSEC 10 mSEC

3-8-6. Write/Read Test of CXD-8655

After writing 0x55 in the “Interrupt Timing Register” of the CXD8655 (IC1021), the value in the same register is read out and is

checked whether the data is 0x55 or not.

3-8-7. Watch IC Test I

Displays the inside data of the watch IC and performs the error

correction of the oscillation clock.

08-07

/* CLOCK DATA */

SECOND = 54 CORRECT = 10

MINUTE = 37 CRTL_1 = 20

OCLOCK = 14 CTRL_2 = 00

WEEK = 00

DAY = 02 SET CORRECT (JOG & ENTER)

MONTH = 91 32769.500 - 32769.599 (10)

YEAR = 00

“MONTH = 91” means a status that the 100-yaer bit is on. It

becomes November by masking MSB.

1. Contents of displays

Items Contents of display

SECOND Displays the value of the “second” count register in 2-digit BCD.

MINUTE Displays the value of the “minute” count register in 2-digit BCD.

OCLOCK Displays the value of the “hour” count register in 2-digit BCD using

24-hour display.

WEEK Displays the value of the “week” count register in 2-digit

hexadecimal number.

No. 0 to No. 7 corresponds to Sunday through Saturday

respectively. But, because this machine does not use the day of

No. 7, the data is different from the actual day of the week.

DAY Displays the value of the “date” count register in 2-digit hexadecimal

number.

MONTH Displays the value of the “month” count register in 2-digit

hexadecimal number.

The bit 7 is set to “1” when the “year” count register is capable up

to 100 years.

YEAR Displays the value of the “year” count register in 2-digit BCD.

Displays the value of the “CORRECT” error correction register

in 2-digit hexadecimal number.

CRTL_1 Displays the value of the control register 1 in 2-digit hexadecimal

number.

Bit name Used for Setup value

7 : WALE Alarm control 0 = Alarm is invalid

6 : DALE Alarm control 0 = Alarm is invalid

5 : 12 24 12-hours/24-hours clock 1 = 24-hours clock

4 : CLEN2 32 kHz output 0 = Valid

3 : TEST IC test 0 = Normal operation

mode

2 : CT2 0 = OFF

1 : CT1 0 = OFF

0 : CT0 0 = OFF

Selecting the

periodic interrupt

08-06

/* CXD- 8 6 5 5 WR/RD */

WRITE/READ COMPLETE.

If value is the same, “WRITE/READ COMPLETE” appears.

If value differs, “WRITE/READ ERROR!” appears.

22

Page 23

MDCC-2000

CRTL_2 Displays the value of the control register 2 in 2-digit

hexadecimal number.

Bit name Used for Setup value

7 : VDSL Power supply monitoring 0 = 2.1V

voltage

6 : VDET Result of power supply 0 = More than

monitoring monitoring

voltage

5 : SCRATCH Scribble bit

4 : XSTP Stops sending data 0 = Normal send

status

3 : CLEN1 32 kHz output 0 = Valid

2 : CTFG Fixed cycle interrupt 0 = OFF

output

1 : WAFG Alarm matches. 0 = Does not match.

0 : DAFG Alarm matches. 0 = Does not match.

SET CORRECT Indicates the method to set the correction value.

32768.500 to Indicates the clock oscillation frequency range.

32768.599 ( ) Indicates the correction value in parenthesis ( ).

2. Error Correction

Corrects an error of the clock oscillation frequency of the watch

IC.

1. Pull up the clock output (TP1001) of the watch IC to the

Vcc with a resistor (about 10 kΩ).

2. Measure the clock oscillation frequency.

The frequency counter which has the measurement accuracy

of eight digits or more should be used.

3. Select the range of the oscillation frequency using the JOG

dial.

4. Press the ENTER button.

When the writing data into the watch IC and the storing

data into the NVRAM are complete, “COMPLETE”

appears.

5. When the ENTER button pressed once and then the hand

removed from the ENTER button, the value that are set in

“CORRECT=” is reflected and stored.

(Note)

In order to return the machine to the customer with the status

in which the clock error correction value is being saved,

select “SHIPPING” in the test mode of the NVRAM and

press the ENTER button, or alternately exit the test mode

and enter the STANDBY mode.

In the latter method, be careful that the stamp information,

password, reverse time, etc are not initialized.

(If the NVRAM is initialized or the pattern write test is

performed, the clock error correction value that is sav ed in

the NVRAM, will also be initialized.)

3-8-8. Watch IC Test II (When power is turned on)

The inside data of the watch IC before executing the backup

battery run-out check is displayed at the moment of immediately

after the power-on of the machine.

Accordingly, the data before resetting the watch IC at the event

of backup battery run-out check, etc can be confirmed.

08-08

/* CLOCK IC (Data just before power on) */

SECOND = 54 CORRECT = 10

MINUTE = 37 CRTL_1 = 20

OCLOCK = 14 CTRL_2 = 00

WEEK = 00

DAY = 02 [OSCILLATOR : OK (CONTINUED) ]

MONTH = 91 [SECOND-YEAR DATA : LEGAL ]

YEAR = 00 [BACKUP BATTERY : OK (MORE THAN 2.1V) ]

“MONTH = 91 becomes November by masking MSB in the status

in which the 100-yaer bit is set to on.

1. Contents of displays

The contents are the same as those of Section 3-8-7. “Watch

IC T est I” except for the following.

Items Contents of displays

[OSCILLATOR : OK (CONTINUED) ] When the oscillation stop

is not detected.

[OSCILLATOR : NG (STOPED) ]

[SECOND-YEAR DATA : LEGAL ]

[SECOND-YEAR DATA : ILLEGAL ]

[BACKUP BATTERY : OK (MORE THAN 2.1V) ] When the backup battery

[BACKUP BATTERY : LESS THAN 2.1V ] When the backup battery

When the oscillation stop

is detected.

When the data of second,

minute, hour, date, month,

and year are of the

possible values.

When the data of second,

minute, hour, date, month,

and year are of the

impossible values.

is normal.

has run out.

3-8-9. LED ON/OFF

The LEDs of the channel 3 and channel 4 of the monitor and

those of LINE OUT, the deck-A and deck-B, and the REC button

simultaneously blink.

08-09

/* LED ON/OFF */

1. 3ch/4ch

2. DECK A/B

3. REC A/B

The period of blinking is 0.5 seconds for “on” and 0.5 seconds

for “off”.

0.5 SEC 0.5 SEC

23

Page 24

MDCC-2000

3-8-10. NMI Test

When the NMI starts, “NMI ON” appears.

08-0A

/* NMI */

NMI ON

“NMI OFF” appears about one second later.

08-0A

/* NMI */

NMI OFF

Outputs the pulse to pin-73 (RA03) terminal TP1058 of the

IC1033 CXD-1809.

Pulse width is about 1 sec.

IC1002-8 PIN

IC1007-72 PIN

IC1033-72 PIN

1 SEC

3-9-1. Setup for Shipment of the Machine

The data except the watch correction value and the number of

times of use of the laser are initialized.

09-01

/* NVRAM INITIALIZE / CHECK */

Setting-up is under way.

Setup for shipment of the machine is under way.

09-10

/* NVRAM SHIPPING */

Result

(Normal completion)

Display of completion of setup for shipment of the machine

09-FF

/* NVRAM SHIPPING */

COMPLETE.

CUT OFF POWER!

Shut off the power supply after this.

(After completion of the test mode by setting k_test_h to 0x00,

you may set the [STANDBY] mode.)

LCD display

"NMI OFF" "NMI ON" "NMI OFF"

3-9. NVRAM Test: [NVRAM]

After writing the word data (2 bytes) with 128 words to the evennumbered address from the address 0x00, write 128 words to the

odd- numbered address from the address 0x01.

After reading and checking at every ev en-numbered address from

the address 0x00, read and check at odd-numbered address from

the address 0x01.

09-01

/* NVRAM INIIALIZE / CHECK */

09-01 SHIPPING

09-02 INITIALIZE

09-03 PATTERN CHECK

SELECT and ENTER

While pressing the g button, rotate the [JOG] dial, then the

setup or test starts by pressing the ENTER button after changed

k_test_l.

• Remote selection

By sending the remote command for the setup of k_test_h and

k_test_l, the test can start to perform directly without operating

buttons of g , [JOG], ENTER , etc.

(Abnormal completion)

Display of the abnormal completion of the setup for shipment

of the machine

09-10

/* NVRAM SHIP INITIALIZE */

ERROR.

REPAIR HARDWARE!

Data of the NVRAM are undefined.

Investigation to perform repair, etc is required.

Initialized data of the NVRAM

Marks Items Values Remarks

A disp_cnt_A/B 0x11 A=Lower 4-bit, B=Higher 4-bit

B deck status 0x00 use, mark_a/b

C mark_clust_a 0x00 Cluster address of the mark A

D mark_clust_b 0x00 Cluster address of the mark B

E mark_sect_a 0x00 Sector address of the mark A

F mark_sect_b 0x00 Sector address of the mark B

G pb_stop (A/B) 0x00 Playback stop position address

H laser (A/B) ? Count of use of the laser

I rec_mode 0x01 Record ATARC mode

J rev_time 0x00 Reverse time

K pass_word 0x00 Password

L correct ? Error correction value of the watch

M reserve 1 Reserved

N crc_int ? CRC of the above

O stamp 0x00 Stamp character string

P crc_stamp ? CRC in stamp character string

24

Page 25

MDCC-2000

3-9-2. Initialization of the NVRAM

09-02

/* NVRAM INITIALIZE/CHECK */

During execution of the initialization, “k_test_l” shows the

following values.

Value of k_test_l Status

0x21 During write.

0x22 During read.

0xFF Completion of the check

Display during initialization

09-20

/* NVRAM INITIALIZE */

NOW NVRAM INITIALIZE.

Result

(Normal completion of the initialization)

If nv_error=0, the initialization has normally ended.

09-FF

/* NVRAM INITIALIZE */

COMPLETE.

CUT OFF POWER.

3-9-3. 4-Pattern Check

09-03

/* NVRAM INITIALIZE / CHECK */

During execution of the check, “k_test_l” shows the following

values.

Value of k_test_l Status

0x31 Data write is in progress. Both even number and odd number

are 0x0000.

0x32 Data read and data check are in progress.

0x33 Data write is in progress. Even number is 0x5555 and odd

number is 0xAAAA.

0x34 Data read and data check are in progress.

0x35 Data write is in progress. Even number is 0xAAAA and odd

number is 0x55555.

0x36 Data read and data check are in progress.

0x37 Data write is in progress. Both even number and odd number

are 0xFFFF.

0x38 Data read and data check are in progress.

0xFF Check is complete.

Display during check

09-31

/* NVRAM PATTERN CHECK */

1. NOW 00-00 PATTERN CHECK

All data of the NVRAM are set up to 0xFFFF (the initial value of

the device).

After this, shut off the power supply.

(Note) The correction information of the watch is set up to “No

correction (0)”.

(Abnormal completion of the initialization)

If nv_error=0x10, the initialization has ended with failure.

09-FF

/* NVRAM INITIALIZE */

ERROR.

REPAIR HEARDWARE!

The data of the NVRAM are undefined.

Investigation to perform repair, etc is required.

(Note) The correction information of the watch is set up to “No

correction (0)”.

Result of the check

(In the normal case)

If nv_error=0, the result is normal.

09-FF

/* NVRAM CHECK */

1. 00-00 PATTERN CHECK OK.

2. 55-AA PATTERN CHECK OK.

3. AA-55 PATTERN CHECK OK.

4. FF-FF PATTERN CHECK OK.

CHECK END.

CUT OFF POWER.

All data of the NVRAM are set up to 0xFFFF (the initial value of

the device).

After this, shut off the power supply.

(Note) The correction information of the watch is set up to “No

correction (0)”.

(In the abnormal case)

If nv_error>0, the result is abnormal.

09-FF

/* NVRAM CHECK */

1. 00-00 PATTERN CHECK OK.

2. 55-AA PATTERN CHECK OK.

3. AA-55 PATTERN CHECK ERROR.

4. FF-FF PATTERN CHECK OK.

REPAER THE HEARDWARE!

Example : An error in write and read of the AA-55 pattern

Investigation to perform repair, etc is required.

(Note) The correction information of the watch is set up to “No

correction (0)”.

25

Page 26

MDCC-2000

MEMO

26

Page 27

SECTION 4

ELECTRICAL ADJUSTMENTS

MDCC-2000

4-1. Laser Power Adjustment

1. Enter the test mode of Checking Operations of Mechanism,

and start up the adjustment program. (Refer to section 3-3-13.

Checking Operations of Mechanism.)

:MON>mdmon

MD DRIVE TEST MODE MONITOR Wait..... Hit ’.’ to exit

>>>PDMD-7 TEST MODE V2.14 [Feb. 16 1998]

>>

2. When the return key is pressed, the menu is displayed.

>>>PDMD-7 TEST MODE V2.14

P)Play A)Access N)Info E)Eject R)Rec K)Erase V)Volum !)Reset

X)Cmd L)Laser F)Focus W)Switch S)Spindl J)Jump G)FGSV D)Sled

M)EEPROM U)Adjust C)Spec T)Still Y)Sync 1)Mon 2)Aging

>>

3. Select U)Adjust.

>>u

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>

4. Select 2) LASER.

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>2

--- READJUST?

5. Set the laser power meter (J-2501-046-A) and press the return

key.

>>WRITE POWER : 6.85 mW

1)- 2)+ [DA] FD [00ED]

6. Adjust the laser power by pressing [1] key (decreasing the laser

power), [2] key (increasing the laser po wer) until the laser power

measurement value is as close as possible to 6.85 mW. Press

the return key to set the adjustment value.

(Do not take to long time for adjustment. If it takes too long

time, the laser power will fluctuate due to temperature increase.)

1)- 2)+ [DA] FD [00ED]

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>

7. Eject the probe of the laser power meter.

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>e

4-2. Servo Adjustment

1. Set the MD data disk (recordable disk).

2. Select 3) EFBL/SERVO/FBIAS.

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>3

---MO PIT (FBIAS)---------FBIAS [10]

---MO GROOVE (EFBL)---------EFBL [0F]

---MO WRITE (EFBL)---------EFBL [0F]

---MO GROOVE (FOCUS)---------K13 [4D]

---MO GROOVE (TRACKING)---------K23 [43] K07 [43]

---MO GROOVE (FBIAS)---------FBIAS [2F]

T=6774(msec)

3. Press the [ESC] key to terminate the adjustment menu.

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>

>>

4. Eject the MD data disk (recordable disk).

>>e

5. Select U)Adjust.

>>u

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>

6. Set the MD data disk (read only disk).

7. Select 3) EFBL/SERVO/FBIAS.

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>

---CD DISC (EFBL)---------EFBL[10]

---CD DISC (FOCUS)---------K13[38]

---CD DISC (TRACKING)---------K23[30] K07[30]

---CD (FBIAS)---------FBIAS[00]

T=3143(msec)

8. Press the [ESC] key to terminate the adjustment menu.

1)TEMP 2)LASER 3)EFBL/SERVO/FBIAS

5)EFBL 6)SERVO 7)FBIAS E)Eject >>

>>

9. Eject the MD data disk (read only disk).

>>e

10. Press the period [.] key to exit the adjustment program.

>>.

:MON>

11. Turn off the main power of this machine.

:MON>pwof

Note :

If discs are replaced while the machine is left in the U/Adjust mode

in the machines up to Ver 2.14, the disk types may be incorrectly

recognized and adjustment may not be possible.

In such a case, press the [ESC] key to terminate the U)Adjust mode

once and then select U)Adjust again.

27

Page 28

MDCC-2000

SECTION 5

DIAGRAMS

Note on Printed Wiring Boards: MAIN SECTION

• X : parts extracted from the component side.

• : Pattern from the side which enables seeing.

(The other layers' patterns are not indicated.)

• : Pattern of the rear side.

Note on Schematic Diagram: MAIN SECTION

• All capacitors are in µF unless otherwise noted. pF: µµF 50 WV or

less are not indicated except for electrolytics and tantalums.

• All resistors are in Ω and 1/

f

•

Note: The components identified by mark 0 or dotted line with

• : B+ Line.

• Power voltage is dc 12V and fed with regulated dc power supply

• Voltages and waveforms are dc with respect to ground under no-

• Voltages are taken with a VOM (Input impedance 10 MΩ).

• Waveforms are taken with a oscilloscope.

• Circled numbers refer to waveforms.

• Signal path.

: internal component.

mark 0 are critical for safety.

Replace only with part number specified.

from battery terminal.

signal conditions.

no mark : PLAY

Voltage variations may be noted due to normal production tolerances.

Voltage variations may be noted due to normal production tolerances.

E : PB

a : REC

4

W or less unless otherwise specified.

• WAVEFORMS

1

IC1004 1 (TP1001)

30.5 µs (32.768kHz)

2

IC1009 4 (TP1006)

62.5 ns (16MHz)

3

IC1018 4

22.1 ns (45.1584MHz)

4

IC38 eh (CL25)

4.8 Vp-p

5.4 Vp-p

7.4 Vp-p

39.4 ns (25.4MHz)

5

IC2 ya (CL18)

100 ns (10MHz)

4.6 Vp-p

4.6 Vp-p

28

Page 29

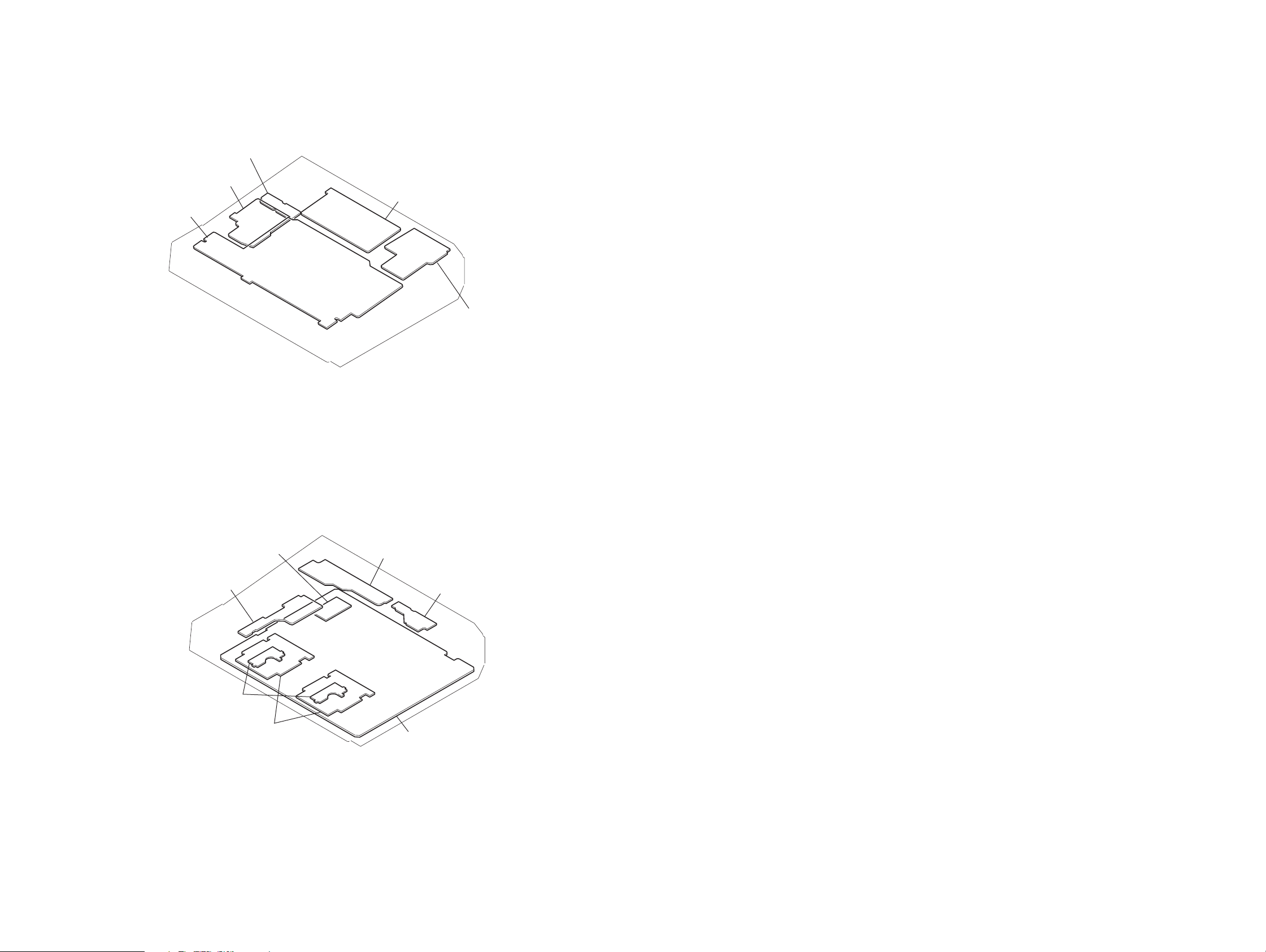

5-1. CIRCUIT BOARDS LOCATION

d

VOLUME board

LEVEL METER board

SWITCH board

MDCC-2000

LCD board

LINE SELECTOR

board

MUTE board

FOOT SWITCH board

BUM-F1 board

MD board

AUDIO I/O board

SERIAL I/O boar

MAIN board

2929

Page 30

MDCC-2000

5-2. BLOCK DIAGRAMS

MD SECTION

HR901

OVER WRITE HEAD

OPTICAL

PICK-UP

KMS-250A

(J2N)

VC

PD

ILCC

FCS+

FCS-

TRK+

TRK-

MOD

MD BOARD

I-V AMP

IC22

3

1

75

IC23

3

75

II

J

A

B

C

D

E

F

Q3,4

AUTOMATIC

POWER

CONTROL

IC13

1

4

2

VS

IC24

SUM

1

4

1

3

RF MATRIX AMP

1

J

2

VC

3

A

4

B

5

C

6

D

7

E

8

F

9

PD

10

11

APC

IC14

4

FOCUS/TRACKING COIL DRIVER

SPINDLE MOTOR DRIVER

24

RO4

8

FO1

11

RO1

29

FO3

26

RO3

LDON

IC15

1

4

2

IC37

RI4

19

FI1

6

5

RI1

FI3

31

32

RI3

PS

CLK

3

34

XRST XRST

IC21

2

FFDR

FRDR

TFDR

TRDR

FS4

VREF

PEAK

BOTM

ABCD

AUX

ADFG

APCREF

SWDT

SCLK

XLAT

LPF,PHASE SHIFT

3

2

21

38

RF

37

36

35

33

32

SE

28

12

FE

34

TE

26

16

17

18

XSHOCK

LMOD

IC17

1

5

IC26

2

2

SPSW

1

6

IC9

1

IC10

1

4

7

9

10

SPFD

7

FGSV

6

Q11-14

OVER WRITE

HEAD DRIVER

7

CHUT

IC12

24

6

7

6

14

IC34

SHOCK DETECT

Q6-8

SWITCH

6

7

7

IC35

LPF

2

1

IC33

1

14

2

13

LMOD

XSHOCK

B+

5

4

1

+2.8V REG

IC29

DRIVER

2

18

Y1

3

17

I2I1Y2

8

12

I7Y7

9

11

I8G2Y8

19

EFM/ACIRC ENCODER/DECODER

69

VC

RFI

58

PEAK

64

BOTM

65

ABCD

66

AUX1

68

ADFG

82

SE

76

LDDR

84

FE

67

IC36

TE

77

1

IC20

4

2

SPFD

94

FFDR

FRDR

TFDR

TRDR

FS4

IC39

SPFD

87

FFDR

89

FRDR

86

TFDR

85

TRDR

90

FS4

32

6

3

XMGON

Q15,16

RF MOD

SWITCH

IC28

IC38

DSP,

5

4

1

2

VCC

WRPWR

EFMO

DTI

DTO

C2PO

BCK

LRCK

REC

FOK

SENS

SQSY

COUT

SRDT

XTAI

XTAO

SPRD

SWDT

SCLK

XLAT

XRST

UNREG

• Signal Path

: PB

: REC

IC2

MD MECHANISM

CONTROLLER

79

45

29

30

31

32

33

24

12

14

99

11

35

34

93

99

10

16

DTI

DTO

C2PO

BCK

LRCK

2

6

X1

25.4MHz

SPDL

DIR

8

Q9

TEMP

SENSOR

REC

FOK

SENS

WRPWR

SQSY

TCNT

SRDT

X2

10MHz

IC18

7

1

5

FGDR

6

SPSW

FGSV

AD1

AD2

80

81

AD3

CSV

60

PS2

58

PS0

82

P74

P75

83

87

IRQ0

88

IRQ1

PA3

96

15

RXD1

66

EXTL

XTL

67

P45

24

23

P44

TCA4

4

13

TXD1

17

CLK1

P94

16

PB4

6

IRQ3

90

LDON

PB7

9 63

MLON

PB5

7

IC5

4

1

2

8

PB6

RECS

5

PB3

TXD0

RXD0

D0-D7 D0-D7

A0-A15 A0-A15

XRD

XWR XWE

CSO

P42

P41

P40

PS1

P43

IRQ2

TCA0

PA0

TCKB

PA1

TCA3

PA7

PA6

PA4

RES

1

12

14

27-34

36-43

45-52

70

71

91

20

19

18

59

21

89

95

93

3

94

2

100

99

97

IC6

RESET

TXD

RXD

XRST

3

VS

DIR

PVCC

IC3

EEPROM

DAT

3

SCK

4

CS

1

XRST2

UNREG

FLASH MEMORY

21-23

25-29

20-13

3,2,31

1,12,4

5,11

32

XOE

7

XCE

30

DSCPRO

RFLCT

DISCIN