Sony ICX054AK Datasheet

ICX054AK

A

A

For the availability of this product, please contact the sales office.

1/3-inch CCD Image Sensor for NTSC Color Camera

Description

The ICX054AK is an interline CCD solid-state

image sensor suitable for NTSC 1/3-inch color video

cameras. High sensitivity is achieved through the

adoption of Ye, Cy, Mg and G complementary color

mosaic filters and HAD (Hole-Accumulation Diode)

sensors.

This chip features a field period readout system,

and an electronic shutter with variable chargestorage time.

Features

• High sensitivity (+3dB compare with ICX044BKA)

and low dark current

• Continuous variable-speed shutter

1/60s (Typ.), 1/100s to 1/10000s

• Low smear

• Excellent antiblooming characteristics

• Ye, Cy, Mg and G complementary color mosaic

filters on chip

• Horizontal register: 5V drive

• Reset gate: 5V drive

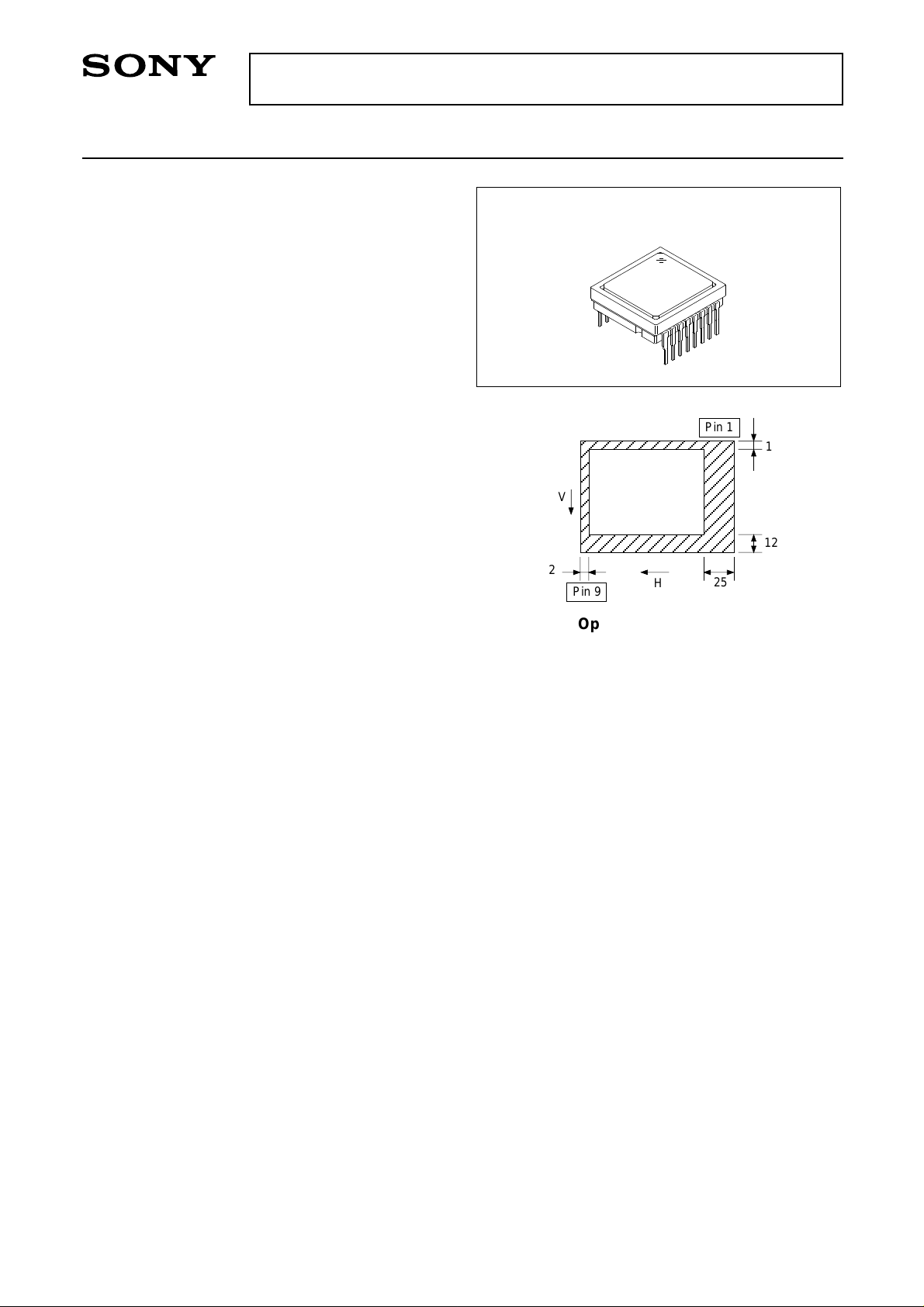

16 pin DIP (Plastic)

AAA

V

AAA

2

Pin 9

Optical black position

H

(Top View)

Pin 1

1

12

25

Device Structure

• Optical size: 1/3-inch format

• Number of effective pixels: 510 (H) x 492 (V) approx. 250K pixels

• Number of total pixels: 537 (H) x 505 (V) approx. 270K pixels

• Interline CCD image sensor

• Chip size: 6.00mm (H) x 4.96mm (V)

• Unit cell size: 9.6µm (H) x 7.5µm (V)

• Optical black: Horizontal (H) direction: Front 2 pixels, Rear 25 pixels

Vertical (V) direction: Front 12 pixels, Rear 1 pixel

• Number of dummy bits: Horizontal 16

Vertical 1 (even field only)

• Substrate material: Silicon

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E92107C66-ST

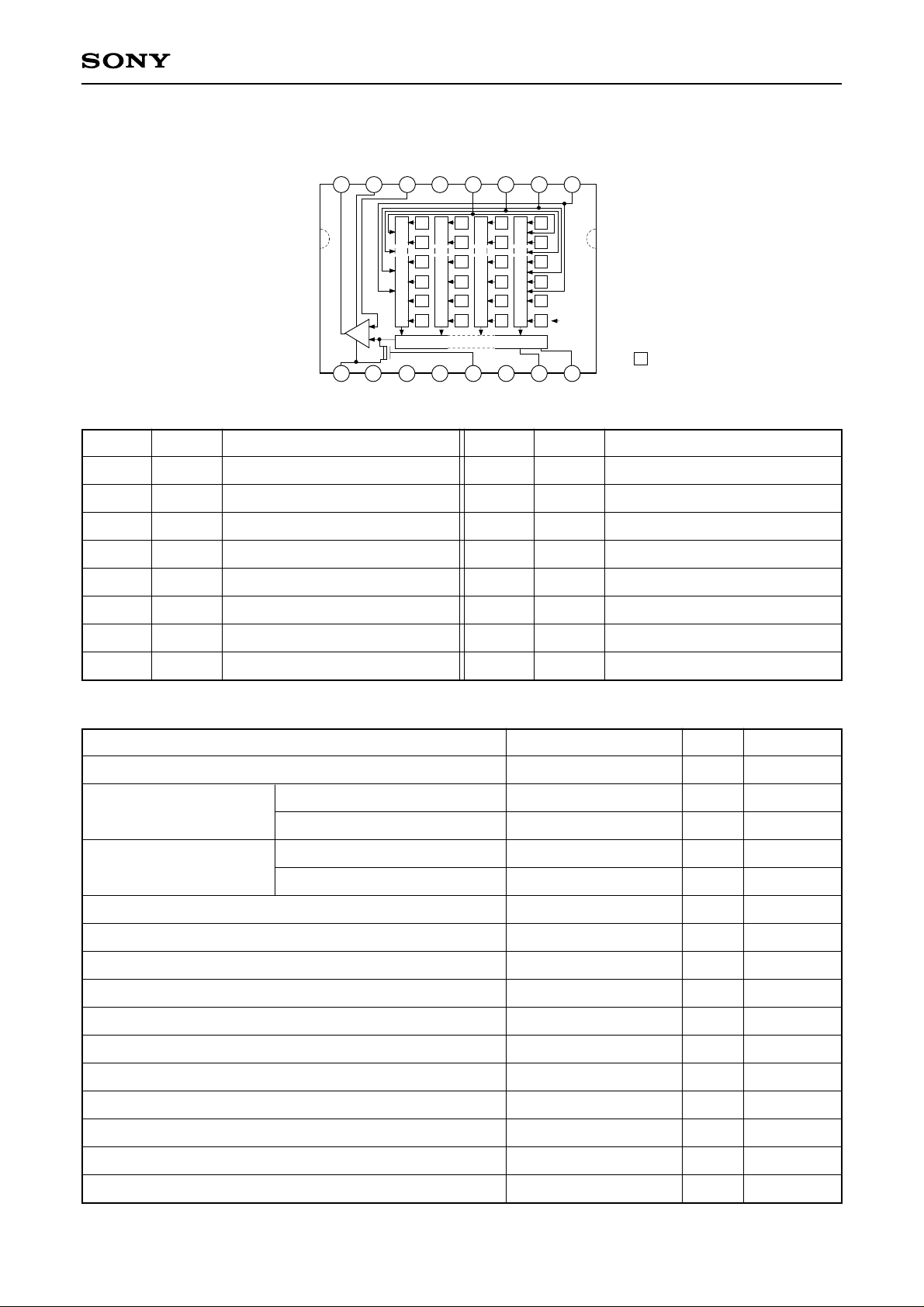

Block Diagram and Pin Configuration

(Top View)

Pin Description

2

SS

V

7

10

GND

GG

V

6

Cy

G

Cy

G

Cy

Vertical register

Mg

11

SUB

OUT

V

8

9

DD

V

1

GND

Vφ

5

4

Ye

Cy

Mg

G

Ye

Cy

Mg

G

Ye

Cy

G

Mg

Horizontal register

13

12

L

V

RG

Vφ

3

14 15

NC

4

3

Vφ

Vφ

1

2

Ye

Mg

Ye

Mg

Ye

Note

G

Note) : Photo sensor

16

2

1

Hφ

Hφ

Pin No. Symbol Description Pin No. Symbol Description

ICX054AK

1

2

3

4

5

6

7

8

Vφ4

Vφ3

Vφ2

Vφ1

GND

VGG

VSS

VOUT

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

Vertical register transfer clock

GND

Output amplifier gate bias

Output amplifier source

Signal output

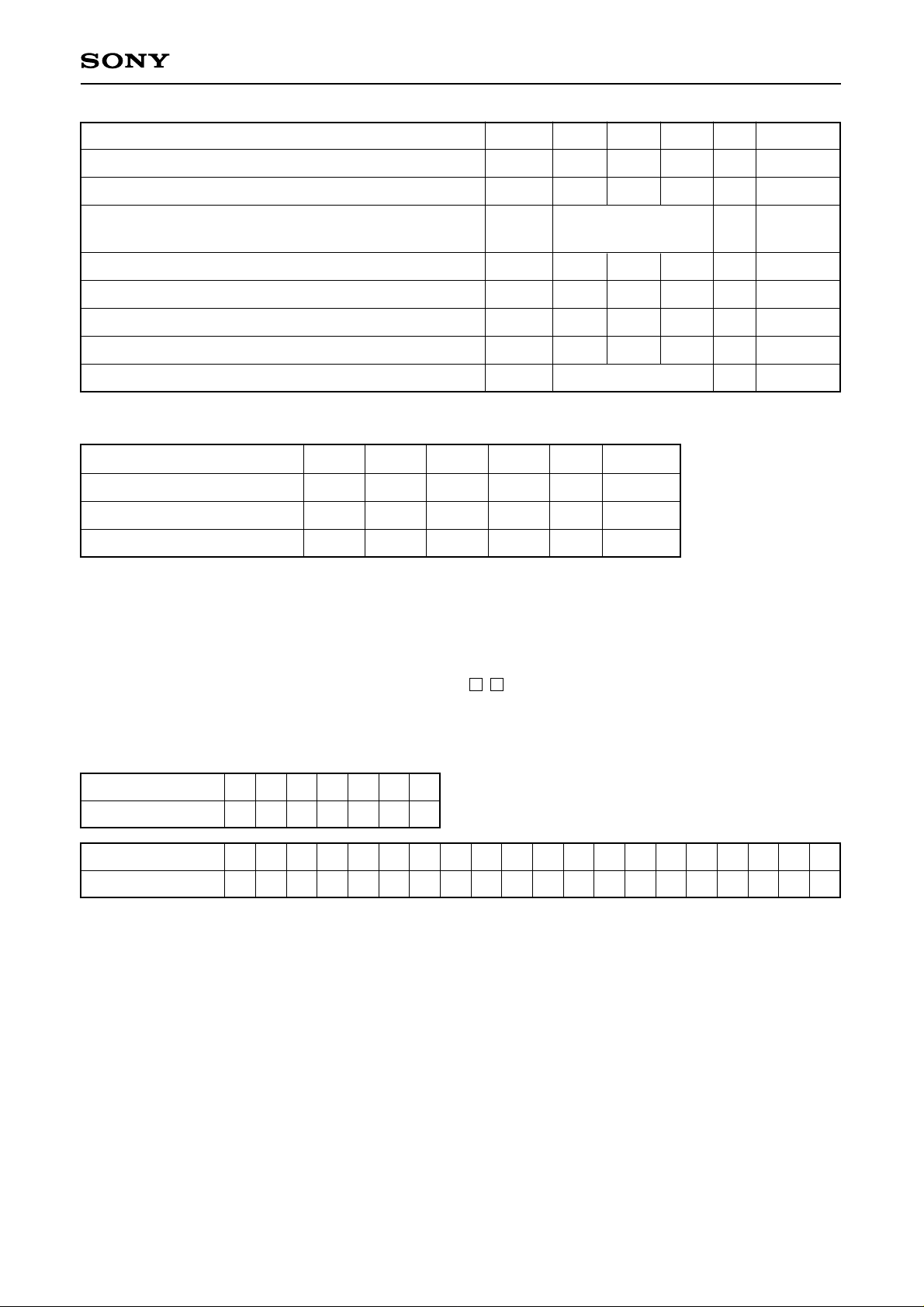

Absolute Maximum Ratings

Item

Substrate voltage SUB – GND

VDD, VOUT, VSS – GND

Supply voltage

VDD, VOUT, VSS – SUB

Vφ1, Vφ2, Vφ3, Vφ4 – GND

Vertical clock input voltage

Vφ1, Vφ2, Vφ3, Vφ4 – SUB

Voltage difference between vertical clock input pins

9

10

11

12

13

14

15

16

VDD

GND

SUB

VL

RG

Output amplifier drain supply

GND

Substrate (Overflow drain)

Protective transistor bias

Reset gate clock

NC

Hφ1

Hφ2

Horizontal register transfer clock

Horizontal register transfer clock

Ratings Unit Remarks

–0.3 to +55

–0.3 to +18

–55 to +10

–15 to +20

to +10

to +15

V

V

V

V

V

∗1

V

Voltage difference between horizontal clock input pins

Hφ1, Hφ2 – Vφ4

Hφ1, Hφ2, RG, VGG – GND

Hφ1, Hφ2, RG, VGG – SUB

VL – SUB

Vφ1, Vφ2, Vφ3, Vφ4, VDD, VOUT – VL

RG – VL

VGG, Vss, Hφ1, Hφ2 – VL

Storage temperature

Operating temperature

∗1

+27V (Max.) when clock width < 10µs, clock duty factor < 0.1%.

– 2 –

to +17

–17 to +17

–10 to +15

–55 to +10

–65 to +0.3

–0.3 to +30

–0.3 to +24

–0.3 to +20

–30 to +80

–10 to +60

V

V

V

V

V

V

V

V

°C

°C

Bias Conditions

ICX054AK

Item

Output amplifier drain voltage

Output amplifier gate voltage

Output amplifier source

Substrate voltage adjustment range

Fluctuation range after substrate voltage adjustment

Reset gate clock voltage adjustment range

Fluctuation range after reset gate clock voltage adjustment

Protective transistor bias

Symbol Min. Typ. Max. Unit Remarks

VDD

VGG

VSS

VSUB

∆VSUB

VRGL

∆VRGL

VL

14.55

1.75

15.0

2.0

Grounded with

680Ω resistor

9.0

–3

1.0

–3

∗2

15.45

2.25

18.5

+3

4.0

+3

%

%

V

V

±5%

∗1

V

∗1

V

DC Characteristics

Item

Output amplifier drain current

Input current

Input current

∗1

Indications of substrate voltage (VSUB) · reset gate clock voltage (VRGL) setting value.

Symbol Min. Typ. Max. Unit Remarks

IDD

IIN1

IIN2

3

1

10

mA

µAµA∗3

∗4

The setting values of substrate voltage and reset gate clock voltage are indicated on the back of the image

sensor by a special code. Adjust substrate voltage (VSUB) and reset gate clock voltage (VRGL) to the

indicated voltage. Fluctuation range after adjustment is ±3%.

VSUB code one character indication

VRGL code one character indication ↑↑

VRGL code VSUB code

Code and optimal setting correspond to each other as follows.

VRGL code

1

3

2

45

6

7

Optimal setting 1.0 1.5 2.0 2.5 3.0 3.5 4.0

VSUB code

Optimal setting

EfG

9.0 9.5

hJKL

m

NP

Q

STUVWX

R

10.0 10.511.0 11.5 12.0 12.5 13.0 13.5 14.014.5 15.0 15.5 16.0 16.5 17.017.5 18.018.5

<Example> “5L” → VRGL = 3.0V

VSUB = 12.0V

∗2

VL setting is the VVL voltage of the vertical transfer clock waveform.

∗3

1) Current to each pin when 18V is applied to VDD, VOUT, Vss and SUB pins, while pins that are not tested

are grounded.

2) Current to each pin when 20V is applied sequentially to Vφ1, Vφ2, Vφ3 and Vφ4 pins, while pins that are

not tested are grounded. However, 20V is applied to SUB pin.

3) Current to each pin when 15V is applied sequentially to RG, Hφ1, Hφ2 and VGG pins, while pins that are

not tested are grounded. However, 15V is applied to SUB pin.

4) Current to VL pin when 30V is applied to Vφ1, Vφ2, Vφ3, Vφ4, VDD and VOUT pins or when, 24V is applied

to RG pin or when, 20V is applied to VGG, Vss, Hφ1 and Hφ2 pins, while VL pin is grounded. However,

GND and SUB pins are left open.

∗4

Current to SUB pin when 55V is applied to SUB pin, while pins that are not tested are grounded.

Y

Z

– 3 –

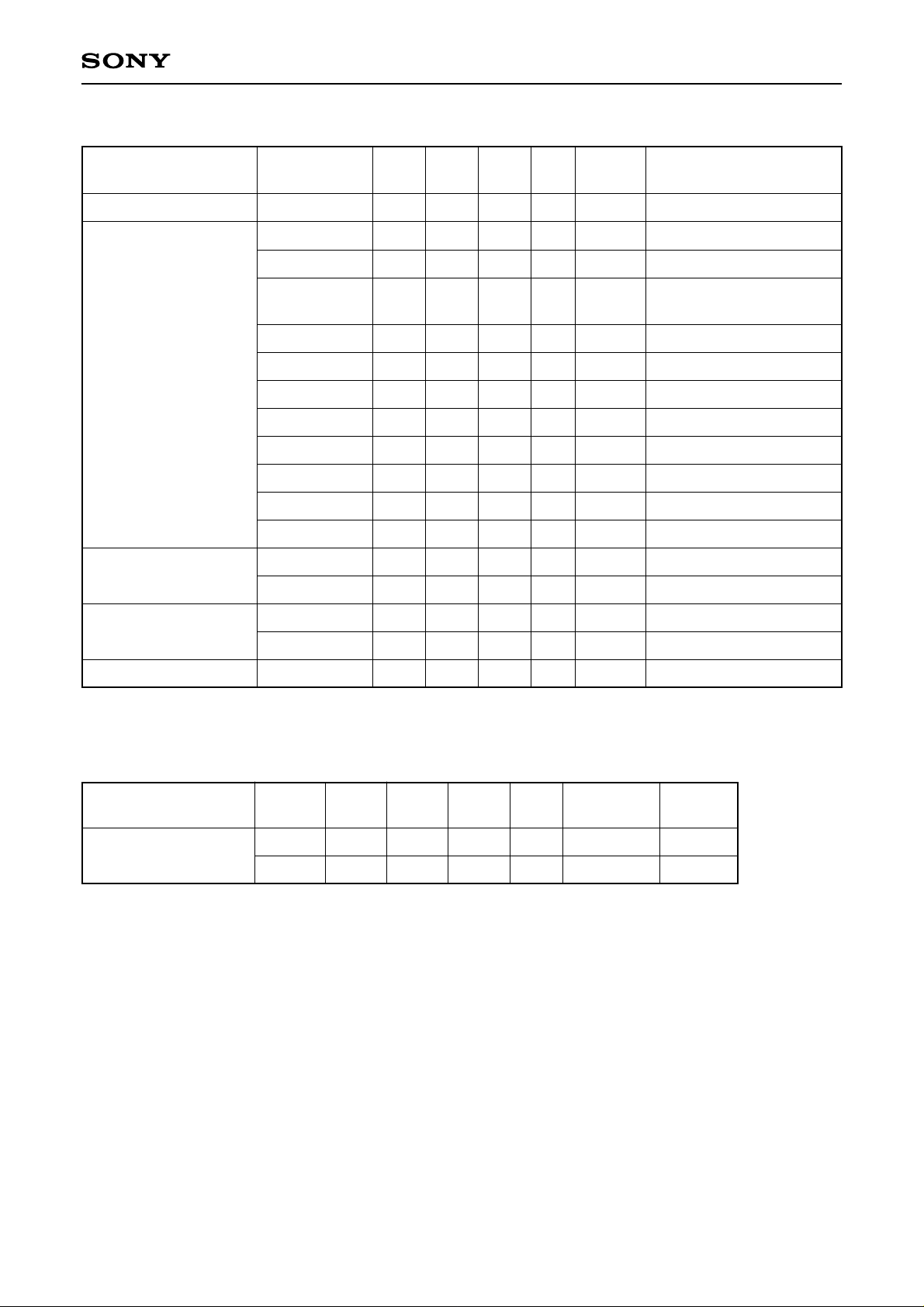

Clock Voltage Conditions

ICX054AK

Item

Readout clock voltage

Vertical transfer clock

voltage

Horizontal transfer

clock voltage

Reset gate clock

voltage

Symbol Min. Typ. Max. Unit

VVT

VVH1, VVH2

VVH3, VVH4

VVL1, VVL2,

VVL3, VVL4

VφV

|VVH1 – VVH2|

VVH3 – VVH

VVH4 – VVH

VVHH

VVHL

VVLH

VVLL

VφH

VHL

VφRG

V

RGLH –

V

RGLL

14.55

–0.05

–0.2

–9.0

7.8

–0.25

–0.25

4.75

–0.05

4.5

15.0

0

0

–8.5

8.5

5.0

0

5.0

15.45

0.05

0.05

–8.0

9.05

0.1

0.1

0.1

0.5

0.5

0.5

0.5

5.25

0.05

5.5

0.8

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

Waveform

diagram

1

2

2

2

2

2

2

2

2

2

2

2

3

3

4

4

Remarks

VVH = (VVH1+VVH2) /2

VVL = (VVL3 + VVL4) /2

VφV = VVHn – VVLn (n = 1 to 4)

High-level coupling

High-level coupling

Low-level coupling

Low-level coupling

∗1

Low-level coupling

Substrate clock voltage

∗1

The reset gate clock voltage need not be adjusted when reset gate clock is driven when the specifications

VφSUB

22.5

23.5

24.5

V

5

are as given below. In this case, the reset gate clock voltage setting indicated on the back of the image

sensor has not significance.

V

V

Waveform

diagram

4

4

Remarks

Item

Reset gate clock

voltage

Symbol

VRGL

VφRG

Min. Typ. Max. Unit

–0.2

8.5

0

9.0

0.2

9.5

– 4 –

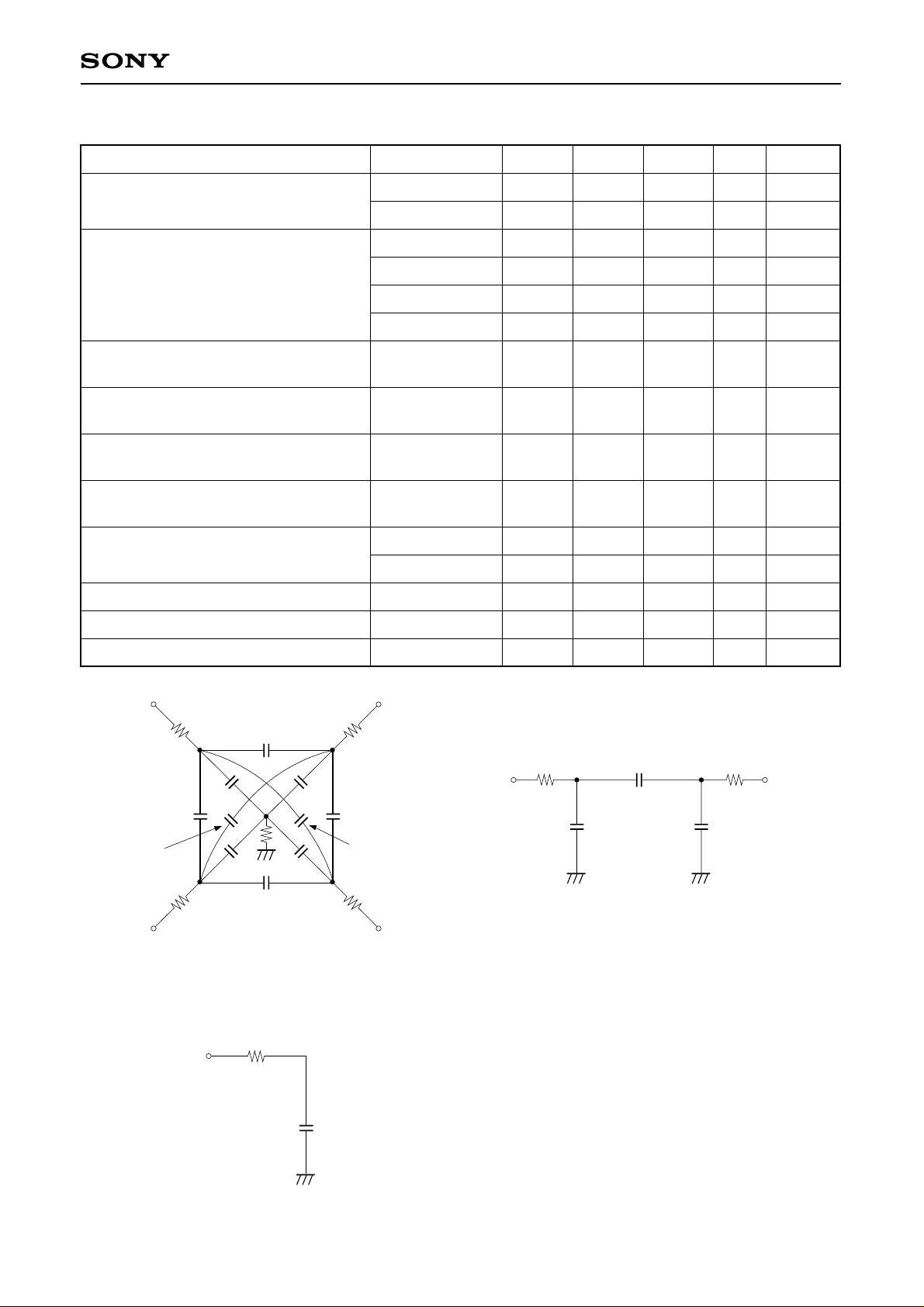

Clock Equivalent Circuit Constant

ICX054AK

Item

Capacitance between vertical transfer

clock and GND

Capacitance between vertical transfer

clocks

Capacitance between horizontal

transfer clock and GND

Capacitance between horizontal

transfer clocks

Capacitance between reset gate clock

and GND

Capacitance between substrate clock

and GND

Vertical transfer clock series resistor

Vertical transfer clock ground resistor

Symbol Min. Typ. Max. Unit Remarks

CφV1, CφV3

CφV2, CφV4

CφV12, CφV34

CφV23, CφV41

CφV13

CφV24

CφH1, CφH2

CφHH

CφRG

CφSUB

R1, R3

R2, R4

RGND

1500

820

470

230

150

230

47

47

5

320

51

100

15

pF

pF

pF

pF

pF

pF

pF

pF

pF

pF

Ω

Ω

Ω

Horizontal transfer clock series resistor

Reset gate clock series resistor

Vφ1

R1

CφV24

R4

Vφ4 Vφ3

CφV12

CφV1 CφV2

RGND

CφV4 CφV3

CφV34

R2

CφV23CφV41

CφV13

R3

RφH

RφRG

Vφ2

10

40

RφH RφH

CφHH

CφH1 CφH2

Vertical transfer clock equivalent circuit Horizontal transfer clock equivalent circuit

RGφ

RφRG

Ω

Ω

Hφ2Hφ1

Cφ

RG

Reset gate clock equivalent circuit

– 5 –

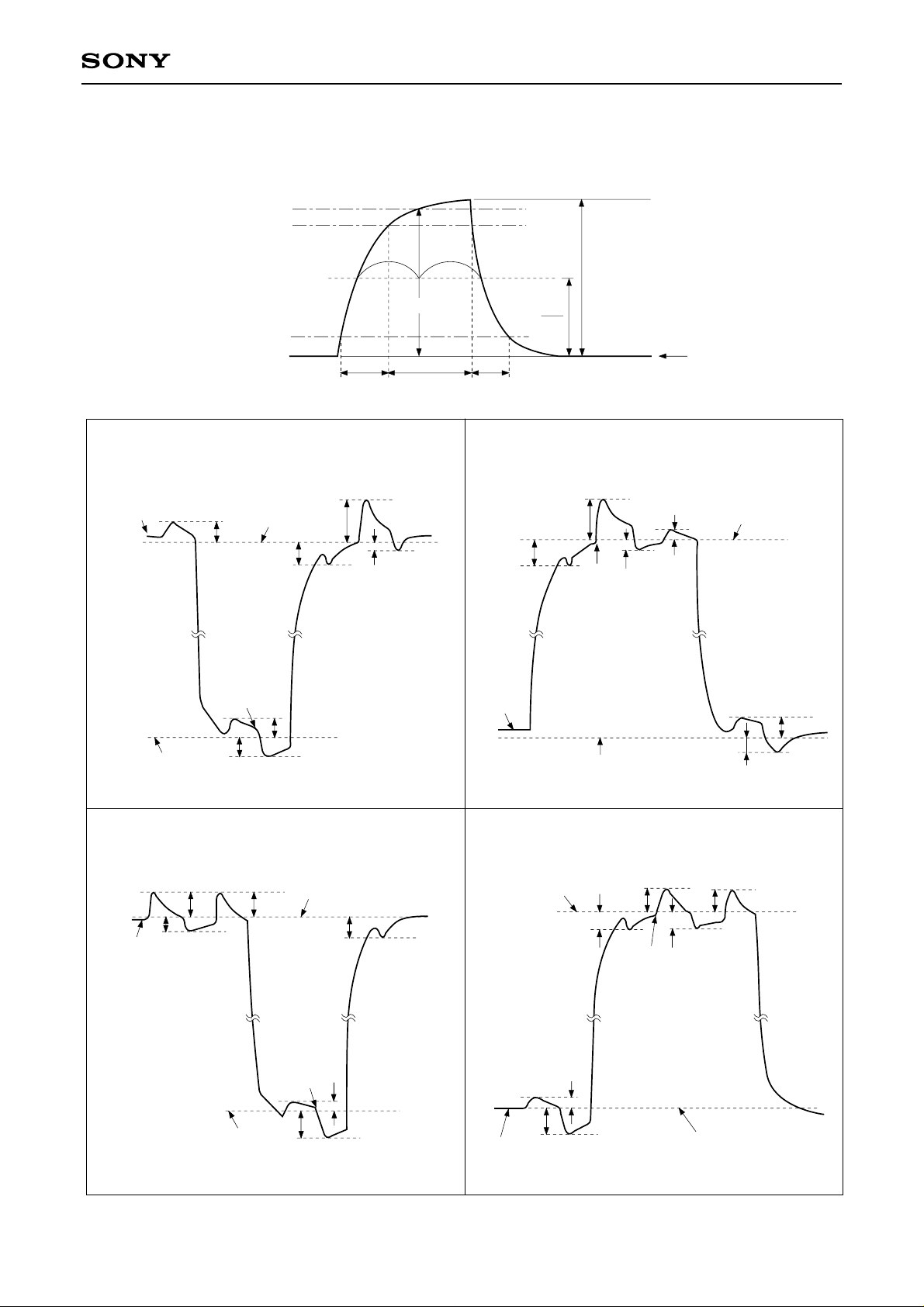

Drive Clock Waveform Conditions

(1) Readout clock waveform

100%

90%

ICX054AK

II II

VVT

10%

0%

tr twh tf

(2) Vertical transfer clock waveform

Vφ1 Vφ3

VVH1

VVHH

VVL1

VVH

VVHL

VVLH

VVHH

VVHL

VVHL

VVL3

φM

2

VVHH

φM

VVH3

VVHL

VVHH

0V

VVH

VVLH

VVL

Vφ2 Vφ4

VVHL

VVH2

VVLL

VVHH VVHH

VVL

VVLL

VVH

VVL2

VVHL

VVLH

VVL4

VVLL

VVH

VVLH

VVHL

VVL

VVLL

VVHH VVHH

VVHL

VVH4

VVL

– 6 –

Loading...

Loading...