Sony CXP88140, CXP88132 Datasheet

CXP88132/88140

CMOS 8-bit Single Chip Microcomputer

Description

The CXP88132/88140 is a CMOS 8-bit microcomputer which consists of A/D converter, serial

interface, timer/counter, time base timer, vector

interruption, high precision timing pattern generation

circuits, PWM generator, PWM for tuner, VISS/VASS

circuit, 32kHz timer/event counter, remote control

receiving circuit, FDP controller/driver, VCR vertical

sync separation circuit and the measuring circuit

which measure signals of capstan FG and drum

FG/PG and other servo systems, as well as basic

configurations like 8-bit CPU, ROM, RAM and I/O

port. They are integrated into a single chip.

Also, CXP88132/88140 provides sleep/ stop

function which enables to lower power consumption

and ultra-low speed instruction mode in 32kHz

operation.

Structure

Silicon gate CMOS IC

100 pin QFP (Plastic)

Features

• A wide instruction set (213 instructions) which cover various types of data

— 16-bit arithmetic instruction/multiplication and division instructions/boolean bit operation instruction

• Minimum instruction cycle During operation 250ns/16MHz, During operation 122µs/32kHz

• Incorporated ROM capacity 32Kbytes (CXP88132), 40Kbytes (CXP88140)

• Incorporated RAM capacity 1296bytes

• Peripheral function

— A/D converter 8-bit, 8-channel, successive approximation system

(Conversion time: 20.0µs/16MHz)

— Serial I/O with auto transfer mode Incorporated 8-stage FIFO for data (1 to 8 bytes auto transfer)

— Timer 8-bit timer/counter, 2-channel, 19-bit time base timer

— High precision timing pattern generation PPG 8 pins 32-stage programmable circuit RTG 5 pins 2-channel

— PWM/DA gate output 12-bit, 2-channel (Repetitive frequency 62.5kHz/16MHz)

— Servo input control Capstan FG, Drum FG/PG, CTL input

— VSYNC separator

— FRC capture unit Incorporated 26-bit and 8-stage FIFO

— PWM output for tuner 14-bit

— VISS/VASS circuit Pulse duty auto detection circuit

— 32kHz timer/event counter 32kHz oscillation circuit, ultra-low speed instruction mode

— Remote control receiving circuit 8-bit pulse measuring counter, 6-stage FIFO

— FDP controller/driver Max.148 segments can be displayed

Hardware key scanning function (Max.16 × 3 key matrix available)

— Tri-state output PPG 1 pin, RTG 1 pin, output 8 pins

— Pseudo HSYNC output function

— High speed head switching circuit

• Interruption 22 factors, 15 vectors, multi-interruption possible

• Standby mode SLEEP/STOP

• Package 100-pin plastic QFP

• Piggyback/evaluation chip CXP88100

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E94417-PS

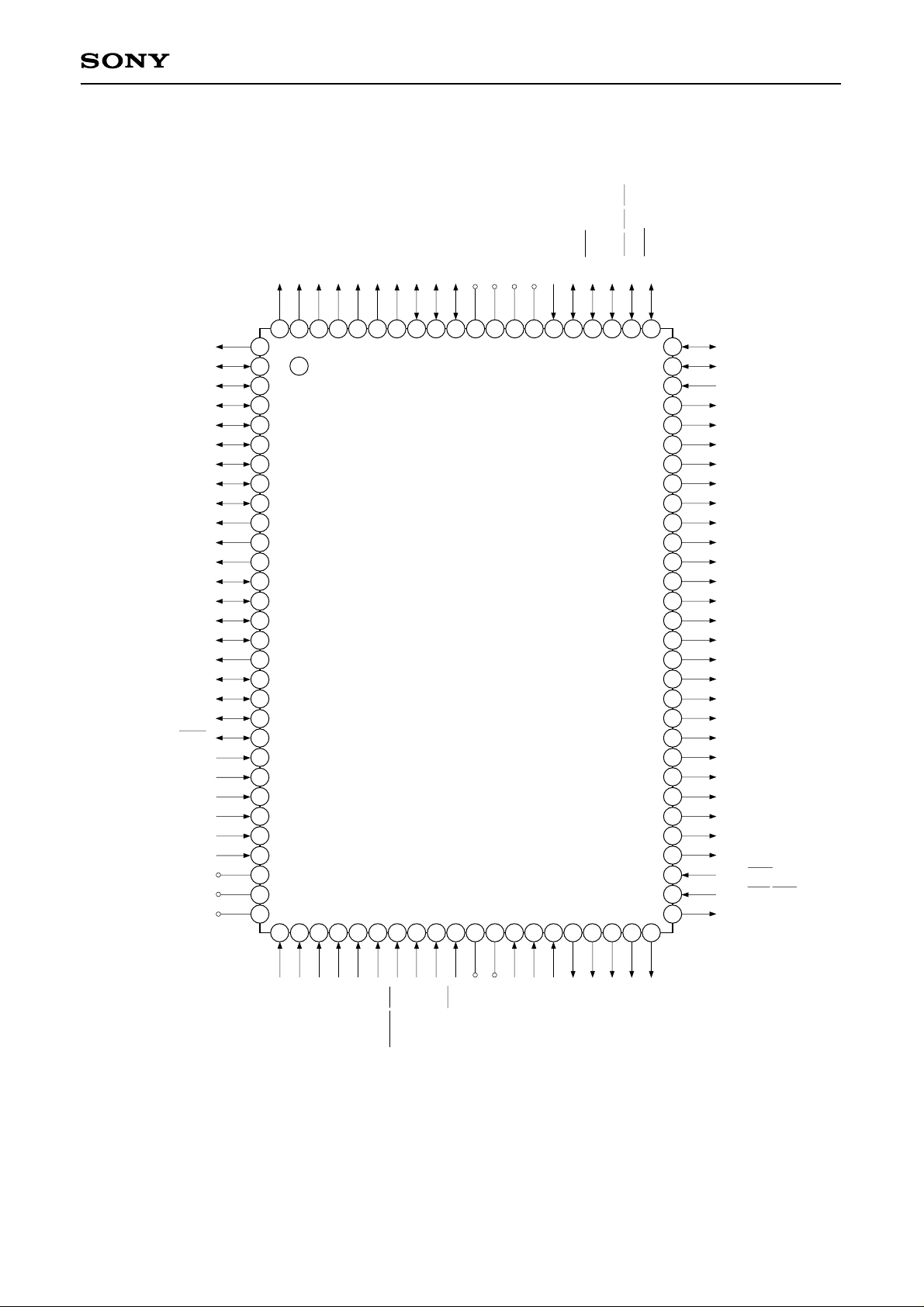

PA0 to PA7

(Common with PPO pin)

4

PB0 to PB7

4

PORT A8PORT B8PORT C

PF4 to PF7

(Common with A/D input pin)

PE0 to PE1

PD0 to PD7

PC0 to PC7

(Common with PPO, RTO pins)

(Common with interruption pin)

PE2 to PE7

2

8

PORT D

(Common with PWM, DA pins)

PF0 to PF3

(Common with A/D input pin)

6

PORT E

4

(Standby release)

PG0 to PG7

(Common with SERVO

PF4 to PF7

input, EC input pins)

(Common with SIO pin)

4

PORT F8PORT G3PORT H7PORT I

PI0 to PI7

PH0 to PH2

(Common with key return input pin)

(Common with SIO, other I/O)

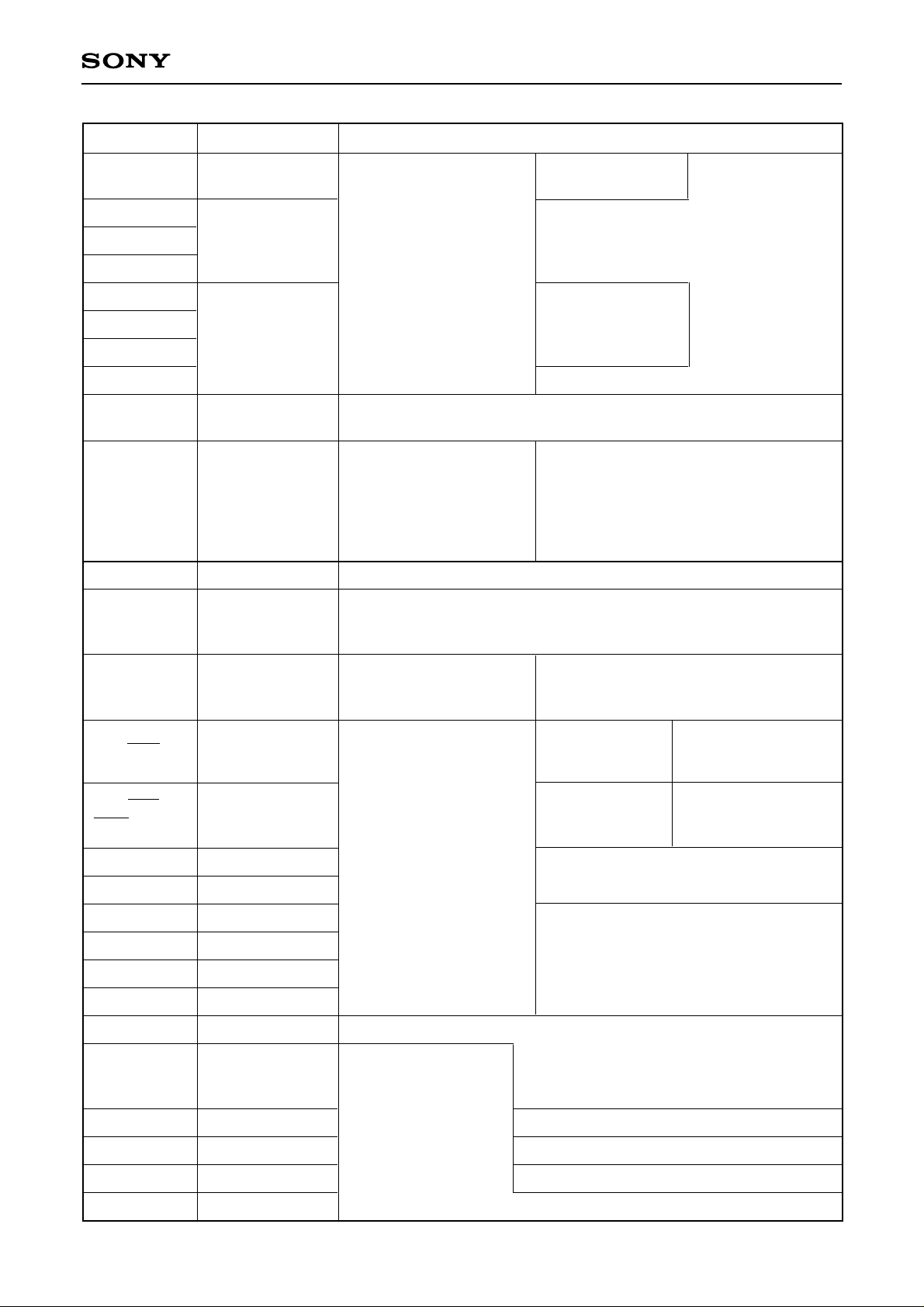

CXP88132/88140

Vss

DD

V

MP

RST

TX

TEX

XTAL

EXTAL

PE1/INT2

PI4/INT1/NMI

PE0/INT0

CLOCK

SPC700

NMI

2

GENERATOR/

CPU CORE

SYSTEM CONTROL

RAM

1296 BYTES

ROM

32k/40k BYTES

INTERRUPT CONTROLLER

2

2

PRESCALER/

TIME BASE TIMER

2

32kHz

TIMER/COUNTER

FIFO

FRC

CAPTURE UNIT

3

2

RAM

FDP

/DRIVER

CONTROLLER

CH

PULSE

REALTIME

CH0

GENERATOR

RAM

96BYTES

PATTERN

GENERATOR

PROGRAMABLE

2

4

(Common with Port D)

8

88

to

T8/S15

T15/S8

S0 to S7

T0 to T7

V

FDP

1

5

7

(Common with Port C)

RTO3 to RTO7

(Common with Port A)

PPO0 to PPO7

AVss

AV

REF

AV

DD

AN0 to AN3

Block Diagram

FIFO

(CH0)

SERIAL

A/D CONVERTERCONVERTER

INTERFACE UNIT

SERIAL INTERFACE UNIT

12

to

PF0/AN4

PI4/CS0

PF7/AN11

PI7/SI0

PI6/SO0

PF6/SI1

PI5/SCK0

PF5/SO1

(CH1)

8 BIT TIMER/COUNTER1

8 BIT TIMER/COUNTER 0

EC

SELECT

PE1/EC0

PF4/SCK1

PI3/TO/DD0

CONTROL

SERVO INPUT

V SYNC SEPARATOR

DRUM

CAPSTAN

PG1/DFG

PG0/CFG

PG7/EXI1

PG6/EXI0

PG5/SYNC1

PG2/DPG

PG4/SYNC0/EC2

– 2 –

FIFO

VISS/VASS

CTL

REMOCON INPUT

PI1/RMC

PG3/PBCTL/EC1

14 BIT PWM GENERATOR

PI2/PWM

PE2/PWM0

12 BIT PWM GENERATOR CH1

12 BIT PWM GENERATOR CH0

PE6/DAB0

PE4/DAA0

PE3/PWM1

PSEUDO HSYNC GENERATOR

PA0/HGO

PE7/DAB1

PE5/DAA0

Pin Configuration (Top View)

PB1

PB2

PB3

PB4

PB5

PB6

PB7

PH1/KR1

PH0/KR0

NC

PH2/KR2

CXP88132/88140

SS

DD

V

TX

V

TEX

PI2/PWM

PI1/RMC

PI5/SCK0

PI4/INT1/NMI/CS0

PI3/T0/DD0/ADJ

PB0

PC7/RTO7

PC6/RTO6

PC5/RTO5

PC4/RTO4

PC3/RTO3

PC2

PC1

PC0

PA7/PPO7

(HAMP) PA6/PPO6

(ROTA) PA5/PPO5

(RF-PLS) PA4/PPO4

PA3/PPO3

PA2/PPO2

PA1/PPO1

PA0/PPO0/HGO

PF7

PF6/SI1

PF5/SO1

PF4/SCK1

PF3/AN7

PF2/AN6

PF1/AN5

PF0/AN4

AN3

AN2

AVREF

AVSS

AVDD

10

11

12

13

14

15

16

17

18

19

20

21

22

23

25

26

27

28

29

30

24

100

99

98

1

2

3

4

5

6

7

8

9

32

31

33

97

34

96

35

95

36

94

37

93

38

92

39

91

40

90

41

89

42

88

43

44

87

45

86

46

85

47

84

48

83

82

49

81

50

80

79

78

77

76

75

74

73

72

70

69

68

67

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

71

66

PI6/SO0

PI7/SI0

VFDP

PD0/S0

PD1/S1

PD2/S2

PD3/S3

PD4/S4

PD5/S5

PD6/S6

PD7/S7

T15/S8

T14/S9

T13/S10

T12/S11

T11/S12

T10/S13

T9/S14

T8/S15

T7

T6

T5

T4

T3

T2

T1

T0

PE0/INT0 (ENV-DET)

PE1/EC0/INT2

PE2/PWM0

SS

MP

AN1

AN0

PG6/EXI0

PG7/EXI1

PG5/SYNC1

PG3/PBCTL/EC1

PG4/SYNC0/EC2

PG2/DPG

RST

V

XTAL

EXTAL

Note) 1. NC (Pin 90) is always connected to VDD.

2. Vss (Pins 41 and 88) are both connected to GND.

– 3 –

PG0/CFG

PG1/DFG

PE5/DAA1

PE6/DAB0

PE7/DAB1

PE4/DAA0

PE3/PWM1

Pin Description

Symbol I/O Description

CXP88132/88140

PA0/PPO0/

HGO

PA1/PPO1

PA2/PPO2

PA3/PPO3

PA4/PPO4

PA5/PPO5

PA6/PPO6

PA7/PPO7

PB0 to PB7

PC0/PPO8

to

PC7/PPO15

T0 to T7

T8/S15

to

T15/S8

Output/Real time

output/output

I/O/

Real time output

Output/

Real time output

Output

Output/

Real time output

Output

Output/Output

Pseudo HSYNC

output pin.

(Port A)

8-bit I/O port. Enable to

specify I/O by bit unit.

Data is gated with RTO

Real-time pulse generator (RTG) output.

Functions as high precision real-time

pulse output port.

(5 pins)

content by OR-gate and

they are output.

(8 pins)

Head switching

output pins.

8-bit output port. Tri-state can be controlled.

(8 pins)

(Port C)

8-bit I/O port. Enable to

specify I/O by bit unit.

Data is gated with RTO

content by OR-gate and

Real-time pulse generator (RTG) output.

Functions as high precision real-time pulse

output port.

(5 pins)

they are output. (8 pins)

FDP timing signal output pin.

Output pins for FDP timing signal and segment signal.

PD0 to PD7

PE0/INT0

PE1/EC0/

INT2

PE2/PWM0

PE3/PWM1

PE4/DAA0

PE5/DAA1

PE6/DAB0

PE7/DAB1

AN0 to AN3

PF0/AN0

to

PF3/AN3

PF4/SCK1

PF5/SO1

PF6/SI1

Output

Input/Input

Input/Input/Input

Output/Output

Output/Output

Output/Output

Output/Output

Output/Output

Output/Output

Input

Input/Input

I/O/I/O

I/O/Output

I/O/Input

(Port D)

8-bit output port.

FDP segment signal output pin.

(8 pins)

Trigger pulse

input pin for head

switching output.

External event

(Port E)

8-bit port.

Lower 2 bits are input pins

and upper 6 bits are

output pins.

input pin for

timer/counter.

PWM output pins.

(2 pins)

(8 pins)

DA gate pulse output pins.

(2 pins)

Analog input pins to A/D converter. (8 pins)

(Port F)

8-bit I/O port. Enable

to specify I/O by bit unit.

(8 pins)

Serial clock (CH1) I/O pin.

Serial data (CH1) output pin.

Serial data (CH1) input pin.

Input pin to request

external interruption.

Active when falling edge.

Input pin to request

external interruption.

Active when falling edge.

PF7

I/O

– 4 –

Symbol I/O Description

PG0/CFG

Input/Input

Capstan FG input pin.

CXP88132/88140

PG1/DFG

PG2/DPG

PG3/

PBCTL/EC1

PG4/

SYNC0/EC2

PG5/SYNC1

PG6/EXI0

PG7/EXI1

PH0/KR0

to

PH7/KR2

PI1/RMC

PI2/PWM

PI3/TO/

DDO/ADJ

PI4/INT1/

NMI/CS0

PI5/SCK0

Input/Input

Input/Input

Input/Input/Input

Input/Input/Input

Input/Input

Input/Input

Input/Input

I/O/Input

I/O/Input

I/O/Input

I/O/Input

I/O/Input/

Input/Input

I/O/Input

(Port G)

8-bit input port.

(8 pins)

(Port H)

3-bit I/O port.

(3 pins)

(Port I)

8-bit I/O port.

Enable to

specify I/O by

bit unit.

(8 pins)

Drum FG input pin.

Drum PG input pin.

External event

Playback CTL input pin.

input pin for

timer/counter.

External event

input pin for

Composite sync signal input pin.

timer/counter.

External input pin for FRC capture unit.

Key return input signal for key scanning at FDP

segment signal.

Remote control receiving circuit input pin.

14-bit PWM output pin.

Timer/counter, CTL duty detection, 32kHz oscillation

adjustment output pin.

Input pin to request external interruption,

non-maskable interruption and for serial chip select

(CH0). Active when falling edge.

Serial clock (CH1) I/O pin.

PI6/SO0

PI7/SI0

EXTAL

XTAL

TEX

TX

RST

MP

VFDP

AVDD

AVREF

AVss

VDD

Vss

I/O/Output

I/O/Input

Input

Output

Input

Output

Input

Input

Input

Serial data (CH1) output pin.

Serial data (CH1) input pin.

Connecting pin of crystal oscillator for system clock.

When supplying the external clock, input the external clock to EXTAL

pin and input opposite phase clock to XTAL pin.

Connecting pin of crystal oscillator for 32kHz timer clock.

When used as event counter, input to TEX pin and leave TX pin open.

(Feedback resistor is not removed.)

System reset pin of active "L" level.

Microprocessor mode input pin. Always connect to GND.

FPD voltage supply pin when specifying internal resistor by mask

option.

Positive power supply pin of A/D converter.

Reference voltage input pin of A/D converter.

GND pin of A/D converter.

Positive power supply pin.

GND pin. Connect both Vss pins to GND.

– 5 –

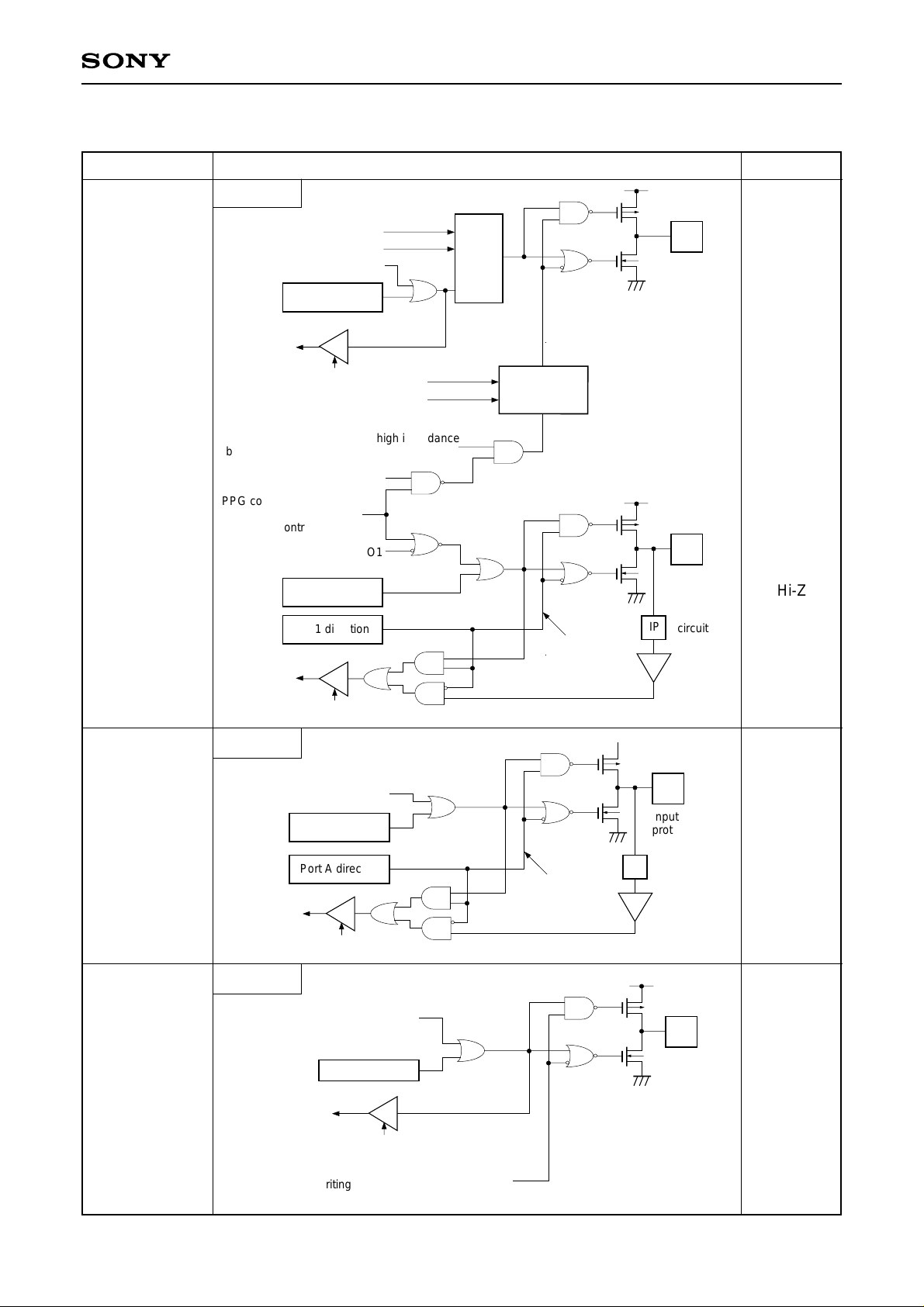

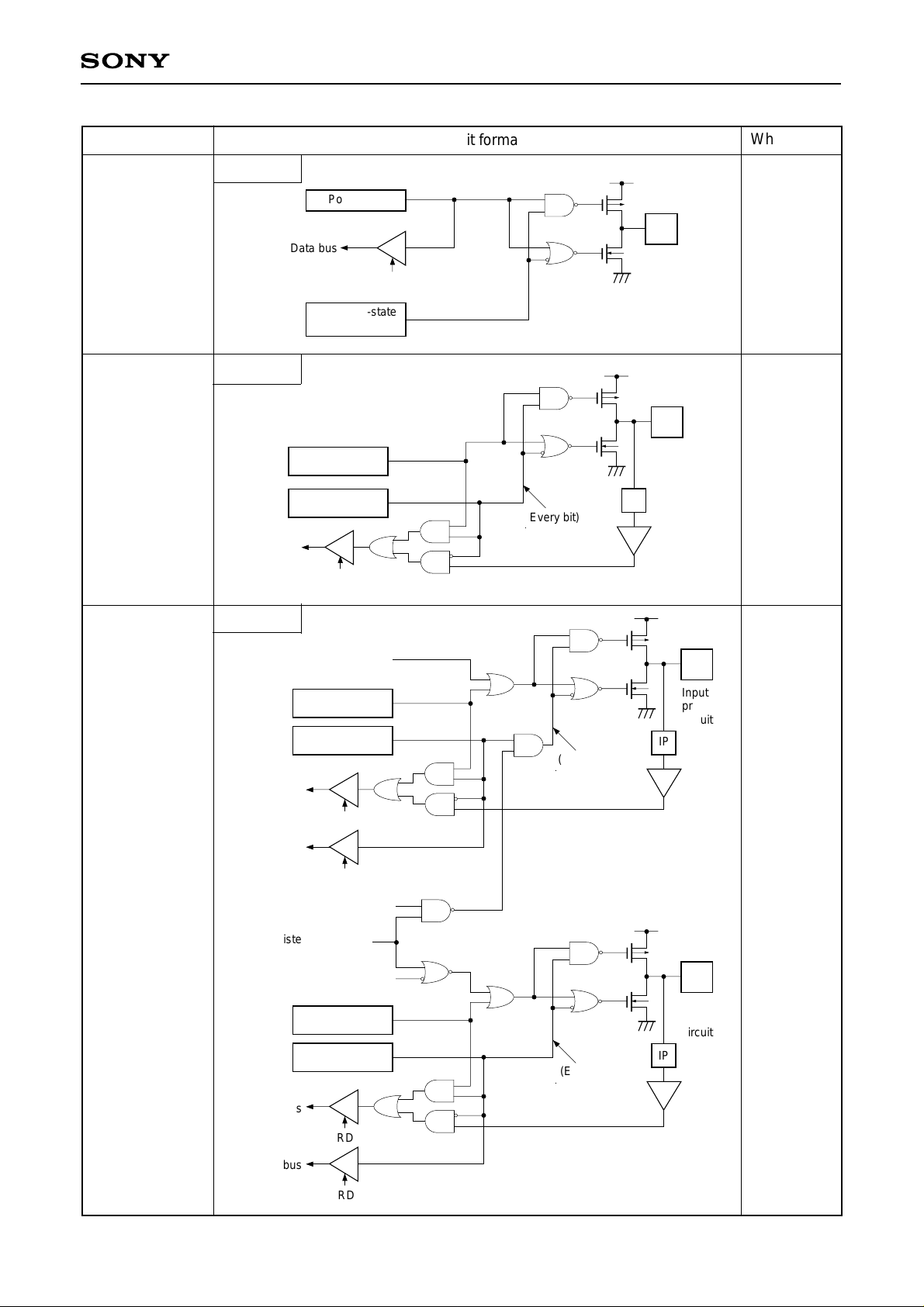

Input/Output Circuit Formats for Pins

CXP88132/88140

Pin

PA0/PPO0/

HGO

1 pin

PA1/PPO1

Circuit format

Port A

HSEL

HOUT

PPO0

PA0

Data bus

RD

(Port A)

Output becomes active from high impedance

by data writing to port register.

PPG control status

register bit 0

Tri-state control selection

PA0

PA1 direction

HSEL

HOUTE

PPO1

PPO1

MPX

MPX

(Every bit)

IP

Input

protection

circuit

When reset

Hi-Z

Hi-Z

1 pin

PA2/PPO2

to

PA4/PPO4

3 pins

PA5/PPO5

to

PA7/PPO7

Data bus

Port A

Data bus

Port A

RD (Port A)

Port A data

Port A direction

Data bus

PPO data

RD (Port A)

PPO data

Port A data

(Every bit)

IP

Input

protection

circuit

Hi-Z

Hi-Z

3 pins

RD (Port A)

Output becomes active from high impedance

by data writing to port register.

– 6 –

CXP88132/88140

PB0

to

PB7

8 pins

PC0

to

PC2

3 pins

Port B

Port C

Data bus

Port B data

Data bus

Port B tri-state

control

Port C data

Port C direction

RD (Port C)

Circuit format

RD (Port B)

(Every bit)

IP

Input

protection

circuit

When resetPin

Hi-Z

Hi-Z

PC3/RTO3

1 pin

PC3/RTO4

Port C

RTO3

PC3

PC3 direction

Data bus

RD (Port C)

Data bus

RD (Port C)

RTG interruption

control register bit 7

Tri-state control selection

PC4

PC4 direction

RTO4

RTO4

(Every bit)

(Every bit)

IP

IP

Input

protection

circuit

Input

protection

circuit

Hi-Z

Hi-Z

1 pin

Data bus

RD (Port C)

Data bus

RD (Port C)

– 7 –

CXP88132/88140

PC5/RTO5

to

PC7/RTO7

3 pins

PD0/S0

to

PD7/S7

8 pins

Port C

Port C data

Port C direction

Data bus

RD (Port C)

Port D

Segment output data

Output selection control signal

("0" when reset)

Port D data

Data bus

RD (Port D)

RTO data

Circuit format

Pull-down resistor

(Every bit)

OP

Input

protection

circuit

IP

High voltage drive

transistor

Mask option

VFDP

When resetPin

Hi-Z

Hi-Z

T0 to T7

8 pins

T8/S15

to

T15/S8

8 pins

Timing output data

Output selection control signal

("0" when reset)

Timing output data

Output selection control signal

("0" when reset)

Segment output data

Pull-down resistor

Pull-down resistor

High voltage drive

transistor

OP

Mask option

High voltage drive

transistor

Mask option

OP

Hi-Z

VFDP

Hi-Z

VFDP

– 8 –

Loading...

Loading...