Sony CXP823P24 Datasheet

CMOS 8-bit Single Chip Microcomputer

Description

The CXP823P24 is a highly integrated CMOS 8-bit

single-chip microcomputer which is mainly composed

of an 8-bit CPU, PROM, RAM and I/O ports. This

microcomputer features many other high-performance

circuits in a single-chip CMOS design, including an

A/D converter, serial interface, timer/counter, timebase timer, capture timer/counter, fluorescent display

tube controller/driver, and remote control receiver.

Also, the CXP823P24 provides the power-on reset

function as well as the sleep/stop function which

assures reduced power consumption.

Being a PROM-incorporated version of the

CXP82324 which has on-chip mask ROM, the

CXP823P24 permits program writing. Therefore, it is

ideally suited for use in system development stage

evaluation and job lot production.

Structure

Silicon gate CMOS IC

CXP823P24

80 pin QFP (Plastic)

Features

• Instruction set which supports a wide array of data types 213 types

— 16-bit arithmetic instruction/multiplication and division instructions/boolean bit operation instruction

• Minimum instruction cycle During operation 400ns/10MHz

• Incorporated PROM capacity 24K bytes

• Incorporated RAM capacity 704 bytes (Including fluorescent display data area)

• Peripheral functions

— A/D converter 8-bit, 8-channel, successive comparison type

(conversion time: 32µs at 10MHz)

— Serial interface 1 channel data interface with an 8-bit, 8-stage FIFO

(1 to 8 byte automatic transfer)

1-channel, 8-bit clock synchronized interface

— Timers 8-bit timer

8-bit timer/counter

19-bit time-base timer

16-bit capture timer/counter

— Fluorescent display tube controller/driver

Display of up to 336 segments

1 to 16 digit dynamic display

Dimmer function

High voltage tolerance output (40V)

Built-in pull-down resistor

— Remote control receiver Built-in noise suppressor circuit

Built-in 8-bit pulse counter and 6-stage FIFO

• Interrupts 14 factors, 15 vectors, multiple interrupt pocessing

• Standby mode Sleep/stop

• Package 80-pin plastic QFP

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E92Y35A78-PS

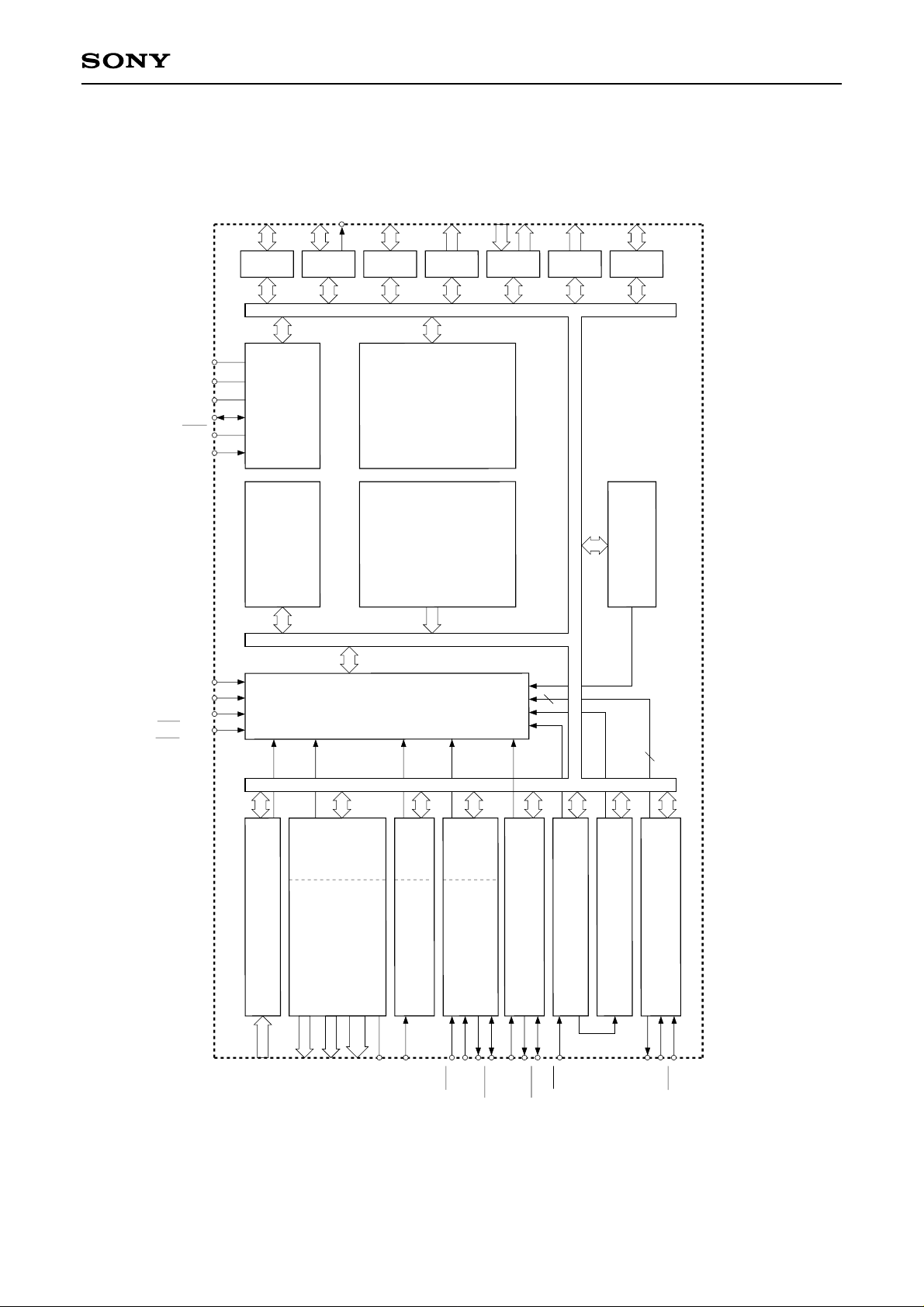

CXP823P24

V

SS

Vpp

V

DD

RST

XTAL

EXTAL

PA0 to PA7

8

PB0 to PB6

7

PORT A

CLOCK

GENERATOR/

SYSTEM CONTROL

SPC700

CPU CORE

PB7

PORT B

PC0 to PC7

8

PORT C

RAM

704 BYTES

PROM

24K BYTES

PD0 to PD7

8

PE0 to PE5

6

PORT D

PE6 to PE7

2

PF0 to PF7

8

PORT E

PORT F

PRESCALER/

PG0 to PG3

4

PORT G

TIME BASE TIMER

Block Diagram

PE3/INT3

PE2/INT2

PE1/EC1/INT1

PE0/EC0/INT0

A/D CONVERTER

8

PA0/AN0 to

PA7/AN7

RAM

80 BYTES

FDP

CONTROLLER/

8

8

T0 to T7

T8/S28 to

T15/S21

DRIVER

21

FDP

V

S0 to S20

FIFO

REMOCON

PE4/RMC

INTERRUPT CONTROLLER

2

FIFO

UNIT 0

SERIAL

INTERFACE

PB3/SI0

PB1/CS0

PB0/SO0

PB2/SCK0

PB6/SI1

8 BIT TIMER/COUNTER 0

SERIAL INTERFACE UNIT 1

PB7/SO1

PB5/SCK1

PE0/INT0/EC0

2

8 BIT TIMER 1

16 BIT CAPTURE

TIMER/COUNTER 2

PE7/TO

PB0/CINT

PE1/INT1/EC1

– 2 –

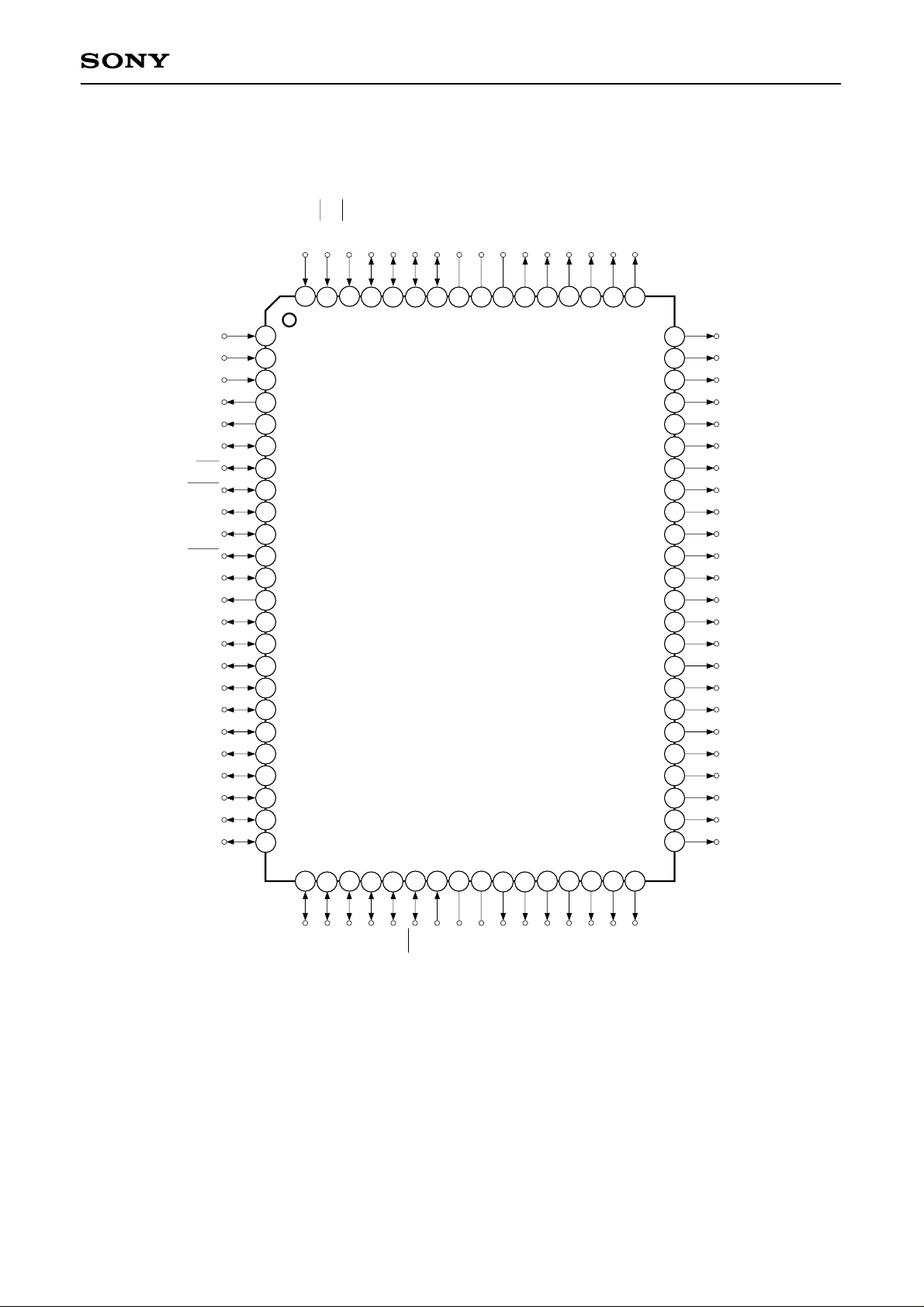

Pin Assignment (Top View)

PE1/EC1/INT1

PE2/IN2

PE0/EC0/INT0

PG3

PG2

PG1

PG0

Vpp

DD

V

FDP

V

T0

T1

T2

T3

T4

CXP823P24

T5

PE3/INT3

PE4/RMC

PE5

PE6

PE7/TO

PB0/CINT

PB1/CS0

PB2/SCK0

PB3/SI0

PB4/SO0

PB5/SCK1

PB6/SI1

PB7/SO1

PC0/KR0

PC1/KR1

PC2/KR2

PC3/KR3

PC4/KR4

PC5/KR5

PC6/KR6

PC7/KR7

PA0/AN0

PA1/AN1

PA2/AN2

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

80

78

79

1

2

3

4

5

6

7

8

9

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

T6

T7

T8/S28

T9/S27

T10/S26

T11/S25

T12/S24

T13/S23

T14/S22

T15/S21

S20

S19

S18

S17

S16

PF7/S15

PF6/S14

PF5/S13

PF4/S12

PF3/S11

PF2/S10

PF1/S9

PF0/S8

PD7/S7

25

26

PA3/AN3

27

28

PA4/AN4

PA5/AN5

29

PA7/AN7

PA6/AN6

30

31

RST

32

XTAL

EXTAL

33

SS

V

34

Note) Vpp (Pin 73) is always connected to VDD.

– 3 –

35

PD1/S1

PD0/S0

36

PD2/S2

37

PD3/S3

38

PD4/S4

39

PD5/S5

40

PD6/S6

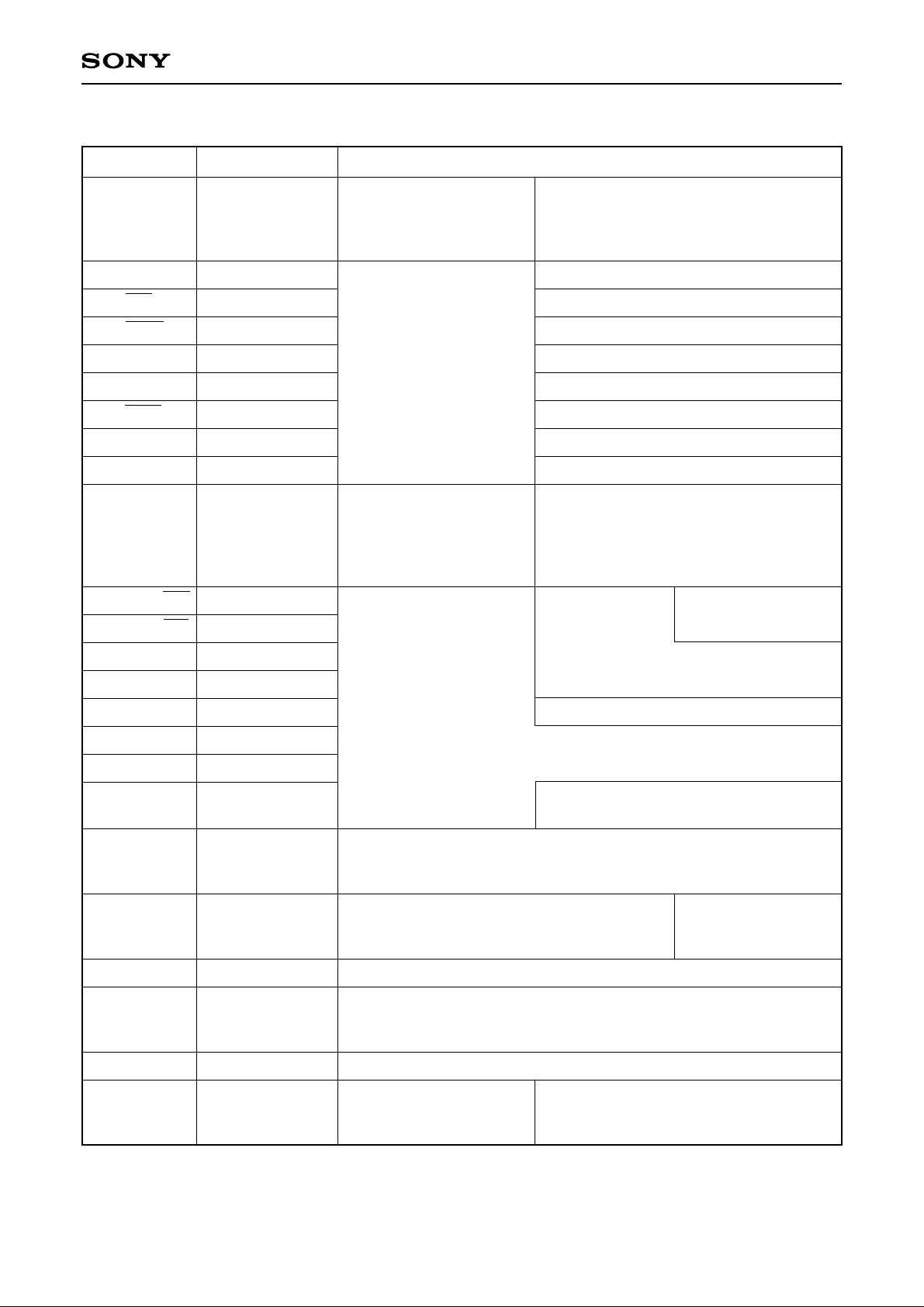

Pin Description

Symbol I/O Description

CXP823P24

PA0/AN0

to

PA7/AN7

PB0/CINT

PB1/CS0

PB2/SCK0

PB3/SI0

PB4/SO0

PB5/SCK1

PB6/SI1

PB7/SO1

PC0/KR0

to

PC7/KR7

PE0/INT0/EC0

PE1/INT1/EC1

PE2/INT2

PE3/INT3

PE4/RMC

PE5

PE6

I/O/Analog input

I/O/Input

I/O/Input

I/O/I/O

I/O/Input

I/O/Output

I/O/I/O

I/O/Input

Output/Output

I/O/Input

Input/Input/Input

Input/Input/Input

Input/Input

Input/Input

Input/Input

Input

Output

(Port A)

8-bit port; single bit

addressable.

(8 pins)

(Port B)

Single bit addressable from

amongst lower 7 bits;

highest bit (PB7)

dedicated to output.

(8 pins)

(Port C)

8-bit port; single bit

addressable. Can provide

12mA sink current.

(8 pins)

(Port E)

8-bit port with lower 6 bits

dedicated to input and

upper 2 bits dedicated to

output.

(8 pins)

Analog input to A/D converter.

(8 pins)

External capture input for 16-bit timer/counter.

Chip select input for serial interface (CH0).

Serial clock (CH0) input/output.

Serial data (CH0) input.

Serial data (CH0) output.

Serial clock (CH1) input/output.

Serial data (CH1) input.

Serial data (CH1) output.

Key return input for FDP segment signal

which performs key scanning.

External event input

to timer/counter.

Input for external

(2 pins)

interrupt requests.

(4 pins)

Input for remote control receiving circuit.

PE7/TO

PG0 to PG3

PF0/S8

to

PF7/S15

S16 to S20

T8/S28

to

T15/S21

T0 to T7

PD0/S0

to

PD7/S7

Output/Output

I/O

Output/Output

Output

Output/Output

Output

Output/Output

Output pin for 16-bit timer/counter

rectangular waveform.

(Port G)

4-bit input/output port; single bit addressable.

(4 pins)

(Port F)

8-bit dedicated output port.

(8 pins)

Segment signal

output for FDP.

Segment signal output for FDP.

Dual purpose output for FDP timing and segment signals.

Timing signal output for FDP.

(Port D)

8-bit dedicated output port.

Segment signal output for FDP.

(8 pins)

– 4 –

Symbol I/O Description

CXP823P24

VFDP

EXTAL

XTAL

RST

Vpp

VDD

VSS

Input

Output

I/O

Provides voltage for FDP.

Connection for system clock oscillation crystal. When using an external

clock, input normal signal to EXTAL and reverse phase signal to the

XTAL pin.

System reset, active "L". The RST pin is an input/output pin which

outputs a "L" level from the on-chip power on reset circuit when the

power is turned on.

Positive power supply for the programmable on-chip PROM; connect to

VDD for nomal operation.

Positive power supply pin.

GND

– 5 –

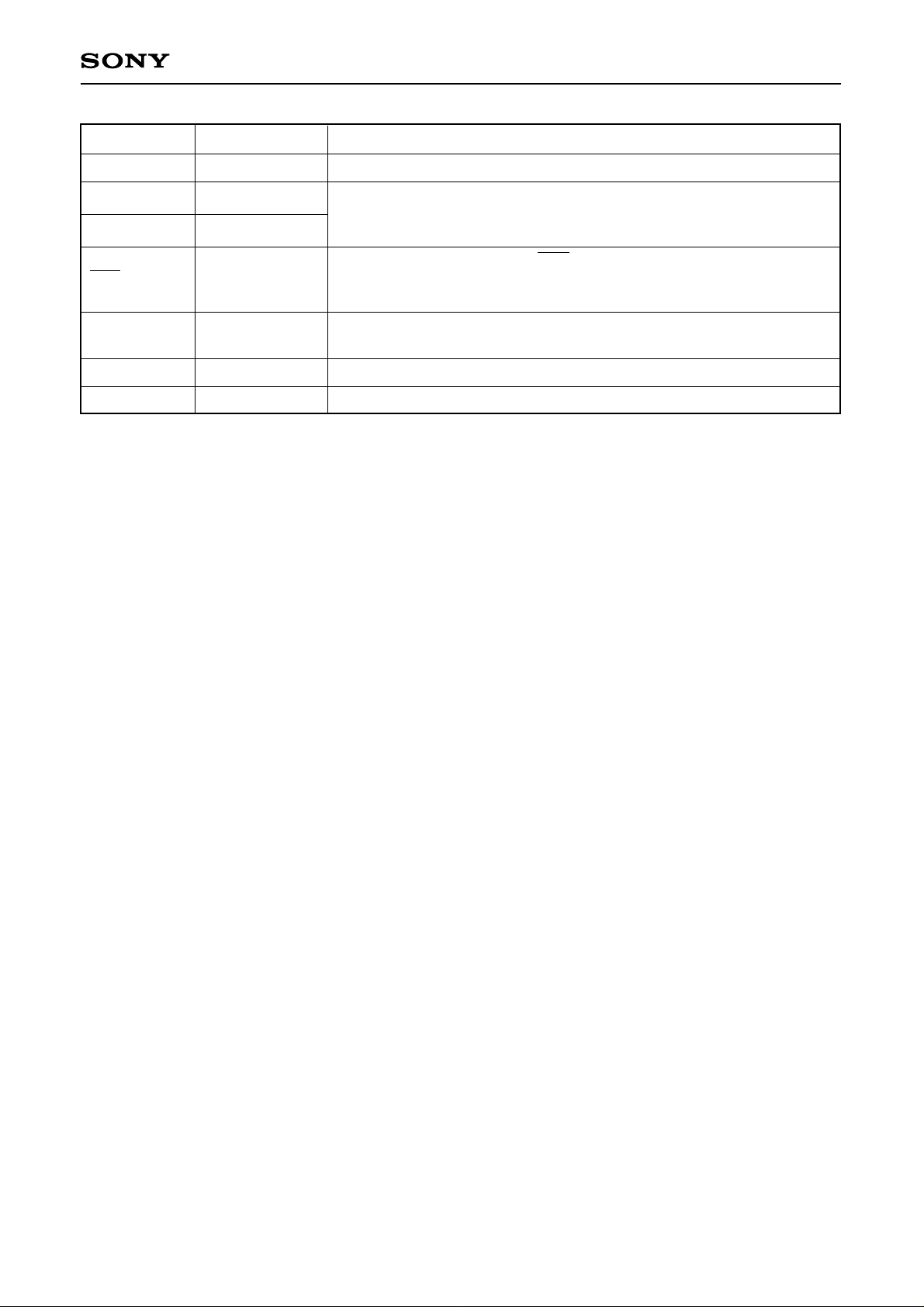

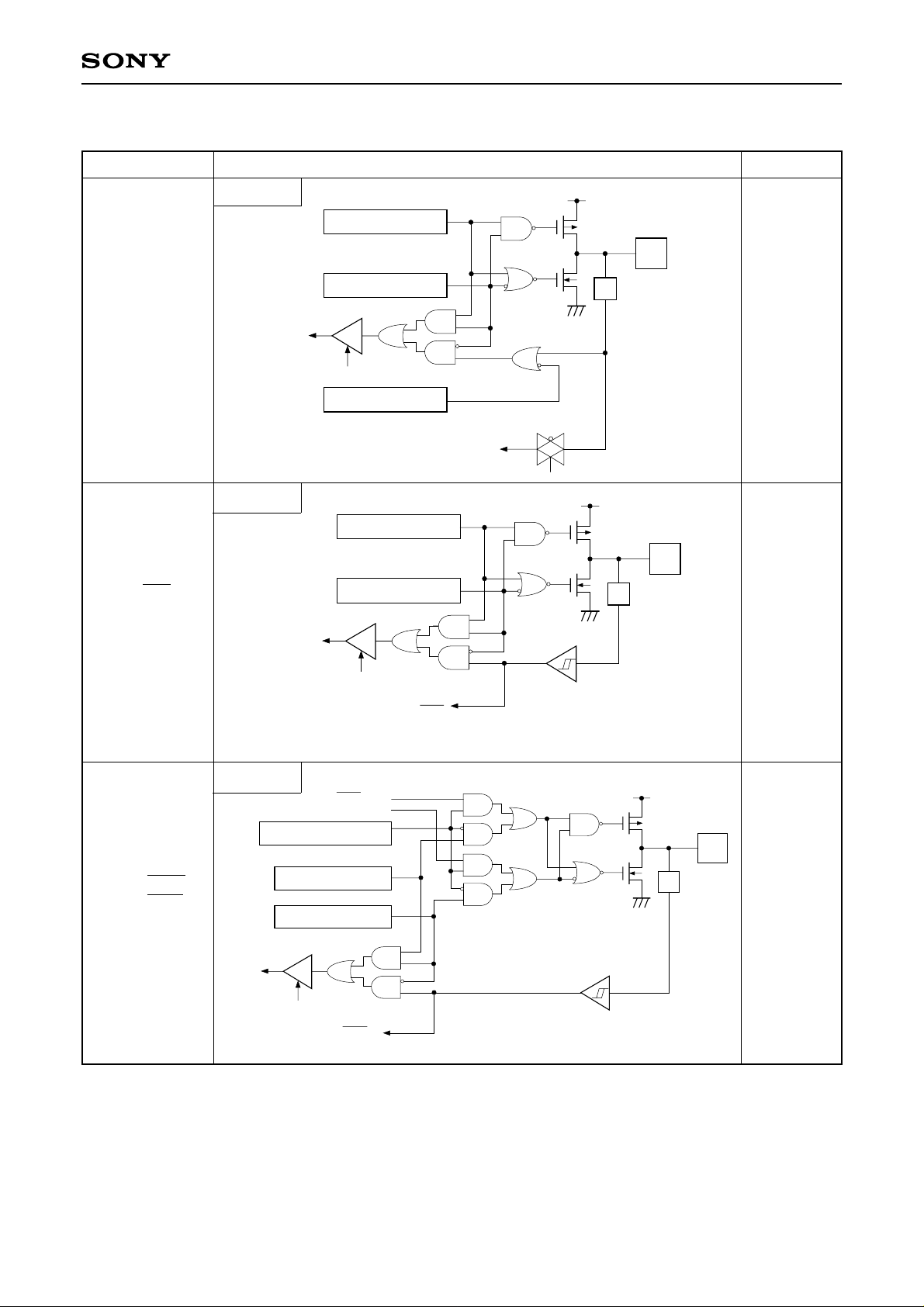

Input/Output Circuit Formats for Pins

CXP823P24

Pin

PA0/AN0

to

PA7/AN7

8 pins

PB0/CINT

PB1/CS0

PB3/SI0

PB6/SI1

Port A

Data bus

Port B

Data bus

Port A data

Port A direction

"0" when reset

RD (Port A)

Port A input select

"0" when reset

Port B data

Port B direction

"0" when reset

Circuit format

A/D converter

Input multiplexer

Schmitt input

IP

When reset

Input

protection

circuit

Hi-Z

IP

Hi-Z

4 pins

PB2/SCK0

PB5/SCK1

2 pins

Port B

Port B output select

"0" when reset

"0" when reset

Data bus

RD (Port B)

SCK OUT

Output enable

Port B data

Port B direction

RD (Port B)

SCK in

CINT

CS0

SI0

SI1

IP

Hi-Z

Schmitt input

– 6 –

Loading...

Loading...