Sony CXP508L6, CXP508L4 Datasheet

CXP508L4/508L6

For the availability of this product, please contact the sales office.

CMOS 4-bit Single Chip Microcomputer

Description

The CXP508L4/508L6 is a CMOS 4-bit microcomputer which consists of 4-bit CPU, ROM, RAM,

I/O port, 8-bit timer, 8-bit timer/counter, 18-bit time

base timer, 8-bit serial I/O, vector interruption, and a

liquid crystal displayer (LCD) controller/driver. They

are integrated into a single clip with the standby

function etc. which are to be operated at low power

consumption.

64 pin SDIP (Plastic) 64 pin QFP (Plastic)

Features

• Instruction cycle 4µs/2MHz (2.4V to 3.5V)

• ROM capacity 4.096 × 8 bits (CXP508L4)

6.144 × 8 bits (CXP508L6)

• RAM capacity 400 × 4 bits

(24 × 4 bits is used in combination

with the LCD display memory)

• 32 general purpose I/O ports

(For 16 segment outputs)

• LCD controller/driver (Direct drive possible)

— Optical specification of 24, 20 or 16 segment

outputs

— 1/2, 1/3, 1/4 duty selectable through program

— 1/3 bias

• 2 external interruption input pins

• 8-bit/4-bit variable serial I/O

• 8-bit timer, 8bit timer/event counter and 18-bit time

base timer are independently controllable

• Arithmetic and logical operations possible between

the entire RAM area, I/O area and the accumulator

by means of memory mapped I/O

• Reference to the entire ROM area is possible with

the table look-up instruction

• 2 types of power down models, sleep and stop

• 64-pin plastic SDIP/QFP available

• Piggy back package (CXP5080) available

Structure

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E95108-ST

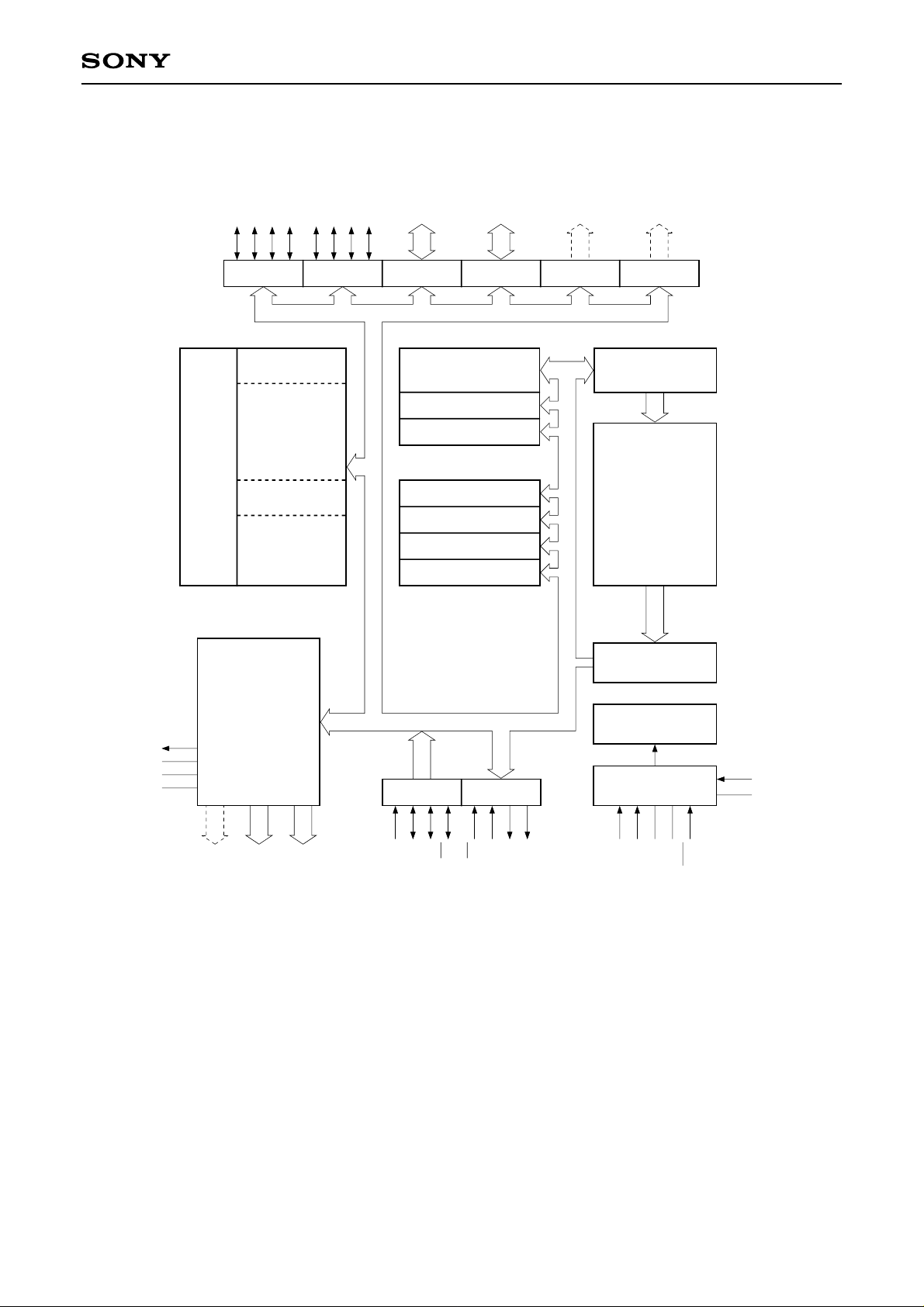

Block Diagram

CXP508L4/508L6

400 × 4

bits

(Enables to specify the

I/O with bit unit)

Port A Port B Port C Port D Port E Port F

Register

Data memory

Stack

Data memory

(Enables to specify the

I/O with port unit)

4 4 4 4

ALU

Accumulator

Flag

Timer (8)

Timer/Counter (8)

Serial I/O (8)

Interrupt control

(Combines use of mask with

segment output, optional)

Program counter

Program memory

6144 × 8 bits

(CXP508L6)

4096 × 8 bits

(CXP508L4)

(13)

LCD

controller/driver

VL

VLC1

VLC2

VLC3

SEG16

to

SEG23

(Common with Port E, Port F)

1684

SEG0

COM0

to

SEG15

to

COM3

Port YPort X

PX3/SI

(Common with serial I/O)

PX0/SC

PX2/SOA

PX1/SOB

PY3/EC

PY2/INT2

PY1

PY0

Instruction control

Time base timer

(18)

Clock control

SS

DD

WP

INT1

V

V

EXTAL

XTAL

RST

– 2 –

Pin Configuration (Top View)

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26 27

28

29

30

31

32

1

40

39

38

37

36

35

34

33

41

42

43

44

45

46

47

48

49

50

51

PY0

PY1

INT2/PY2

EC/PY3

SC/PX0

SOB/PX1

SOA/PX2

SI/PX3

PD0

PD1

PD2

PD3

PC0

PC1

PC2

PC3

PB0

PB1

PB2

PB3

PA0

PA1

PA2

PA3

Vss

NC

PE3/SEG23

PE2/SEG22

PE1/SEG21

PE0/SEG20

PF3/SEG19

PF2/SEG18

COM3

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16/PF0

SEG17/PF1

INT1

WP

RST

EXTAL

XTAL

V

L

V

DD

V

LC3

V

LC2

V

LC1

COM0

COM1

COM2

52

53

54

55

56

57

58

59

60

63

64

61

62

CXP508L4/508L6

XTAL

EXTAL

RST

WP

INT1

PY0

PY1

INT2/PY2

EC/PY3

SC/PX0

SOB/PX1

SOA/PX2

SI/PX3

PD0

PD1

PD2

PD3

PC0

PC1

PC2

PC3

PB0

PB1

PB2

PB3

PA0

PA1

PA2

PA3

NC

Vss

VL

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

VDD

VLC3

VLC2

VLC1

COM0

COM1

COM2

COM3

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16/PF0

SEG17/PF1

SEG18/PF2

SEG19/PF3

SEG20/PE0

SEG21/PE1

SEG22/PE2

SEG23/PE3

Note) Do not make any connection to NC pin.

– 3 –

CXP508L4/508L6

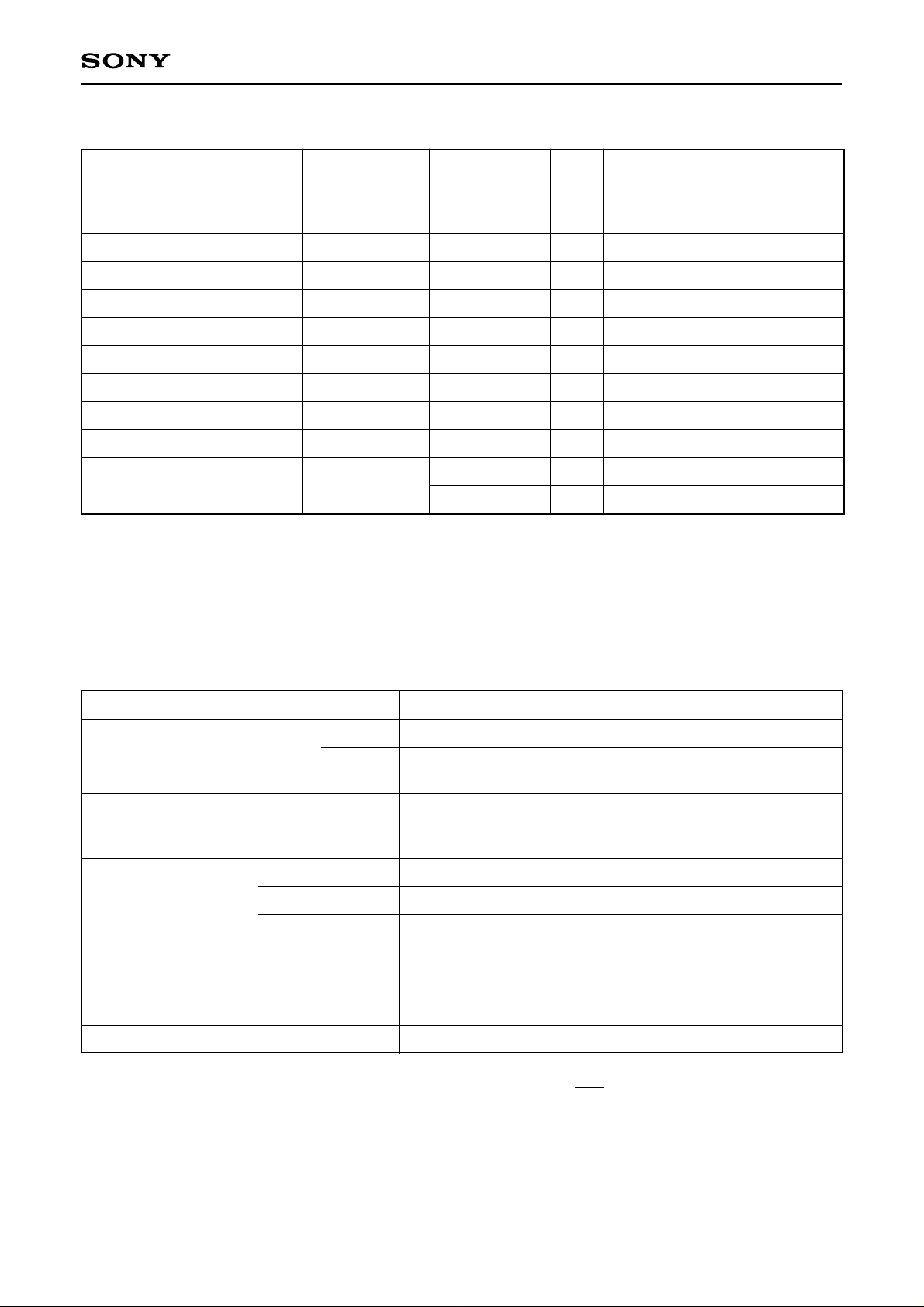

Absolute Maximum Ratings

Item

Power supply voltage

LCD bias voltage

Input voltage

Output voltage

High level output current

High level total output current

Low level output current

Low level total output current

Operating temperature

Storage temperature

Allowable power dissipation

∗1

VLC1, VLC2, VLC3, VIN and VOUT should not exceed VDD + 0.3V.

∗2

The PE and PF are specified when PA to PD, PX0 to PX2, PY0, PY1 and mask option are port selected.

Symbol Ratings Unit Remarks

VDD

VLC1, VLC2, VLC3

VIN

VOUT

IOH

∑IOH

IOL

∑IOL

Topr

Tstg

–0.3 to +5.0

–0.3 to +5.0

–0.3 to +5.0

–0.3 to +5.0

–5

–50

15

50

–20 to +75

–55 to +150

1000

∗1

∗1

∗1

V

V

V

V

mA

mA

mA

mA

°C

°C

mW

PD

600

mW

(Ta = –20 to +75°C, VSS = 0V)

General purpose port∗2: per pin

Entire pin total

General purpose port∗2: per pin

Entire pin total

SDIP

QFP

Note) Usage exceeding absolute maximum ratings may permanently impair the LSI. Normal operation should

better take place under the recommended operating conditions. Exceeding those conditions may

adversely affect the reliability of the LSI.

Recommended Operating Conditions

Item

Power supply voltage VDD

Symbol Min.

2.4

2.0

Max. Unit Remarks

3.5

3.5

V

Guaranteed range during operation

Guaranteed data hold operation range

V

during STOP

VLC1,

LCD bias voltage

VLC2,

VSS

VDD

V

Liquid crystal power supply voltage

VLC3

VIH

High level input voltage

VIHS

VIHEX

VIL

Low level input voltage

VILS

VILEX

Operating temperature

∗1

The optimum value is determined by the characteristics of the liquid crystal display element used.

∗2

They are the respective pins of INT1, WP, PX0, PX3, PY2, PY3 and RST.

∗3

Specified only during external clock input.

Topr

0.7VDD

0.8VDD

VDD – 0.4

0

0

–0.3

–20

VDD

VDD

VDD + 0.3

0.3VDD

0.2VDD

0.4

+75

V

V

Hysteresis input

V

EXTAL pin

V

V

Hysteresis input

V

EXTAL pin

°C

∗2

∗3

∗2

∗3

(VSS = 0V)

∗1

– 4 –

Loading...

Loading...