CCD Delay Line for NTSC

For the availability of this product, please contact the sales office.

Description

The CXL1512M is an IC developed for use in

conjunction with Y/C signal processing ICs for NTSC.

This CCD delay line provides the comb filter output

for eliminating the chrominance signal cross talk and

1H delay output for luminance signals.

Features

• Single power supply (5V)

• Built-in quadruple progression PLL circuit

• Built-in comb filter

• 1H delay output

• Built-in peripheral circuits

• Positive phase signal input, positive phase signal output

CXL1512M

24 pin SOP (Plastic)

Functions

• Comb filter output

• 1H delay output for luminance signal

• Clock driver

• Autobias circuit

• Input clamp circuit (for luminance signals)

• Center bias circuit (for chrominance signals)

• Sample-and-hold circuit

• Quadruple progression PLL circuit

• Clock buffer output circuit

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD +6 V

• Operating temperature Topr –10 to +60 °C

• Storage temperature Tstg –55 to +150 °C

•

Allowable power dissipation

Recommended Operating Voltage (Ta = 25°C)

PD 500 mW

VDD 5V ± 5%

Structure

CMOS-CCD

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E94803-ST

Recommended Clock Conditions (Ta = 25*C)

• Input clock amplitude VCLK 0.3Vp-p to 1.0Vp-p (0.5Vp-p Typ.)

• Clock frequency fCLK 3.579545MHz

• Input clock waveform sine wave

Input Signal Amplitude

Vsig 350mVp-p (Typ.), 575mVp-p (Max.)

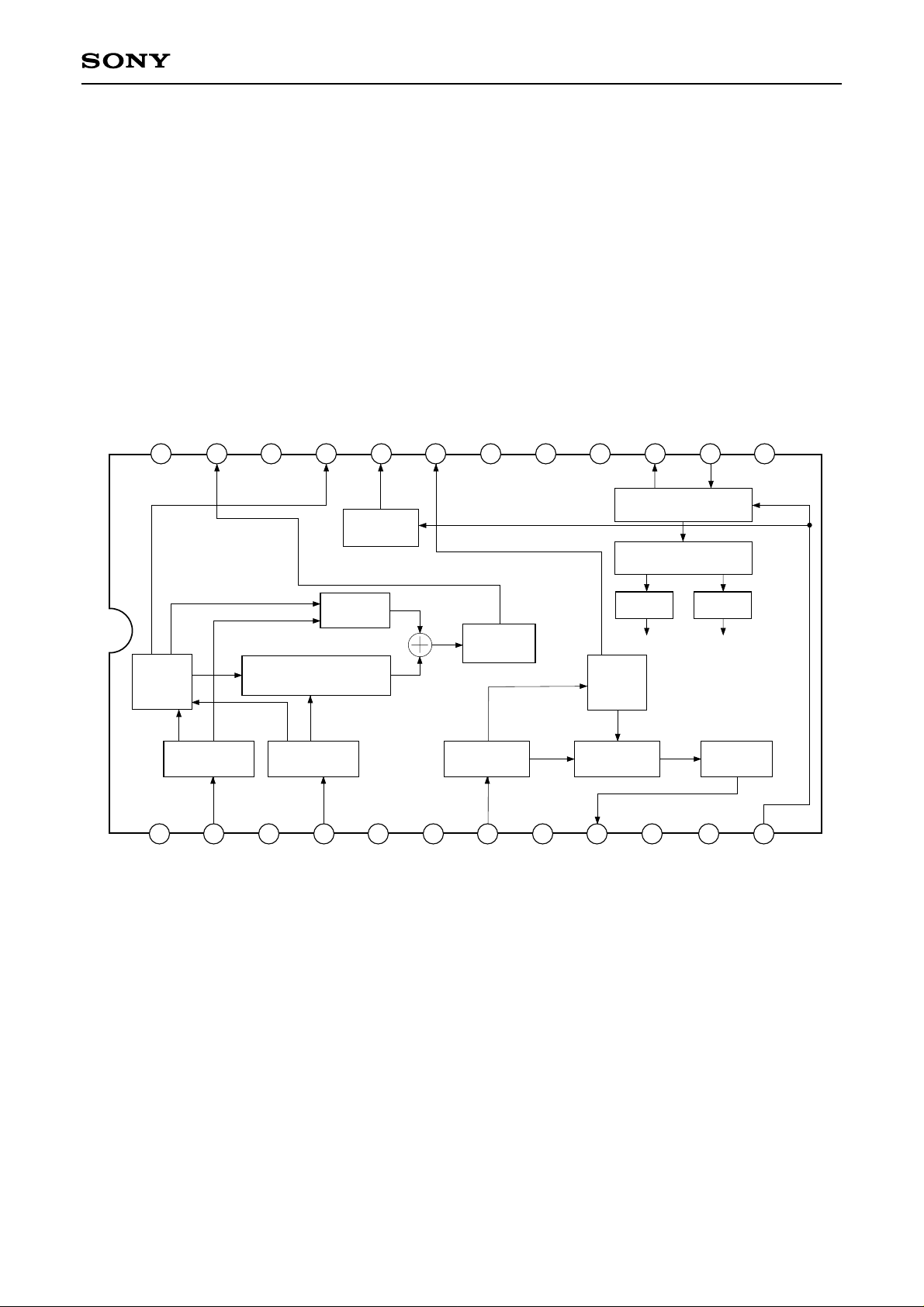

Block Diagram and Pin Configuration (Top View)

CXL1512M

Vss

24

Autobias

circuit (C)

1

Vss

C-OUT

23

Bias circuit Bias circuit Clamp circuit 1H

2

C-IN1

22

3

(IC)

DD

V

AB-C

21

1H + D

4

C-IN2

fsc

20

fsc buffer

D

5

(NC)

AB-P

19

6

(IC)

(NC)

18

Output

circuit (S/H)

7

Y-IN

17

8

(NC)

(NC)

(NC)

16

Driver

Autobias

circuit (Y)

9

Y-OUT

PCOUT

Timing

φ1 φ2

10

(NC)

VCOIN

1415

PLL

Driver

circuit (S/H)

11

(NC)

Vss

13

Output

12

CLK

– 2 –

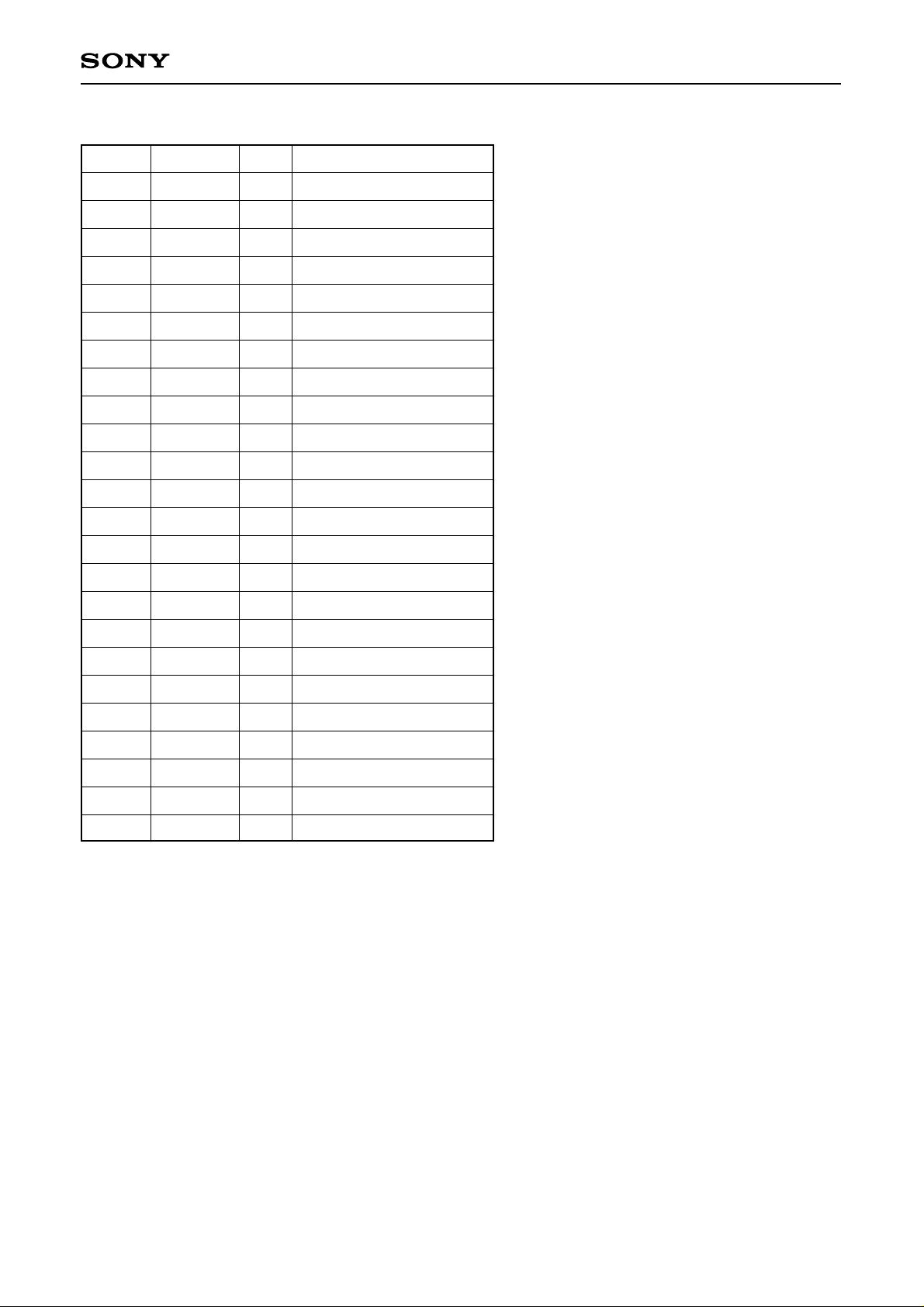

SOP 24pin

CXL1512M

Pin No.

1

2

3

4

5

∗

6

7

8

9

10

11

12

13

14

15

16

Symbol

VSS

C-IN1

VDD

C-IN2

(NC)

(IC)

Y-IN

(NC)

Y-OUT

(NC)

(NC)

CLK

VSS

VCOIN

PCOUT

(NC)

I/O

GND

—

Chrominance signal input 1

I

Power supply

—

Chrominance signal input 2

I

Description

—

(Connected internally)

—

Luminance signal input

I

—

Luminance signal output

O

—

—

Clock input

I

GND

—

VCO input

I

Phase comparator output

O

—

—

—

—

—

—

∗

(NC)

(NC)

AB-P

fsc

AB-C

(IC)

C-OUT

VSS

—

—

Autobias output (P)

O

fsc buffer output

O

Autobias output (C)

O

(Connected internally)

I

Chrominance signal output

O

GND

—

—

—

17

18

19

20

21

22

23

24

∗

Pins 6 and 22 are internally connected. Therefore, connect a voltage of 5V when using these pins.

– 3 –

Description of Functions

The CXL1512M provides chrominance signal comb filters and luminance signal delay outputs.

Number of CCD bits

CXL1512M

Chrominance comb filter output

Luminance signal delay output

1H (910bit)

1H (908bit)

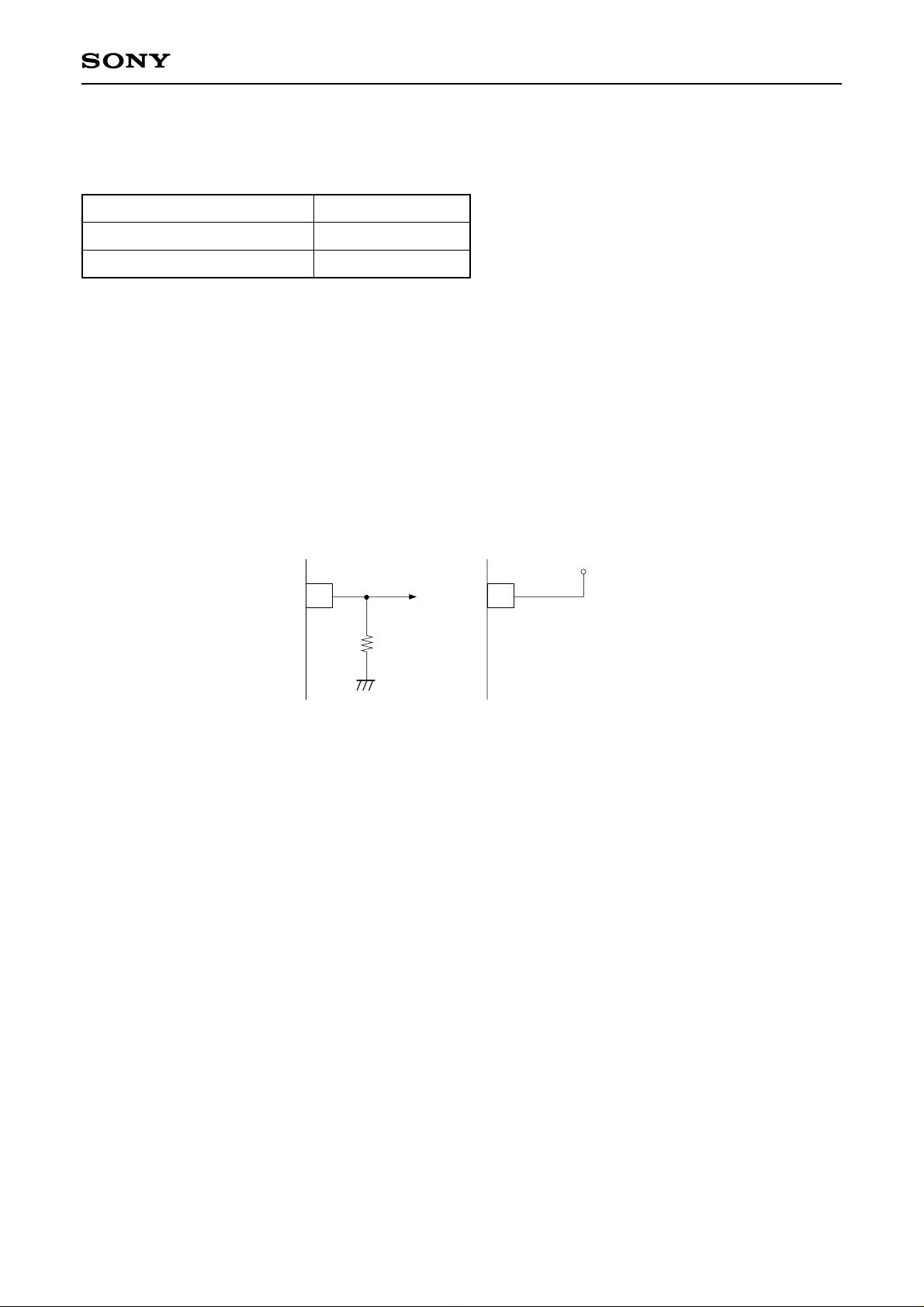

• fsc Output Pin

The buffer output of the clock input from the CLK pin is provided at the fsc output pin. Since a pull-up resistor

is contained inside the IC, the supply voltage is produced during open, and the output is stopped. Connect a

2.2kΩ pull-down resistor when the fsc output is to be used.

<When in use> <When not in use>

fsc

2.2k

fsc

VDD

– 4 –

Loading...

Loading...