CMOS-CCD Signal Processor

For the availability of this product, please contact the sales office.

Description

The CXL1501M is a CMOS-CCD signal processor

designed for 8-mm VCR video signal processing. In

combination with the 8-mm VCR video Y/C signal

processing IC CXA1200Q, this IC configures a comb

filter for Y/C separation in recording an image and

elimination of crosstalk in playing back.

Features

• Single power supply 5V

• Low power consumption 225mW (Typ.)

• Built-in peripheral circuits

• Completely adjustment free

• Built-in quadruple progression PLL circuit

• For NTSC signals

CXL1501M

30 pin SOP (Plastic)

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD 6V

•Operating temperature Topr –10 to +60 °C

• Storage temperature Tstg –55 to +150 °C

• Allowable power dissipation PD 500 mW

Functions

• 1H comb filter output

• Dropout compensation (D.O.C) output

• Delay time matching through output (THR)

• PLL circuit (quadruple progression)

• Clock driver

• Autobias circuit

• Sync tip clamp circuit

• Sample and hold circuit

Structure

CMOS-CCD

Recommended Operating Conditions (Ta = 25°C)

Supply voltage VDD 5 ± 5% V

Recommended Clock Conditions (Ta = 25°C)

• Input clock amplitude VCLK 0.4 to 1.0 Vp-p

(0.5Vp-p Typ.)

• Clock frequency fCLK 3.579545 MHz

• Input clock waveform sine wave

Input Signal Amplitude

VSIG 571 mVp-p

(Max.)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E71050-PS

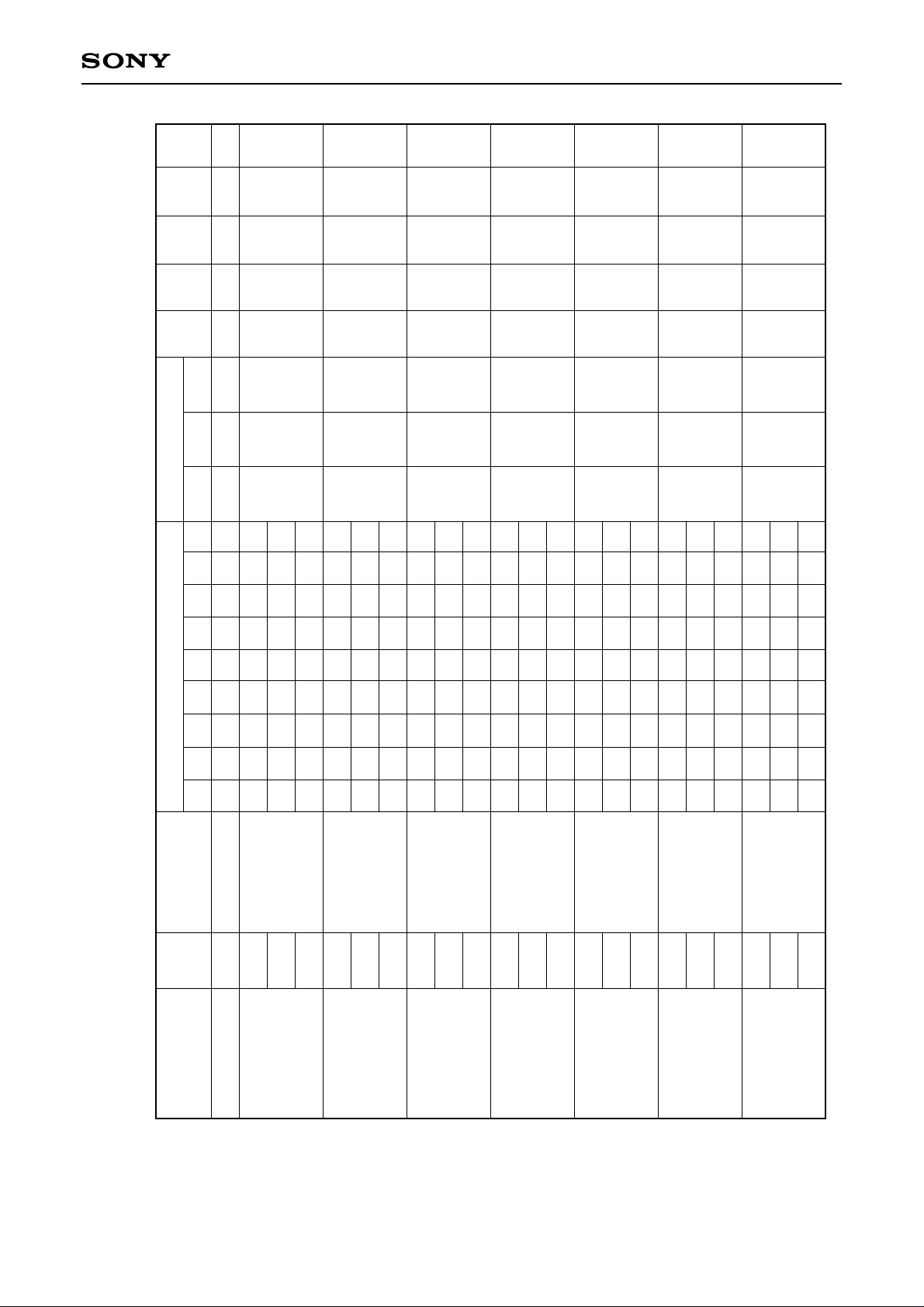

CXL1501M

V

SS

16

V

SS

17

TH

18

DD

V

19

ADJY

20

NC

21

VCO OUT

22

NC

23

V

SS

24

CLK

25

Phase

comparator

Bias circuit

φ1

φ2

(A)

(B)

Bias circuit

Output circuit, S/H circuit

D

Output circuit, S/H circuit

D

14 15

SS

13

12

11

Output circuit, S/H circuit

10

9

SS

8

IH + D

DD

7

6

Y-YD

VGGB

V

YD

VGGA

ABP

NC

V

V

NC

V

DD

2627

Clock driver

PC OUT

VCO IN

SS

V

CCD1

28

29

30

VCO 1/4 divider

Block Diagram and Pin Configuration (Top View)

Autobias

circuit (N)

– 2 –

Autobias

circuit (P)

CCD3

5

ABN

4

ADJC

3

CCD2

2

V

SS

1

Pin Description

CXL1501M

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Symbol

VSS

CCD2

ADJC

ABN

CCD3

NC

VDD

VSS

NC

ABP

VGGA

YD

VSS

VGGB

Y-YD

VSS

I/O

GND

—

Signal input 2 (Reverse phase signal)

I

Forward phase CCD bias DC output

O

Reverse phase autobias DC output

O

Signal input 3 (Forward phase signal)

I

Description

—

5V power supply (For clock driver)

—

GND

—

—

Forward phase autobias DC output

O

Gate bias (A) DC output

O

D.O.C signal output (Reverse phase signal)

O

GND

—

Gate bias (B) DC output

O

Comb filter signal output

O

GND

—

Impedance (Ω)

> 100k (at no clamp)

600 to 2k

2k to 20k

> 100k (at no clamp)

2k to 20k

2k to 10k

40 to 500

2k to 10k

40 to 500

17

18

19

20

21

22

23

24

25

26

27

28

29

30

VSS

TH

VDD

ADJY

NC

VCO OUT

NC

VSS

CLK

VDD

PC OUT

VCO IN

VSS

CCD1

GND

—

THR signal output (Forward phase signal)

O

5V power supply (For analog)

—

Reverse phase CCD bias DC output

O

—

VCO output

O

—

GND

—

Clock input

I

5V power supply (For digital)

—

Phase comparator output

O

VCO input

I

GND

—

Signal input 1 (Reverse phase signal)

I

40 to 500

600 to 2k

4k to 40k

2k to 5k

> 100k

> 100k (at no clamp)

– 3 –

CXL1501M

3

∗

∗4

∗5

∗6

∗7

∗7

∗8

∗9

mA

Unit Note

55

Max.

45

Typ.

35

Min.

(V)

2

∗

See the Electrical Characteristics Test Circuit.

—

BIAS3

V

—

dB

–1.0

–3.0

–5.0

—

—

VBIAS2

—

BIAS1

Bias conditions

V

DD = 5V, fCLK = 3.579545MHz, VCLK = 500mVp-p sine wave)

(Ta = 25°C, V

9

—

8

—

7

a

a

6

—

b

b

b

a

a

a

c

b

a

a

a

a

dB

–2.5

–4.5

–6.5

VID

+0.25

VIC

–0.25

VIT

–0.25

b

b

a

b

b

b

b

b

dB

–0.5

–1.5

–2.5

VID

+0.25

VIC

–0.25

VIT

–0.25

b

b

b

b

c

a

b

b

b

b

c

b

b

b

b

b

%

a

a

b

b

mVp-p

350

—

—

VID

+0.5

VIC

VIT

a

b

b

b

a

c

b

b

degree

7

3

0

—

—

—

c

c

c

a

a

a

c

b

a

a

a

a

7

3

0

—

—

—

c

c

c

a

a

a

c

b

a

a

a

a

dB

–52

–56

—

—

—

—

d

d

d

a

a

a

c

b

a

a

a

a

a

5

4

a

a

a

SW conditions

a

3

2

1

1

∗

a

a

a

a

a

—

Test conditions

DD

GLT

I

Symbol

Item

Electrical Characteristics

Supply current

a

a

b

a

a

a

a

a

a

a

a

a

a

196.678kHz

500mVp-p

GLC

Low frequency

c

a

sine wave

GLD

gain

GHT

b

b

b

a

a

a

a

a

a

a

a

a

c

3.579545MHz

150mVp-p

GHC

High frequency

gain

c

c

←→

b

sine wave

3.579545MHz

196.678kHz

←→

GHDfTfc

Frequency

b

b

a

a

a

a

a

a

c

c

←→

←→

b

b

150mVp-p

sine wave

fD

response

a

a

a

a

a

a

a

a

f

f

7

∗

5-staircase

wave

DGT

DGC

Differential

gain

a

a

a

a

f

DGD

a

a

a

a

a

a

a

a

f

f

∗7

5-staircase

wave

DPT

DPC

Differential

phase

a

a

a

a

f

DPD

b

b

b

b

b

b

b

b

b

b

b

b

—

—

—

No-signal input

VPT

VPC

VPD

S/H pulse

coupling

a

a

a

b

b

b

b

b

b

b

b

b

—

—

—

∗9

No-signal input

SNT

SNC

S/N ratio

SND

– 4 –

Loading...

Loading...