Sony CXG1082EN Datasheet

CXG1082EN

Receive Dual Low Noise Amplifier/Mixer

Description

The CXG1082EN is a receive dual low noise amplifier/

mixer MMIC. This IC is designed using the Sony’s

GaAs J-FET process.

Features

• High conversion gain:Gp = 17dB (LNA Typ.)

Gc = 11 to 12dB (MIX Typ.)

• Low noise figure: NF = 1.5dB (LNA Typ.)

NF = 4.2dB (MIX Typ.)

• Single 3V power supply operation

• Low LO input power operation PLO = –15dBm

• Single CTL pin achieved by the built-in inverter

circuit

• 16-pin VSON package

Applications

800MHz Japan digital cellular telephones (PDC)

Structure

GaAs J-FET MMIC

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD 4.5 V

• Input power PIN +13 dBm

• Current consumption IDD 15 mA

• Operating temperature Topr –35 to +85 °C

• Storage temperature Tstg –65 to +150 °C

Recommended Operating Voltages

• Supply voltage VDD 2.7 to 3.3 V

• Control voltage VCTL (H) 2.4 to 3.3 V

VCTL (L) 0 to 0.3 V

– 1 –

E00408-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

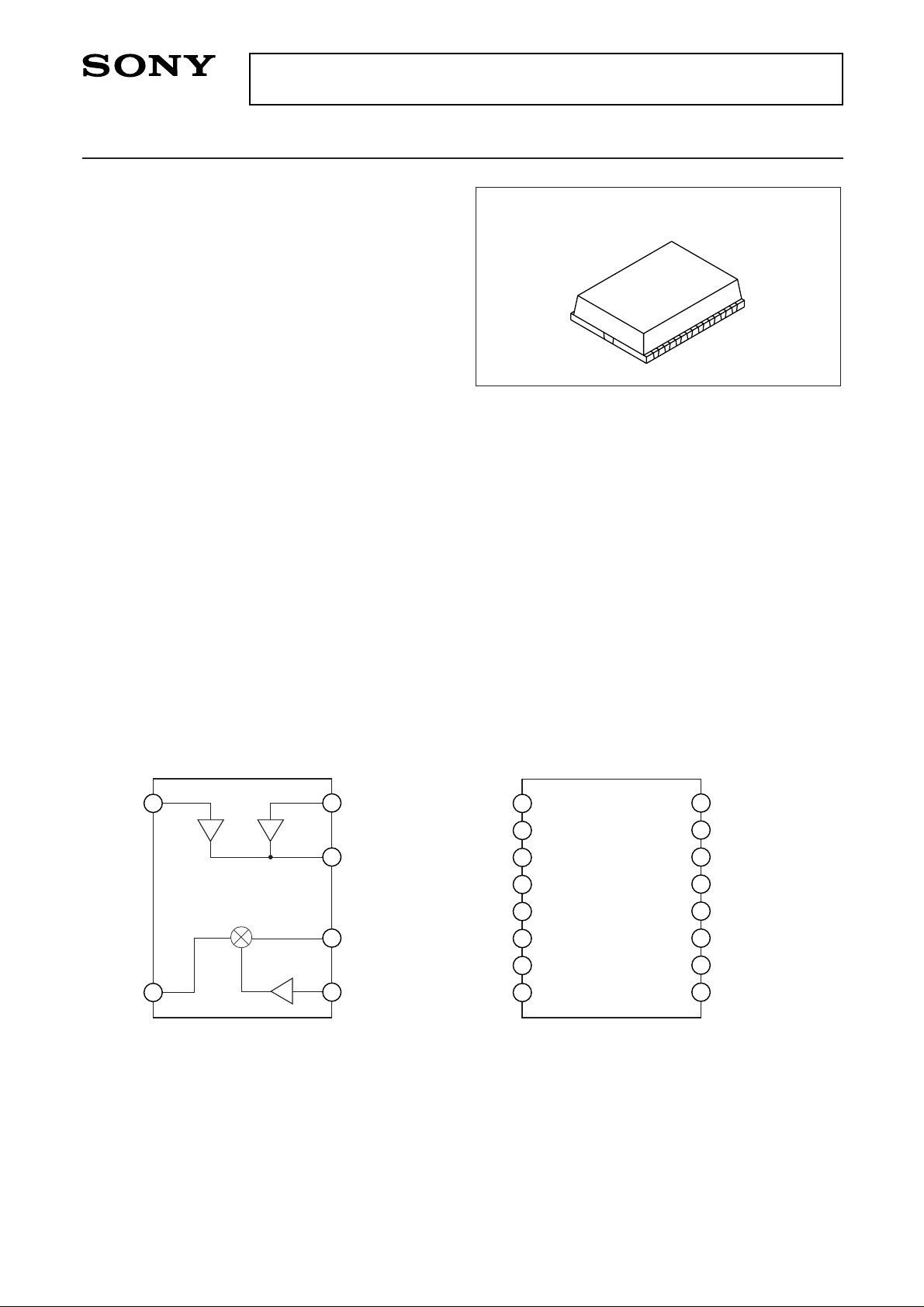

Block Diagram

IFOUT

LNA RFIN1

LO IN

LNA RF

IN2

LNA RF

OUT

MIX RFIN

1

3

6

8

9

16

Pin Configuration

IFOUT/VDD3 (MIX)

LNA RF

IN1

CAP

GND

CTL

GND

GND

V

DD2 (LO AMP)

LO IN

LNA RF

IN2

CAP

GND

LNA RF

OUT/VDD1 (LNA)

OPT

MIX RF

IN

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

16 pin VSON (Plastic)

GaAs MMICs are ESD sensitive devices. Special handling precautions are required.

For the availability of this product, please contact the sales office.

– 2 –

CXG1082EN

Electrical Characteristics

Conditions: VDD = 3.0V, VCTL (H) = 3.0V, VCTL (L) = 0V, fRF1 = 870MHz, fRF2 = 820MHz, fLO = fRF – 130MHz,

PLO = –15dBm, Ta = 25°C, unless otherwise specified

Low Noise Amplifier Block

Mixer Block

The values shown above are the specified values on the Sony’s recommended evaluation board. (When no

option pin resistor is added.)

∗1

Conversion from the IM3 suppression ratio for two-wave input: PRF = –30dBm (low noise amplifier block)/

–25dBm (mixer block) at fRFoffset = 100kHz.

Item

Current

consumption

Control current

Power gain

Noise figure

Input IP3

Isolation

Symbol

IDD

ICTL

Gp

NF

IIP3

Iso

Path

—

—

RFIN1 → RFOUT

RFIN2 → RFOUT

RFIN1 → RFOUT

RFIN2 → RFOUT

RFIN1 → RFOUT

RFIN2 → RFOUT

RFOUT → RFIN1

RFOUT → RFIN2

VCTL

H

L

H

L

H

L

H

L

H

L

H

L

H

L

Min. Typ. Max. Unit

—

—

—

–1

15

—

—

15

—

—

–13

–13

17

18

1.9

1.9

55

0

17

–20

–25

17

1.5

1.5

–9

–9

22

23

2.5

2.5

80

—

19

–15

–20

19

2.0

2.0

—

—

—

—

mA

µA

dB

dB

dBm

dBm

Measurement

condition

When no

signal

When a

small signal

∗1

When a

small signal

RF frequency

—

—

—

—

fRF1

fRF2

fRF1

fRF2

fRF1

fRF2

fRF1

fRF2

Item

Current consumption

Power gain

Noise figure

Input IP3

LO to RF leak level

Symbol

IDD

Gc

NF

IIP3

Plk

Min. Typ. Max. Unit

—

10

9

—

—

–4.0

–3.5

—

—

4.5

12

11

4.2

4.2

–1.0

–0.5

–31

–31

6.0

14

13

6.0

6.0

—

—

–26

–26

mA

dB

dB

dBm

dBm

Measurement condition

When no signal

When a small signal

∗1

fLO = 740MHz

fLO = 690MHz

RF frequency

—

fRF1

fRF2

fRF1

fRF2

fRF1

fRF2

fRF1

fRF2

– 3 –

CXG1082EN

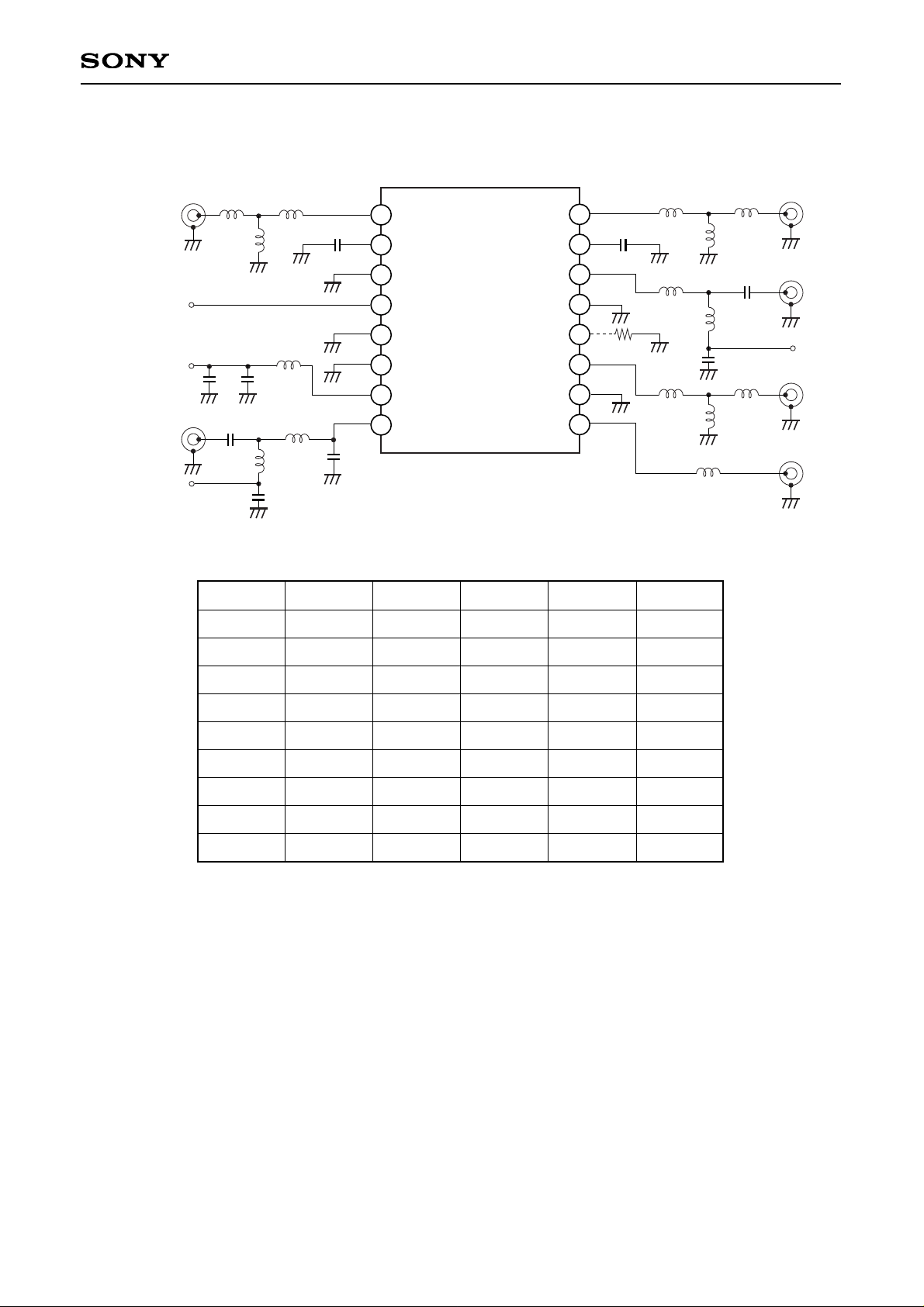

Recommended Evaluation Circuit

C9

L8 L9

L7

L10

C4

IFOUT

VDD3 (MIX)

CTL

V

DD2 (LO AMP)

LO

IN

MIX RFIN

L3

50Ω

L1

L2

R1

C2

C6

C3

C5

C1

LNA RFIN1

50Ω

50Ω

50Ω

L13 L14

L15

LNA RFIN2

50Ω

L11

L12

LNA RFOUT

VDD1 (LNA)

50Ω

L4

L6

L5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

C8

C7

L1

L2

L3

L4

L5

L6

L7

L8

L9

L10

150nH

120nH

33nH

18nH

6.8nH

27nH

33nH

27nH

5.6nH

12nH

L11

L12

L13

L14

L15

C1

C2

C3

C4

C5

18nH

10nH

22nH

5.6nH

22nH

6pF

1000pF

1000pF

100pF

1000pF

C6

C7

C8

C9

R1

18pF

1000pF

100pF

56pF

Loading...

Loading...