Sony CXD2720Q Datasheet

CXD2720Q

Single-Chip Digital Signal Processor for Karaoke

Description

The CXD2720Q is a digital signal processor LSI for

Karaoke, suitable for use in LD/CD/CD-G/video CD

and the like.

A large capacity DRAM and AD/DA converters are

built in, and Karaoke functions such as key control,

microphone echo and voice canceling are contained

on a single chip.

100 pin QFP (Plastic)

Features

• 3-channel 1-bit AD converter and decimation filter

S/N ratio: 88 dB

THD + N: 0.016%

Filter pass band ripple: less than ±0.5dB

Filter stop band attenuation: less than –41dB

(all characteristics are typical values)

• 2-channel 1-bit DA converter and oversampling

filter

S/N ratio: 98dB

THD + N: 0.006%

Filter pass band ripple: less than ±0.2dB

Filter stop band attenuation: less than –41dB

(all characteristics are typical values)

• In addition to analog input/output, 2-channel input/

2-channel output of digital input/output are provided.

The interface also supports a variety of formats.

• 128K-bit DRAM for key control and microphone

echo processing

Functions

• Key controller pitch setting can be varied to a

maximum of ±1 octave with a precision of 14 bits

• Microphone echo delay time can be varied to a

maximum of 185ms (when Fs = 44.1kHz)

• Voice canceller supports settings other than center

by the panpot volume

• Voice parametric equalizer

• Voice pitch shifter

• Mixing function to support sound multiplexing

software

• Digital de-emphasis function

Structure

Silicon gate CMOS

Applications

Equipment having Karaoke function, such as

LD/CD, compact music center, video games, etc.

Absolute Maximum Ratings

(Ta = 25°C, VSS = 0V)

• Supply voltage VDD VSS – 0.5 to +7.0 V

• Input voltage VI VSS – 0.5 to VDD + 0.5 V

• Output voltage VO VSS – 0.5 to VDD + 0.5 V

• Operating temperature

Topr –20 to +75 °C

• Storage temperature Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage VDD 4.5 to 5.5 (5.0 typ.) V

• Operating temperature

Ta –20 to +75 °C

Input/Output Capacitance

• Input capacitance CIN 9 (max.) pF

• Output capacitance COUT 11 (max.) pF

• Input/output capacitance CI/O 11(max.) pF

∗

Measurement conditions: VDD = VI = 0V, F = 1MHz

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E96426-ST

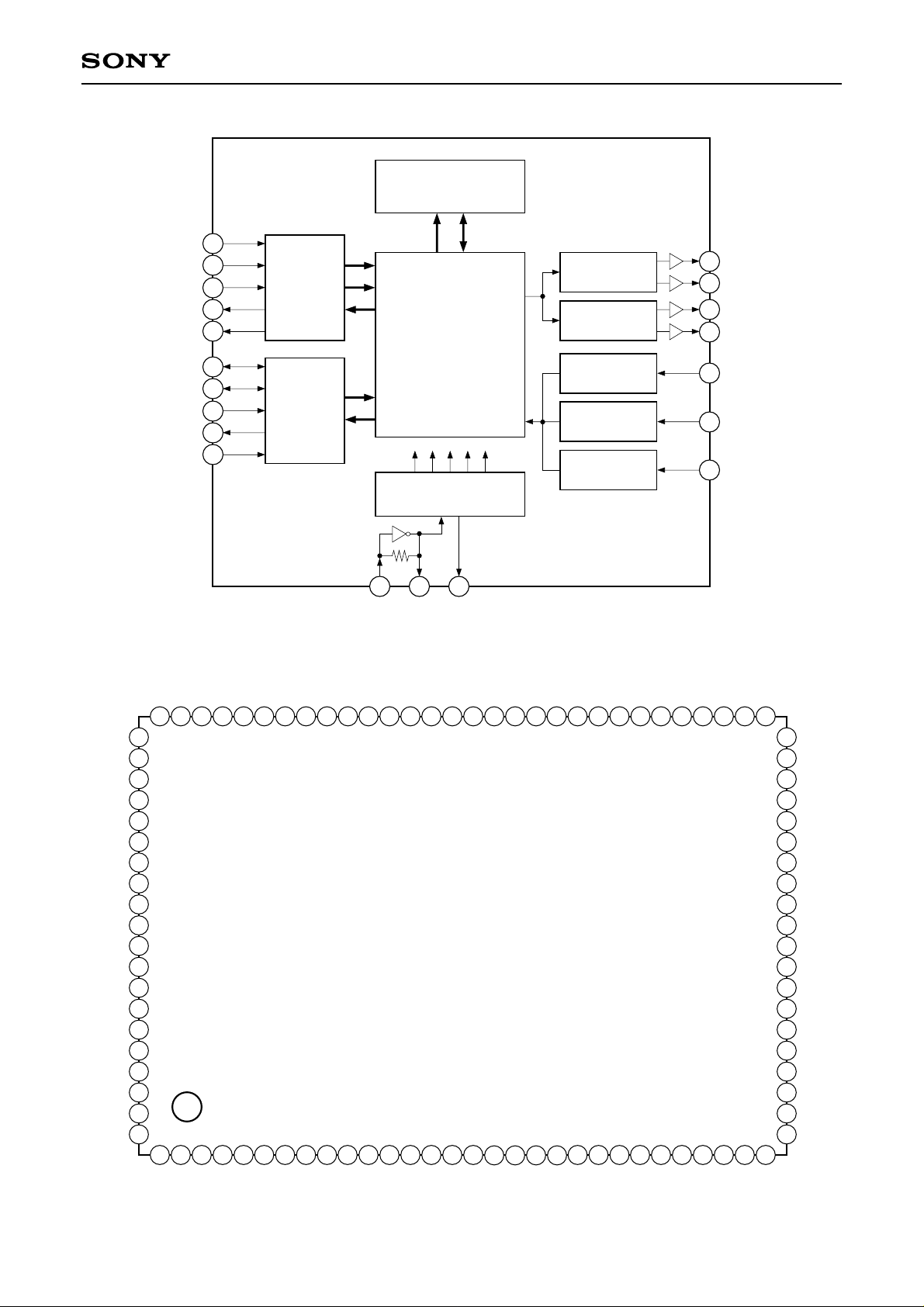

Block Diagram

RVDT

SCK

XLAT

REDY

TRDT

LRCK

BCK

SO

XWO

CXD2720Q

128K bit DELAY RAM

3

AO1P

4

5

6

7

MICRO

COMPUTER

I/F

DAC1

DAC2

25

26

39

40

AO1N

AO2N

AO2P

DSP

88

87

86

SI

12

SERIAL

DATA

I/F

ADC1

ADC2

29

36

AIN1

AIN2

8

ADC3

22

AIN3

CLOCK GENERATOR

/TIMING CIRCUIT

Pin Configuration

6

SS

NC

V

80

78

79

81

X768

82

BFOT

83

INVI

84

NC

85

NC

86

SI

87

BCK

88

LRCK

89

XMST

90

SS7

V

91

NC

92

NC

93

NC

94

NC

95

NC

96

NC

NC

97

98

NC

99

DD3

V

100

D0

AV

1

2

3

0

0

S

SS

V

AV

NC

77

4

RVDT

NC

76

SCK

NC

5

XLAT

75

6

NC

74

7

REDY

NC

73

8

TRDT

NC

72

9

XWO

33

XTLI XTLO BFOT

2

DD

V

NC

NC

69

71

70

12

10

11

0

1

SS

DD

V

V

XRST

5

SS

V

SO

68

13

32

NC

67

14

XS24

82

NC

66

15

TST0

NC

65

16

TST1

NC

64

17

TST2

NC

63

18

TST3

NC

62

19

TST4

NC

61

20

TST5

NC

2

SS

V

60

21

NC

3

S

AV

59

22

NC

58

23

AIN3

NC

3

D

AV

57

24

NC

4

D

AV

56

25

NC

55

26 27

AO1P

NC

54

AO1N

NC

4

S

AV

53

28

4

SS

V

1

S

AV

52

29

NC

51

30

AIN1

NC

1

D

AV

48

47

45

44

33

50

49

46

43

42

41

40

39

38

37

36

35

34

32

31

NC

NC

NC

NC

NC

NC

NC

DD1

V

SS3

V

S5

AV

AO2P

AO2N

D5

AV

D2

AV

AIN2

S2

AV

SS

XV

XTLI

XTLO

DD

XV

– 2 –

Pin Description

CXD2720Q

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Symbol I/O Description

AVS0

VSS0

RVDT

SCK

XLAT

REDY

TRDT

XWO

XRST

VSS1

VDD0

SO

XS24

TST0

—

DRAM digital GND.

—

Digital GND.

I

Data input for microcomputer interface.

I

Shift clock input for microcomputer interface.

I

Latch input for microcomputer interface.

Transmission enabling signal output for microcomputer interface. Transmission

O

prohibited when Low.

O

Serial data output for microcomputer interface.

I

Window open input for synchronization. Normally High.

I

System reset input. Resets when Low.

—

Digital GND.

—

Digital power supply.

O

1-sampling 2-channel serial data output.

I

Serial data 24-/32-bit slot selection. 24-bit slot when Low. (valid for slave mode)

I

Test pin. Normally set Low.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

TST1

TST2

TST3

TST4

TST5

VSS2

AVS3

AIN3

AVD3

AVD4

AO1P

AO1N

AVS4

AVS1

AIN1

AVD1

XVDD

I

Test pin. Normally set Low.

I

Test pin. Normally set Low.

I

Test pin. Normally set Low.

I

Test pin. Normally set Low.

I

Test pin. Normally set Low.

—

Digital GND.

—

CH3 AD converter GND.

I

CH3 AD converter analog input (for microphone input).

—

CH3 AD converter power supply.

—

CH1 DA converter power supply.

O

CH1 DA converter analog positive phase output.

O

CH1 DA converter analog reversed phase output.

—

CH1 DA converter GND.

—

CH1 AD converter GND.

I

CH1 AD converter analog input.

—

CH1 AD converter power supply.

—

Digital power supply for master clock.

32

33

34

35

XTLO

XTLI

XVSS

AVS2

O

Crystal oscillator circuit output.

I

Crystal oscillator circuit input.

—

Digital GND for master clock.

—

CH2 AD converter GND.

– 3 –

CXD2720Q

Pin

No.

36

37

38

39

40

41

42

43

44 to 52

53

54 t o 68

69

70

71 t o 79

80

Symbol I/O Description

AIN2

AVD2

AVD5

AO2N

AO2P

AVS5

VSS3

VDD1

NC

VSS4

NC

VSS5

VDD2

NC

VSS6

I

CH2 AD converter analog input.

—

CH2 AD converter power supply.

—

CH2 DA converter power supply.

O

CH2 DA converter analog reversed phase output.

O

CH2 DA converter analog positive phase output.

—

CH2 DA converter GND.

—

Digital GND.

—

Digital power supply.

Normally open.

—

Digital GND.

Normally open.

—

Digital GND.

—

Digital power supply.

Normally open.

—

Digital GND.

81

82

83

84

85

86

87

88

89

90

91 t o 98

99

100

X768

BFOT

INVI

NC

NC

SI

BCK

LRCK

XMST

VSS7

NC

VDD3

AVD0

I

Test input pin. Normally set Low.

O

Clock, frequency-divider output (384fs).

I

Test pin. Normally set Low.

Normally open.

Normally open.

I

1-sampling 2-channel serial data input.

I/O

Serial bit transmission clock for serial input/output data SI and SO.

I/O

Sampling frequency clock for serial input/output data SI and SO.

I

BCK, LRCK master/slave mode switching input. Master mode when Low.

—

Digital GND.

Normally open.

—

Digital power supply.

—

Digital power supply for DRAM.

– 4 –

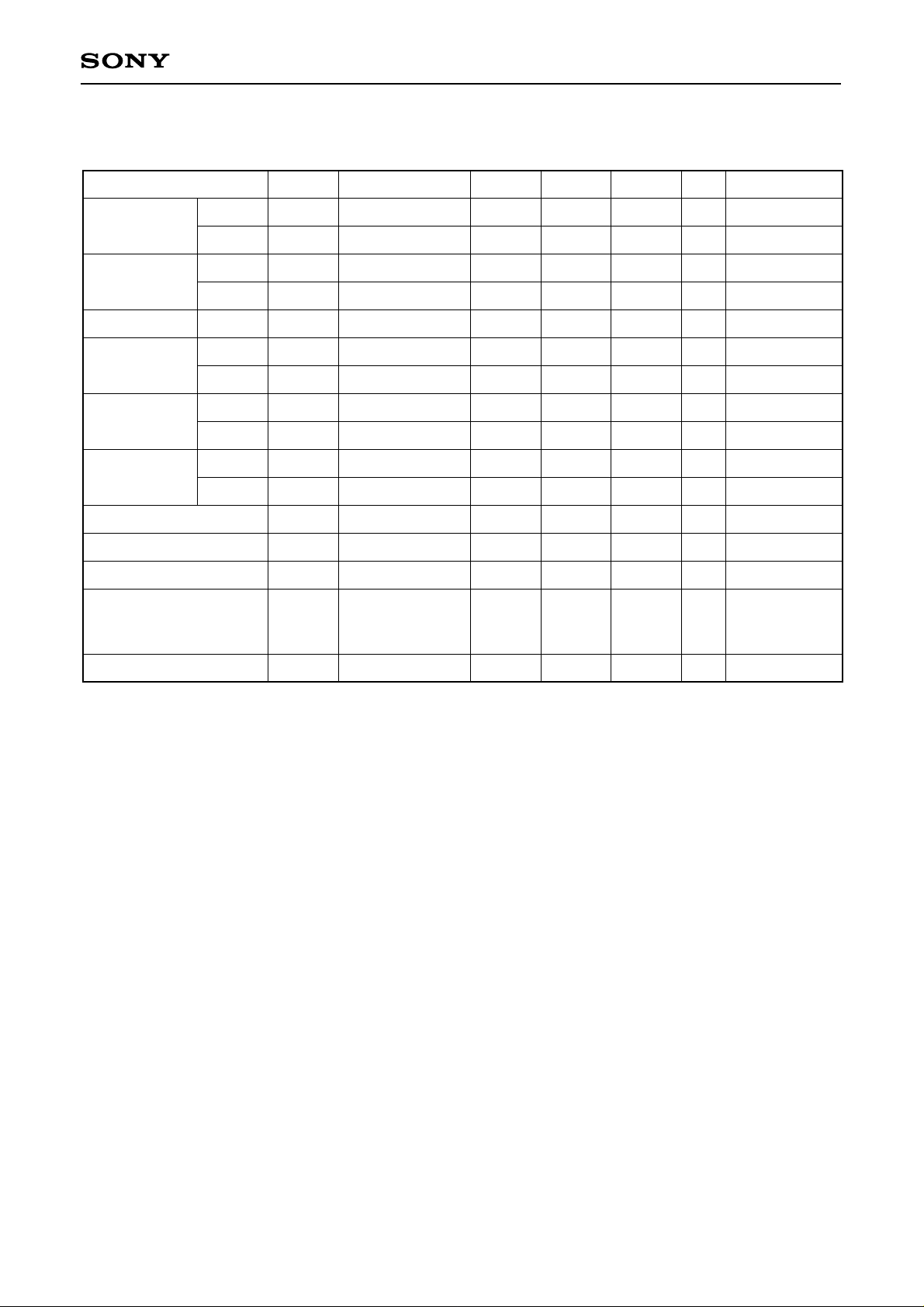

DC Characteristics

(AVD0 to 5 = XVDD = VDD0 to 3 = 5V ± 10%, AVS0 to 5 = XVSS = VSS0 to 7 = 0V, Ta = –20 to +75°C)

Item Symbol Conditions Min. Typ. Max. Unit Applicable pins

High level

Input voltage (1)

Low level

High level

Input voltage (2)

Low level

Input voltage (3)

Output voltage

(1)

Output voltage

(2)

Output voltage

(3)

High level

Low level

High level

Low level

High level

Low level

Input leak current (1)

Input leak current (2)

Output leak current

VIH

VIL

VIH

VIL

VIN

VOH

VOL

VOH

VOL

VOH

VOL

II

II

IOZ

Analog input

IOH = –2.0mA

IOL = 4.0mA

IOH = –6.0mA

IOL = 4.0mA

IOH = –12.0mA

IOL = 12.0mA

VIH = VDD, VSS

VIH = VDD, VSS

VIH = VDD, VSS

0.7VDD

0.8VDD

VSS

VDD – 0.8

VDD – 0.8

VDD/2

–10

–40

–40

0.3VDD

0.2VDD

VDD

0.4

0.4

VDD/2

10

40

40

V

V

V

V

V

V

V

V

V

V

V

µA

µA

µA

CXD2720Q

∗1, ∗4, ∗5

∗1, ∗4, ∗5

∗3

∗3

∗2

∗6, ∗7, ∗8

∗6, ∗7, ∗8, ∗9

∗10

∗10

∗11

∗11

∗1, ∗3, ∗5

∗4

∗8, ∗9

Feedback resistance

Current consumption

∗1

RVDT, SCK, XLAT, XWO, XRST, XS24, TST0 to TST5, X768, SI, XMST

∗2

AIN1, AIN2, AIN3

∗3

INVI

∗4

During input to bidirectional pins BCK, LRCK

∗5

XTLI

∗6

During output from bidirectional pins BCK, LRCK

∗7

SO, BFOT

∗8

TRDT

∗9

REDY

∗10

AO1P, AO1N, AO2N, AO2P

∗11

XTLO

RFB

IDD

fs = 44.1kHz

250k

1M

79

2.5M

90

Ω

mA

Resistance

between

∗5

and ∗11.

– 5 –

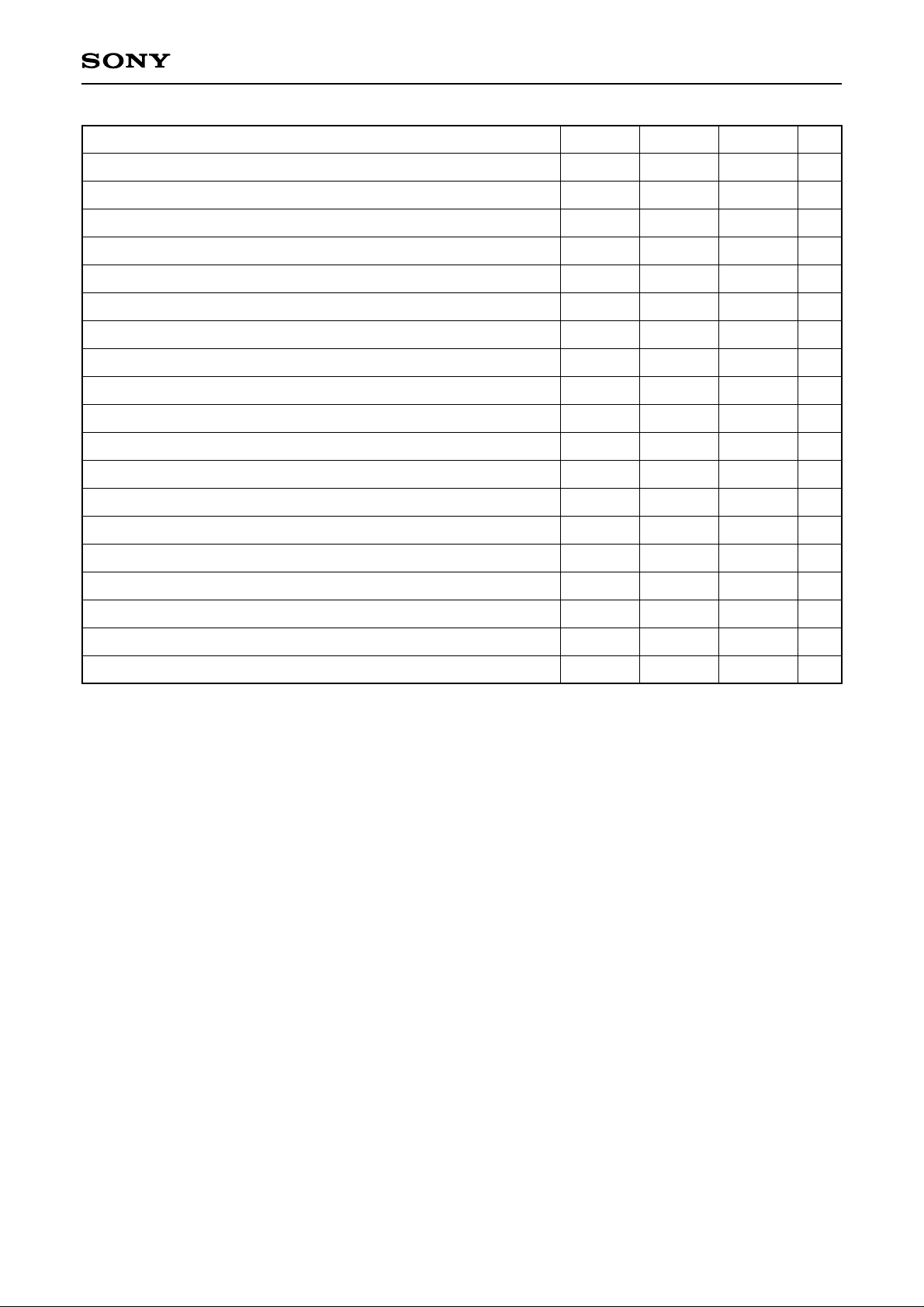

AC Characteristics

(AVD0 to 5 = XVDD = VDD0 to 3 = 5V±10%, AVS0 to 5 = XVSS = VSS0 to 7 = 0V, Ta = –20 to +75°C)

Serial Audio Interface Timing

[Slave mode]

CXD2720Q

BCK

SI

SO

LRCK

[Master mode]

BCK

LRCK

SO

Item

tDSSO

0.7VDD

0.3VDD

tHSItSSI

DD

0.7V

0.3VDD

tHLR

tDLR

tDMSO

tSLR

0.7VDD

0.3VDD

Symbol Conditions Min. Max. Unit

SI setup time

SI hold time

SO delay time

LRCK setup time

LRCK hold time

LRCK delay time

SO delay time

tSSI

tHSI

tDSSO

tSLR

tHLR

tDLR

tDMSO

Slave mode

Slave mode

Slave mode, CL = 60pF

Slave mode

Slave mode

Master mode, CL = 120pF

Master mode, CL = 60pF

20

40

20

40

50

50

100

ns

ns

ns

ns

ns

ns

ns

– 6 –

Microcomputer Interface Timing

[Write]

• Transmission timing for address section, transmission mode section, data section LSB

CXD2720Q

RVDT

SCK

Address LSB Data LSB Data MSB

tSWL

tSWH tDS tDH

Mode MSB

0.7VDD

0.3VDD

0.7VDD

0.3VDD

tLSDtSLP

XLAT

tLWH

tLWL

0.7VDD

0.3VDD

REDY

• Transmission timing from data section MSB to address section and transmission mode section

RVDT

SCK

XLAT

REDY

Data MSB Address LSB Mode MSB

tSS

tSLD

tSBD tLDR

tBSP

0.7VDD

0.3VDD

0.7VDD

0.3VDD

tRLP

[Read]

0.7VDD

0.3VDD

• Transmission timing for address section and transmission mode section is the same as for write.

RVDT

SCK

XLAT

REDY

TRDT

Mode MSB

tSLP

tLWL tLBD

tRSDP

tLDN tSDD

Data MSBData LSB

Address LSB

tSS

0.7VDD

0.3VDD

0.7VDD

0.3VDD

0.7VDD

0.3VDD

– 7 –

CXD2720Q

Item

RVDT setup time relative to SCK rise

RVDT data hold time from SCK rise

SCK Low level width

SCK High level width

XLAT Low level width

XLAT High level width

SCK rise preceding time relative to XLAT rise

SCK rise wait time relative to XLAT rise

Delay time to REDY fall relative to XLAT rise.

Delay time to REDY fall relative to SCK rise

REDY fall preceding time relative to SCK rise

REDY rise preceding time relative to XLAT rise

REDY rise preceding time relative to SCK fall

XLAT fall wait time relative to SCK rise

XLAT fall delay time relative to REDY fall

Delay time from XLAT rise until TRDT data becomes active

Delay time from SCK rise until TRDT data becomes high-impedance

Delay time from SCK fall until TRDT data is verified

CK rise wait time for next transmission

Symbol Min.

tDS

tDH

tSWL

tSWH

tLWL

tLWH

1t + 20

1t + 20

1t + 20

1t + 20

1t + 20

tSLP

tLSD

3t + 20

tLBD

tSBD

tBSP

tRLP

tRSDP

tSLD

3t + 20

tLDR

tLDN

tSDF

tSDD

tSS

2t + 40

20

20

20

20

20

20

Max.

3t + 50

4t + 50

3t + 80

3t + 80

2t + 70

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Note 1) t is the cycle of 1/2 the clock frequency applied to the XTLI pin. (384fs)

Note 2) REDY and TRDT pins are the values for CL = 60pF.

– 8 –

CXD2720Q

Analog Characteristics (AVD0 to 5 = VDD0 to 3 = XVDD = 5.0V, AVS0 to 5 = VSS0 to 7 = XVSS = 0.0V, Ta = 25°C,

DSP: each function = OFF, gain = 1)

[1] ADC + DAC connection total characteristics

The measurement circuit in Figure 1-1 is used. Unless otherwise indicated, the measurement conditions are as

given below.

• Input signal ...1.0Vrms, 1kHz

• fs....................44.1kHz

• Rin.................0Ω

S/N ratio

Item

1.0Vrms, EIAJ (with “A” weighting filter)

1.0Vrms, EIAJ

Measurement conditions Min. Typ. Max.

80 88

0.016

0.03

THD + N

Dynamic range

Channel separation

Level difference between

channels

0.5Vrms, EIAJ

EIAJ

Only ADC characteristics using DAC1,

EIAJ

Only ADC characteristics using DAC1

Rin = 0Ω

0.012

92

108

0.05

1.26

Analog full-scale input level

Rin = 22kΩ

ADC input impedance

Analog current consumption

∗1

Analog input level which outputs digital full scale.

2.06

34.6

21

An optional analog input signal level Vin (Vrms) of 1.26Vrms or more can be set in digital full scale by the

measurement circuit external resistor Rin.

The calculation formula for external resistor Rin is:

Unit

dB

%

dB

dB

dB

Vrms

kΩ

mA

Rin = 27.5 × Vin – 34.6 [kΩ]......(1)

However, THD + N characteristics deteriorate for full-scale output as shown in Graph 1, so use of up to 80%

(when Rin = 0Ω, 0.8 × 1.26 (Vrms) = 1.0 (Vrms) →“analog full scale”) of the analog signal level is recommended

for digital full-scale output.

In this case, the Rin calculation formula is the same as formula (1), except that Vin becomes 1.25 × Vin.

Note that this change causes the output level after ADC + DAC to change.

Most of the above specifications are measurement values for analog full scale.

– 9 –

CXD2720Q

[2] DAC unit characteristics

Use the measurement circuit in Figure 1-2. Unless otherwise specified, the measurement conditions are as

follows.

• Input signal....0dB, 1kHz, 16 bit

• fs....................44.1kHz

Item

S/N ratio

THD + N

Dynamic range

Channel separation

Level difference between

channels

Output level

Measurement conditions Min. Typ. Max. Unit

EIAJ (with “A” weighting filter)

EIAJ (0dB)

EIAJ (–1dB)

EIAJ (–60dB)

EIAJ

EIAJ

EIAJ (Measure at OUT in Figure 1-2.)

1.00

98

0.006

0.004

98

120

0.05

2.0

dB

%

dB

dB

dB

Vrms

0.10

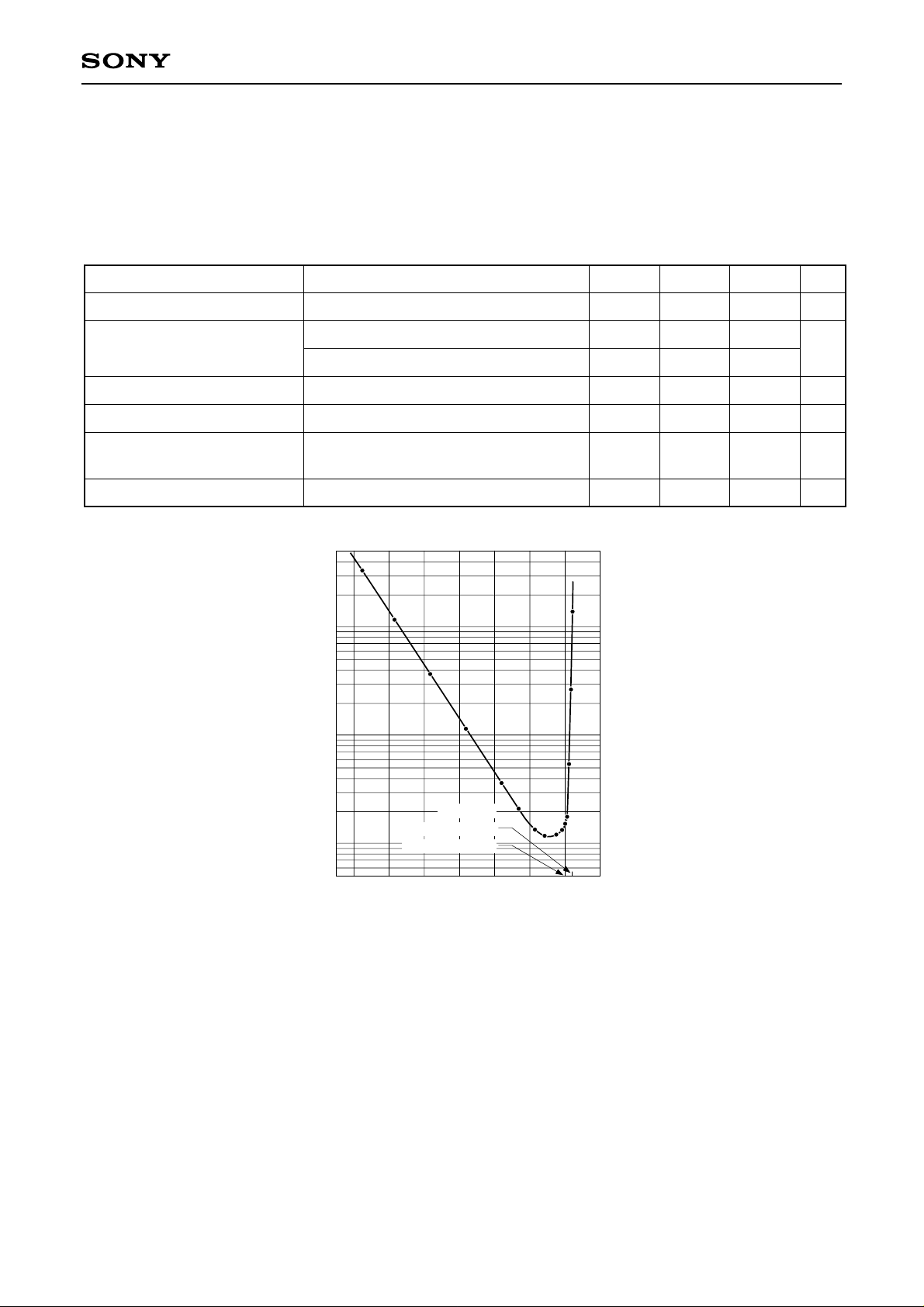

THD + N [%]

0.01

–60

(Rin = 0Ω)

Digital full scale

Analog full scale

–50 –40 –30 –20 –10 0 10

(1Vrms)

Analog input level [dBV]

Graph 1.

– 10 –

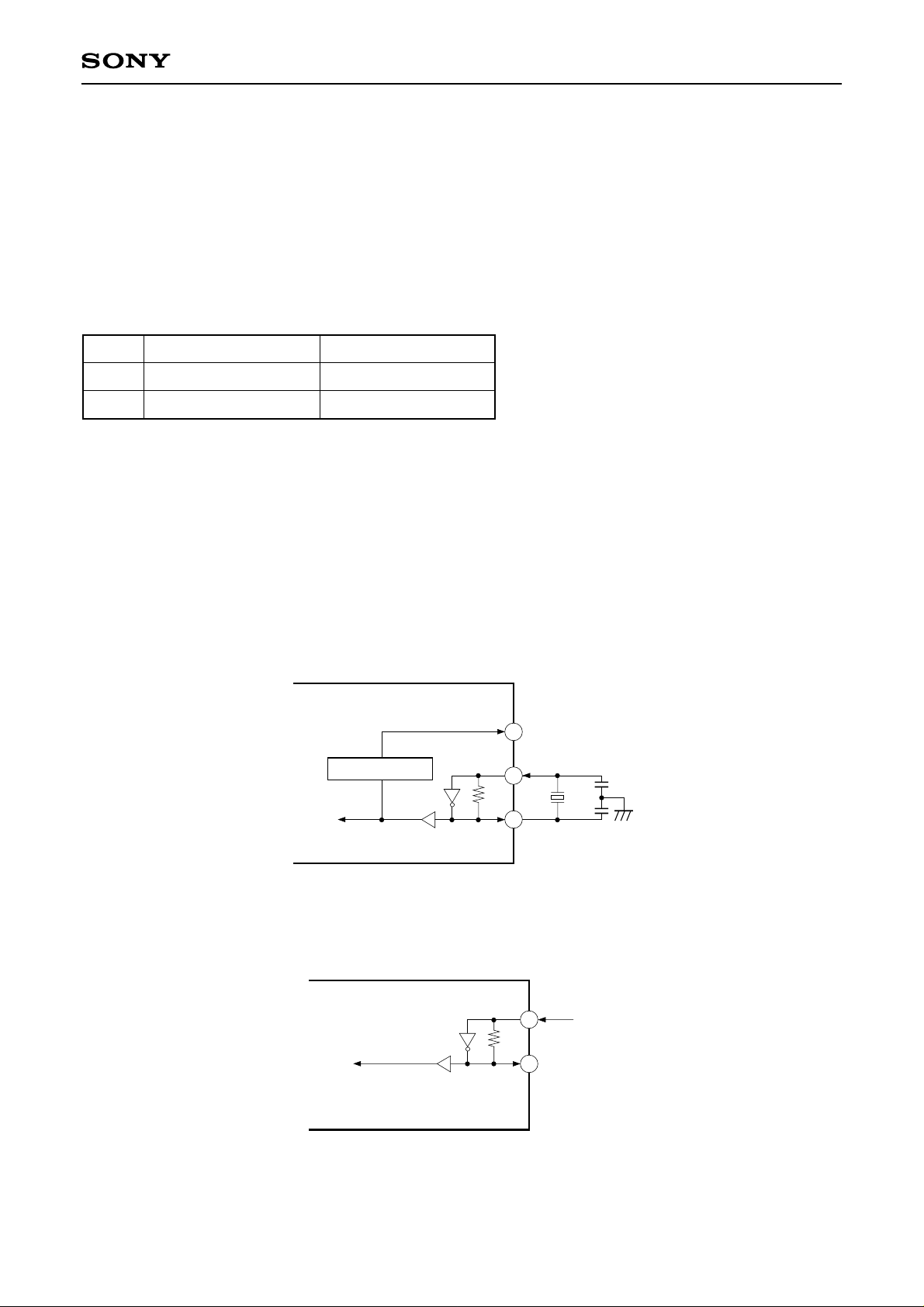

CXD2720Q

(Master mode)

CXD2720Q

150p

Vin

10µ

Rin

1M

AINx AOxN

22k12k

330p

AOxP

22k12k

39k

39k

150p

Figure 1-1. ADC + DAC Measurement Circuit Diagram

CXD2720Q

(Slave mode)

8200p

2.2k2.2k

820p

OUT

768fs

48fs

fs

DATA

(fs = 44.1kHz)

XTLI

BCK

LRCK AOxN

AOxP

SI

22k12k

330p

22k12k

39k

150p

150p

39k

8200p

Figure 1-2. DAC Measurement Circuit Diagram

2.2k2.2k

820p

OUT

– 11 –

CXD2720Q

Description of Functions

1. Master/Slave Modes

[Relevant pins] XMST, LRCK, BCK

When connecting multiple CXD2720Qs, or when using as a pair with a D/A converter such as the CXD2558M,

one of the CXD2720Q should be in master mode to supply LRCK and BCK.

The clock applied to LRCK and BCK in slave mode must be synchronized to either the crystal oscillator clock

of the XTLI and XTLO pins or the external clock input from the XTLI pin

XMST

H

L

Mode LRCK, BCK I/O

Slave mode

Master mode

Input

Output

Table 1-1. LRCK, BCK Mode Setting

2. Master Clock System

[Relevant pins] XTLI, XTLO, BFOT

768fs (fs = 44.1kHz) is assumed for the master clock system, and the connection is as shown below. (Please

inquire with regard to use at other than fs = 44.1kHz.)

(1) Master

O

384fs

BFOT

Frequency divider

768fs

I

O

XTLI

768fs

XTLO

(2) Slave

768fs

– 12 –

I

O

768fs

XTLI

OPEN

XTLO

Loading...

Loading...