Sony CXD2548R Datasheet

CXD2548R

For the availability of this product, please contact the sales office.

CD Digital Signal Processor with Built-in Digital Servo and DAC

Description

The CXD2548R is a digital signal processor LSI for

CD players. This LSI incorporates a digital servo,

digital filter, zero detection circuit, 1-bit DAC and

analog low-pass filter on a single chip.

Features

• All digital signal processing during playback is

performed with a single chip

• Highly integrated mounting possible due to a built-

in RAM

112 pin LQFP (Plastic)

Digital Signal Processor (DSP) Block

• Playback mode which supports CAV (Constant

Angular Velocity)

• Frame jitter free

• 0.5 × to 2.5 × continuous playback possible

• Allows relative rotational velocity readout

• Supports spindle external control

• Wide capture range playback mode

• Spindle rotational velocity following method

• Supports normal-speed, double-speed playback

• 16K RAM

• EFM data demodulation

• Enhanced EFM frame sync signal protection

• SEC strategy-based error correction

• Subcode demodulation and Sub Q data error

detection

• Digital spindle servo

• 16-bit traverse counter

• Asymmetry compensation circuit

• CPU interface on serial bus

• Error correction monitor signal, etc. output from a

new CPU interface

• Servo auto sequencer

• Digital audio interface outputs

• Digital level meter, peak meter

Digital Servo (DSSP) Block

• Microcomputer software-based flexible servo control

• Offset cancel function for servo error signal

• Auto gain control function for servo loop

• E:F balance, focus bias adjustment functions

• Surf jump function supporting micro two-axis

Digital Filter, DAC and Analog Low-Pass Filter Blocks

• Digital de-emphasis

• Digital attenuation

• Zero detection function

• 8Fs oversampling digital filter

• S/N: 100dB or more (master clock: 384Fs, typ.)

• THD + N: 0.007% or more (master clock: 384Fs,

typ.)

• Rejection band attenuation: –60dB or more

Applications

CD players

Structure

Silicon gate CMOS IC

Absolute Maximum Ratings

• Supply voltage VDD –0.3 to +7.0 V

• Input voltage VI –0.3 to +7.0 V

(VSS – 0.3V to VDD + 0.3)

• Output voltage VO –0.3 to +7.0 V

• Storage temperature Tstg –40 to +125 °C

• Supply voltage difference

VSS – AVSS –0.3 to +0.3 V

VDD – AVDD –0.3 to +0.3 V

Recommended Operating Conditions

• Supply voltage VDD

•

Operating temperature

Note) The VDD (Min.) for the CXD2548R varies

according to the playback speed selection.

Playback

speed

2 ×

1 ×

∗1

1 ×

∗1

When the internal operation of the CD-DSP side

is set to double-speed mode and the crystal

oscillation frequency is halved, normal-speed

playback results.

I/O Capacitance

• Input pin CI 12 (Max.) pF

• Output pin CO 12 (Max.) pF

Note) Measurement conditions VDD = VI = 0V

CD-DSP block DAC block

3.4V 4.5V

3.4V 3.4V

3.4V

Note)

Topr –20 to +75 °C

VDD (min.) [V]

–3.4 to +5.25 V

DSSP block

3.4V

3.4V

3.4V

fM = 1MHz

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E96404-PS

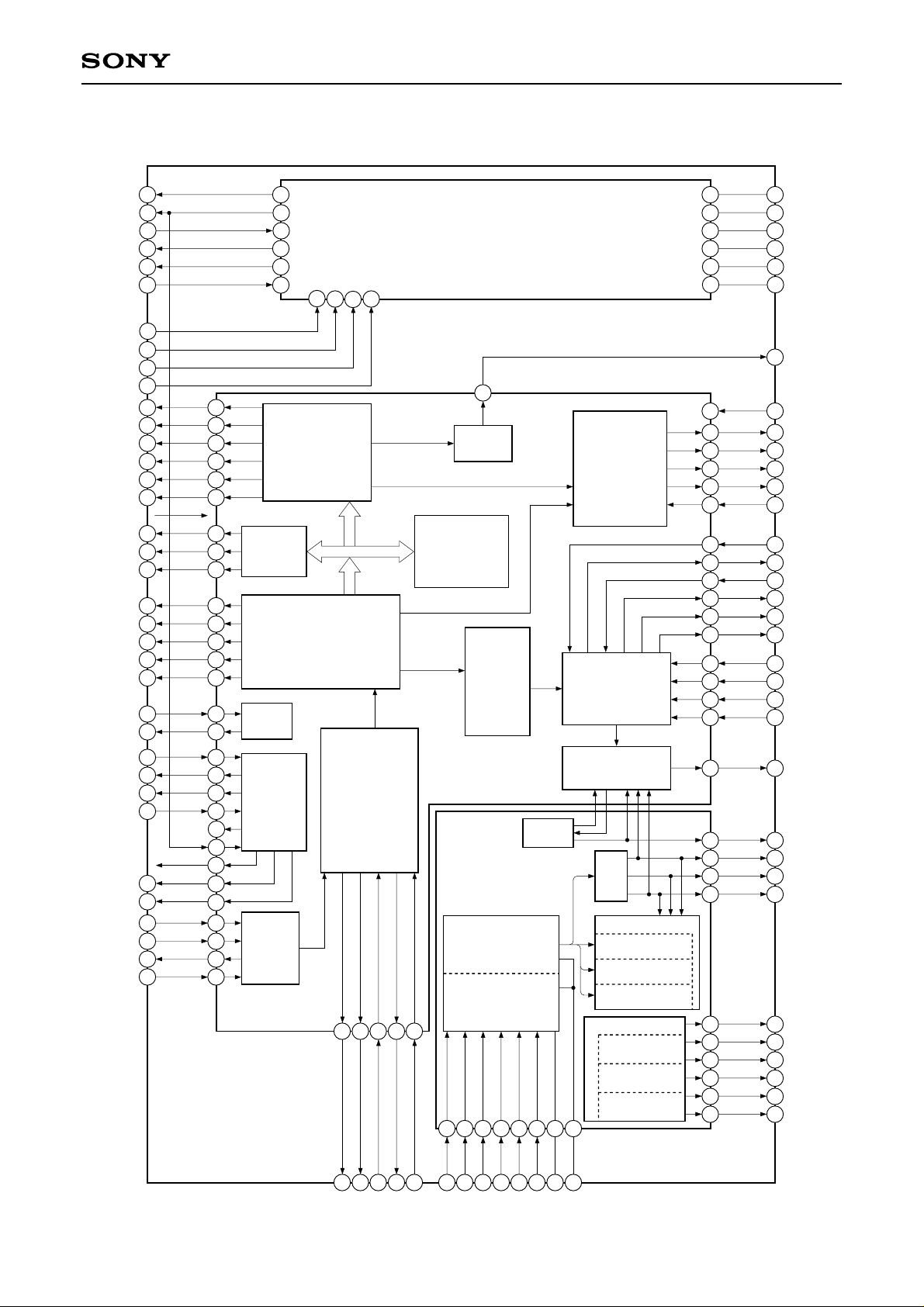

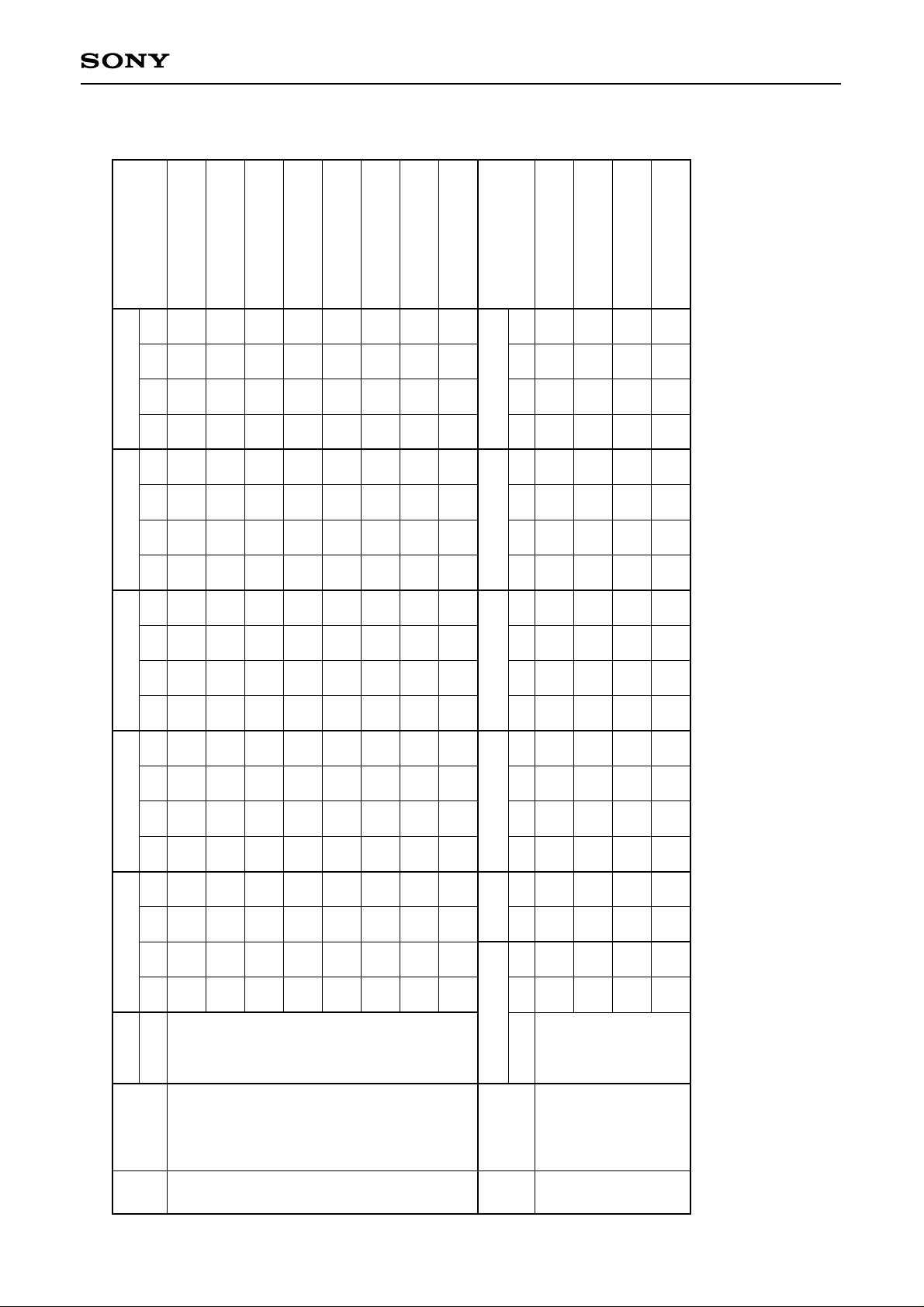

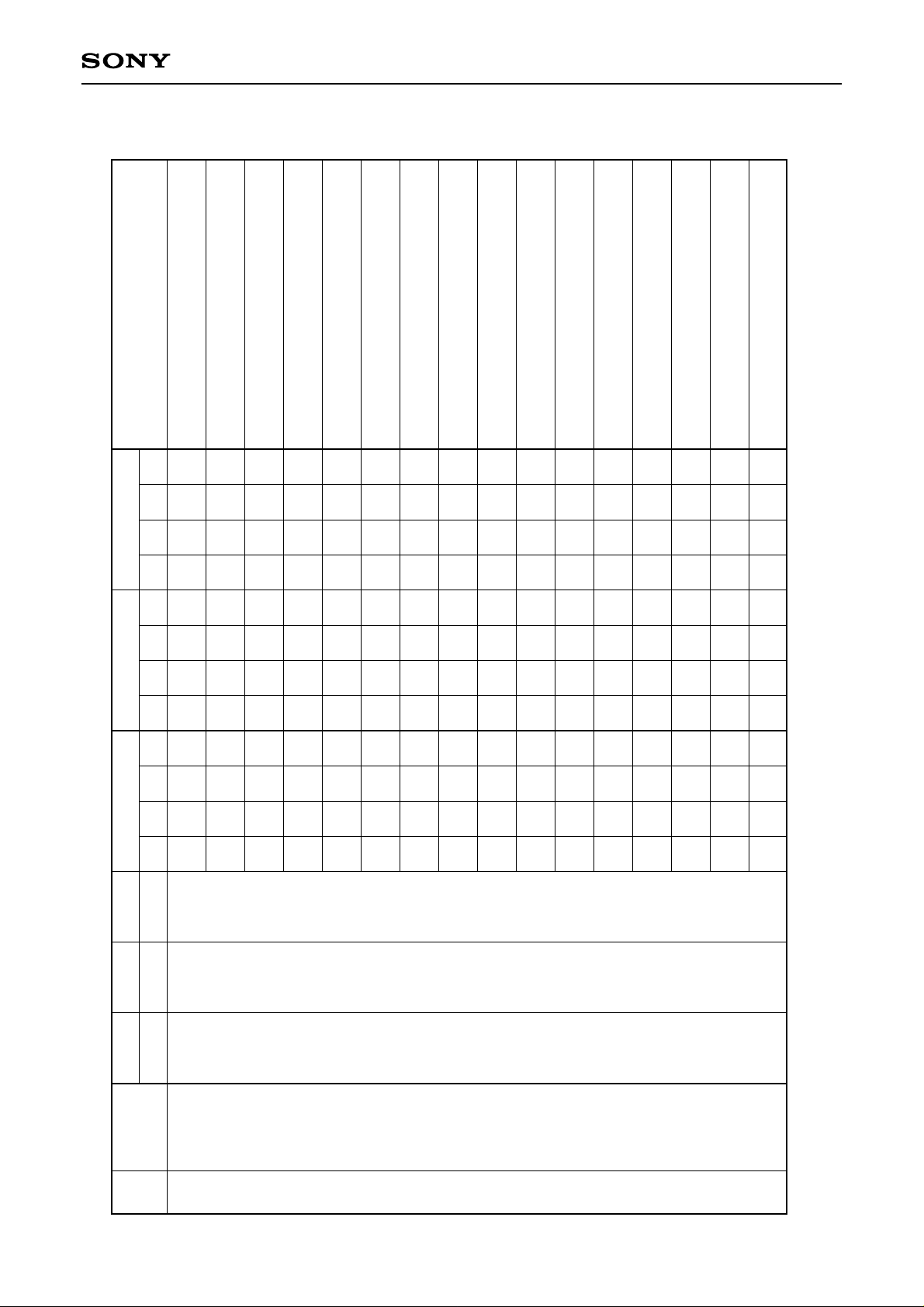

Block Diagram

CXD2548R

104

103

4

3

2

1

90

92

88

94

BCK

91

PCMD

89

LRCK

87

WDCK

85

C2PO

26

RFCK

25

TES0

MNT0

29

MNT1

30

MNT3

31

WFCK

20

EMPH

93

GFS

24

XUGF

22

GTOP

21

VCTL

43

V16M

42

VCKI

41

VPCO1

39

VPCO2

40

XTSL

83

XTAO

XTAI

FSTO

C4M

84

ACDT

16

RFAC

50

ASYI

52

ASYO

53

BIAS

51

CKOUT

XTAO

XTAI

LMUT2(CH2)

RMUT1(CH1)

SYSM

91

89

87

85

26

25

29

30

Corrector

31

20

93

24

22

21

43

OSC

42

41

39

40

Generator

83

104

103

81

84

16

50

52

Asymmetry

Corector

53

51

104

103

Error

Clock

4

3

2

1

D/A

Interface

demodurator

90

EFM

92

88

BCKI

PCMDI

23

XPCK

23

94

LRCKI

Digital

PLL

45

FILO

45

46

FILI

46

EMPHI

44

PCO

44

48

CLTV

48

16K

RAM

59

RFDC

59

57

TE

57

Digital Filter

+

1 bit DAC

DOUT

33

Digital

OUT

Sub Code

Processor

A/D

CONVERTER

OpAmp

A Sw

55

56

54

SE

FE

VC

55

56

54

Servo

Interface

60

58

CE

RFC

60

58

Digital

CLV

CPU

Interface

Servo

Auto

SEquencer

MIRR

DFCT

FOK

SERVO DSP

FOCUS SERVO

TRACKING SERVO

SLED SERVO

PWM GENERATOR

FOCUS PWM

GENERATOR

TRACKING PWM

GENERATOR

SLED PWM

GENERATOR

61

ADIO

61

99

100

109

108

107

18

10

76

98

15

27

77

78

79

17

8

9

7

6

28

19

14

13

12

36

35

37

69

70

71

72

73

74

AOUT1

AIN1

LOUT1

AOUT2

AIN2

LOUT2

XRST

XROF

LOCK

MDS

MDP

PWMI

SQCK

SQSO

EXCK

SBSO

SCOR

XLON

SPOA

CLOK

XLAT

DATA

SENS

DFCT

MIRR

COUT

FOK

SFDR

SRDR

TFDR

TRDR

FFDR

FRDR

98

99

100

109

108

107

33

15

27

77

78

79

17

8

9

7

6

28

18

19

14

13

12

10

36

35

76

37

69

70

71

72

73

74

– 2 –

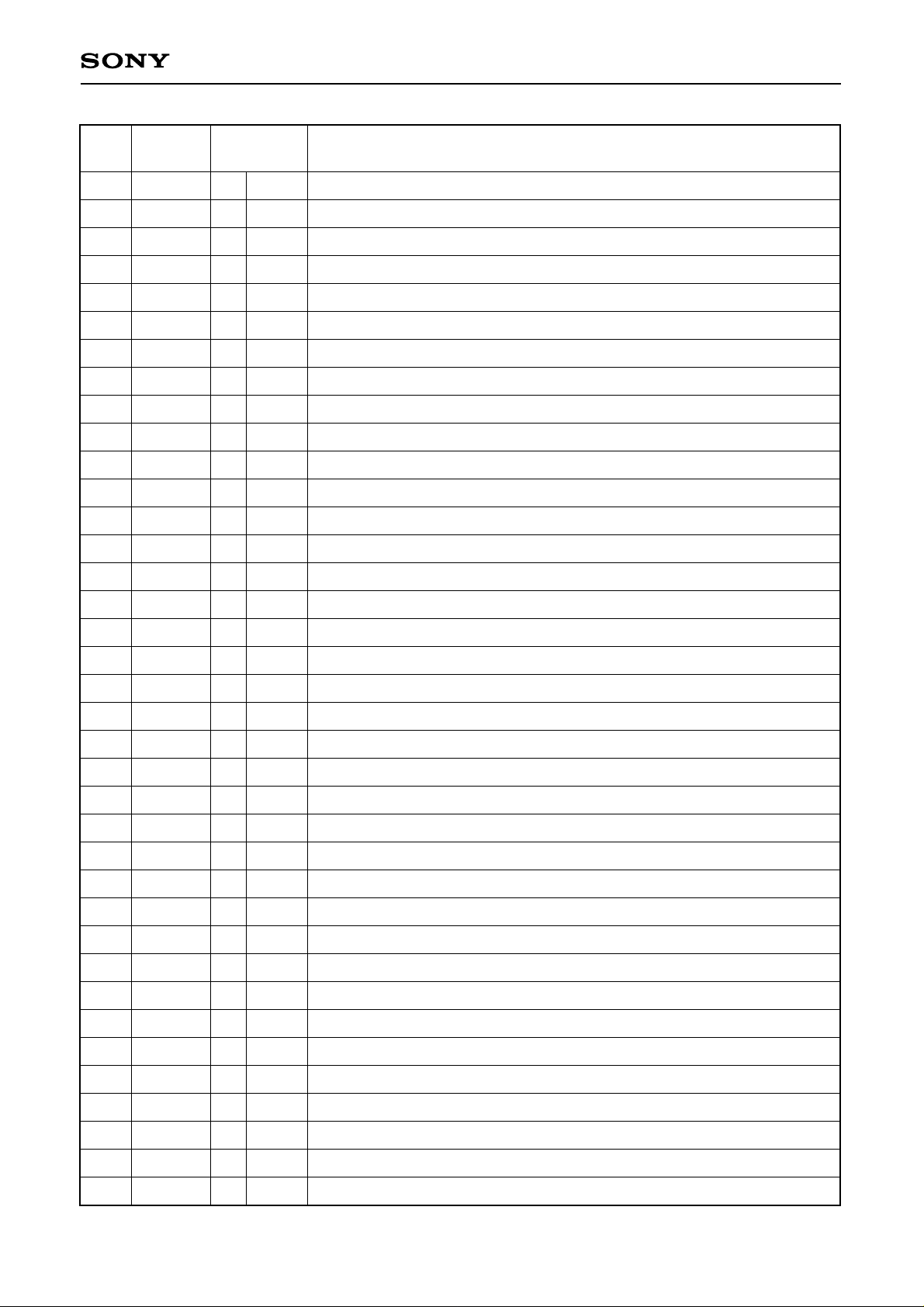

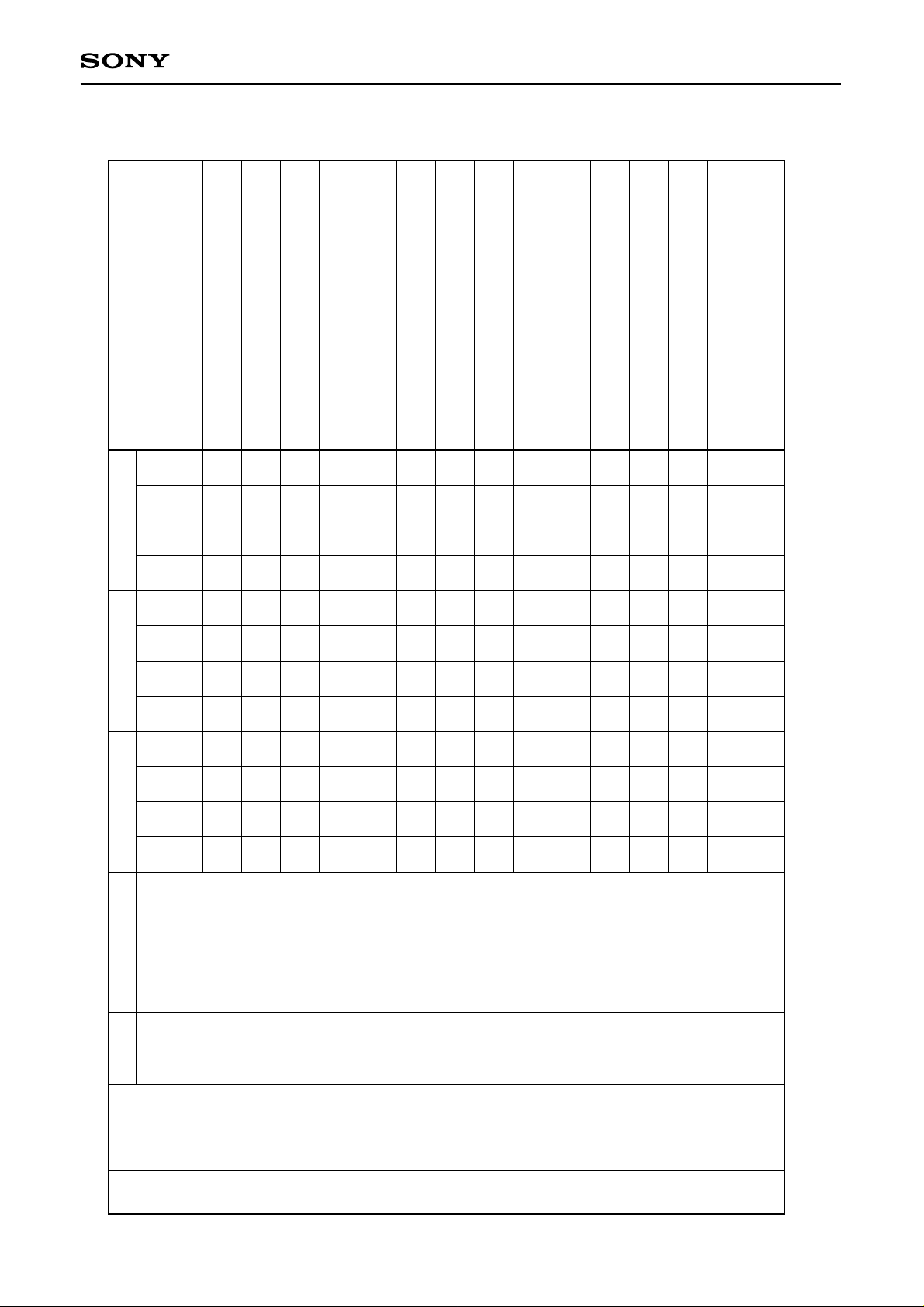

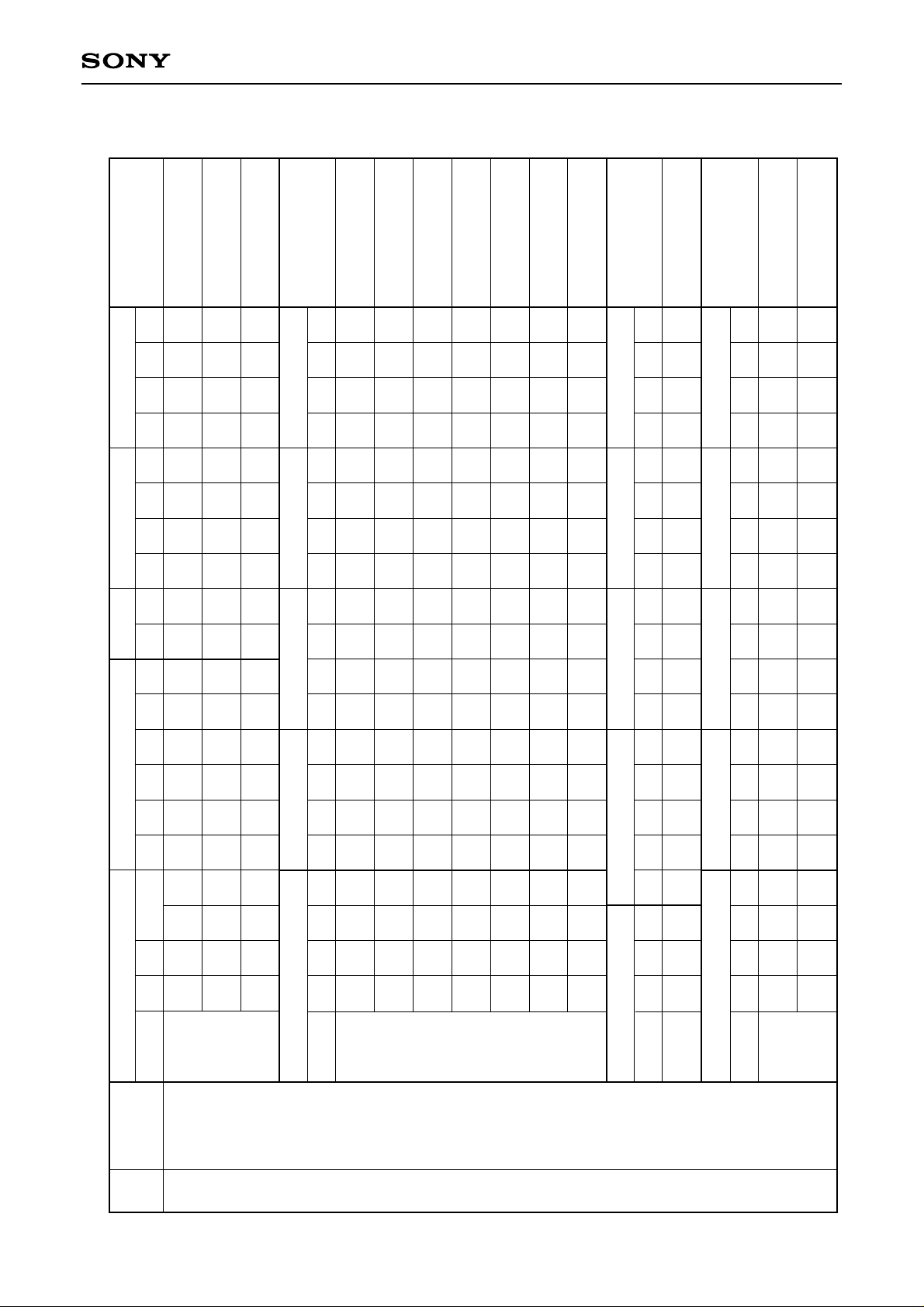

Pin Configuration

XTSL

C4M

84

83

WDCK

PCMDI

EMPHI

AOUT1

LOUT1

LOUT2

AOUT2

V

DD3

LRCK

LRCKI

PCMD

BCK

BCKI

EMPH

V

SS3

AV

SS1

AV

DD1

AIN1

AVSS1

XV

DD

XTAI

XTAO

XV

SS

AV

SS2

AIN2

AV

DD2

AVSS2

VSS0

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

1

SYSM

2

RMUT1

FSTI

82

3

LMUT2

FSTO

81

4

CKOUT

80

5

SSTP

79

6

0

DD

V

MDS

MDP

78

7

EXCK

SBSO

77

8

COUT

LOCK

76

9

SQCK

SQSO

75

10

2

DD

V

74

11

SENS

FRDR

FFDR

73

12

SCLK

DATA

72

13

TRDR

71

14

XLAT

SRDR

TFDR

70

15

XRST

CLOK

69

16

TEST

SFDR

68

17

PWMI

ACDT

67

18

2

SS

V

66

19

XLON

TES2

TES3

65

20

SPOA

WFCK

3

DD

AV

64

21

GTOP

IGEN

63

22

XUGF

62

23

3

SS

AV

61

24

XPCK

ADIO

60

25

GFS

RFDC

RFC

59

26 27

C2PO

RFCK

58

TE

CE

57

28

XROF

SCOR

CXD2548R

SE

56

FE

55

VC

54

ASYO

53

ASYI

52

BIAS

51

RFAC

50

AV

49

CLTV

48

AV

47

FILI

46

FILO

45

PCO

44

VCTL

43

V16M

42

VCKI

41

VPCO2

40

VPCO1

39

V

DD1

38

FOK

37

DFCT

36

MIRR

35

ATSK

34

DOUT

33

V

SS1

32

MNT3

31

MNT1

30

MNT0

29

DD4

SS4

– 3 –

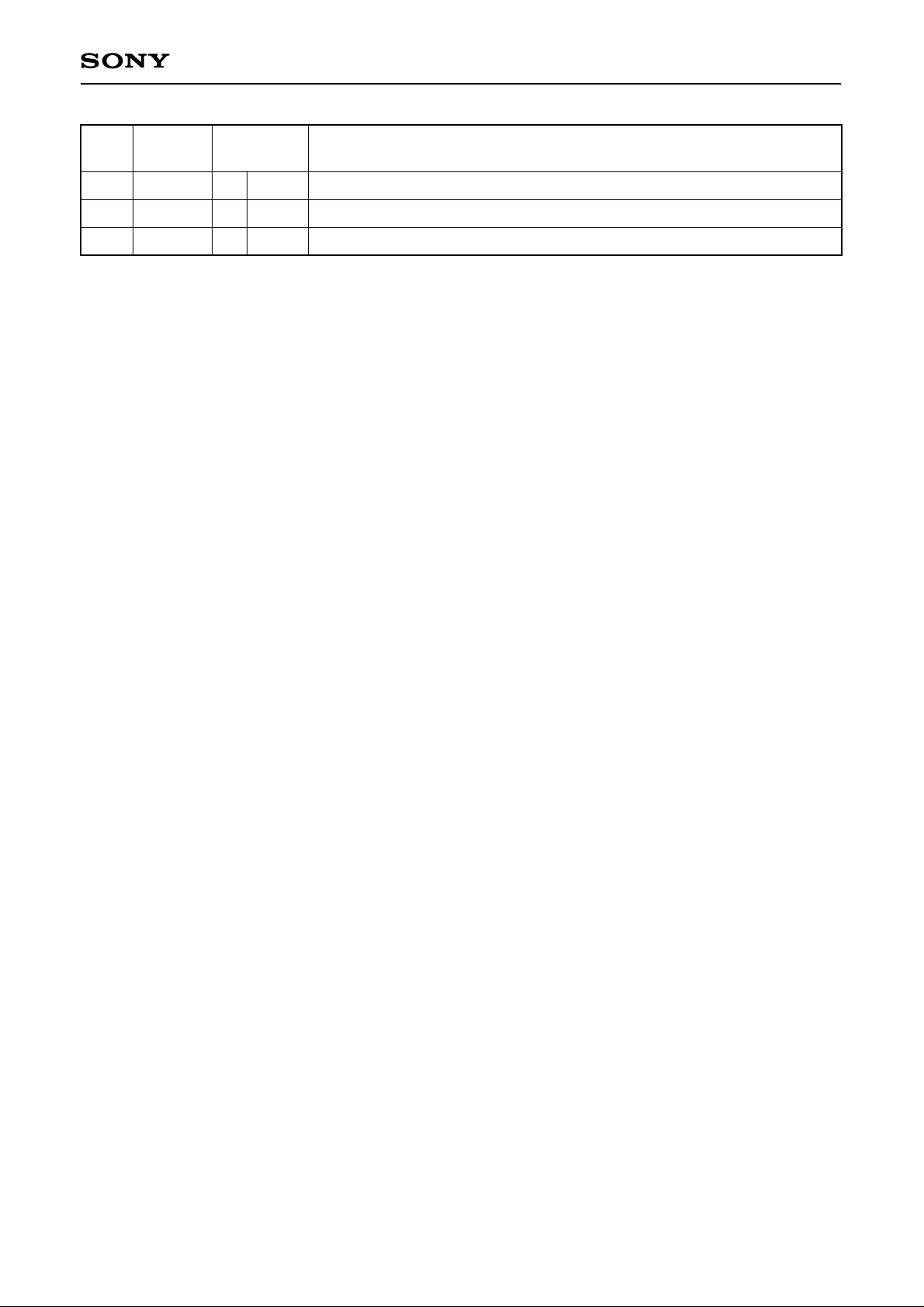

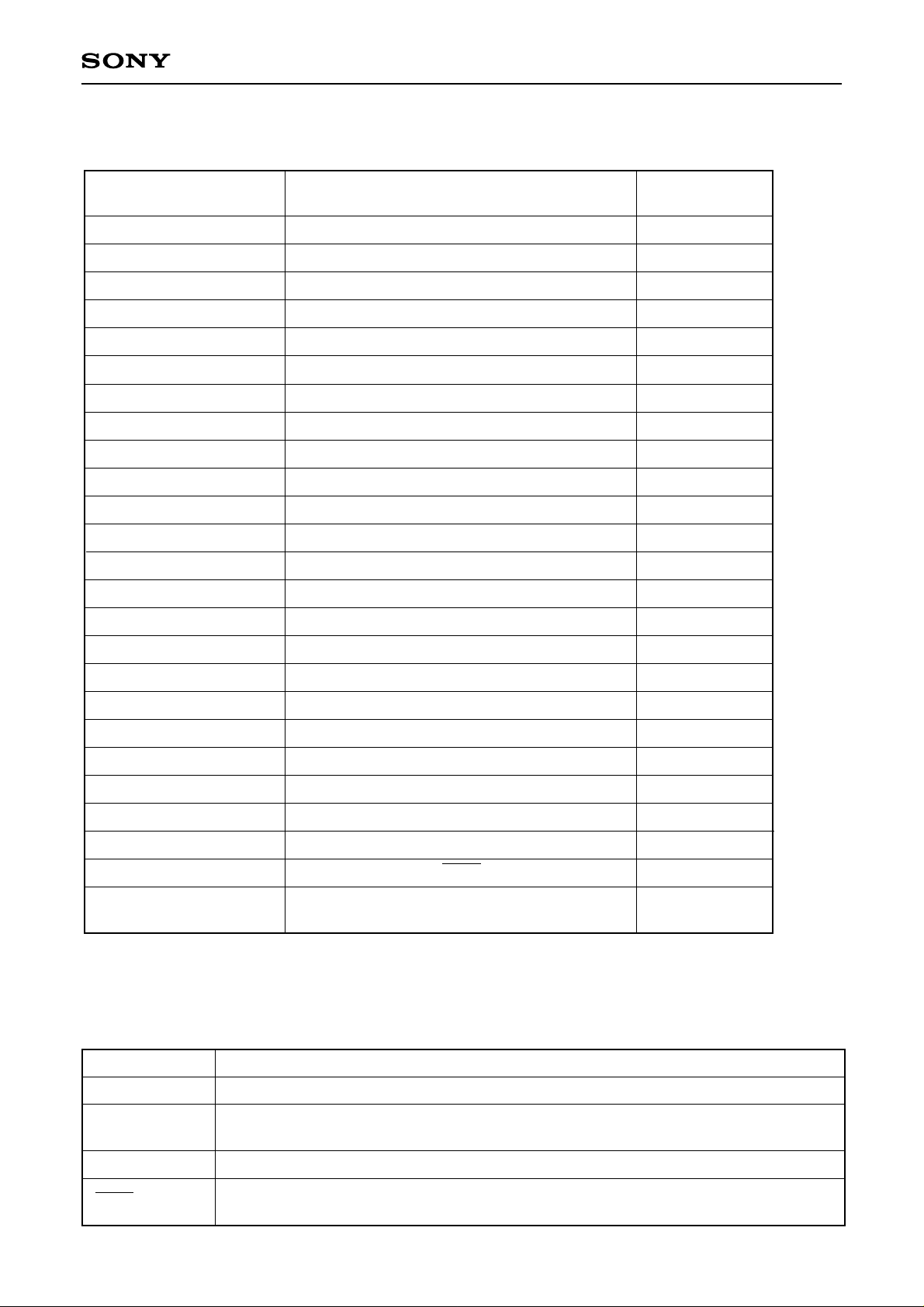

Pin Description

CXD2548R

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Symbol I/O

SYSM

RMUT1

LMUT2

CKOUT

I

O

O

O

VDD0

SBSO

EXCK

SQCK

SQSO

SENS

SCLK

DATA

XLAT

CLOK

O

I

I

O

O

I

I

I

I

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

Description

System mute input. (high = on, low = off)

R ch zero detection output. (high = on, low = off)

L ch zero detection output. (high = on, low = off)

DAC master clock frequency division output. Either the clock input from

XTAI × 1, × 1/2 or × 1/4, or low output is selected and output.

Digital power supply.

Sub P to W serial output.

SBSO readout clock input.

SQSO readout clock input.

Sub Q 80-bit and PCM peak and level data 16-bit output.

SENS output to CPU.

SENS serial data readout clock input.

Serial data input from CPU.

Latch input from CPU. Serial data is latched at the falling edge.

Serial data transfer clock input from CPU.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

XRST

ACDT

PWMI

XLON

SPOA

WFCK

GTOP

XUGF

XPCK

GFS

RFCK

C2PO

XROF

SCOR

MNT0

MNT1

MNT3

I

1, 0

O

I

1, 0

O

I

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

System reset. Reset when low.

Normally not used. Leave open.

Spindle motor external control input.

Microcomputer extension interface (output).

Microcomputer extension interface (input A).

WFCK (Write Flame Clock) output.

GTOP output.

XUGF output.

XPLCK output.

GFS output.

RFCK output.

C2PO output.

XRAOF output.

Outputs a high signal when either subcode sync S0 or S1 is detected.

MNT0 output.

MNT1 output.

MNT3 output.

32

33

34

35

36

Vss1

DOUT

ATSK

MIRR

DFCT

Digital GND.

1, 0

O

I

1, 0

O

1, 0

O

Digital Out output pin.

Anti-shock pin.

Mirror signal output.

Defect signal output.

– 4 –

CXD2548R

Pin

No.

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

Symbol I/O

FOK

O

VDD1

VPCO1

VPCO2

VCKI

V16M

VCTL

PCO

FILO

FILI

O

O

I

O

I

O

O

I

AVss4

CLTV

I

AVDD4

RFAC

BIAS

I

I

1, 0

1, Z, 0

1, Z, 0

1, 0

1, Z, 0

Analog

Description

Focus OK signal output.

Digital power supply.

Wide-band EFM PLL charge pump output.

Wide-band EFM PLL VCO2 charge pump output.

Wide-band EFM PLL VCO2 oscillation input.

Wide-band EFM PLL VCO2 oscillation output.

Wide-band EFM PLL VCO2 control input.

Master PLL charge pump output.

Master PLL filter output (slave = digital PLL).

Master PLL filter input.

Analog GND.

Master VCO control voltage input.

Analog power supply.

EFM signal input.

Asymmetry circuit constant current input.

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

ASYI

ASYO

VC

FE

SE

TE

CE

RFDC

RFC

ADIO

AVss3

IGEN

AVDD3

TES2

TES3

Vss2

TEST

I

O

1, 0

I

I

I

I

I

I

I

O

Asymmetry comparator voltage input.

EFM full-swing output (low = VSS, high = VDD).

Center voltage input.

Focus error signal input.

Sled error signal input.

Tracking error signal input.

Center error signal input.

RF signal input. Input range: 2.15 to 5.0V. (when DVDD = AVDD = 5.0V)

Connects an RF signal LPF time-constant capacitor.

Operational amplifier output.

Analog GND.

I

Connects an operational amplifier current source reference resistor.

Analog power supply.

I

I

Test pin. Normally fixed to low.

Test pin. Normally fixed to low.

Digital GND.

I

Test pin. Normally fixed to low.

69

70

71

72

73

SFDR

SRDR

TFDR

TRDR

FFDR

O

1, 0

O

1, 0

O

1, 0

O

1, 0

O

1, 0

Sled drive output.

Sled drive output.

Tracking drive output.

Tracking drive output.

Focus drive output.

– 5 –

CXD2548R

Pin

No.

74

75

76

77

78

79

80

81

82

83

84

85

86

87

Symbol I/O

FRDR

O

VDD2

COUT

LOCK

MDS

MDP

SSTP

FSTO

FSTI

XTSL

C4M

WDCK

O

O

O

O

I

O

I

I

O

O

VDD3

LRCK

O

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

Description

Focus drive output.

Digital power supply.

Track count signal output.

GFS is sampled at 460Hz; when GFS is high, this pin outputs a high signal.

If GFS is low eight consecutive samples, this pin outputs low.

Spindle motor servo control output.

Spindle motor servo control output.

Disc innermost track detection signal input.

2/3-frequency division output for Pins 103 and 104.

Digital servo reference clock input.

Crystal selection input. Low when the crystal is 16.9344MHz; high when the

crystal is 33.8688MHz.

4.2336MHz output.

D/A interface. Word clock f = 2Fs

Digital power supply.

D/A interface. LR clock f = Fs

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

LRCKI

PCMD

PCMDI

BCK

BCKI

EMPH

EMPHI

Vss3

AVss1

AVDD1

AOUT1

AIN1

LOUT1

AVss1

XVDD

XTAI

O

O

O

O

O

I

I

I

I

I

I

1, 0

1, 0

1, 0

Analog

Analog

LR clock input to DAC (48-bit slot).

D/A interface. Serial data. (two's complement, MSB first)

Audio data input to DAC (48-bit slot).

D/A interface. Bit clock.

Bit clock input to DAC (48-bit slot).

Outputs a high signal when the playback disc has emphasis, and a low

signal when there is no emphasis.

DAC de-emphasis ON/OFF. (high = on, low = off)

Digital GND.

L ch, analog GND.

L ch, analog power supply.

L ch, analog output.

L ch, operational amplifier input.

L ch, LINE output.

L ch, analog GND.

Master clock analog power supply.

Master clock 16.9344MHz crystal oscillation circuit input, or 33.8688MHz input.

104

105

106

107

108

109

XTAO

XVss

AVss2

LOUT2

AIN2

AOUT2

O

O

O

I

1, 0

Analog

Analog

Master clock 16.9344MHz crystal oscillation circuit output.

Master clock analog GND.

R ch, analog GND.

R ch, LINE output.

R ch, operational amplifier input.

R ch, analog output.

– 6 –

CXD2548R

Pin

No.

110

111

112

Symbol I/O

AVDD2

AVss2

Vss0

R ch, analog power supply.

R ch, analog GND.

Digital GND.

Notes) • PCMD is a MSB first, two's complement output.

• GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

• XUGF is the frame sync obtained from the EFM signal, and negative pulse. It is the signal before

sync protection.

• XPLCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the

EFM signal transition point coincide.

• The GFS signal goes high when the frame sync and the insertion timing match.

• RFCK is derived from the crystal accuracy, and has a cycle of 136µs (during normal speed).

• C2PO represents the data error status.

• XRAOF is generated when the 16K RAM exceeds the ±4F jitter margin.

Description

– 7 –

CXD2548R

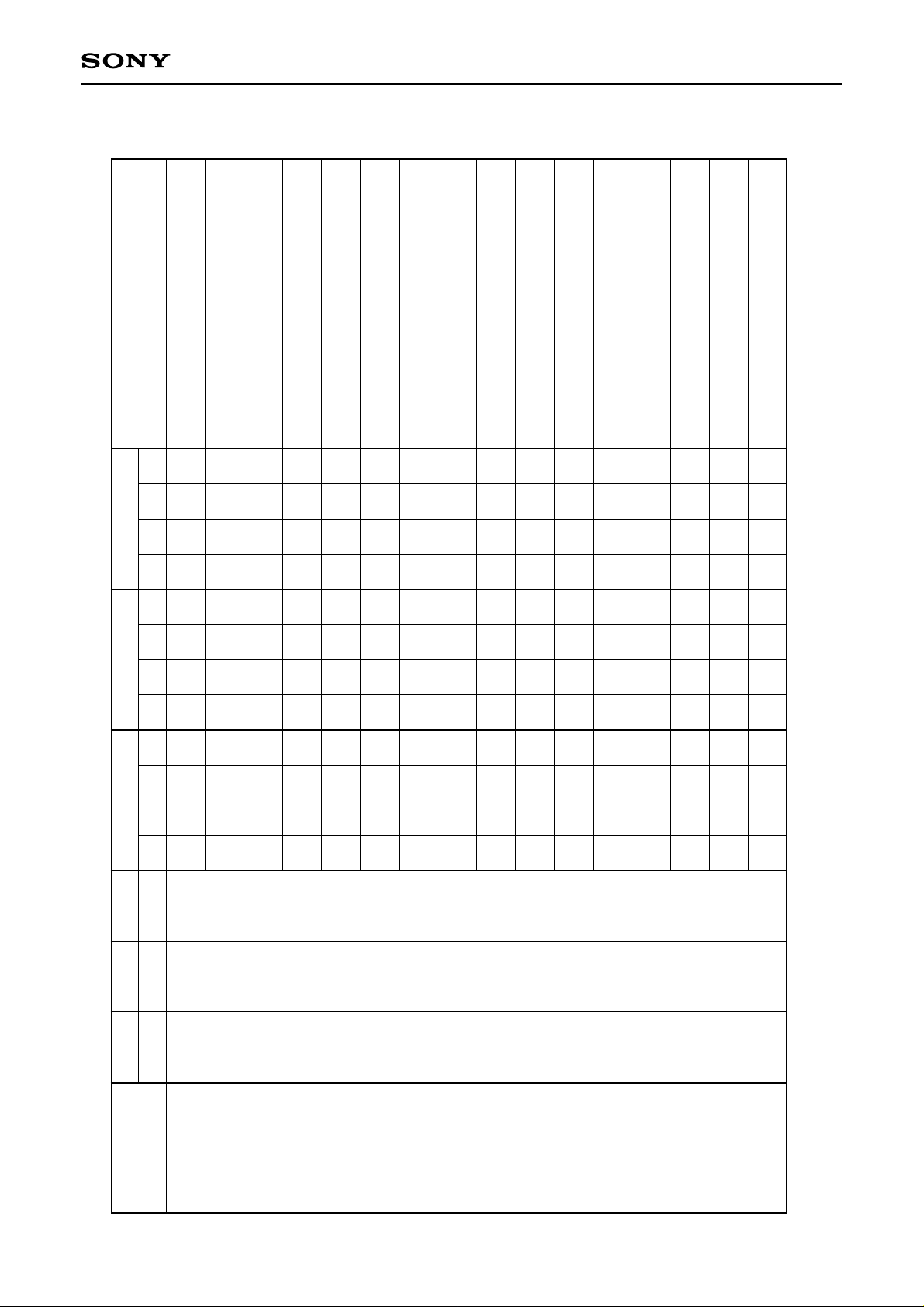

Electrical Characteristics

1. DC Characteristics (VDD = AVDD = 5.0V ± 5%, Vss = AVss = 0V, Topr = –20 to +75°C)

Input voltage (1)

High level input voltage

Low level input voltage

High level input voltage

Input voltage (2)

Low level input voltage

Input voltage (3)

Output

voltage (1)

Output

voltage (2)

Output

voltage (3)

Input voltage

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

Input leak current (1)

Input leak current (2)

Input leak current (3)

Tri-state pin

output leak current

Item

VIH (1)

VIL (1)

VIH (2)

VIL (2)

VIN(3)

VOH(1)

VOL(1)

VOH(2)

VOL(2)

VOH(3)

VOL(3)

ILI (1)

ILI (2)

ILI (3)

ILO

Conditions Min. Typ. Max. Unit

0.7VDD

0.3VDD

Schmitt input

0.8VDD

0.2VDD

Analog input

IOH = –4mA

IOL = 4mA

IOH = –2mA

IOL = 4mA

IOH = –0.28mA

IOL = 0.36mA

VI = 0 to 5.5V

VI = 1.5 to 3.5V

VI = 0 to 5.0V

VO = 0 to 5.5V

Vss

VDD – 0.8

0

VDD – 0.8

0

VDD – 0.5

0

–10

–20

–40

–5

VDD

VDD

0.4

VDD

0.4

VDD

0.4

10

20

600

5

Applicable pins

V

∗1

V

V

∗2

V

∗3

V

V

, 7, 8,

∗4

V

V

∗5

V

V

∗6

V

∗1

µA

µA

µA

µA

,

∗7

∗8

∗9

10

2

Applicable pins

∗1

XTSL, DATA, XLAT, TEST, TES2, TES3, SSTP, ATSK, PWMI, SYSM, EMPHI, PCMDI

∗2

CLOK, XRST, EXCK, SQCK, VCKI, LRCKI, BCKI, SPOA, SCLK

∗3

CLTV, FILI, RFAC, VCTL, AIN1, AIN2, ASYI

∗4

MDP, PCO, PDO, VPCO1, VPCO2

∗5

ASYO, DOUT, FSTO, C4M, SBSO, SQSO, SCOR, EMPH, LOCK, WDCK, SENS, MDS, MNT0, MNT1,

MNT3, WFCK, V16M, CKOUT, LMUT2, RMUT1, XLON, LRCK, PCMD, BCK, GTOP, XUGF, XPCK, GFS,

RFCK, C2PO, XRAOF, MIRR, DFCT, COUT, FFDR, FRDR, TFDR, TRDR, SFDR, SRDR

∗6

FILO

∗7

TE, SE, FE, CE, VC

∗8

RFDC

∗9

SENS, MDS, MDP, PDO, PCO, VPCO1, VPCO2

∗10

RFC

– 8 –

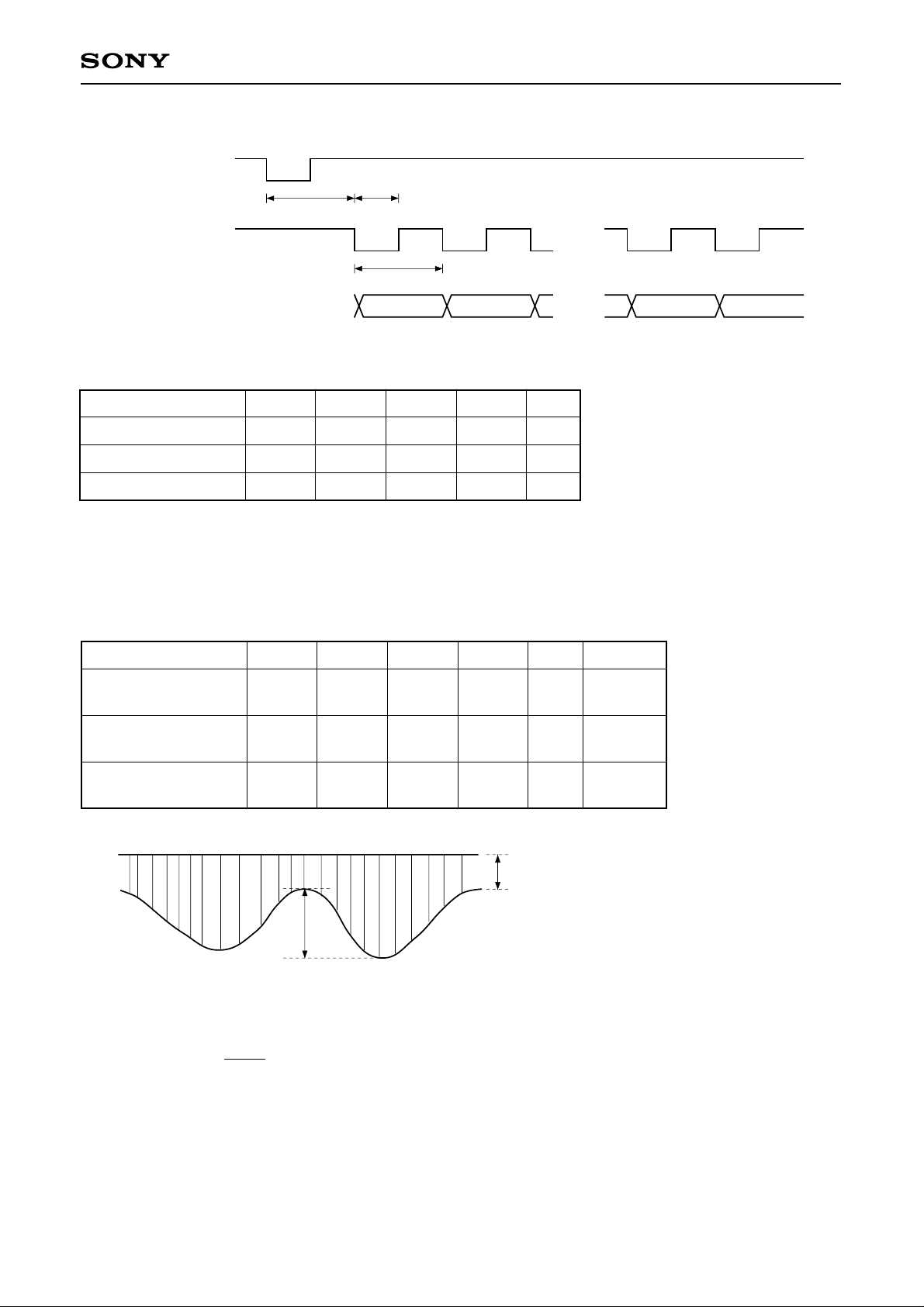

2. AC Characteristics

(1) XTAI pin

(a) When using self-excited oscillation

(Topr = –20 to +75°C, VDD = AVDD = 5.0V ± 5%)

CXD2548R

Item Symbol Min. Typ. Max.

Oscillation

frequency

fMAX

7

(b) When inputting pulses to XTAI pin

(Topr = –20 to +75°C, VDD = AVDD = 5.0V ± 5%)

Item Symbol Min.

High level pulse

width

Low level pulse

width

Pulse cycle

tWHX

tWLX

tCK

13 500

13 500

26 1,000

Typ. Max. Unit

Input high level VIHX VDD – 1.0

Input low level VILX 0.8

Rise time, fall

time

tR, tF

34

10

Unit

MHz

ns

ns

ns

V

V

ns

tCX

tWHX

XTLI

tR tF

tWLX

(c) When inputting sine waves to XTLI pin via a capacitor

(Topr = –20 to +75°C, VDD = AVDD = 5.0V ± 5%)

Item Symbol Min.

Typ. Max. Unit

Input amplitude VI 2.0 VDD + 0.3 Vp-p

VIHX

V

IHX × 0.9

V

DD/2

VIHX × 0.1

VILX

– 9 –

(2) CLOK, DATA, XLAT, SQCK, and EXCK pins

(VDD = AVDD = 5.0V ± 5%, VSS = AVSS = 0V, Topr = –20 to +75°C)

CXD2548R

Item Symbol

Clock frequency

Clock pulse width

Setup time

Hold time

Delay time

Latch pulse width

EXCK, SQCK frequency

EXCK, SQCK pulse width

fCK

tWCK

tSU

tH

tD

tWL

fT

fWT

Min. Typ. Max. Unit

0.65

750

300

300

300

750

0.65

∗1

750

1/fCK

tWCK tWCK

CLK

DATA

XLT

EXCK

SQCK

SUBQ

SQCK

tSU

tSU

tH

tWT tWT

1/fT

tH

∗1

MHz

MHz

tD

ns

ns

ns

ns

ns

ns

tWL

∗1

In quasi double-speed playback mode, except when SQSO is Sub Q Read, the SQCL maximum operating

frequency is 300kHz and its minimum pulse width is 1.5µs.

(3) BCKI, LRCKI and PCMDI pins (VDD = AVDD = 5.0V ± 5%, VSS = AVSS = 0V, Topr = –20 to +75°C)

Item Symbol

BCK pulse width

DATAL, R setup time

DATAL, R hold time

LRCK setup time

BCKI

PCMDI

tW

tSU

tH

tSU

Conditions

VDD/2 VDD/2

tSU

(PCMDI)

Min.

Typ.

94

18

18

18

tW(BCKI)tW(BCKI)

H

t

(PCMDI)

tSU

(LRCKI)

Max. Unit

ns

ns

ns

ns

LRCKI

– 10 –

(4) SCLK pin

CXD2548R

XLAT

tSPWtDLS

SCLK

Serial Read Out Data

(SENS)

Item

SCLK frequency

SCLK pulse width

Delay time

1/fSCLK

MSB LSB

Symbol Min. Typ. Max.

fSCLK

tSPW

tDLS

500

15

1 MHz

···

···

Unit

ns

µs

(5) COUT, MIRR and DFCT pins

Operating frequency (VDD = AVDD = 5.0V ± 5%, VSS = AVSS = 0V, Topr = –20 to +75°C)

Item Symbol

COUT maximum

operating frequency

fCOUT

Min. Typ.

40

Max.

Unit

kHz

Conditions

∗1

MIRR maximum

operating frequency

DFCT maximum

operating frequency

∗1

When using a high-speed traverse TZC

fMIRR

fDFCTH

40

5

kHz

kHz

∗2

∗3

∗2

B

A

When the RF signal continuously satisfies the following conditions during the above traverse.

• A = 0.6 to 1.3V

B

• = 25% or less

A + B

∗3

During complete RF signal omission

When settings related to DFCT signal generation are Typ.

– 11 –

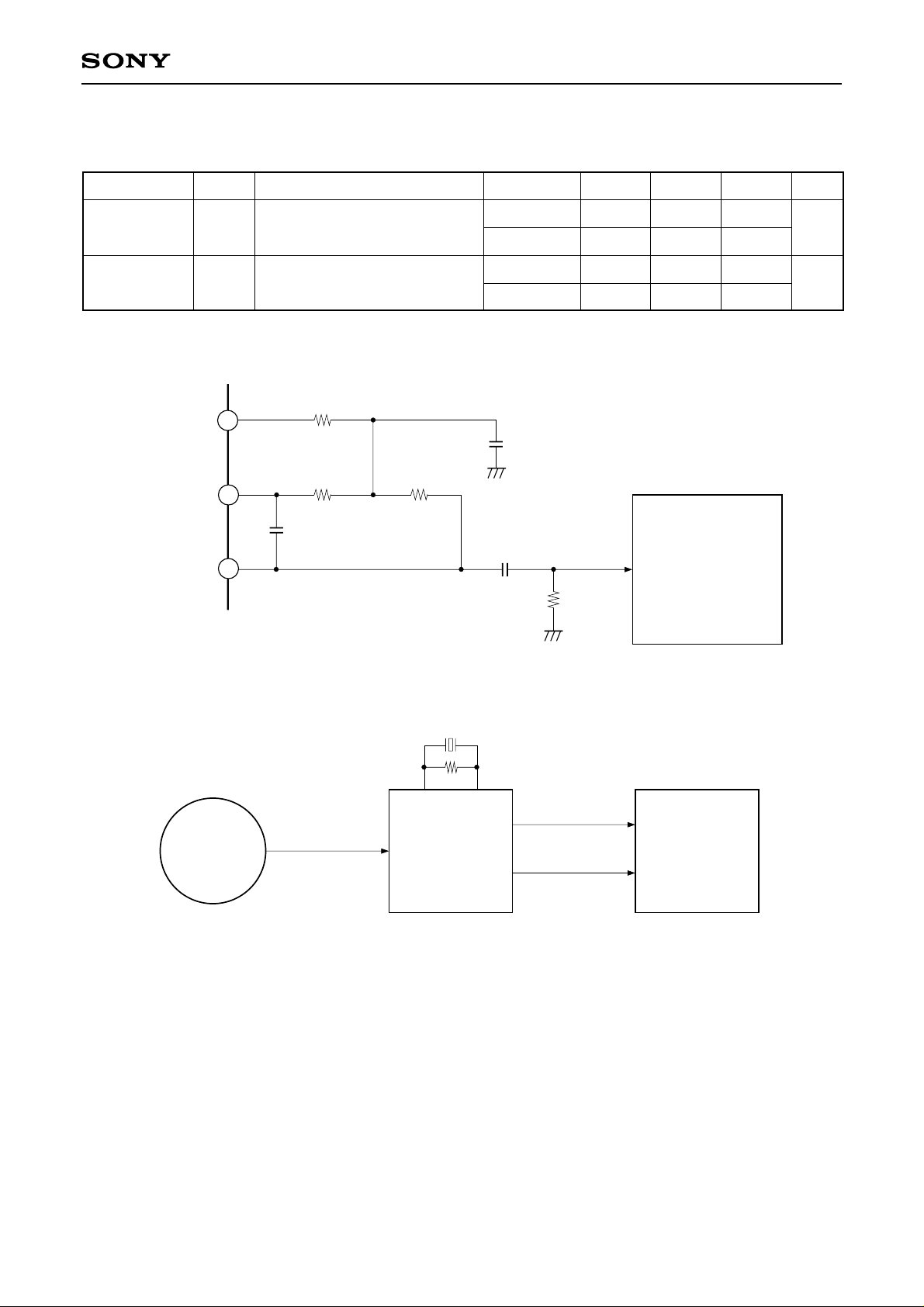

1-bit DAC and LPF Block Analog Characteristics

Analog characteristics (VDD = AVDD = 5.0V, VSS = AVSS = 0V, Ta = 25°C)

CXD2548R

Item

Total harmonic

distortion

Signal-to-noise

ratio

Symbol

THD

S/N

Conditions

1kHz, 0dB data

1kHz, 0dB data

(Using A-weighting filter)

Crystal

384Fs

768Fs

384Fs

768Fs

Min.

96

96

Typ.

0.0050

0.0045

100

100

Fs = 44.1kHz in all cases.

The total harmonic distortion and signal-to-noise ratio measurement circuits are shown below.

12k

AOUT1 (2)

680p

12k

AIN1 (2)

150p

LOUT1 (2)

12k

SHIBASOKU (AM51A)

Audio Analyzer

22µ

100k

Max.

0.0070

0.0065

Unit

%

dB

TEST DISC

LPF external circuit diagram

768Fs/384Fs

Rch A

DATA RF

CXD2548R

Lch B

Block diagram of analog characteristics measurement

Audio Analyzer

– 12 –

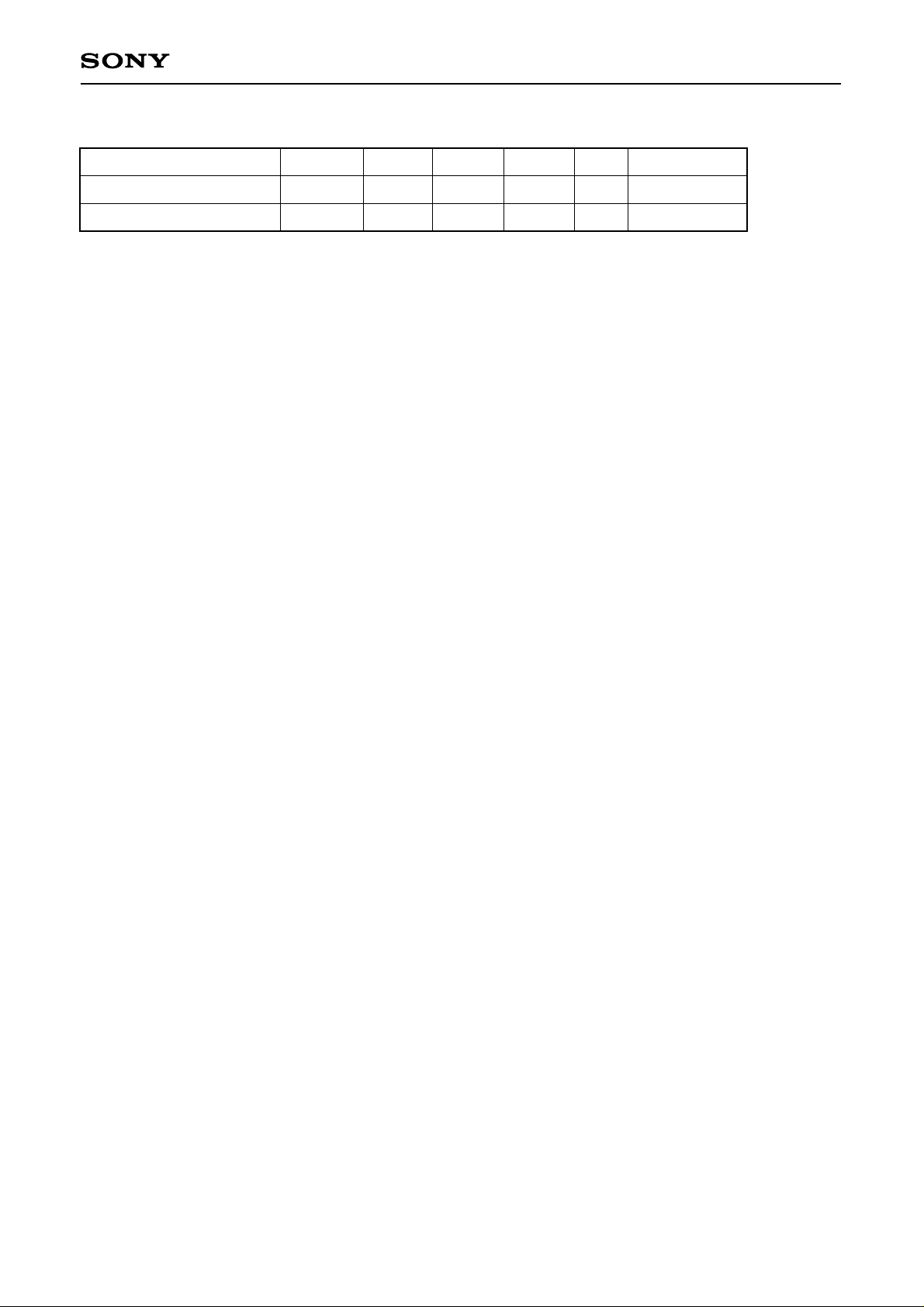

(VDD = AVDD = 5.0V, VSS = AVSS = 0V, Topr = –20 to +75°C)

CXD2548R

Item Symbol

Output voltage

Load resistance

∗

When a sine wave of 1kHz and 0dB is output.

VOUT

RL

Applicable pins

∗1

LOUT1, LOUT2

Min.

8

Typ.

1.15

Max.

∗

Unit

Vrms

Applicable pins

kΩ

∗1

∗1

– 13 –

CXD2548R

Contents

[1] CPU Interface

§1-1. CPU Interface Timing ...................................................................................................................... 15

§1-2. CPU Interface Command Table ...................................................................................................... 16

§1-3. CPU Command Presets .................................................................................................................. 25

§1-4. Description of SENS Signals ........................................................................................................... 30

[2] Description of CD Signal Processing and DAC System Commands and Subcode Interface

§2-1. Description of Commands and Data Sets ....................................................................................... 31

§2-2. Subcode Interface ........................................................................................................................... 50

[3] Description of Other CD Signal Processing and DAC System Functions

§3-1. Description of DSP Operating Modes ............................................................................................. 55

(a) CLV-N Mode .................................................................................................................................... 55

(b) CLV-W Mode ................................................................................................................................... 55

(c) CAV-W Mode .................................................................................................................................. 55

§3-2. Frame Sync Protection .................................................................................................................... 57

§3-3. Error Correction ............................................................................................................................... 57

§3-4. DA Interface .................................................................................................................................... 58

§3-5. Digital Out ........................................................................................................................................ 60

§3-6. Servo Auto Sequence ..................................................................................................................... 60

§3-7. Asymmetry Compensation .............................................................................................................. 67

§3-8. Channel Clock Regeneration by the Digital PLL Circuit .................................................................. 68

§3-9. Digital CLV ...................................................................................................................................... 70

§3-10. 1-bit DAC Block ............................................................................................................................... 71

§3-11. LPF Block ........................................................................................................................................ 73

§3-12. Setting the Playback Speed for the CD-DSP and 1-bit DAC Blocks ............................................... 74

[4] Description of Servo Signal Processing System Functions and Commands

§4-1. General Description of the Servo Signal Processing System ......................................................... 75

§4-2. Digital Servo Block Master Clock (MCK) ......................................................................................... 76

§4-3. AVRG Measurement and Compensation ........................................................................................ 76

§4-4. E:F Balance Adjustment Function ................................................................................................... 78

§4-5. FCS Bias Adjustment Function ....................................................................................................... 78

§4-6. AGCNTL Function ........................................................................................................................... 80

§4-7. FCS Servo and FCS Search ........................................................................................................... 82

§4-8. TRK and SLD Servo Control ........................................................................................................... 83

§4-9. MIRR and DFCT Signal Generation ................................................................................................ 84

§4-10. DFCT Countermeasure Circuit ........................................................................................................ 85

§4-11. Anti-Shock Circuit ............................................................................................................................ 85

§4-12. Brake Circuit .................................................................................................................................... 86

§4-13. COUT Signal ................................................................................................................................... 87

§4-14. Serial Readout Circuit ..................................................................................................................... 87

§4-15. Writing the Coefficient RAM ............................................................................................................ 88

§4-16. PWM Output .................................................................................................................................... 88

§4-17. Servo Status Changes Produced by the LOCK Signal ................................................................... 90

§4-18. Description of Commands and Data Sets ........................................................................................ 90

§4-19. List of Servo Filter Coefficients ...................................................................................................... 102

§4-20. FILTER Composition ..................................................................................................................... 104

§4-21. TRACKING and FOCUS Frequency Response ............................................................................ 111

[5] Application Circuit

§5-1. Application Circuit .......................................................................................................................... 112

Explanation of abbreviations AVRG: Average

AGCNTL: auto gain control

FCS: Focus

TRK: Tracking

SLD: Sled

DFCT: Defect

– 14 –

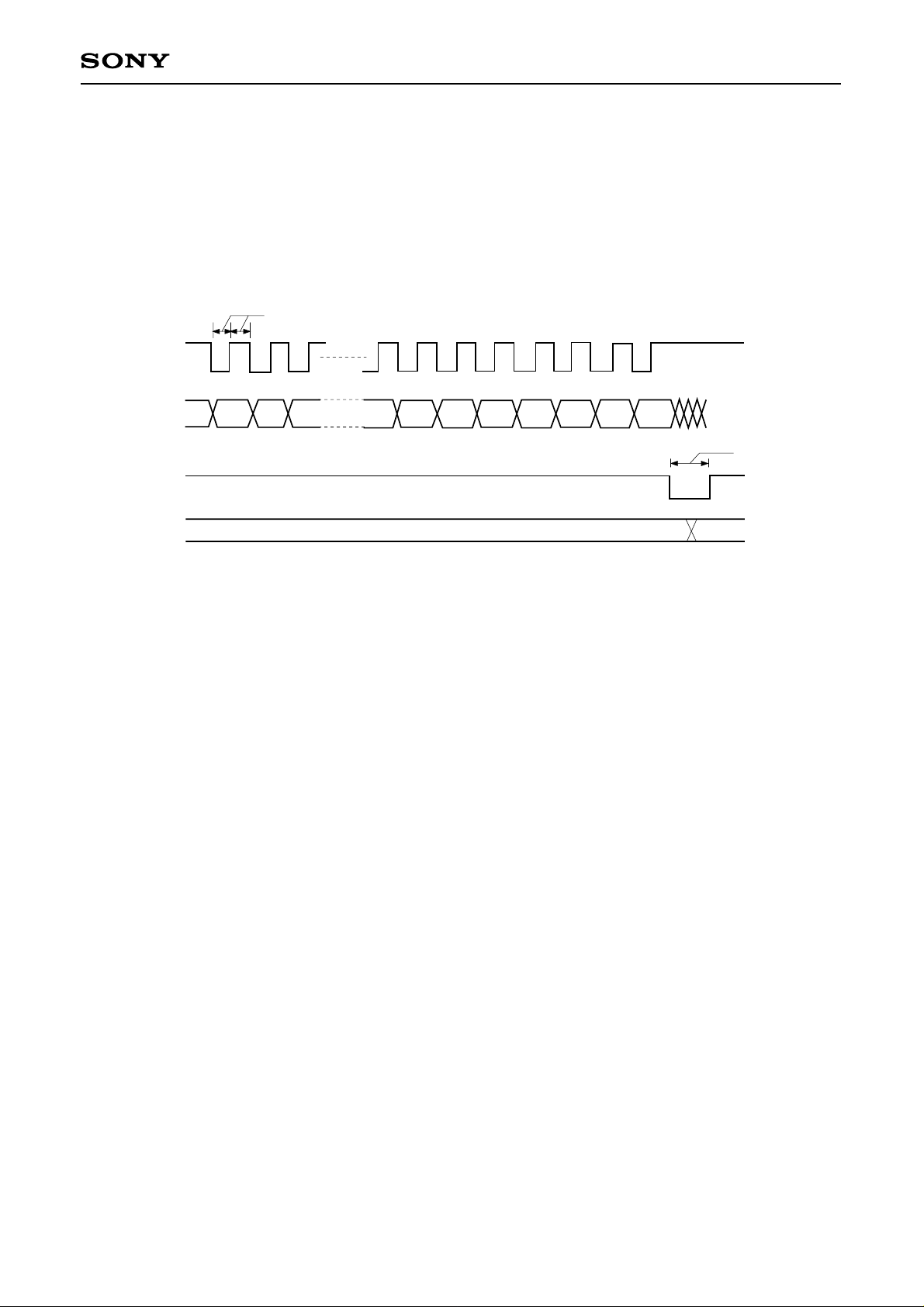

[1] CPU Interface

§1-1. CPU Interface Timing

• CPU Interface

This interface uses DATA, CLOK, and XLAT to set the modes.

The interface timing chart is shown below.

750ns or more

CLOK

CXD2548R

DATA

(Example)

XLAT

Registers

D18 D19 D20 D21 D22 D23

• The internal registers are initialized by a reset when XRST = 0.

Note) Be sure to set SQCK to high when XLAT is low.

750ns or more

Valid

– 15 –

FOCUS SERVO ON

(FOCUS GAIN

NORMAL)

FOCUS SERVO ON

(FOCUS GAIN

DOWN)

FOCUS SERVO OFF,

0V OUT

FOCUS SERVO OFF,

FOCUS SEARCH

VOLTAGE OUT

FOCUS SEARCH

VOLTAGE DOWN

FOCUS SEARCH

VOLTAGE UP

ANTI SHOCK ON

ANTI SHOCK OFF

BRAKE ON

BRAKE OFF

TRACKING GAIN

NORMAL

TRACKING GAIN UP

TRACKING GAIN UP

CXD2548R

—: Don’t care

FILTER SELECT 1

TRACKING GAIN UP

FILTER SELECT 2

Data 5

Data 4

Data 3

D0

D3 D2 D1

D4

D7 D6 D5

D11 D10 D9 D8

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Data 2

D14 D13 D12

D15

—

—

—

—

Data 1

Address

Command

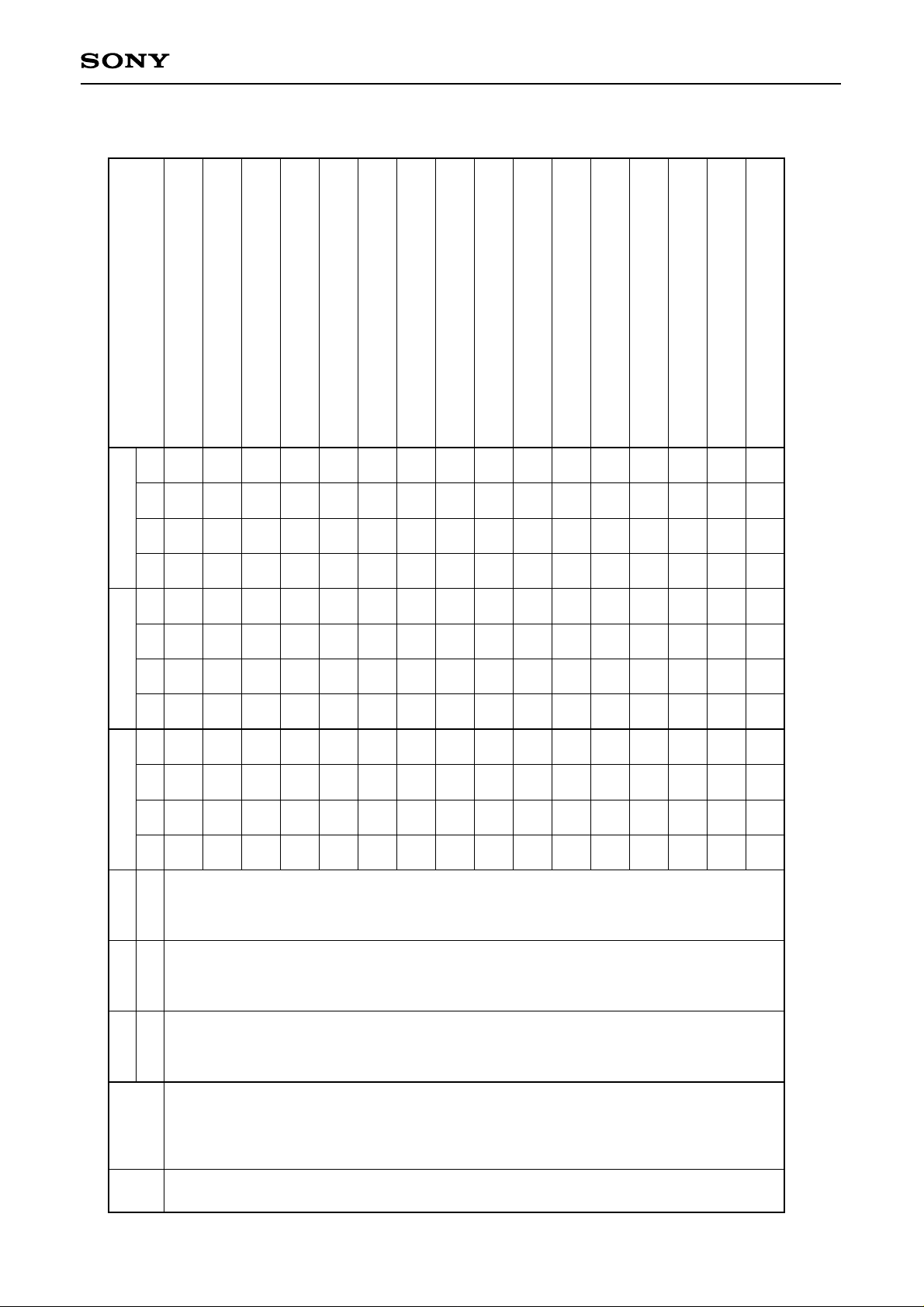

§1-2. CPU Interface Command Table

Register

Command Table ($0X to 1X)

0

D18 D17 D16

1

D19

D23 to D20

—

—

—

—

—

1

1

—

—

—

—

0

—

0

0 0 0 0

FOCUS

CONTROL

0

—

—

—

—

1

—

0

—

—

—

0

1

—

0

—

—

—

1

1

—

0

—

—

—

—

—

0

1

—

—

—

—

—

—

0

—

—

—

—

—

1

—

—

—

—

—

—

—

—

—

0

—

0

—

—

—

0 0 0 1

TRACKING

CONTROL

1

—

—

—

—

1

—

—

—

—

—

1

—

—

—

—

—

—

0

—

—

—

– 16 –

TRACKING SERVO OFF

TRACKING SERVO ON

FORWARD TRACK JUMP

REVERSE TRACK JUMP

—

—

—

—

—

—

—

—

SLED SERVO OFF

SLED SERVO ON

FORWARD SLED MOVE

—

—

—

—

—

—

REVERSE SLED MOVE

—

—

(±1 × basic value) (Default)

SLED KICK LEVEL

—

—

basic value)

basic value)

×

SLED KICK LEVEL

(±2

SLED KICK LEVEL

—

—

basic value)

×

×

(±3

SLED KICK LEVEL

(±4

—

—

—

—

CXD2548R

—: Don’t care

Data 5

Data 4

Data 3

Data 2

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

D13 D12

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Data 5

Data 4

Data 3

Data 2

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

D13 D12

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

0

—

—

—

0

1

D15 D14

—

—

D17 D16

Data 1

Address

Command Table ($2X to 3X)

D19 D18

D23 to D20

Command

Register

0

0

—

0

—

0

—

1

—

1

—

0 0 1 0

TRACKING

MODE

2

—

—

1

0

—

—

—

0

1

—

—

—

1

1

—

—

– 17 –

D15 D14

Data 1

D17 D16

D19 D18

Address

D23 to D20

Command

Register

0

0

0

0

—

—

1

0

0

0

—

0

1

0

0

0 0 1 1

SELECT

3

—

1

1

0

0

Data 2

KRAM DATA (K00)

SLED INPUT GAIN

KRAM DATA (K01)

KD0

D1 D0

KD1

KD2

SLED LOW BOOST FILTER A-H

KRAM DATA (K02)

SLED LOW BOOST FILTER A-L

KRAM DATA (K03)

SLED LOW BOOST FILTER B-H

KRAM DATA (K04)

SLED LOW BOOST FILTER B-L

KRAM DATA (K05)

SLED OUTPUT GAIN

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

KRAM DATA (K06)

FOCUS INPUT GAIN

KRAM DATA (K07)

SLED AUTO GAIN

KRAM DATA (K08)

KD0

KD0

KD0

KD1

KD1

KD1

KD2

KD2

KD2

FOCUS HIGH CUT FILTER A

KRAM DATA (K09)

FOCUS HIGH CUT FILTER B

KRAM DATA (K0A)

FOCUS LOW BOOST FILTER A-H

KRAM DATA (K0B)

FOCUS LOW BOOST FILTER A-L

KRAM DATA (K0C)

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

CXD2548R

FOCUS LOW BOOST FILTER B-H

KRAM DATA (K0D)

FOCUS LOW BOOST FILTER B-L

KRAM DATA (K0E)

FOCUS PHASE COMPENSATE FILTER A

KRAM DATA (K0F)

FOCUS DEFECT HOLD GAIN

KD0

KD0

KD0

KD1

KD1

KD1

KD2

KD2

KD2

D3 D2

D5 D4

Data 1

D7 D6

D8

Address 4

D11 D10 D9

Address 3

D15 to D12

Address 2

D19 to D16

KD3

KD4

KD5

KD6

KD7

0

0

0

0

KD3

KD4

KD5

KD6

KD7

1

0

0

0

KD3

KD4

KD5

KD6

KD7

0

1

0

0

KD3

KD4

KD5

KD6

KD7

1

1

0

0

KD3

KD4

KD5

KD6

KD7

0

0

1

0

KD3

KD4

KD5

KD6

KD7

1

0

1

0

KD3

KD4

KD5

KD6

KD7

0

1

1

0

KD3

KD4

KD5

KD6

KD7

1

1

1

0

KD3

KD4

KD5

KD6

KD7

0

0

0

1

0 0 0 0SELECT

0 1 0 0

KD3

KD4

KD5

KD6

KD7

1

0

0

1

KD3

KD4

KD5

KD6

KD7

0

1

0

1

KD3

KD4

KD5

KD6

KD7

1

1

0

1

KD3

KD4

KD5

KD6

KD7

0

0

1

1

KD3

KD4

KD5

KD6

KD7

1

0

1

1

KD3

KD4

KD5

KD6

KD7

0

1

1

1

KD3

KD4

KD5

KD6

KD7

1

1

1

1

Address 1

D23 to D20

Command

Command Table ($340X)

Register

0 0 1 1

3

– 18 –

Data 2

KRAM DATA (K10)

FOCUS PHASE COMPENSATE FILTER B

KRAM DATA (K11)

FOCUS OUTPUT GAIN

KRAM DATA (K12)

ANTI SHOCK INPUT GAIN

KRAM DATA (K13)

FOCUS AUTO GAIN

KRAM DATA (K14)

D0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

HPTZC / AUTO GAIN HIGH PASS FILTER A

KRAM DATA (K15)

HPTZC / AUTO GAIN HIGH PASS FILTER B

KRAM DATA (K16)

ANTI SHOCK HIGH PASS FILTER A

KRAM DATA (K17)

HPTZC / AUTO GAIN LOW PASS FILTER B

KRAM DATA (K18)

FIX

KRAM DATA (K19)

TRACKING INPUT GAIN

KRAM DATA (K1A)

KD0

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

KD2

TRACKING HIGH CUT FILTER A

KRAM DATA (K1B)

TRACKING HIGH CUT FILTER B

KRAM DATA (K1C)

TRACKING LOW BOOST FILTER A-H

KRAM DATA (K1D)

TRACKING LOW BOOST FILTER A-L

KRAM DATA (K1E)

TRACKING LOW BOOST FILTER B-H

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

CXD2548R

KRAM DATA (K1F)

TRACKING LOW BOOST FILTER B-L

KD0

KD1

KD2

D3 D2 D1

D4

Data 1

D7 D6 D5

D8

Address 4

D11 D10 D9

Address 3

D15 to D12

Address 2

D19 to D16

KD3

KD4

KD5

KD6

KD7

0

0

0

0

KD3

KD4

KD5

KD6

KD7

1

0

0

0

KD3

KD4

KD5

KD6

KD7

0

1

0

0

KD3

KD4

KD5

KD6

KD7

1

1

0

0

KD3

KD4

KD5

KD6

KD7

0

0

1

0

KD3

KD4

KD5

KD6

KD7

1

0

1

0

KD3

KD4

KD5

KD6

KD7

0

1

1

0

KD3

KD4

KD5

KD6

KD7

1

1

1

0

KD3

KD4

KD5

KD6

KD7

0

0

0

1

0 0 0 1SELECT

0 1 0 0

KD3

KD4

KD5

KD6

KD7

1

0

0

1

KD3

KD4

KD5

KD6

KD7

0

1

0

1

KD3

KD4

KD5

KD6

KD7

1

1

0

1

KD3

KD4

KD5

KD6

KD7

0

0

1

1

KD3

KD4

KD5

KD6

KD7

1

0

1

1

KD3

KD4

KD5

KD6

KD7

0

1

1

1

KD3

KD4

KD5

KD6

KD7

1

1

1

1

Address 1

D23 to D20

Command

Command Table ($341X)

Register

0 0 1 1

3

– 19 –

Data 2

KRAM DATA (K20)

TRACKING PHASE COMPENSATE FILTER A

KRAM DATA (K21)

TRACKING PHASE COMPENSATE FILTER B

KRAM DATA (K22)

TRACKING OUTPUT GAIN

KRAM DATA (K23)

TRACKING AUTO GAIN

KRAM DATA (K24)

FOCUS GAIN DOWN HIGH CUT FILTER A

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

D2 D1 D0

KD2

KD2

KD2

KD2

KD2

KRAM DATA (K25)

FOCUS GAIN DOWN HIGH CUT FILTER B

KRAM DATA (K26)

FOCUS GAIN DOWN LOW BOOST FILTER A-H

KRAM DATA (K27)

FOCUS GAIN DOWN LOW BOOST FILTER A-L

KRAM DATA (K28)

FOCUS GAIN DOWN LOW BOOST FILTER B-H

KRAM DATA (K29)

FOCUS GAIN DOWN LOW BOOST FILTER B-L

KRAM DATA (K2A)

FOCUS GAIN DOWN PHASE COMPENSATE FILTER A

KD0

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

KD2

CXD2548R

KRAM DATA (K2B)

FOCUS GAIN DOWN DEFECT HOLD GAIN

KRAM DATA (K2C)

FOCUS GAIN DOWN PHASE COMPENSATE FILTER B

KRAM DATA (K2D)

FOCUS GAIN DOWN OUTPUT GAIN

KRAM DATA (K2E)

NOT USED

KRAM DATA (K2F)

NOT USED

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

D3

D5 D4

Data 1

D7 D6

D9 D8

Address 4

D11 D10

Address 3

D15 to D12

Address 2

D19 to D16

KD3

KD4

KD5

KD6

KD7

0

0

0

0

KD3

KD4

KD5

KD6

KD7

1

0

0

0

KD3

KD4

KD5

KD6

KD7

0

1

0

0

KD3

KD4

KD5

KD6

KD7

1

1

0

0

KD3

KD4

KD5

KD6

KD7

0

0

1

0

KD3

KD4

KD5

KD6

KD7

1

0

1

0

KD3

KD4

KD5

KD6

KD7

0

1

1

0

KD3

KD4

KD5

KD6

KD7

1

1

1

0

KD3

KD4

KD5

KD6

KD7

0

0

0

1

0 0 1 0SELECT

0 1 0 0

KD3

KD4

KD5

KD6

KD7

1

0

0

1

KD3

KD4

KD5

KD6

KD7

0

1

0

1

KD3

KD4

KD5

KD6

KD7

1

1

0

1

KD3

KD4

KD5

KD6

KD7

0

0

1

1

KD3

KD4

KD5

KD6

KD7

1

0

1

1

KD3

KD4

KD5

KD6

KD7

0

1

1

1

KD3

KD4

KD5

KD6

KD7

1

1

1

1

Address 1

D23 to D20

Command

Command Table ($342X)

Register

0 0 1 1

3

– 20 –

Data 2

KRAM DATA (K30)

FIX

KRAM DATA (K31)

KD0

KD1

D2 D1 D0

KD2

ANTI SHOCK LOW PASS FILTER B

KRAM DATA (K32)

NOT USED

KRAM DATA (K33)

ANTI SHOCK HIGH PASS FILTER B-H

KRAM DATA (K34)

ANTI SHOCK HIGH PASS FILTER B-L

KRAM DATA (K35)

ANTI SHOCK FILTER COMPARATE GAIN

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

KRAM DATA (K36)

TRACKING GAIN UP2 HIGH CUT FILTER A

KRAM DATA (K37)

TRACKING GAIN UP2 HIGH CUT FILTER B

KRAM DATA (K38)

TRACKING GAIN UP2 LOW BOOST FILTER A-H

KRAM DATA (K39)

TRACKING GAIN UP2 LOW BOOST FILTER A-L

KRAM DATA (K3A)

TRACKING GAIN UP2 LOW BOOST FILTER B-H

KRAM DATA (K3B)

TRACKING GAIN UP2 LOW BOOST FILTER B-L

KD0

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

KD2

CXD2548R

KRAM DATA (K3C)

TRACKING GAIN UP PHASE COMPENSATE FILTER A

KRAM DATA (K3D)

TRACKING GAIN UP PHASE COMPENSATE FILTER B

KRAM DATA (K3E)

TRACKING GAIN UP OUTPUT GAIN

KRAM DATA (K3F)

NOT USED

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

D3

Data 1

D6 D5 D4

D7

D9 D8

Address 4

D11 D10

Address 3

D15 to D12

Address 2

D19 to D16

KD3

KD4

KD5

KD6

KD7

0

0

0

0

KD3

KD4

KD5

KD6

KD7

1

0

0

0

KD3

KD4

KD5

KD6

KD7

0

1

0

0

KD3

KD4

KD5

KD6

KD7

1

1

0

0

KD3

KD4

KD5

KD6

KD7

0

0

1

0

KD3

KD4

KD5

KD6

KD7

1

0

1

0

KD3

KD4

KD5

KD6

KD7

0

1

1

0

KD3

KD4

KD5

KD6

KD7

1

1

1

0

KD3

KD4

KD5

KD6

KD7

0

0

0

1

0 0 1 1SELECT

0 1 0 0

KD3

KD4

KD5

KD6

KD7

1

0

0

1

KD3

KD4

KD5

KD6

KD7

0

1

0

1

KD3

KD4

KD5

KD6

KD7

1

1

0

1

KD3

KD4

KD5

KD6

KD7

0

0

1

1

KD3

KD4

KD5

KD6

KD7

1

0

1

1

KD3

KD4

KD5

KD6

KD7

0

1

1

1

KD3

KD4

KD5

KD6

KD7

1

1

1

1

Address 1

D23 to D20

Command

Command Table ($343X)

Register

0 0 1 1

3

– 21 –

Data 2

KRAM DATA (K40)

TRACKING HOLD FILTER INPUT GAIN

KRAM DATA (K41)

TRACKING HOLD FILTER A-H

KRAM DATA (K42)

TRACKING HOLD FILTER A-L

KRAM DATA (K43)

TRACKING HOLD FILTER B-H

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

D2 D1 D0

KD2

KD2

KD2

KD2

KRAM DATA (K44)

TRACKING HOLD FILTER B-L

KRAM DATA (K45)

TRACKING HOLD FILTER OUTPUT GAIN

KRAM DATA (K46)

NOT USED

KRAM DATA (K47)

NOT USED

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KRAM DATA (K48)

FOCUS HOLD FILTER INPUT GAIN

KRAM DATA (K49)

FOCUS HOLD FILTER A-H

KRAM DATA (K4A)

FOCUS HOLD FILTER A-L

KRAM DATA (K4B)

FOCUS HOLD FILTER B-H

KRAM DATA (K4C)

FOCUS HOLD FILTER B-L

KD0

KD0

KD0

KD0

KD0

KD1

KD1

KD1

KD1

KD1

KD2

KD2

KD2

KD2

KD2

CXD2548R

KRAM DATA (K4D)

FOCUS HOLD FILTER OUTPUT GAIN

KRAM DATA (K4E)

NOT USED

KRAM DATA (K4F)

NOT USED

KD0

KD0

KD0

KD1

KD1

KD1

KD2

KD2

KD2

D3

Data 1

D6 D5 D4

D7

D9 D8

Address 4

D11 D10

Address 3

D15 to D12

Address 2

D19 to D16

KD3

KD4

KD5

KD6

KD7

0

0

0

0

KD3

KD4

KD5

KD6

KD7

1

0

0

0

KD3

KD4

KD5

KD6

KD7

0

1

0

0

KD3

KD4

KD5

KD6

KD7

1

1

0

0

KD3

KD4

KD5

KD6

KD7

0

0

1

0

KD3

KD4

KD5

KD6

KD7

1

0

1

0

KD3

KD4

KD5

KD6

KD7

0

1

1

0

KD3

KD4

KD5

KD6

KD7

1

1

1

0

KD3

KD4

KD5

KD6

KD7

0

0

0

1

0 1 0 0SELECT

0 1 0 0

KD3

KD4

KD5

KD6

KD7

1

0

0

1

KD3

KD4

KD5

KD6

KD7

0

1

0

1

KD3

KD4

KD5

KD6

KD7

1

1

0

1

KD3

KD4

KD5

KD6

KD7

0

0

1

1

KD3

KD4

KD5

KD6

KD7

1

0

1

1

KD3

KD4

KD5

KD6

KD7

0

1

1

1

KD3

KD4

KD5

KD6

KD7

1

1

1

1

Address 1

D23 to D20

Command

Command Table ($344X)

Register

0 0 1 1

3

– 22 –

FOCUS BIAS LIMIT

FOCUS BIAS DATA

TRVSC DATA

FOCUS SEARCH SPEED/

VOLTAGE/AUTO GAIN

DTZC/TRACK JUMP

VOLTAGE/AUTO GAIN

FZSL/SLED MOVE/

Voltage/AUTO GAIN

LEVEL/AUTO GAIN/

DFSW/ (Initialize)

SERIAL DATA READ

MODE/SELECT

FOCUS BIAS

Operation for MIRR/

DFCT/FOK

CXD2548R

TZC for COUT SLCT

HPTZC (Default)

TZC for COUT SLCT

DTZC

Filter

—: Don’t care

Others

Data 3

D2 D1 D0

D3

D5 D4

Data 2

D7 D6

Data 1

D9 D8

D11 D10

D12

Address

D16 D15 D14 D13

—

FBL1

FBL2

FBL3

FBL4

FBL5

FBL6

FBL7

FBL8

FBL9

0

1

1

1

1

1

0

—

FB1

FB2

FB3

FB4

FB5

FB6

FB7

FB8

FB9

1

0

1

1

1

1

0

TV0

TV1

TV2

TV3

TV4

TV5

TV6

TV7

TV8

TV9

0

0

1

1

1

1

0

Data 4

Data 3

Data 2

Data 1

D2 D1 D0

D3

D5 D4

D7 D6

D9 D8

D11 D10

D12

D15 D14 D13

D16

FG0

FG1

FG2

FG3

FG4

FG5

FG6

FTZ

FS0

FS1

FS2

FS3

FS4

FS5

FT0

FT1

1

TG0

TG1

TG2

TG3

TG4

TG5

TG6

SFJP

TJ0

TJ1

TJ2

TJ3

TJ4

TJ5

DTZC

0

0

AGHT

AGHS

AGV2

AGV1

AGGT

AGGF

AGJ

AGS

SM0

SM1

SM2

SM3

SM4

SM5

FZSL

FZSH

1

TLC0

TLC1

TLC2

FLC1

TCLM

TBLM

LKSW

DFSW

AGT

AGF

RFLC

RFLM

FLC0

FLM

VCLC

VCLM

0

0

0

0

0

0

0

0

0

SD0

SD1

SD2

SD3

SD4

SD5

SD6

DAC

1

MTI0

INBK

SJHD

CEIT

TPS0

TPS1

FPS0

FPS1

TJD0

0

FBV0

FBV1

FBUP

FBSS

FBON

0

0

0

0

0

RINT

D1V1

D1V2

D2V1

D2V2

BTF

SFOX

MAX1

MAX2

SDF1

SDF2

SFO1

SFO2

1

Data 4

Data 3

Data 2

Data 1

D2 D1 D0

D3

D5 D4

D7 D6

D9 D8

D11 D10

D12

D15 D14 D13

D16

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

Data 4

—

—

—

—

Data 3

—

—

—

—

Data 2

—

—

—

—

Data 1

—

—

1

D2 D1 D0

D3

D5 D4

D7 D6

D9 D8

D11 D10

D12

D15 D14 D13

D16

XT1D

MIRI

0

0

0

RFLP

TLCD

DFIS

T3UM

T3NM

T1UM

T1NM

F3DM

F3NM

F1DM

F1NM

0

COT2

AGHF

0

SRO1

LPAS

0

ASFG

0

DRR0

DRR1

DRR2

0

XT2D

XT4D

AGG4

0

1

0

0

0

1

1

1

0

0

0

Address

D23 to D20 D19 D18 D17

Command

Command Table ($34FX to 3FX)

Register

0 0 1 1

D23 to D20 D19 D18 D17

0

1

1

0

0

1

1

1

1

1

0

0

0

0

0

0

0

1

1

1

1

Address

0 0 1 1

SELECT

3

D23 to D20 D19 D18 D17

0

1

1

0

1

1

0 0 1 1

Address

D23 to D20 D19 D18 D17

1

1

1

1

1

1

0 0 1 1

– 23 –

CXD2548R

Data 6

Data 5

Data 4

Data 3

Data 2

Data 1

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

D14 D13 D12

D15

D17 D16

D19 D18

D21 D20

D23 D22

D24

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

AS0

AS1

AS2

AS3

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0.02ms

0.05ms

0.05ms

0.09ms

0.09ms

0.18ms

0.18ms

0.36ms

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1.45ms

2.9ms

5.8ms

11.6ms

0

—

—

—

—

—

—

—

—

1

2

4

8

16

32

64

128

256

512

1024

2048

4096

8192

16384

32768

1

—

—

—

—

—

—

—

—

0

1

0

0

KSL0

KSL1

KSL2

KSL3

VCO

SEL2

SOCT

0

VCO

SEL1

WSEL

DOUT

ON/OFF

Mute

DOUT

CDROM

0

—

—

—

—

—

—

—

—

—

—

ZMUT

ZDPL

CKOSL0

CKOSL1

MCSL

0

0

0

0

0

0

0

DSPB

ON/OFF

0

1

0

0

0

FMUT

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

0

SMUT

EMPH

OPSL

0

0

ATT

Mute

0

0

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

CPUSR

SL0

SL1

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Gain

Gain

Gain

Gain

0

MDS0

MDS1

MDP0

MDP1

—

—

—

—

—

—

—

—

—

—

—

—

VP0

VP1

VP2

VP3

VP4

VP5

VP6

VP7

Gain

CLVS

TP

TB

DCLV

PWM MD

1

—

—

—

—

—

—

—

—

0

FCSW

Gain

Gain

VPON

LPWR

HIFC

VC2C

SFSL

ICAP

SPDC

EPWM

CM0

CM1

CM2

CM3

0

—: Don’t care

CAV0

CAV1

0

0

1

Address

D27 D26 D25

Command

Register

Command Table ($4X to EX)

name

1

0

0

Auto sequence

Blind (A, E),

Overflow (C)

4

5

1

1

0

Brake (B)

Kick (D)

6

1

0

1

0

0

1

Auto sequence

(N) track jump

count

Mode

specification

7

8

0

0

1

Function

specification

9

– 24 –

1

0

1

Audio CTRL

A

1

0

1

Serial bus

CTRL

B

0

0

1

1

1

1

Spindle servo

coefficient

setting

CLV CTRL

C

D

1

1

1

CLV MODE

E

FOCUS SERVO OFF,

0V OUT

TRACKING GAIN UP

FILTER SELECT 1

TRACKING SERVO OFF

SLED SERVO OFF

SLED KICK LEVEL

(±1 × basic value) (Default)

KRAM DATA

CXD2548R

—: Don’t care

($3400XX to $344fXX)

Data 5

Data 4

Data 3

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

D3 D2 D0 D0

D6 D5 D4

D7

D10 D9 D8

D11

—

— — —

— — — —

— — —

Data 2

D3 D2 D0 D0

Data 1

D6 D5 D4

D7

Address 3

D10 D9 D8

D11

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Data 5

—

—

—

—

Data 4

—

—

—

—

Data 3

—

—

—

—

D13 D12

Data 2

D15 D14

D17 D16

Data 1

D19 D18

Address

D23 to D20

Command

FOCUS

§1-3. CPU Command Presets

Register

Command Preset Table ($0X to 34X)

—

—

—

—

—

0

1

0

0

0

0

0

0

0 0 0 0

0 0 0 1

CONTROL

TRACKING

0

1

CONTROL

—

Data 2

—

—

0

Data 1

0

0

0

Address

0 0 1 0

TRACKING

MODE

2

D13 D12

D15 D14

D17 D16

D19 D18

D23 to D20

Command

Register

— — — —

0 0 —

0 0

0 0 1 1

D13 D12

Address 2

D15 D14

D17 D16

Address 1

D23 to D20 D19 D18

3 SELECT

0 0 See "Coefficient ROM Preset Values Table".

0 0 1 1 0 1 0

– 25 –

FOCUS BIAS LIMIT

FOCUS BIAS DATA

TRVSC DATA

FOCUS SEARCH SPEED/

VOLTAGE AUTO GAIN

DTZC/TRACK JUMP

VOLTAGE AUTO GAIN

FZSL/SLED MOVE/

Voltage/AUTO GAIN

LEVEL/AUTO GAIN/

DFSW/ (Initialize)

SERIAL DATA READ

MODE/SELECT

FOCUS BIAS

Operation for MIRR/

DFCT/FOK

CXD2548R

TZC for COUT SLCT

HPTZC (Default)

Filter

—: Don’t care

Others

Data 3

Data 2

Data 1

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

1

Data 4

0

0

0

0

Data 3

0

0

0

0

Data 2

0

0

1

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

1

1

0

1

1

1

0

0

1

1

1

1

0

0

0

0

0

1

0

0

0

0

1

0

0

1

0

1

1

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Data 4

0

0

1

0

Data 3

1

0

0

0

Data 2

0

0

0

D3 D2 D1 D0

D6 D5 D4

D7

D10 D9 D8

D11

— —

Data 4

— — —

—

Data 3

— — —

Data 2

— — — —

1

1

1

1

0

0

1

0

0 0 1 1

1

Data 1

1

1

0

0

1

0

Address

Address 2

D13 D12

1

1

D15 D14

0

0

D17 D16

1

Address 1

Command Preset Table ($34FX to 3FX)

0

D23 to D20 D19 D18

Command

Register

D13 D12

D15 D14

D17 D16

D23 to D20 D19 D18

0

1

0

1

0

1

0

0

0

0

0

0

1

0

1

0

0

0

1

0

0

0

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

0

0

0

0

0

0

1

1

1

1

0 0 1 1

SELECT

3

D13 D12

Data 1

D15 D14

D17 D16

Address

D23 to D20 D19 D18

— — —

1 0 0

1

0 0 1 1

Data 1

Address

D13 D12

D15 D14

D17 D16

D23 to D20 D19 D18

0

0

0

0

1

1

1

0

0

0

1

1

1

1

0 0 1 1

– 26 –

CXD2548R

Data 6

Data 5

Data 4

D2 D1 D0

D3

D6 D5 D4

D7

D9 D8

D11 D10

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

0

0

1

0

0

0

0

0

0

0

—

0

—

0

—

0

—

0

—

0

—

0

—

0

—

0

—

0

—

0

0

0

0

0

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

—

—

—

—: Don’t care

—

—

—

—

—

—

0

0

0

0

0

Data 3

Data 2

Data 1

D13 D12

D15 D14

D16

D19 D18 D17

D20

D23 D22 D21

0

—

—

—

—

—

—

—

0

0

0

0

0

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

0

1

1

1

0

0

1

0

0

1

1

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

—

—

—

—

—

—

—

0

1

0

0

1

1

0

—

0

—

0

—

0

—

1

—

1

—

1

—

0

0

1

0

1

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

D27 D26 D25 D24

name

1

0

4

Address

Command

Register

Command Preset Table ($4X to EX)

1

0

Auto sequence

Blind (A, E),

Overflow (C)

Brake (B)

5

1

0

Kick (D)

6

1

0

Auto sequence

(N) track jump

7

count

0

1

Mode

specification

8

0

1

Function

specification

9

– 27 –

0

1

A

0

1

Audio CTRL

Serial bus

B

Spindle servo

CTRL

1

1

1

1

coefficient

setting

C

D

1

1

CLV CTRL

CLV MODE

E

<Coefficient ROM Preset Values Table (1)>

CXD2548R

ADDRESS

K00

K01

K02

K03

K04

K05

K06

K07

K08

K09

K0A

K0B

K0C

K0D

K0E

K0F

K10

K11

K12

K13

K14

K15

K16

K17

K18

K19

K1A

K1B

K1C

K1D

K1E

K1F

DATA CONTENTS

E0

81

23

7F

6A

10

14

30

7F

46

81

1C

7F

58

82

7F

4E

32

20

30

80

77

80

77

00

F1

7F

3B

81

44

7F

5E

SLED INPUT GAIN

SLED LOW BOOST FILTER A-H

SLED LOW BOOST FILTER A-L

SLED LOW BOOST FILTER B-H

SLED LOW BOOST FILTER B-L

SLED OUTPUT GAIN

FOCUS INPUT GAIN

SLED AUTO GAIN

FOCUS HIGH CUT FILTER A

FOCUS HIGH CUT FILTER B

FOCUS LOW BOOST FILTER A-H

FOCUS LOW BOOST FILTER A-L

FOCUS LOW BOOST FILTER B-H

FOCUS LOW BOOST FILTER B-L

FOCUS PHASE COMPENSATE FILTER A

FOCUS DEFECT HOLD GAIN

FOCUS PHASE COMPENSATE FILTER B

FOCUS OUTPUT GAIN

ANTI SHOCK INPUT GAIN

FOCUS AUTO GAIN

HPTZC / Auto Gain HIGH PASS FILTER A

HPTZC / Auto Gain HIGH PASS FILTER B

ANTI SHOCK HIGH PASS FILTER A

HPTZC / Auto Gain LOW PASS FILTER B

∗

Fix

TRACKING INPUT GAIN

TRACKING HIGH CUT FILTER A

TRACKING HIGH CUT FILTER B

TRACKING LOW BOOST FILTER A-H

TRACKING LOW BOOST FILTER A-L

TRACKING LOW BOOST FILTER B-H

TRACKING LOW BOOST FILTER B-L

K20

K21

K22

K23

K24

K25

K26

K27

K28

K29

K2A

K2B

K2C

K2D

K2E

K2F

82

44

18

30

7F

46

81

3A

7F

66

82

44

4E

1B

00

00

TRACKING PHASE COMPENSATE FILTER A

TRACKING PHASE COMPENSATE FILTER B

TRACKING OUTPUT GAIN

TRACKING AUTO GAIN

FOCUS GAIN DOWN HIGH CUT FILTER A

FOCUS GAIN DOWN HIGH CUT FILTER B

FOCUS GAIN DOWN LOW BOOST FILTER A-H

FOCUS GAIN DOWN LOW BOOST FILTER A-L

FOCUS GAIN DOWN LOW BOOST FILTER B-H

FOCUS GAIN DOWN LOW BOOST FILTER B-L

FOCUS GAIN DOWN PHASE COMPENSATE FILTER A

FOCUS GAIN DOWN DEFECT HOLD GAIN

FOCUS GAIN DOWN PHASE COMPENSATE FILTER B

FOCUS GAIN DOWN OUTPUT GAIN

NOT USED

NOT USED

– 28 –

<Coefficient ROM Preset Values Table (2)>

CXD2548R

ADDRESS

K30

K31

K32

K33

K34

K35

K36

K37

K38

K39

K3A

K3B

K3C

K3D

K3E

K3F

K40

K41

K42

K43

K44

K45

K46

K47

K48

K49

K4A

K4B

K4C

K4D

K4E

K4F

DATA CONTENTS

80

66

00

7F

6E

20

7F

3B

80

44

7F

77

86

0D

57

00

04

7F

7F

79

17

6D

00

00

02

7F

7F

79

17

54

00

00

∗

Fix

ANTI SHOCK LOW PASS FILTER B

NOT USED

ANTI SHOCK HIGH PASS FILTER B-H

ANTI SHOCK HIGH PASS FILTER B-L

ANTI SHOCK FILTER COMPARATE GAIN

TRACKING GAIN UP2 HIGH CUT FILTER A

TRACKING GAIN UP2 HIGH CUT FILTER B

TRACKING GAIN UP2 LOW BOOST FILTER A-H

TRACKING GAIN UP2 LOW BOOST FILTER A-L

TRACKING GAIN UP2 LOW BOOST FILTER B-H

TRACKING GAIN UP2 LOW BOOST FILTER B-L

TRACKING GAIN UP PHASE COMPENSATE FILTER A

TRACKING GAIN UP PHASE COMPENSATE FILTER B

TRACKING GAIN UP OUTPUT GAIN

NOT USED

TRACKING HOLD FILTER INPUT GAIN