CD Digital Signal Processor

For the availability of this product, please contact the sales office.

Description

The CXD2529Q is a digital signal processor LSI for

CD players and is equipped with built-in digital filters,

zero detection circuit, 1-bit DAC, and analog lowpass filter on a single chip.

Features

Digital Signal Processor (DSP) Block

• Playback mode supporting CAV (Constant Angular

Velocity)

–Frame jitter-free

–Allows 0.5 to double-speed continuous playback

–Allows relative rotational velocity readout

–Supports external spindle control

• Wide capture range mode

–Spindle rotational velocity following method

–Supports normal-speed and double-speed playback

• 16K RAM

• EFM data demodulation

• Enhanced EFM frame sync signal protection

• SEC strategy-based error correction

• Subcode demodulation and Sub Q data error detection

• Digital spindle servo

• 16-bit traverse counter

• Asymmetry compensation circuit

• Serial bus-based CPU interface

• Error correction monitor signals, etc. are output

from a new CPU interface.

• Servo auto sequencer

• Digital audio interface output

• Digital peak meter

CXD2529Q

100 pin QFP (Plastic)

Absolute Maximum Ratings

• Supply voltage VDD –0.3 to +7.0 V

• Input voltage VI –0.3 to +7.0 V

(Vss – 0.3V to VDD + 0.3V)

• Output voltage VO –0.3 to +7.0 V

• Storage temperature Tstg –40 to +125 °C

• Supply voltage difference

VSS – AVSS –0.3 to +0.3 V

VDD – AVDD –0.3 to +0.3 V

Note) AVDD includes XVDD, and AVSS includes XVSS.

Recommended Operating Conditions

• Supply voltage VDD 3.4 to 5.25 V

• Operating temperature Topr –20 to +75 °C

Note) The VDD (min.) for the CXD2519Q varies

according to the playback speed selection.

Playback

speed

× 2

CD-DSP block DAC block

VDD (min.) [V]

3.4V 4.5V

Digital Filter, DAC, Analog Low-Pass Filter Block

• DBB (Digital Bass Boost)

• Supports double-speed playback

• Digital de-emphasis

• Digital attenuation function

• Zero detection function

• 8fs oversampling digital filter

• S/N ratio: 100dB or more (master clock: 384fs typ.)

Logical value: 109dB

• THD + N: 0.007% or less (master clock: 384fs typ.)

• Rejection band attenuation: –60dB or more

Applications

CD players

Structure

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

× 1

∗1

× 1

∗1

When the internal operation of the CD-DSP

side is set to double-speed mode and the

crystal oscillation frequency is halved,

normal-speed playback results.

Input/Output Capacitances

• Input pin CI 12 (max.) pF

• Output pin CO 12 (max.) pF

Note) Measurement conditions VDD = VI = 0V

3.4V 3.4V

3.4V

fM = 1MHz

E96651A73

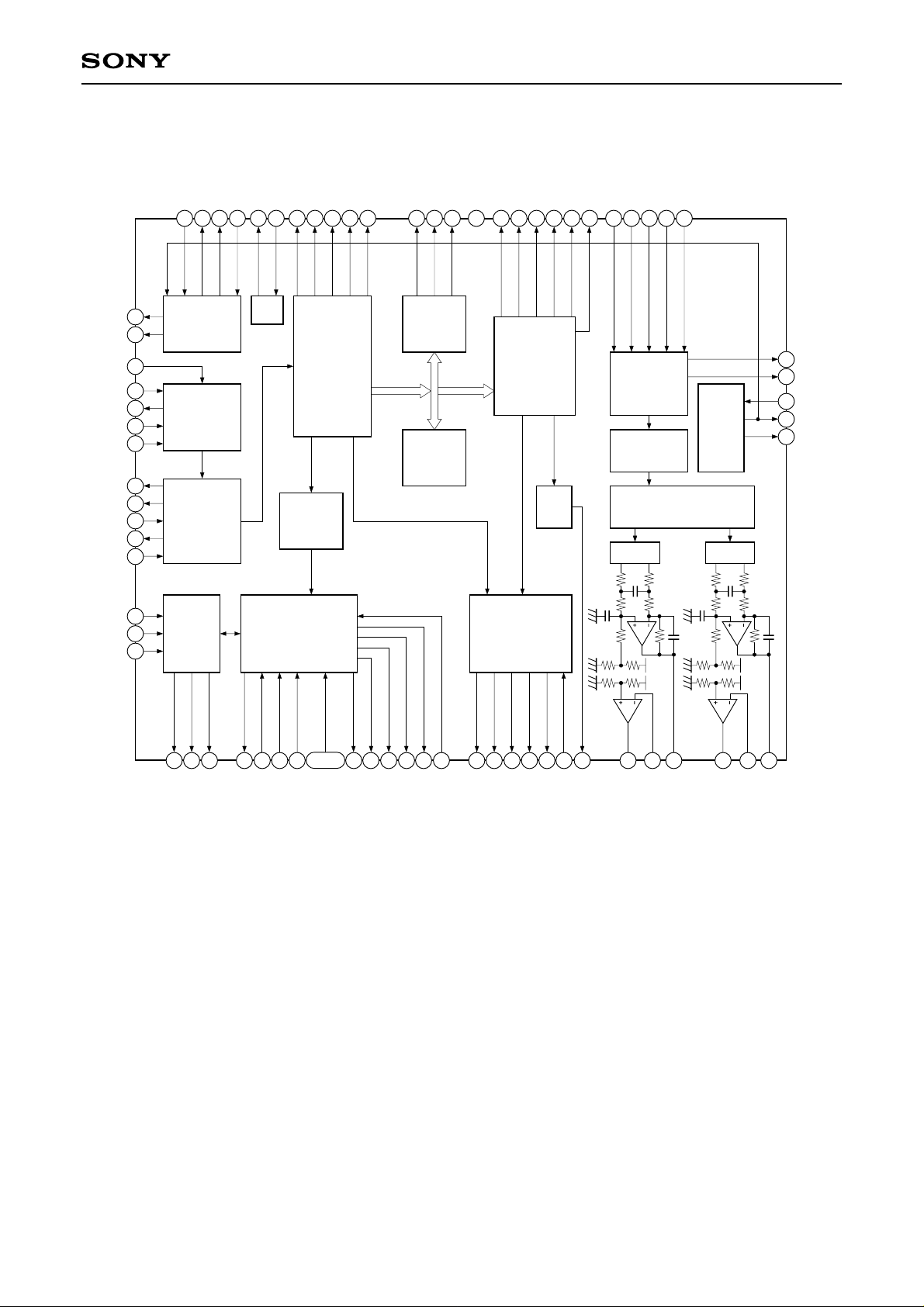

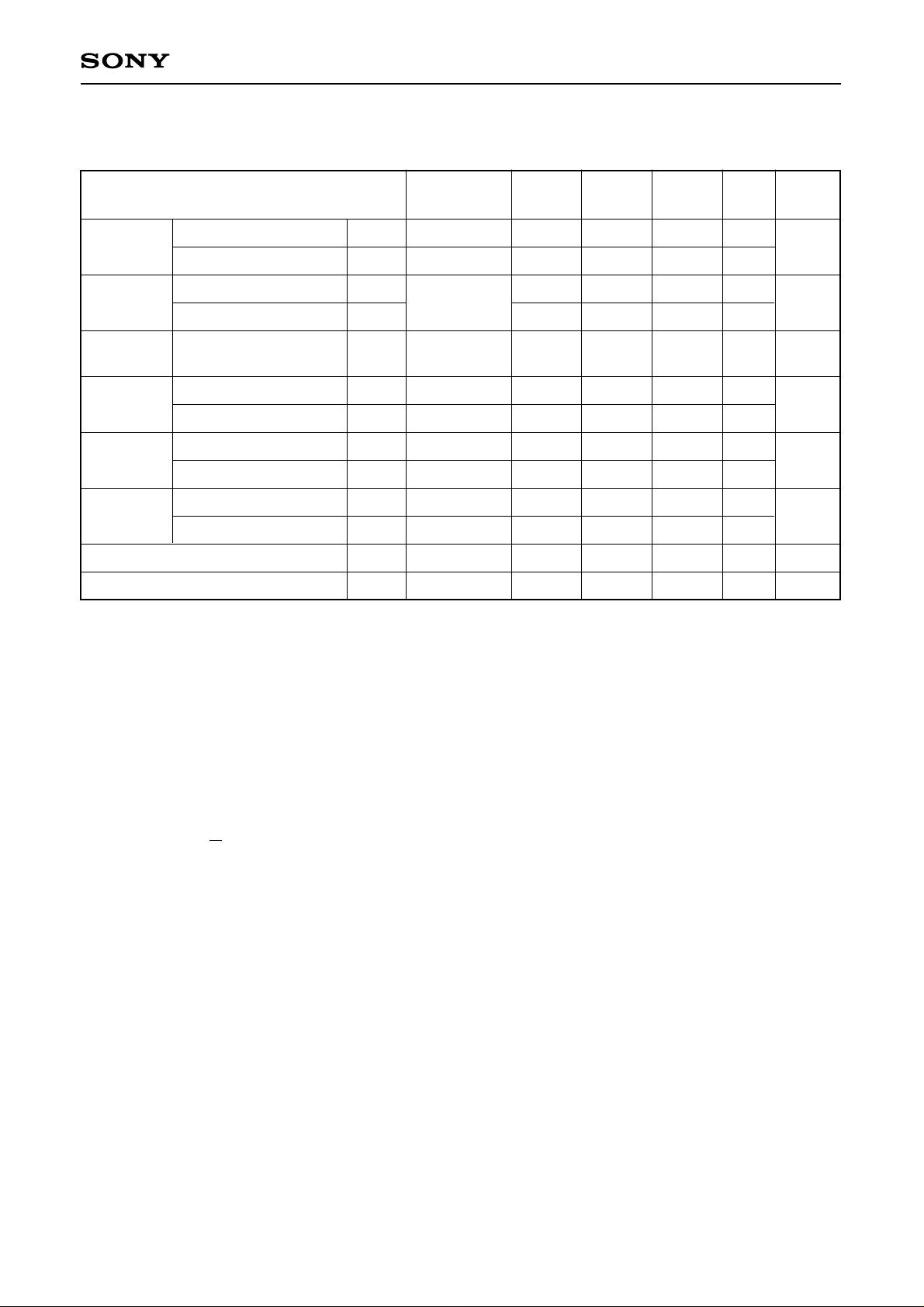

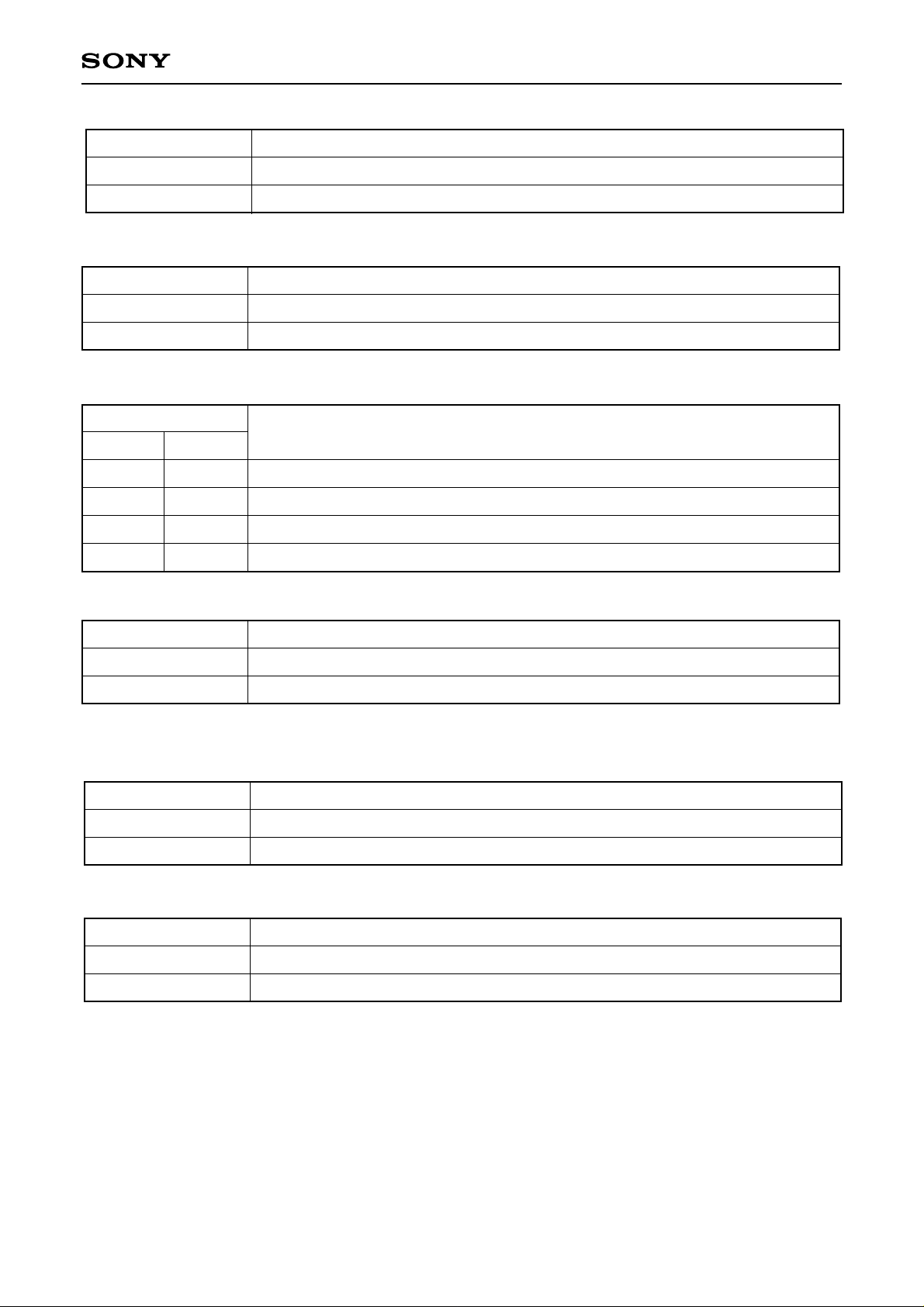

Block Diagram

CXD2529Q

FSTT

C4M

RF

ASYI

ASYO

ASYE

BIAS

XPCK

FILO

FILI

PCO

CLTV

FOK

SEIN

CNIN

VPCO2

VPCO1

XTSL

68

69

70

44

46

47

48

45

60

39

40

38

42

23

13

14

Clock

Generator

Asymmetry

Corrector

Digital

PLL

Servo

Auto

Sequencer

VCKI

35

33

34

36

OSC

V16M

37

GTOP

VCTL

58

Sub Code

Processor

CPU

Interface

demodurator

59

XUGF

61

EFM

GFS

EMPH

72

WFCK

74

MNT1

MNT3

65

66

Error

Corrector

16K

RAM

67

MNT0

31

TES0

62

RFCK

63

Interface

Digital

CLV

C2PO

49

D/A

LRCK

WDCK

50

Digital

OUT

PCMD

52

BCK

54

EMPHI

73

Over Sampling

BCKI

PCMDI

LRCKI

51

Serial-In

Interface

Digital Filter

PWM PWM

55

53

80

3rd-Order

Noise Shaper

SYSM

Timing

Logic

89

90

4

3

6

RMUT

LMUT

XTAI

XTAO

CKOUT

15

16

DATO

17

XLTO

CLKO

9

SENS

10

11

DATA

12

XLAT

18 to 21

CLOK

22

XLON

SPOA to D

75

76

SCOR

77

SBSO

8

EXCK

7

SQSO

SQCK

26

27 28

MON

MDP

29

MDS

64

LOCK

30

XROF

71

PWMI

DOUT

93

LOUT2

94

AIN2

95

AOUT2

86

LOUT1

85

AIN1

84

AOUT1

– 2 –

Pin Configuration

SYSM

80

79

81

NC

82

SS

AV

83

AVDD

AIN1

LOUT1

AV

XV

XTAI

XTAO

XV

AVSS

LOUT2

AIN2

AV

AVSS

NC

NC

XRST

84

85

86

87

SS

88

DD

89

90

91

SS

92

93

94

95

96

DD

97

98

99

100

1

2

DD

V

AOUT1

AOUT2

CXD2529Q

SS

DD

V

V

78

77

4

3

SS

V

LMUT

SBSO

EXCK

76

5

TES2

RMUT

SCOR

75

6

CKOUT

74

WFCK

7

SQCK

EMPHI

73

8

SQSO

72

9

EMPH

DOUT

71

10

SENS

DATA

70

11

C4M

69

12

XLAT

FSTT

68

13

CLOK

XTSL

67

14

SEIN

MNT0

66

15

CNIN

MNT1

65

16

DATO

MNT3

64

17

XLTO

XROF

63

18

CLKO

C2PO

62

19

SPOA

RFCK

61

20

SPOB

GFS

XPCK

60

21

SPOC

SPOD

59

22

XUGF

58

23

XLON

DD

V

GTOP

57

24

DD

V

FOK

SS

V

55

56

26 27 28

25

SS

V

BCKI

54

MON

BCK

53

MDP

PCMD

PCMDI

52

29

MDS

LOCK

51

30

LRCKI

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

PWMI

LRCK

WDCK

ASYE

ASYO

ASYI

BIAS

RF

DD

AV

CLTV

SS

AV

FILI

FILO

PCO

VCTL

V16M

VCKI

VPCO1

VPCO2

TES1

TES0

– 3 –

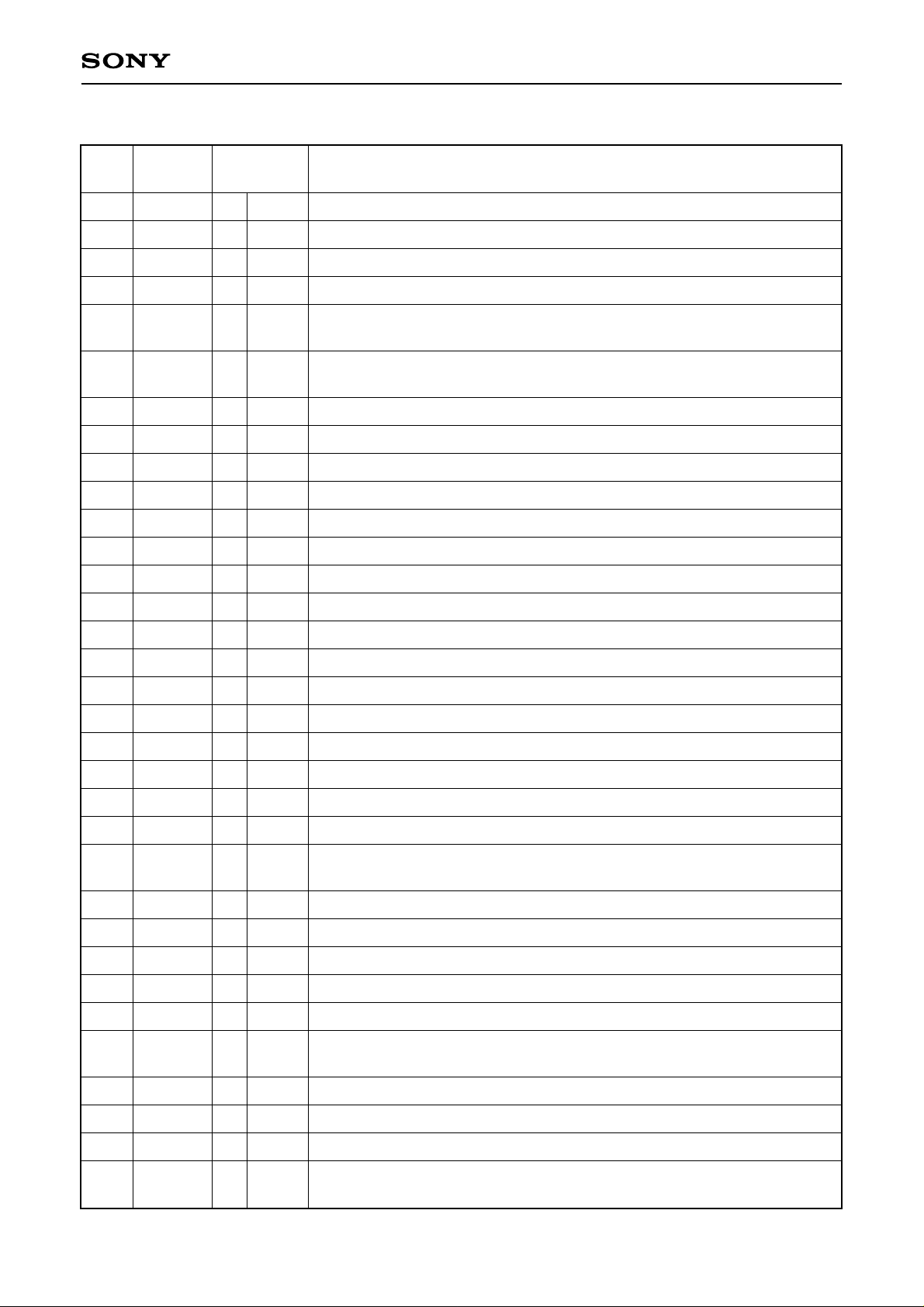

Pin Description

CXD2529Q

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Symbol I/O Description

VDD

VSS

LMUT

RMUT

TES2

CKOUT

SQCK

SQSO

SENS

DATA

XLAT

CLOK

SEIN

CNIN

—

—

O

O

O

O

O

O

—

—

1, 0

1, 0

1, 0

1, 0

I

1, 0

1, 0

I

I

I

I

I

Power supply (+5V).

GND.

Left-channel zero detection flag.

Right-channel zero detection flag.

TEST output pin; normally open.

Master clock frequency-divider output. Selects and outputs XTAI × 1, × 1/2,

× 1/4 or low only.

SQSO readout clock input.

Sub Q 80-bit serial output.

SENS output to CPU.

Serial data input from CPU.

Latch input from CPU. Serial data is latched at the falling edge.

Serial data transfer clock input from CPU.

SENS input from SSP.

Track jump count signal input.

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

DATO

XLTO

CLKO

SPOA

SPOB

SPOC

SPOD

XLON

FOK

VDD

VSS

MON

MDP

MDS

LOCK

O

O

O

O

—

—

O

O

O

O

I

I

I

I

I

1, 0

1, 0

1, 0

1, 0

—

—

1, 0

1, Z, 0

1, Z, 0

1, 0

Serial data output to SSP.

Serial data latch output to SSP. Latched at the falling edge.

Serial data transfer clock output to SSP.

Microcomputer extended interface (input A).

Microcomputer extended interface (input B).

Microcomputer extended interface (input C).

Microcomputer extended interface (input D).

Microcomputer extended interface (output).

Focus OK input.

Used for SENS output and the servo auto sequencer.

Power supply (+5V).

GND.

Spindle motor on/off control output.

Spindle motor servo control.

Spindle motor servo control.

GFS is sampled at 460Hz; when GFS is high, this pin outputs a high signal.

If GFS is low eight consecutive samples, this pin outputs low.

30

31

32

33

PWMI

TES0

TES1

VPCO2

I

I

I

1, Z, 0

O

Spindle motor external control input.

TEST pin; normally GND.

TEST pin; normally GND.

Wide-band EFM PLL charge pump output. Turned on/off by FCSW of

address E.

– 4 –

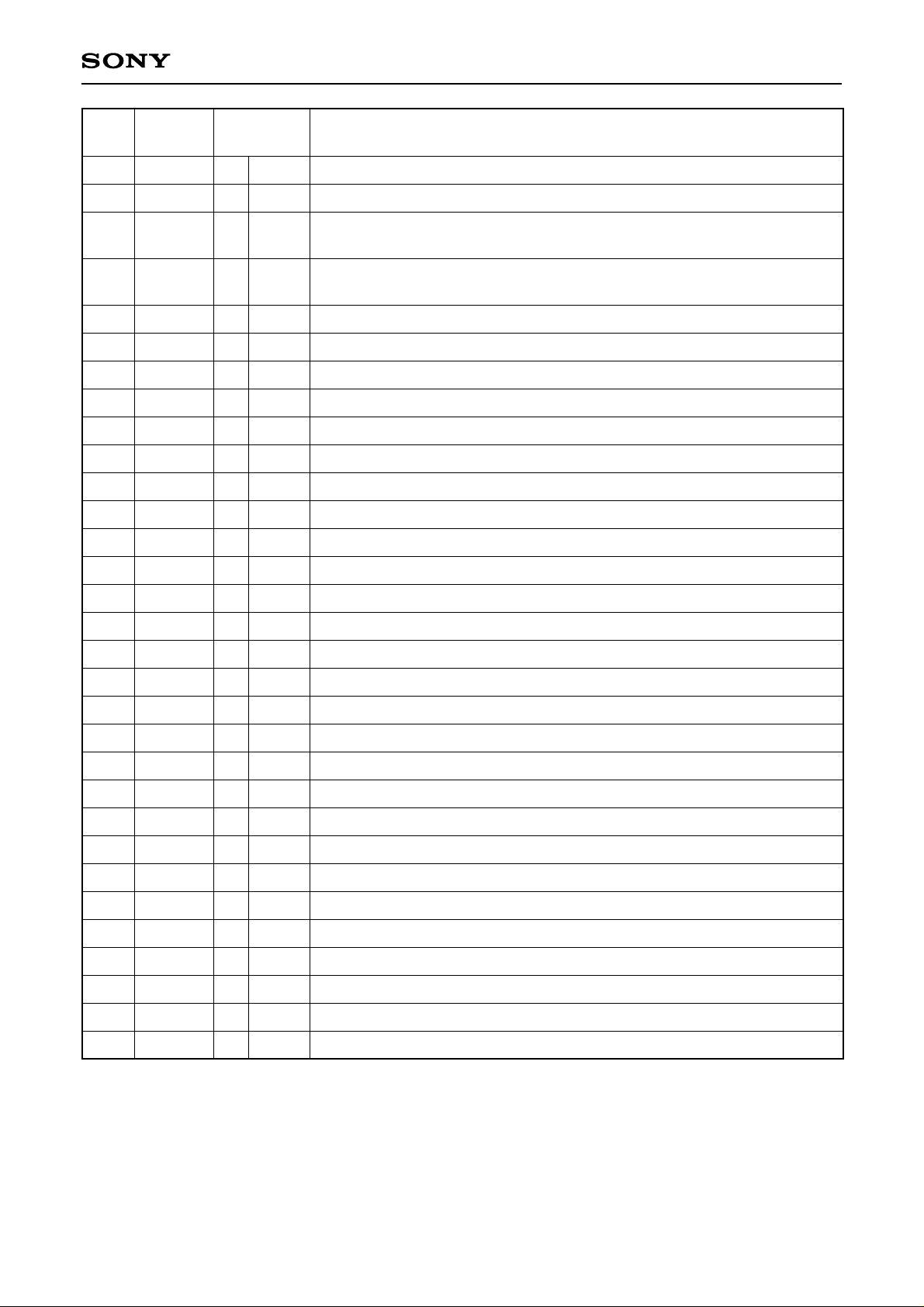

CXD2529Q

Pin

No.

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

Symbol I/O Description

VPCO1

VCKI

V16M

VCTL

PCO

FILO

FILI

AVSS

CLTV

AVDD

RF

BIAS

ASYI

ASYO

ASYE

O

O

O

O

—

—

O

1, Z, 0

I

1, 0

I

1, Z, 0

Analog

I

—

I

—

I

I

I

1, 0

I

Charge pump output for wide-band EFM PLL.

VCO2 oscillation input for the wide-band EFM PLL.

VCO2 oscillation output for the wide-band EFM PLL.

VCO2 control voltage input for the wide-band EFM PLL.

Master PLL charge pump output.

Master PLL (slave = digital PLL) filter output.

Master PLL filter input.

Analog GND.

Master VCO control voltage input.

Analog power supply (+5V).

EFM signal input.

Constant current input of the asymmetry circuit.

Asymmetry comparator voltage input.

EFM full-swing output (low = VSS, high = VDD).

Low: asymmetry circuit off; high: asymmetry circuit on

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

WDCK

LRCK

LRCKI

PCMD

PCMDI

BCK

BCKI

VSS

VDD

GTOP

XUGF

XPCK

GFS

RFCK

C2PO

XROF

MNT3

O

O

O

O

—

—

O

O

O

O

O

O

O

O

1, 0

1, 0

I

1, 0

I

1, 0

I

—

—

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

1, 0

D/A interface. Word clock f = 2fs

D/A interface. LR clock output f = fs

LR clock input.

D/A interface. Serial data output (two’s complement, MSB first).

D/A interface. Serial data input (two’s complement, MSB first).

D/A interface. Bit clock output.

D/A interface. Bit clock input.

GND.

Power supply (+5V).

GTOP output.

XUGF output.

XPLCK output.

GFS output.

RFCK output.

C2PO output.

XRAOF output.

MNT3 output.

66

67

68

69

MNT1

MNT0

XTSL

FSTT

1, 0

O

1, 0

O

I

1, 0

O

MNT1 output.

MNT0 output.

Crystal selector input. Low: 16.9344MHz; high: 33.8688MHz.

2/3 frequency-divider output for Pins 89 and 90.

– 5 –

CXD2529Q

Pin

No.

70

71

72

73

74

75

76

77

78

79

80

81

82

83

Symbol I/O Description

C4M

DOUT

EMPH

EMPHI

WFCK

SCOR

SBSO

EXCK

VSS

VDD

SYSM

O

O

O

O

O

O

—

—

1, 0

1, 0

1, 0

I

1, 0

1, 0

1, 0

I

—

—

I

4.2336MHz output. 1/4 frequency-divided VCKI output in CAV-W mode.

Digital Out output.

Outputs a high signal when the playback disc has emphasis, and a low

signal when there is no emphasis.

Inputs a high signal when de-emphasis is on, and a low signal when de-

emphasis is off.

WFCK output.

Outputs a high signal when either subcode sync S0 or S1 is detected.

Sub P to W serial output.

SBSO readout clock input.

GND.

Power supply (+5V).

Mute input. Active when high.

NC

AVSS

AVDD

—

—

—

—

Analog GND.

Analog power supply (+5V).

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

AOUT1

AIN1

LOUT1

AVSS

XVDD

XTAI

XTAO

XVSS

AVSS

LOUT2

AIN2

AOUT2

AVDD

AVSS

NC

NC

XRST

O

O

—

O

—

O

O

—

—

Left-channel analog output.

I

Left-channel operational amplifier input.

Left-channel LINE output.

—

Analog GND.

Power supply for master clock.

I

Crystal oscillation circuit input. Input the external master clock via this pin.

Crystal oscillation circuit output.

GND for master clock.

—

Analog GND.

Right-channel LINE output.

I

Right-channel operational amplifier input.

Right-channel analog output.

—

—

I

Analog power supply (+5V).

Analog GND.

System reset. Reset when low.

Notes) • PCMD is an MSB first, two’s complement output.

• GTOP is used to monitor the frame sync protection status. (High: sync protection window released.)

• XUGF is the negative pulse for the frame sync derived from the EFM signal. It is the signal before

sync protection.

• XPLCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge of XPLCK

and the EFM signal transition point coincide.

• GFS goes high when the frame sync and the insertion protection timing match.

• RFCK is derived with the crystal accuracy. This signal has a cycle of 136µs (during normal-speed).

• C2PO represents the data error status.

• XRAOF is generated when the 16K RAM exceeds the ±4F jitter margin.

– 6 –

CXD2529Q

Electrical Characteristics

DC Characteristics (VDD = AVDD = 5.0V ± 5%, VSS = AVSS = 0V, Topr = –20 to +75°C)

∗

Item

Input

voltage (1)

Input

voltage (2)

Input

voltage (3)

Output

voltage (1)

Output

voltage (2)

Output

voltage (4)

High level input voltage

Low level input voltage

High level input voltage

Low level input voltage

Input voltage

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

High level output voltage

Low level output voltage

Input leak current

Tri-state pin output leak current

VIH (1)

VIL (1)

VIH (2)

VIL (2)

VIN (3)

VOH (1)

VOL (1)

VOH (2)

VOL (2)

VOH (4)

VOL (4)

ILI

ILO

Conditions Min. Typ. Max. Unit

0.7VDD

0.3VDD

0.8VDD

Schmitt input

0.2VDD

Analog input

IOH = –1mA

IOL = 1mA

IOH = –1mA

IOL = 2mA

IOH = –0.28mA

IOL = 0.36mA

VI = 0 to 5.50V

VO = 0 to 5.50V

Vss

VDD – 0.5

0

VDD – 0.5

0

VDD – 0.5

0

–5

–5

VDD

VDD

0.4

VDD

0.4

VDD

0.4

5

5

V

V

V

V

V

V

V

V

V

V

V

µA

µA

Applicable

pins

∗1

∗2

∗3

∗4

∗5

∗6

∗1, ∗2, ∗3

∗7

Applicable pins

∗1

XTSL, DATA, XLAT, PWMI, SYSM, EMPHI, PCMDI

∗2

CLOK, XRST, EXCK, SQCK, FOK, SEIN, CNIN, VCKI, ASYE, LRCKI, BCKI, SPOA to D

∗3

CLTV, FILI, RF, VCTL, AIN1, AIN2

∗4

MDP, PCO, VPCO1, VPCO2

∗5

ASYO, DOUT, FSTT, C4M, SBSO, SQSO, SCOR, EMPH, MON, LOCK, WDCK, DATO, CLKO, XLTO,

SENS, MDS, MNT0 to 3, WFCK, V16M, CKOUT, LMUT, RMUT, XLON, LRCK, PCMD, BCK, GTOP,

XUGF, XPCK, GFS, RFCK, C2PO, XRAOF

∗6

FILO

∗7

MDS, MDP, PCO, VPCO1, VPCO2

∗

note) : XVDD and XVSS are included for AVDD and AVSS, respectively.

Those are the same for the explanation from the next page.

– 7 –

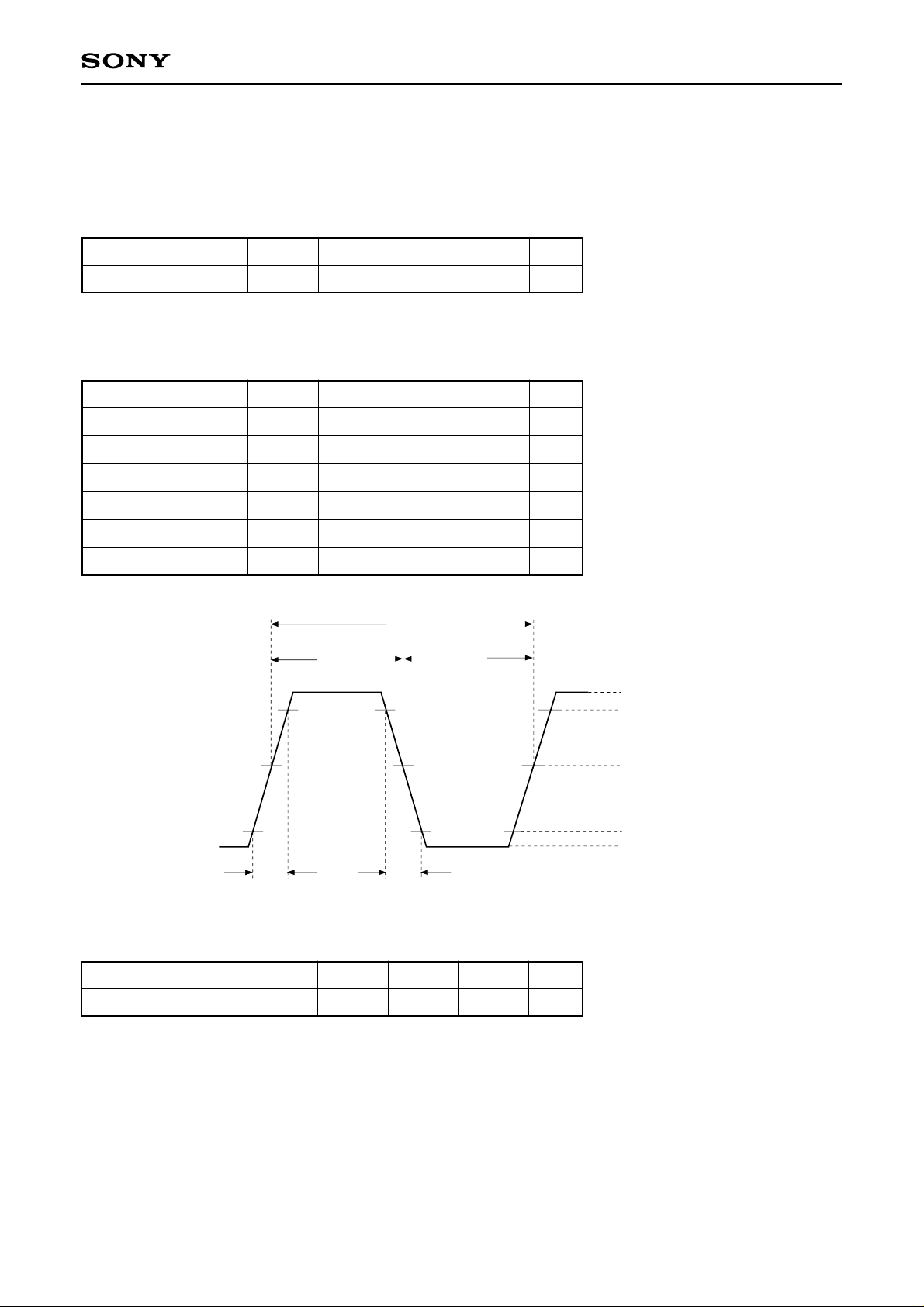

AC Characteristics

1. XTAI pin

(1) When using self-excited oscillation

(Topr = –20 to +75°C, VDD = AVDD = 5.0V ± 5%)

Item Symbol Min. Typ. Max Unit

Oscillation frequency fMAX 15 34 MHz

(2) When inputting pulses to XTAI

(Topr = –20 to +75°C, VDD = AVDD = 5.0V ± 5%)

Item Symbol Min. Typ. Max Unit

CXD2529Q

High level pulse width

Low level pulse width

Pulse cycle

Input high level

Input low level

Rise time, fall time

XTAI

tWHX

tWLX

tCK

VIHX

13

13

26

VDD – 1.0

VILX

tR, tF

tWHX

tR tF

tCK

tWLX

500

500

1,000

0.8

10

ns

ns

ns

V

V

ns

IHX

V

V

IHX × 0.9

VDD/2

VIHX × 0.1

VILX

(3) When inputting sine waves to XTAI via a capacitor

(Topr = –20 to +75°C, VDD = AVDD = 5.0V ± 5%)

Item Symbol Min. Typ. Max Unit

Input amplitude V1 2.0 VDD + 0.3 Vp-p

– 8 –

CXD2529Q

2. CLOK, DATA, XLAT, CNIN, SQCK and EXCK pins (VDD = AVDD = 5.0V ± 5%, VSS = AVSS = 0V, Topr = –20 to +75°C)

Item Symbol Min. Typ. Max. Unit

Clock frequency

Clock pulse width

Setup time

Hold time

Delay time

Latch pulse width

EXCK SQCK frequency

EXCK SQCK pulse width

CLOK

DATA

XLAT

EXCK

CNIN

SQCK

SQSO

SBSO

fCK

tWCK

tSU

tH

tD

tWL

fT

fWT

tSU

tSU

750

300

300

300

750

∗

750

1/fCK

tWCK tWCK

tH

tWT tWT

1/fT

tH

0.65

MHz

ns

ns

ns

ns

ns

∗

0.65

MHz

ns

tD

tWL

∗

In pseudo double-speed playback mode, except when SQSO is Sub Q Read, the maximum operating

frequency for SQCK is 300kHz and the minimum pulse width is 1.5µs.

3. BCKI, LRCKI, PCMDI pins (VDD = AVDD = 5.0V ± 5%, VSS = AVSS = 0V, Topr = –20 to +75°C)

Item Symbol Conditions Typ.

BCK pulse width

DATAL, R setup time

DATAL, R hold time

LRCK setup time

BCKI

PCMDI

tW

tSU

tH

tSU

VDD/2 VDD/2

tSU

(PCMDI)

Min. Max. Unit

94

18

18

18

tW (BCKI) tW (BCKI)

H

t

(PCMDI)

tSU

(LRCKI)

ns

ns

ns

ns

LRCKI

– 9 –

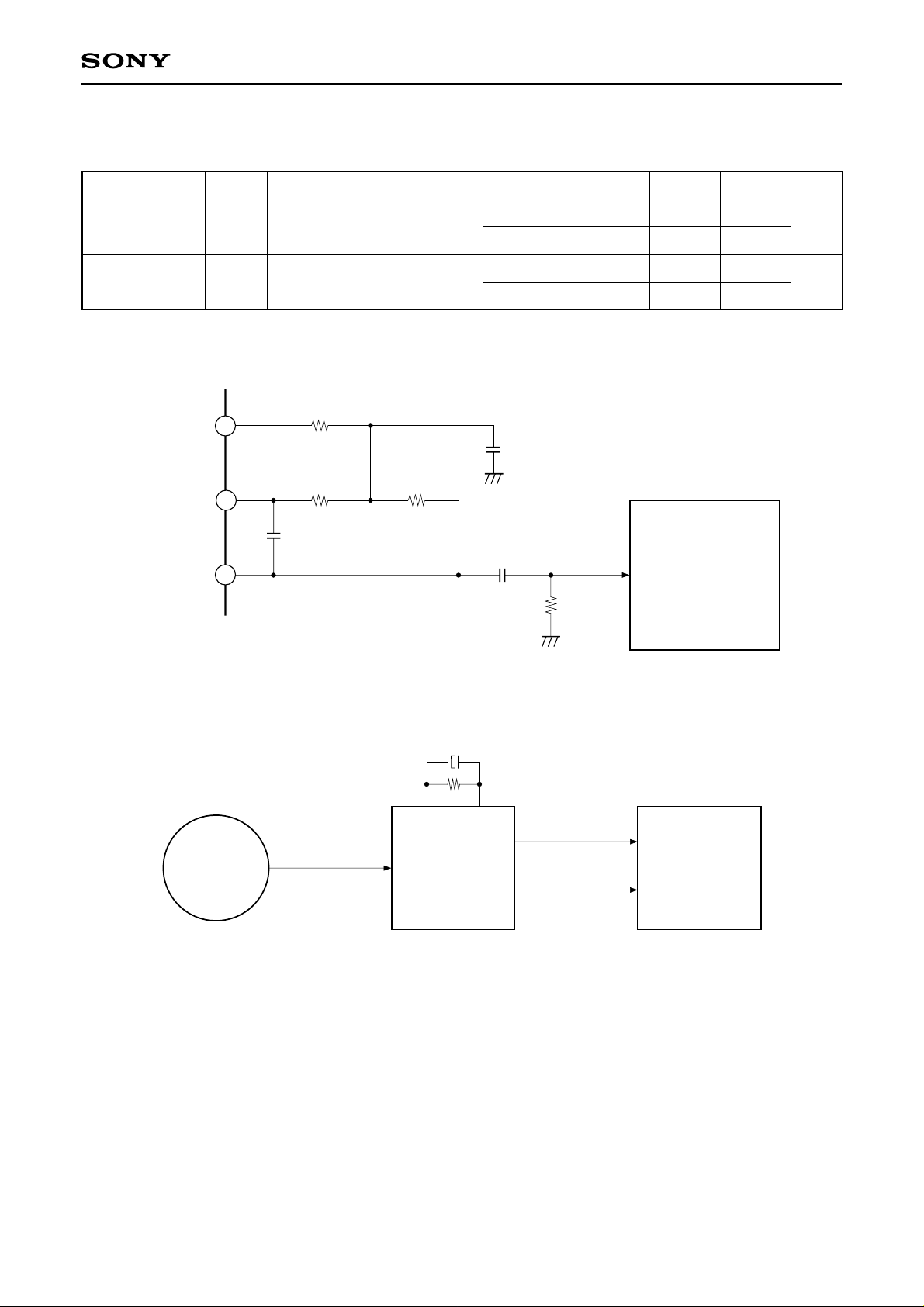

1-bit DAC, LPF Block Analog Characteristics

Analog Characteristics (VDD = AVDD = 5.0V, VSS = AVSS = 0V, Ta = 25°C)

CXD2529Q

Item

Total harmonic

distortion

S/N ratio

Symbol

THD

S/N

Conditions

1kHz, 0dB data

1kHz, 0dB data

(using A-weighting filter)

Crystal

384Fs

768Fs

384Fs

768Fs

Min. Typ. Max. Unit

0.0050

0.0045

96

96

For both items, Fs = 44.1kHz.

The circuits for measuring the total harmonic distortion and S/N ratio are shown below.

150p

12k

12k

12k

680p

SHIBASOKU (AM51A)

22µ

100k

AOUT1 (2)

AIN1 (2)

LOUT1 (2)

0.0070

%

0.0065

100

dB

100

Audio Analyzer

TEST DISC

LPF External Circuit Diagram

768Fs/384Fs

Rch A

DATA RF

CXD2529Q

Lch B

Block Diagram for Measuring Analog Characteristics

Audio Analyzer

– 10 –

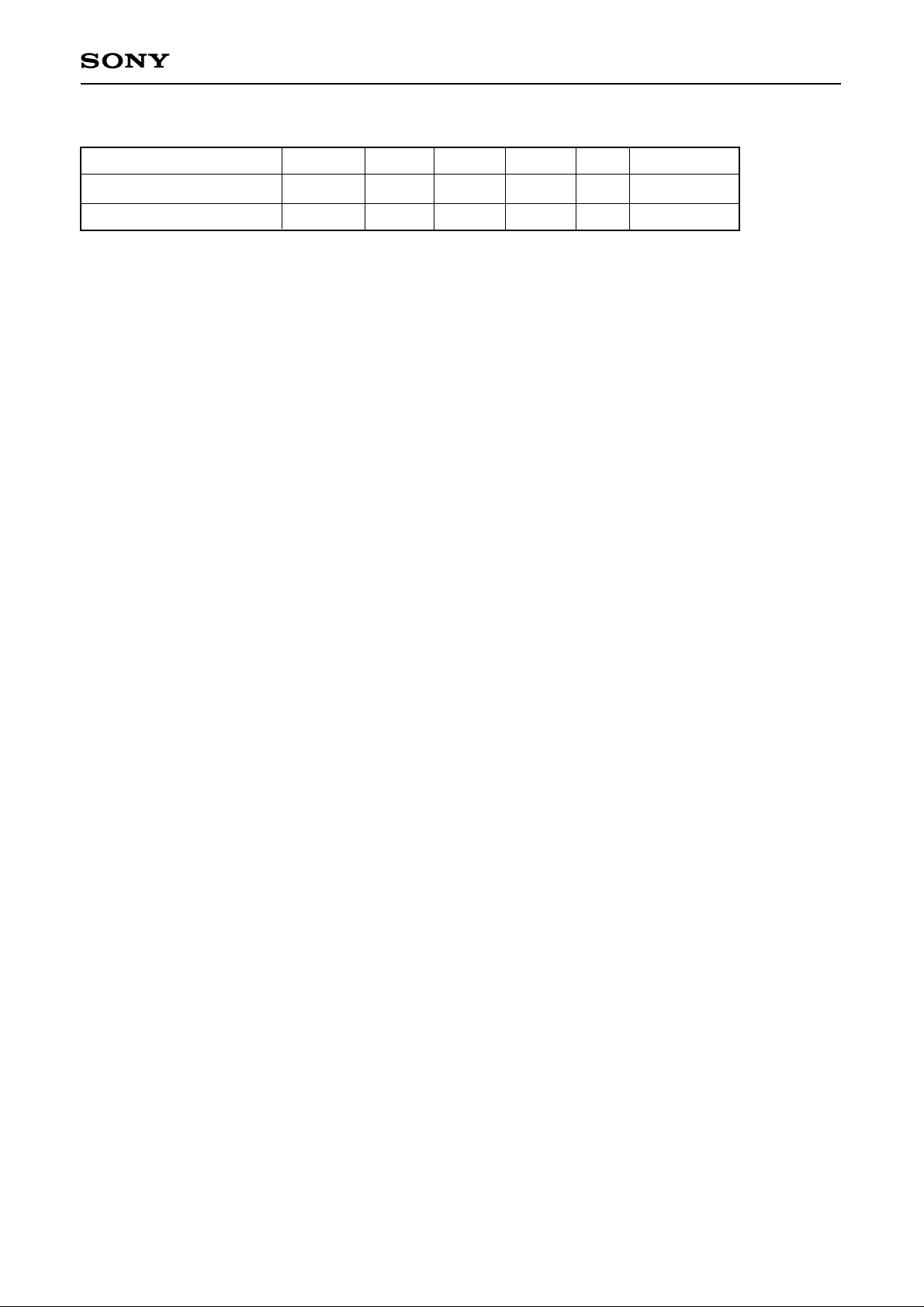

(VDD = AVDD = 5.0V, VSS = AVSS = 0V, Topr = –20 to +75°C)

CXD2529Q

Item Symbol

Output voltage

Load resistance

∗

When the sine wave of 1kHz and 0dB is output and it is measured using the circuit shown on the previous

VOUT

RL

Min.

8

Typ.

1.23

Max.

∗

Vrms

kΩ

Applicable pinsUnit

∗1

∗1

page.

Applicable pins

∗1

LOUT1, LOUT2

– 11 –

Description of Functions

1. CPU Interface and Instructions

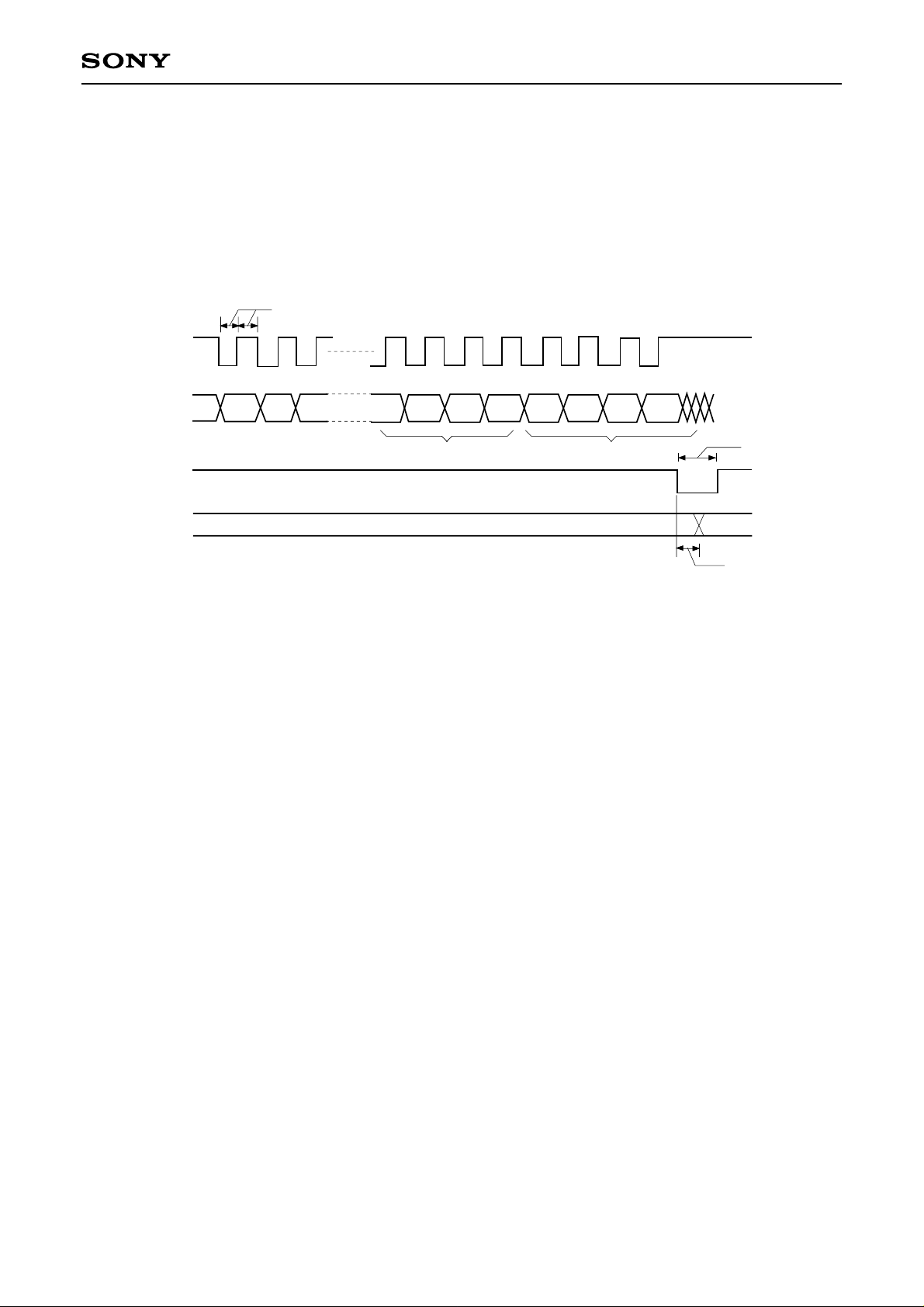

• CPU Interface

This interface uses DATA, CLOK and XLAT to set the modes.

The interface timing chart is shown below.

750ns or more

CLOK

CXD2529Q

DATA

XLAT

Registers 4toE

D1

D2 D3 D0 D1 D2 D3

Data

Address

750ns or more

Valid

300ns max

• Information on each address and the data is provided in Table 1-1.

• The internal registers are initialized by a reset when XRST is low; the initialization data is shown in Table 1-2.

Note) When XLAT is low, SQCK must be set high.

– 12 –

CXD2529Q

D1 D0

Data 6

D3 D2

D1 D0

Data 5

D3 D2

D0

Data 4

D3 D2 D1

D0

Data 3

D3 D2 D1

Data 2

D3 D2 D1 D0

Data 1

D2 D1 D0

D3

D0

D1

Address

D3 D2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

AS0

AS1

AS2

AS3

0

0

1

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0.02ms

0.05ms

0.05ms

0.09ms

0.09ms

0.18ms

0.18ms

0.36ms

1

0

1

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1.45ms

2.9ms

5.8ms

11.6ms

0

1

1

0

—

—

—

—

—

—

—

—

1

2

4

8

16

32

64

128

256

512

1024

2048

4096

8192

16384

32768

1

1

1

0

—

—

—

—

—

—

—

—

0

1

0

0

KSL0

KSL1

KSL2

KSL3

VCO

SEL2

SOCT

0

VCO

SEL1

WSEL

DOUT

ON/OFF

Mute

DOUT

CDROM

0

0

0

1

—

—

—

—

—

—

—

—

0

—

0

—

—

DCOF

0

—

0

—

0

—

ZMUT

ZMUT

ZDPL

ZDPL

CKOSL0

CKOSL0

CKOSL1

CKOSL1

MCSL

MCSL

OPSL10OPSL1

SYCOF

0

0

0

0

0

DSPB

ON/OFF

0

1

0

0

1

1

SYCOF

0

0

0

0

0

DSPB

ON/OFF

0

1

0

0

1

—

BBSL

—

BSBST

—

LRWO

—

FMUT

AD0

AD0

AD1

AD1

AD2

AD2

AD3

AD3

AD4

AD4

AD5

AD5

AD6

AD6

AD7

AD7

AD8

AD8

AD9

AD9

0

0

SMUT

SMUT

EMPH

EMPH

OPSL20OPSL2

0

0

ATT

Mute

0

0

0

1

0

1

1

0

0

ATT

Mute

0

0

0

1

0

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

CPUSR

SL0

SL1

1

1

0

1

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Gain

Gain

Gain

Gain

0

0

1

1

MDS0

MDS1

MDP0

MDP1

—

—

—

—

—

—

—

—

—

—

—

—

VP0

VP1

VP2

VP3

VP4

VP5

VP6

VP7

Gain

CLVS

TP

TB

DCLV

PWM MD

1

0

1

1

—

—

—

—

—

—

—

—

0

FCSW

Gain

Gain

VPON

LPWR

HIFC

VC2C

SFSL

ICAP

SPDC

EPWM

CM0

CM1

CM2

CM3

0

1

1

1

CAV0

CAV1

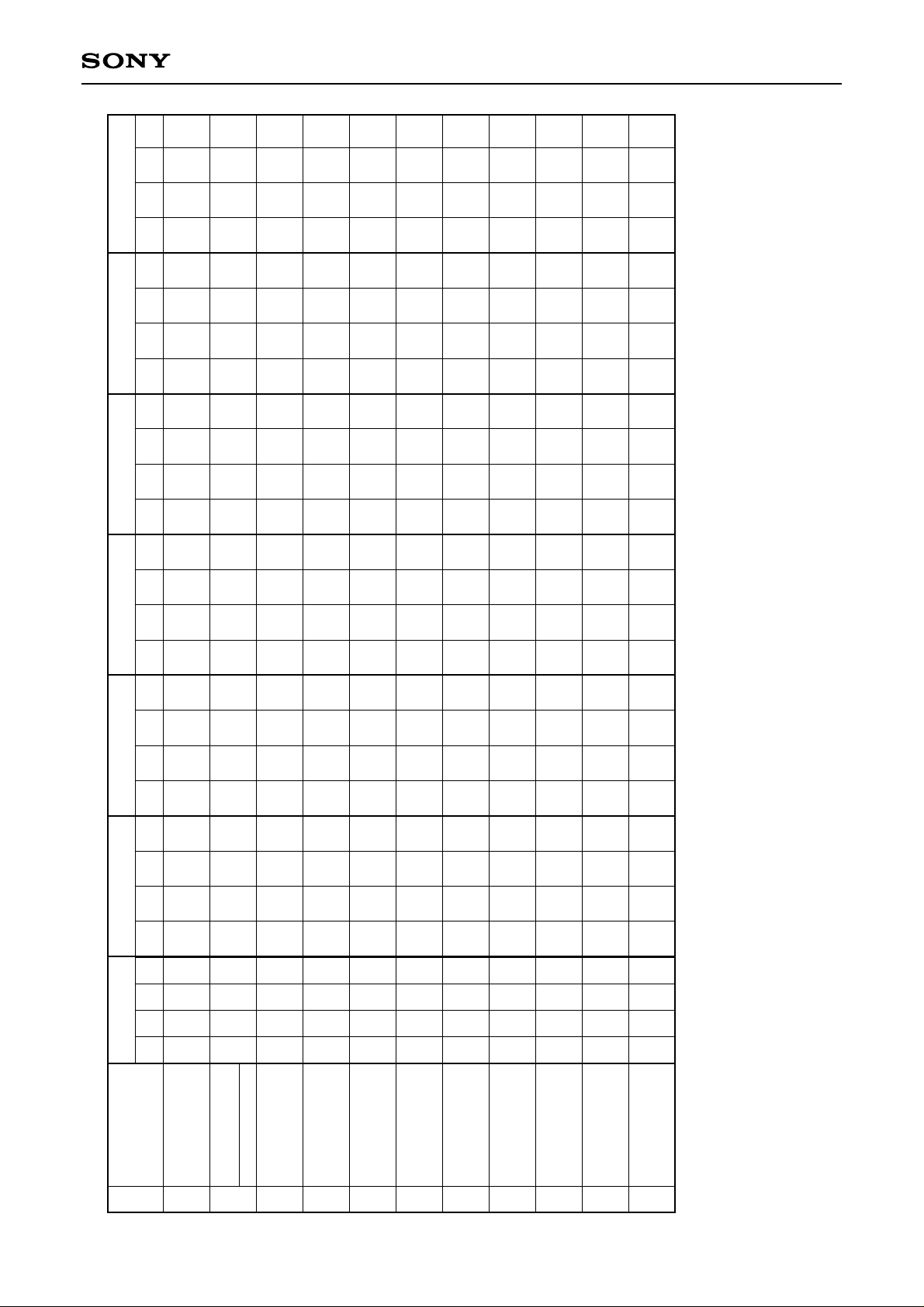

Table 1-1.

Command

Auto

name

Register

Command Table

4

sequence

Blind (A, E),

Overflow (C)

5

Brake (B)

Kick (D)

6

Auto sequence (N)

track jump count

MODE

specification

7

8

Function

specification

9

– 13 –

Audio CTRL

A

Serial bus

CTRL

B

Servo coefficient

setting

CLV CTRL

C

D

CLV mode

E

CXD2529Q

Data 6

Data 5

Data 4

D1 D0

D3 D2

D1 D0

D3 D2

D0

D3 D2 D1

D0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

0

0

1

0

0

0

0

0

0

0

—

0

—

0

—

0

—

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

0

—

0

—

0

—

0

—

0

0

Data 3

D3 D2 D1

Data 2

D3 D2 D1 D0

Data 1

D2 D1 D0

D3

D1 D0

Address

D3 D2

0

—

—

—

—

—

—

—

0

0

0

0

0

0

1

0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

0

1

1

1

0

0

1

0

0

1

1

1

0

0

1

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

1

0

0

1

0

0

1

1

—

—

—

—

—

—

—

0

1

0

0

1

1

0

1

0

—

—

—

—

—

—

—

0

1

1

0

0

0

1

1

0

0

0

0

0

0

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

1

0

0

1

1

1

1

1

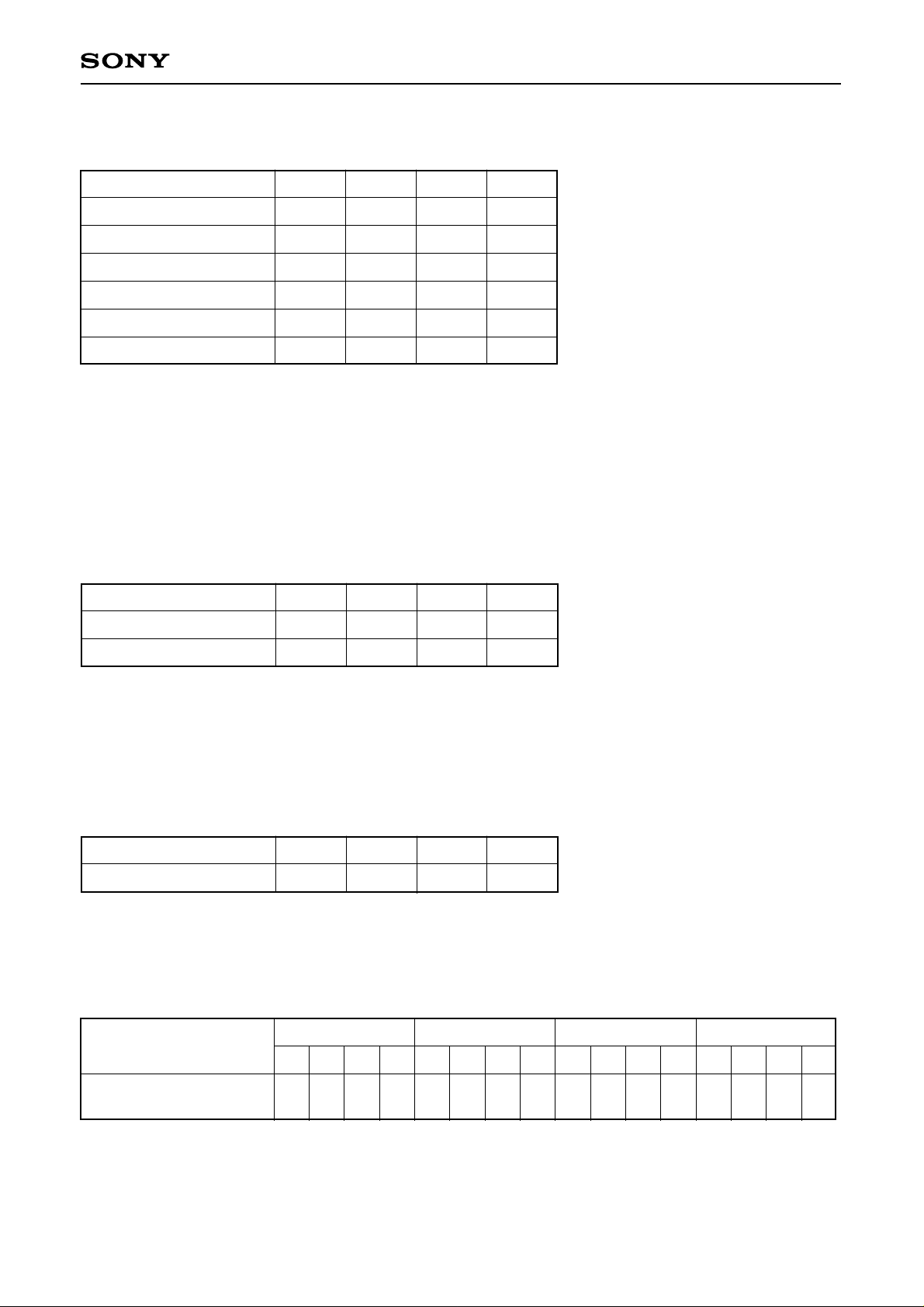

Table 1-2.

Command

Auto

sequence

name

Register

Reset Initialization

4

Blind (A, E),

Overflow (C)

Brake (B)

5

Kick (D)

Auto sequence (N)

track jump count

6

7

MODE

specification

8

Function

specification

9

– 14 –

Audio CTRL

Serial bus

A

B

CTRL

Servo coefficient

setting

C

CLV CTRL

CLV mode

E

D

1-1. The meaning of the data for each address is explained below.

$4X commands

CXD2529Q

Command

CANCEL

FOCUS-ON

1 TRACK JUMP

10 TRACK JUMP

2N TRACK JUMP

N TRACK MOVE

AS3

0

0

1

1

1

1

AS2

0

1

0

0

1

1

AS1

0

1

0

1

0

1

AS0

0

1

RXF

RXF

RXF

RXF

RXF = 0 FORWARD

RXF = 1 REVERSE

• When the Focus-on command ($47) is canceled ($40), $02 is sent and the auto sequence is interrupted.

• When the Track jump/move commands ($48 to $4F) are canceled ($40), $25 is sent and the auto sequence

is interrupted.

$5X commands

Auto sequence timer setting

Setting timers: A, E, C, B

Command

Blind (A, E), Over flow (C)

D3 D2 D1 D0

0.18ms

0.09ms

0.05ms

0.02ms

Brake (B)

0.36ms

0.18ms

Ex.) D2 = D0 = 1, D3 = D1 = 0 (Initial Reset)

A = E = C = 0.11ms

B = 0.23ms

$6X commands

Auto sequence timer setting

Setting timer: D

Command

KICK (D)

D3 D2 D1 D0

11.6ms

5.8ms

Ex.) D3 = 0, D2 = D1 = D0 = 1(Initial Reset)

D = 10.15ms

$7X commands

Auto sequence track jump/move count setting (N)

Data 1 Data 2

Command

D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

Auto sequence track

jump count setting

2152142132122112102928272625242322212

0.09ms

2.9ms

0.05ms

1.45ms

Data 3 Data 4

0

This command is used to set N when a 2N track jump and an N track move are executed for auto sequence.

• The maximum track count is 65,535, but note that with 2N track jumps the maximum track jump count is

determined by the mechanical limitations of the optical system.

• The number of track jump is counted according to the signals input from the CNIN pin.

– 15 –

$8X commands

CXD2529Q

Command

MODE

specification

Command bit

CDROM = 1

CDROM = 0

Data 1 Data 2

D3

CDROM

D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

DOUT

Mute

DOUT

ON/OFF

WSEL

Data 4

D3

D2 D1 D0

0010

C2PO timing

See the Timing

Chart 1-1.

See the Timing

Chart 1-1.

Data 3

VCO

SEL1

0 SOCT

VCO

SEL2

KSL3 KSL2 KSL1 KSL0

See the $BX commands.

Processing

CDROM mode; average value interpolation and pre-value hold

are not performed.

Audio mode; average value interpolation and pre-value hold

are performed.

Command bit

DOUT Mute = 1

DOUT Mute = 0

Digital Out output is muted. (DA output is not muted.)

When no other mute conditions are set, Digital Out output is not muted.

Command bit

DOUT ON/OFF = 1

DOUT ON/OFF = 0

Command bit

WSEL = 1

WSEL = 0

∗1

In normal-speed playback, channel clock = 4.3218MHz.

Digital Out is output from the DOUT pin.

Digital Out is not output from the DOUT pin.

Sync protection window width

±26 channel clock

∗1

±6 channel clock

Processing

Processing

Application

Anti-rolling is enhanced.

Sync window protection is enhanced.

– 16 –

CXD2529Q

Command bit

VCOSEL1

0

0

0

0

1

1

1

1

∗1

Approximately twice the normal speed.

KSL3 KSL2

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Processing

Multiplier PLL VCO1 is set to normal speed, and the output is

1/1 frequency-divided.

Multiplier PLL VCO1 is set to normal speed, and the output is

1/2 frequency-divided.

Multiplier PLL VCO1 is set to normal speed, and the output is

1/4 frequency-divided.

Multiplier PLL VCO1 is set to normal speed, and the output is

1/8 frequency-divided.

Multiplier PLL VCO1 is set to high speed∗1, and the output is

1/1 frequency-divided.

Multiplier PLL VCO1 is set to high speed∗1, and the output is

1/2 frequency-divided.

Multiplier PLL VCO1 is set to high speed∗1, and the output is

1/4 frequency-divided.

Multiplier PLL VCO1 is set to high speed∗1, and the output is

1/8 frequency-divided.

Command bit

VCOSEL2

0

0

0

0

1

1

1

1

∗2

Approximately twice the normal speed.

KSL1 KSL0

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Processing

Wide-band PLL VCO2 is set to normal speed, and the output is

1/1 frequency-divided.

Wide-band PLL VCO2 is set to normal speed, and the output is

1/2 frequency-divided.

Wide-band PLL VCO2 is set to normal speed, and the output is

1/4 frequency-divided.

Wide-band PLL VCO2 is set to normal speed, and the output is

1/8 frequency-divided.

Wide-band PLL VCO2 is set to high speed∗2, and the output is

1/1 frequency-divided.

Wide-band PLL VCO2 is set to high speed∗2, and the output is

1/2 frequency-divided.

Wide-band PLL VCO2 is set to high speed∗2, and the output is

1/4 frequency-divided.

Wide-band PLL VCO2 is set to high speed∗2, and the output is

1/8 frequency-divided.

– 17 –

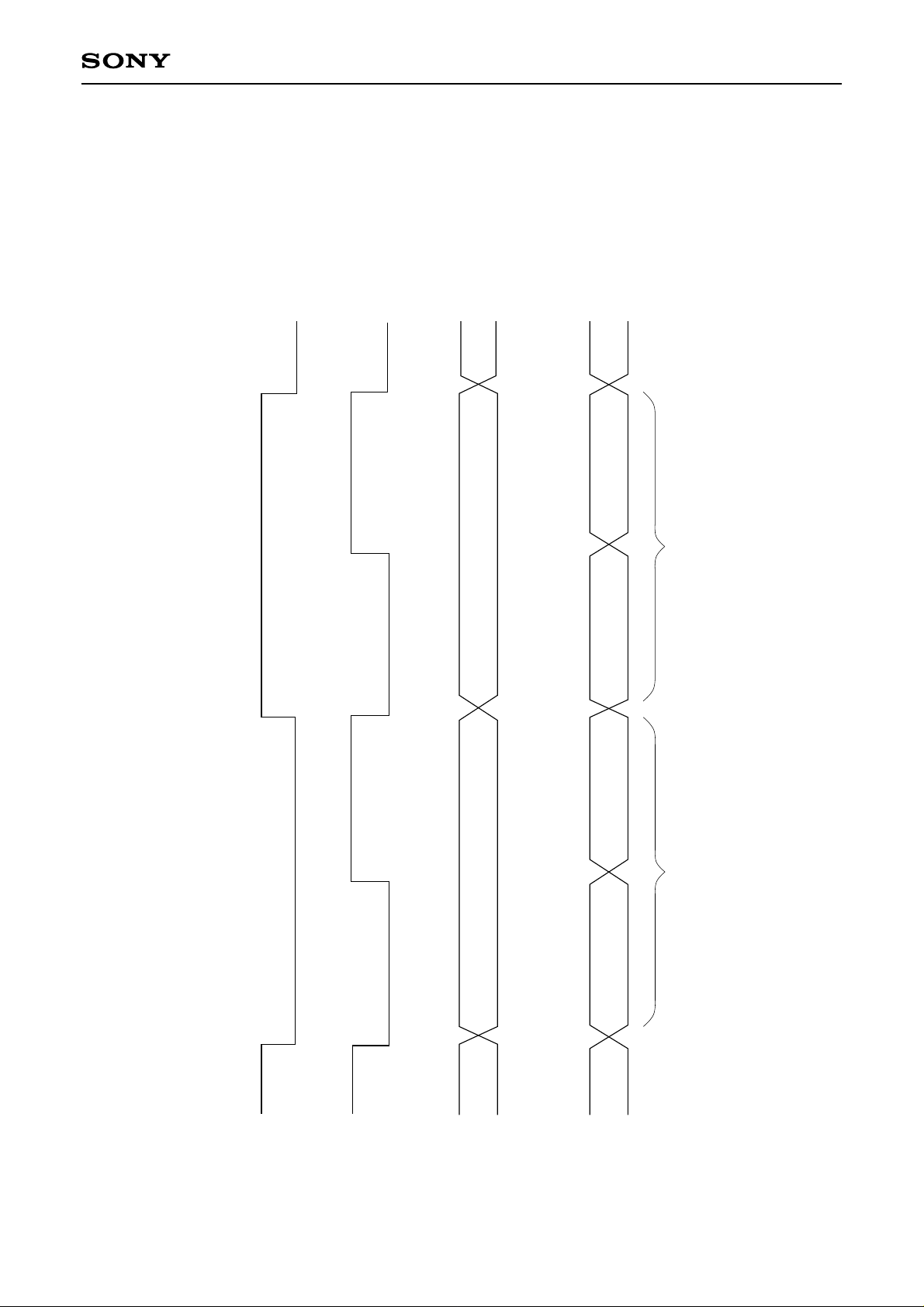

If C2 Pointer = 1,

data is NG

CXD2529Q

Rch 16bit C2 Pointer Lch 16bit C2 Pointer

Lch C2 Pointer

C2 Pointer for upper 8bits C2 Pointer for lower 8bits

Rch C2 Pointer

C2 Pointer for upper 8bits C2 Pointer for lower 8bits

Timing Chart 1-1

LRCK

WDCK

C2PO

CDROM = 0

– 18 –

C2PO

CDROM = 1

CXD2529Q

$9X commands (OPSL1 = 0)

Data 1

Command

D3

Function

specifications

D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

DSPB

0

ON/OFF

$9X commands (OPSL1 = 1)

Data 1

Command

D3

Function

specifications

D2 D1 D0 D3 D2 D1 D0 D3 D2 D1 D0

DSPB

0

ON/OFF

∗

Data 2 D0 and subsequent data are DF/DAC function settings.

Data 3 Data 4Data 2

D3 to D1

0 0 0 MCSL

000

D0

SYCOF

OPSL1

∗

Data 2 D0 and subsequent data are DF/DAC function settings.

Data 3 Data 4Data 2

D3 to D1

0 0 1 MCSL

000

D0

SYCOF

OPSL1

CKOSL1 CKOSL0

CKOSL1 CKOSL0

ZDPL ZMUT — —

Data 5

D3

D2 D1 D0

—

———

ZDPL ZMUT 0 0

Data 5

Command bit

DSPB = 1

DSPB = 0

Double-speed playback (CD-DSP block)

Normal-speed playback (CD-DSP block)

Command bit

SYCOF = 1

SYCOF = 0

∗

Set SYCOF = 0 in advance when setting the $AX command LRWO to 1.

LRCK asynchronous mode

Normal operation

Processing

Processing

D3

D2 D1 D0

0 DCOF 0 0

– 19 –

CXD2529Q

Command bit

OPSL1 = 1

OPSL1 = 0

Command bit

MCSL = 1

MCSL = 0

Command bit

CKOSL1 CKOSL0

0

0

1

1

0

1

0

1

Processing

DCOF can be set.

DCOF cannot be set.

Processing

DF/DAC block master clock selection. Crystal = 768Fs (33.8688MHz)

DF/DAC block master clock selection. Crystal = 384Fs (16.9344MHz)

Processing

The CKOUT pin output is 1/1-frequency divided of the crystal input.

The CKOUT pin output is 1/2-frequency divided of the crystal input.

The CKOUT pin output is 1/4-frequency divided of the crystal input.

The CKOUT pin output is fixed to low.

Command bit

ZDPL = 1

ZDPL = 0

∗

See the description of “Mute Flag Output” for the conditions of the mute flag output.

LMUT and RMUT pins are set to high for mute.

LMUT and RMUT pins are set to low for mute.

Command bit

ZMUT = 1

ZMUT = 0

Zero detection mute is on.

Zero detection mute is off.

Command bit

DCOF = 1

DCOF = 0

∗

DCOF can be set when OPSL is 1.

∗

Set the DC offset to off when the zero detection mute is on.

DC offset is off.

DC offset is on.

Processing

Processing

Processing

– 20 –

Loading...

Loading...