CD Digital Signal Processor

Description

The CXD2500BQ is a digital signal processing LSI

designed for use in compact disc players. It has the

following functions:

• Wide-frame jitter margin (±28 frames) realized by a

built-in 32K RAM.

• Bit clock generated by digital PLL for strobing EFM

signals. Capture range of ±150 kHz and over.

• EFM data demodulation

• Enhanced protection of EFM Frame Sync signals

• Powerful error correction based on Refined Super

Strategy

Error correction C1: Double correction

C2: Quadruple correction

• Double-speed playback and vari-pitch playback

• Reduced noise generation at track jump

• Auto zero-cross muting

• Subcode demodulation and subcode Q data error

detection

• Digital spindle servo system (incorporating an

oversampling filter)

• 16-bit traverse counter

• Built-in asymmetry correction circuit

• CPU interface using a serial bus

• Servo auto sequencer

• Output for digital audio interface

• Built-in digital level meter and peak meter

• Bilingual

CXD2500BQ

80 pin QFP (Plastic)

Features

• All digital signals for regeneration are processed

using one chip.

• The built-in RAM enables high-integration

mounting.

Structure

Silicon-gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

—1—

E91Y46F64-TE

CXD2500BQ

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VCC –0.3 to +7.0 V

• Input voltage VI –0.3 to +7.0 V

• Output voltage VO –0.3 to +7.0 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –40 to +125 °C

• Supply voltage differences VSS–AVSS –0.3 to +0.3 V

VDD–AVDD –0.3 to +0.3 V

Recommended Operating Conditions

• Supply voltage VDD 4.75∗1to 5.25∗3(5.0 V typ.) V

• Operating temperature Topr –20 to +75 °C

• Input voltage VIN VSS–0.3 to + VDD + 0.3 V

∗1

VDD value of 4.75 V (min.) is for the double-speed playback mode at vari-pitch control reset. For the low

power consumption special playback mode, VDD value is 3.6 V (min.). ∗2In the normal-speed playback

mode VDD value is 4.5 V (min.)

∗2

Low power consumption, special playback mode

Set the internal operation of LSI at the double-speed mode, and half the crystal oscillation frequency. This

will result in the normal-speed playback mode.

∗3

VDD value of 5.25 V (max.) is for the double-speed playback mode at vari-pitch control reset. For normalspeed playback and the low power consumption special playback mode, the VDD value is 5.5 V (max.).

I/O Capacity

• Input pins CI 12 pF max.

• Output pins CO 12 pF max. at high impedance

Note: Test Conditions

VDD=VI=0 V

fM=1 MHz

—2—

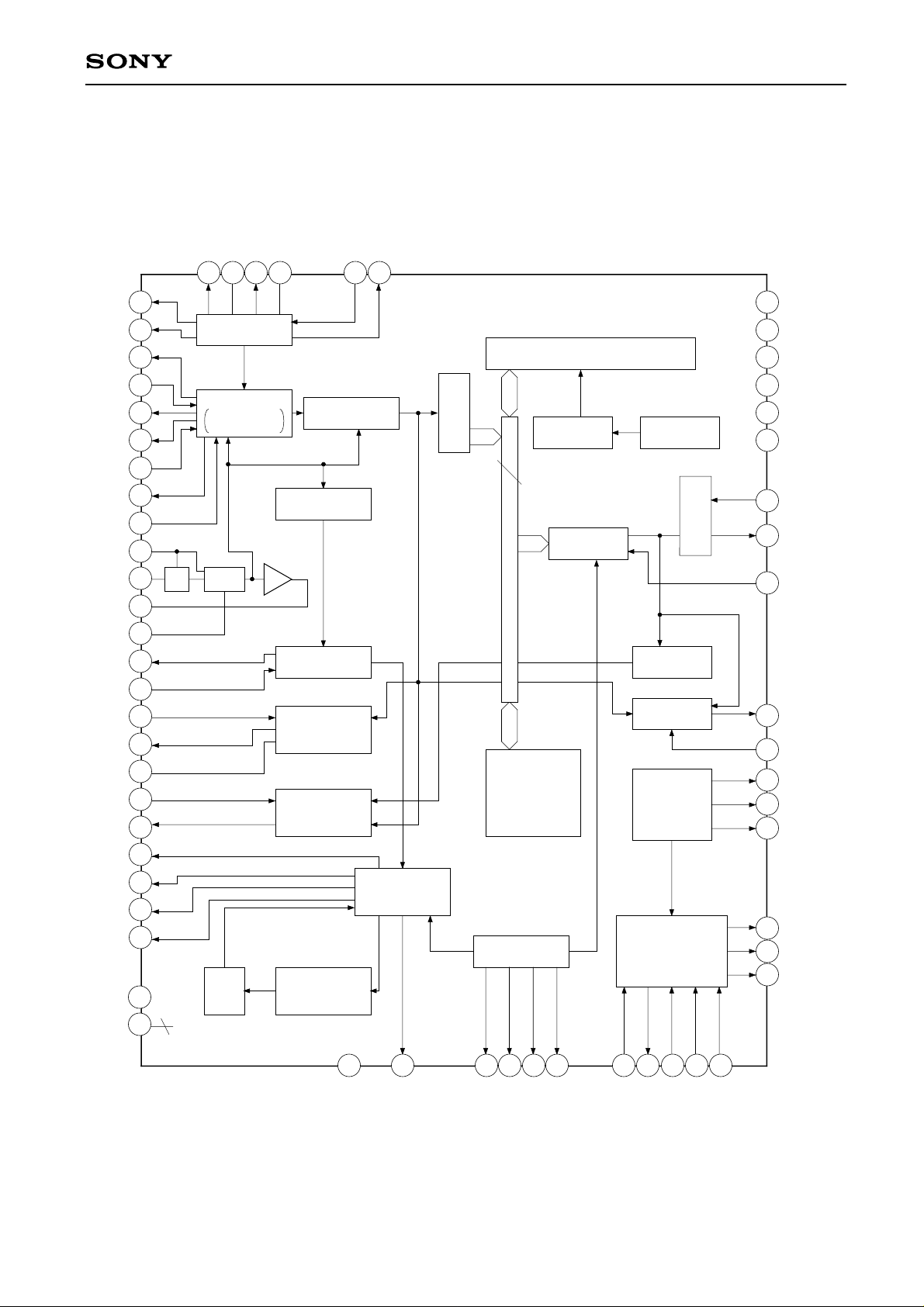

Block Diagram

CXD2500BQ

C4M

C16M

PDO

VCO1

VCO0

PCO

FIL1

FIL0

CLTV

RF

ASY1

ASY0

ASYE

WFCK

SCOR

EXCK

SBSO

EMPH

SQCK

SQSO

MON

FSW

MDP

MDS

TEST

NC

57

58

11

9

8

20

19

18

22

24

26

27

28

62

63

65

64

61

67

66

3

2

4

43

10

FSTT

generator

Digital PLL

vari-pitch

double speed

∗ MUX

Noise

shaper

5

XTAO

XTAI

Clock

XTSL

535456 53 17 19

EFM

demodulator

Sync

Protector

Timing

Generator

Subcode

P-W

Processor

Subcode

Q

Processor

18-times

over samplling

filter

70

VCKI

VPCO

CLV

processor

6

Register

8

Error corrector

Timing

Generator 2

32K RAM

Address

generator

D/A

data processor

313250 51

Priority

encoder

Serial/Parallel

Peak detector

Digital out

CPU interface

Servo

auto

sequencer

6975 76 80

processor

1

23

AV

21

AVSS

33

VDD

73

VDD

12

VSS

52

VSS

30

PSSL

49

DAO 1 to 6

MUTE

68

60

DOUT

MD 2

59

71

DATA

74

CLOK

72

XLAT

DATO

77

79

CLKO

78

XLTO

∗Asymmetry

correction.

DD

XRST

LOCK

—3—

APTR

APTL

LRCK

WDCK

SEIN

SENS

MIRR

CNIN

FOX

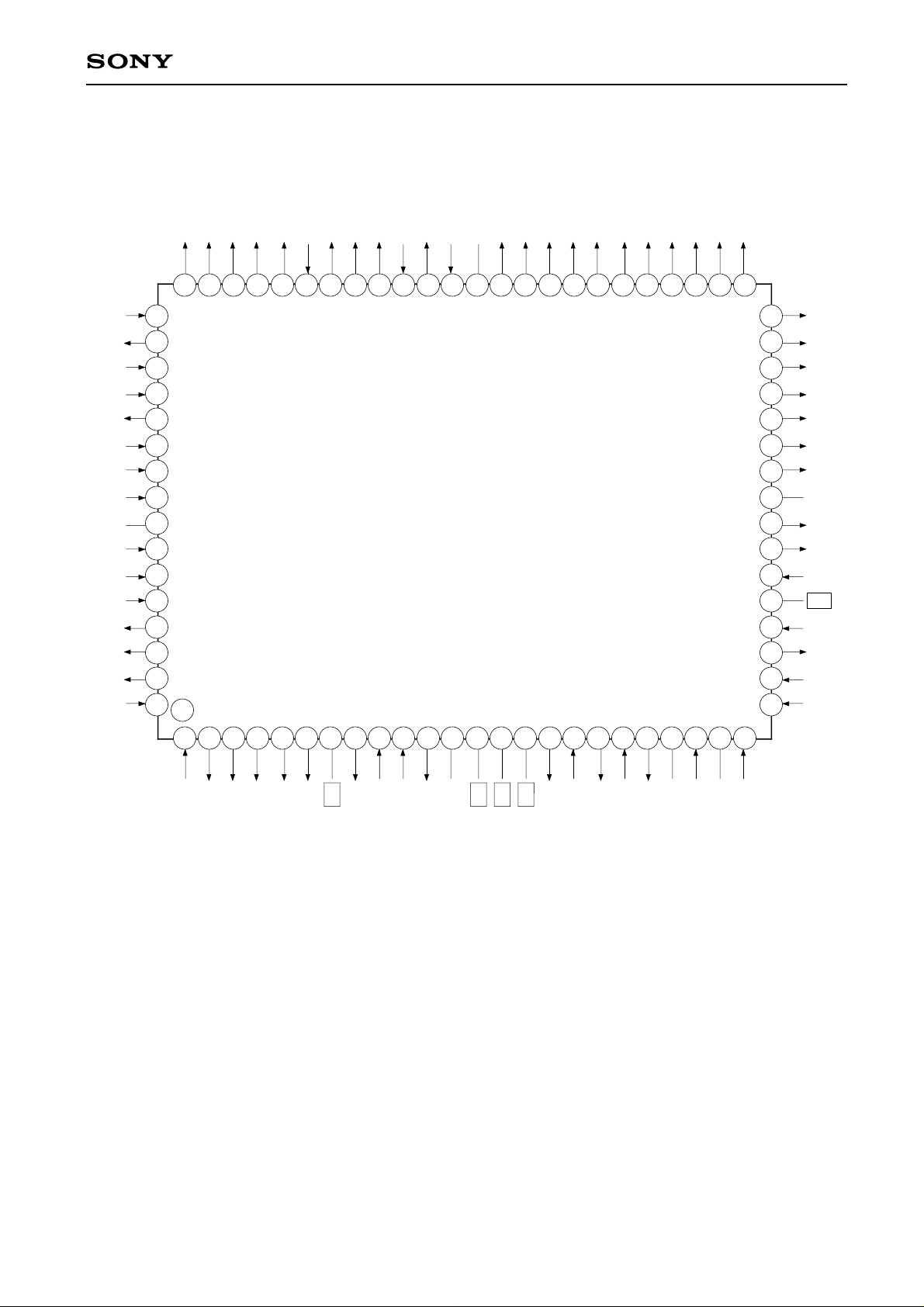

Pin Configuration

CXD2500BQ

EXCK

SQSO

SQCK

MUTE

SENS

XRST

DATA

XLAT

V

CLOK

SEIN

CNIN

DATO

XLTO

CLKO

MIRR

SBSO

SCOR

WFCK

EMPH

DOUT

MD2

C16M

C4M

FSTT

XTSL

XTAQ

XTAI

SS

V

APLL

APTR

DA01

DA02

DA03

DA04

DA05

DA06

DA07

DA08

DA09

414243444546474849505152535455565759 586061626364

65

66

67

68

69

70

71

72

73

DD

D2500B

74

75

76

77

78

79

80

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

DA10

DA11

DA12

DA13

DA14

DA15

DA16

DD

V

LRCK

WDCK

PSSL

NC

ASYE

ASYO

ASYI

BIAS

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 20 21 22 23 2419

SS

FOK

FSW

MON

MDP

MDS

LOCK

NC

VCOO

VCOI

TEST

PDO

NC

V

NC

NC

VPCO

VCKI

FILO

FILI

PCO

SS

AV

CLTV

DD

AV

RF

—4—

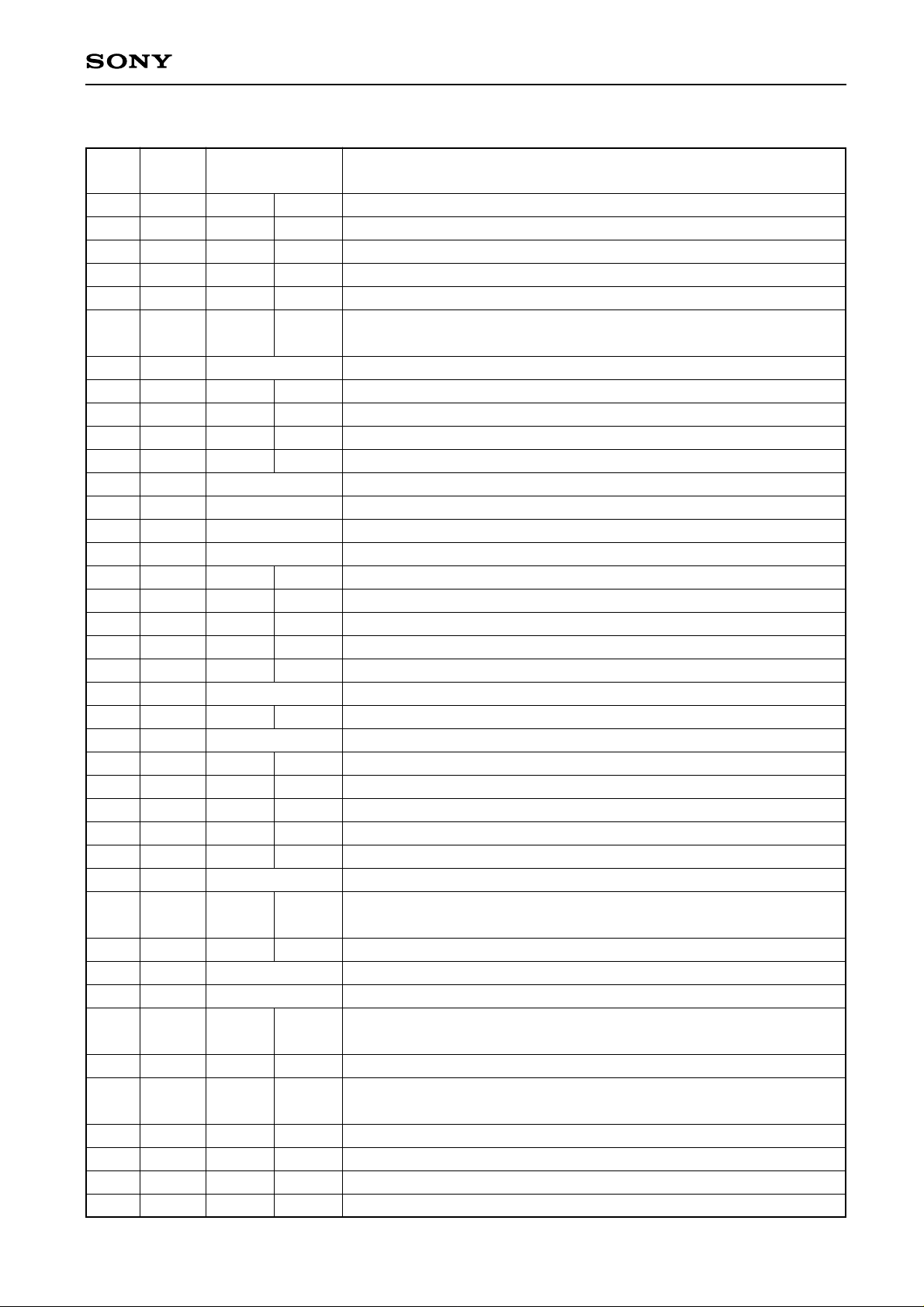

Pin Description

Pin

Symbol I/O Description

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

FOK

FSW

MON

MDP

MDS

LOCK

NC

VCOO

VCOI

TEST

PDO

VSS

NC

NC

NC

VPCO

VCKI

FILO

FILI

PCO

AVSS

CLTV

AVDD

RF

BIAS

ASYI

ASYO

ASYE

NC

PSSL

WDCK

LRCK

VDD

DA16

DA15

DA14

DA13

DA12

DA11

DA10

I

O Z, 0

O 1, 0

O 1, Z, 0

O 1, Z, 0

O 1, 0

—

O 1, 0

I

I

O 1, Z, 0

—

—

—

O 1, Z, 0

I

O Analog

I

O 1, Z, 0

I

I

I

I

O 1, 0

I

—

I

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

CXD2500BQ

Focus OK input. Used for SENS output and servo auto sequencer.

Output used to switch the spindle motor output filter.

Output for spindle motor ON/OFF control

Output for spindle motor servo control

Output for spindle motor servo control

Output is “H” when the GFS signal sampled at 460 Hz is “H”. Output is

“L” when the GFS signal is “L” 8 or more times in succession.

Output of oscillation circuit for analog EFM PLL

Input to oscillation circuit for analog EFM PLL fLOCK=8.6436 MHz

Test. Normally at 0 V (GND).

Output of charge pump for analog EFM PLL

GND

Output of charge pump for vari-pitch PLL

Clock input from external VCO for vari-pitch control. fc center=16.9344 MHz.

Output of filter for master PLL (Slave=Digital PLL)

Input to filter for master PLL

Output of charge pump for master PLL

Analog GND

VCO control voltage input for master PLL

Analog power supply (+5 V)

EFM signal input

Asymmetry circuit constant current input

Asymmetry comparator circuit voltage input

EFM full-swing output

Asymmetry circuit OFF at “L”. Asymmetry circuit ON at “H”.

Input used to switch the audio data output mode. “L” for serial output,

“H” for parallel output.

D/A interface for 48-bit slot. Word clock f=2Fs

D/A interface for 48-bit slot. LR clock f=Fs

Power supply (+5 V)

Outputs DA16 (MSB) when PSSL=1, or serial data from the 48-bit slot

(2’s complements, MSB first) when PSSL=0.

Outputs DA15 when PSSL=1, or bit clock from the 48-bit slot when PSSL=0.

Outputs DA14 when PSSL=1, or serial data from the 64-bit slot (2’s

complements, LSB first) when PSSL=0.

Outputs DA13 when PSSL=1, or bit clock from the 64-bit slot when PSSL=0.

Outputs DA12 when PSSL=1, or LR clock from the 64-bit slot when PSSL=0.

Outputs DA11 when PSSL=1, or GTOP when PSSL=0.

Outputs DA10 when PSSL=1, or XUGF when PSSL=0.

—5—

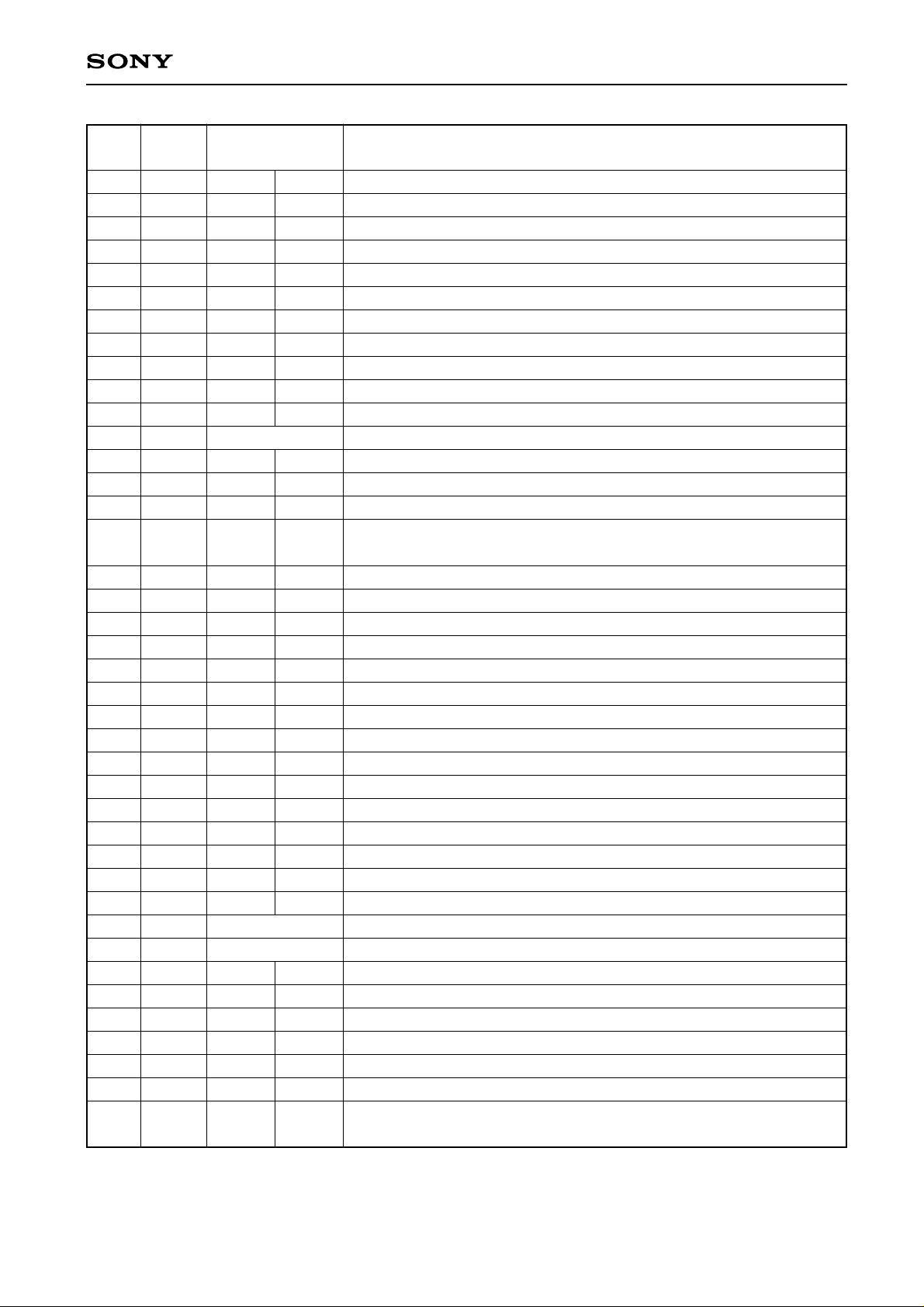

Pin

No.

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

Symbol I/O Description

DA09

DA08

DA07

DA06

DA05

DA04

DA03

DA02

DA01

APTR

APTL

VSS

XTAI

XTAO

XTSL

FSTT

C4M

C16M

MD2

DOUT

EMPH

WFCK

SCOR

SBSO

EXCK

SQSO

SQCK

MUTE

SENS

XRST

DATA

XLAT

VDD

CLOCK

SEIN

CNIN

DATO

XLTO

CLKO

MIRR

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

I

O 1, 0

I

O 1, 0

O 1, 0

O 1, 0

I

O 1, 0

O 1, 0

O 1, 0

O 1, 0

O 1, 0

I

O 1, 0

I

I

— 1, Z, 0

I

I

I

I

I

I

O 1, 0

O 1, 0

O 1, 0

I

Outputs DA9 when PSSL=1, or XPLCK when PSSL=0.

Outputs DA8 when PSSL=1, or GFS when PSSL=0.

Outputs DA7 when PSSL=1, or RFCK when PSSL=0.

Outputs DA6 when PSSL=1, or C2PO when PSSL=0.

Outputs DA5 when PSSL=1, or XRAOF when PSSL=0.

Outputs DA4 when PSSL=1, or MNT3 when PSSL=0.

Outputs DA3 when PSSL=1, or MNT2 when PSSL=0.

Outputs DA2 when PSSL=1, or MNT1 when PSSL=0.

Outputs DA1 when PSSL=1, or MNT0 when PSSL=0.

Control output for aperture correction. “H” for R-ch.

Control output for aperture correction. “H” for L-ch.

GND

Input for 16.9344 MHz and 33.8688 MHz X'tal oscillation circuit.

Output for 16.9344 MHz X'tal oscillation circuit.

X'tal selection input. “L” for 16.9344 MHz X'tal, “H” for 33.8688 MHz X'tal.

2/3 frequency demultiplication output for Pins 53 and 54. Unaffected by

vari-pitch control.

4.2336 MHz output. Subject to vari-pitch control.

16.9344 MHz output. Subject to vari-pitch control.

Digital-Out ON/OFF control. “H” for ON, “L” for OFF.

Digital-Out output.

“H” for playback disc provided with emphasis, “L” for without emphasis.

WFCK (Write Frame Clock) output.

“H” when subcode Sync S0 or S1 is detected.

Serial output of Sub P to W

Clock input for reading SBSO

Outputs 80-bit Sub Q and 16-bit PCM peak-level data.

Clock input for reading SQSO

“H” for muting, “L” for release.

SENS output to CPU

System reset. “L” for resetting.

Inputs serial data from CPU.

Latches serial data input from CPU at falling edge.

Power supply (+5 V)

Inputs serial data transfer clock from CPU.

Inputs SENSE from SSP.

Inputs track jump count signal.

Outputs serial data to SSP.

Latches serial data output to SSP at falling edge.

Outputs serial data transfer clock to SSP.

Inputs mirror signal to be used by auto sequencer when jumping 16 or

more tracks.

CXD2500BQ

—6—

CXD2500BQ

Note:

• The data at the 64-bit slot is output in 2’s complements on an LSB-first basis. The data at the 48-bit slot is

output in 2’s complements on an MSB-first basis.

• GTOP monitors the state of Frame Sync protection. (“H”: Sync protection window released)

• XUFG is a negative Frame Sync pulse obtained from the EFM signal before Frame Sync protection is

effected..

• XPLCK is an inversion of the EFM PLL clock. The PLL is designed so that the falling edge of XPLCK

coincides with a change point of the EFM signal.

• The GFS signal turns “H” upon coincidence between Frame Sync and the timing of interpolation protection.

• RFCK is a signal generated at 136-µs periods using a crystal oscillator.

• C2PO is a signal to indicate data error.

• XRAOF is a signal issued when a jitter margin of ±28F is exceeded by the 32K RAM.

—7—

CXD2500BQ

Electrical Character

DC characteristics (VDD=AVDD=5.0 V±5 %, VSS=AVSS=0 V, Topr=–20 to +75°C)

Item Condition Min. Typ. Max. Unit Related pins

Input voltage.

“H” level

Input voltage

“L” level.

Input voltage

“H” level

Input voltage

“L” level

VIH (1)

VIL (1)

VIN (2)

VIN (2)

Schmitt circuit

input

0.7VDD V

∗1

0.3VDD V

0.8VDD V

∗2

0.2VDD V

Input voltage

Output voltage

“H” level

Output voltage

“L” level

Output voltage

“H” level

Output voltage

“L” level

Output voltage

“L” level

Output voltage

“H” level

Output voltage

Output Output Output Output Input Input Input

voltage (4) voltage (3) voltage (2) voltage (1) voltage (3) voltage (2) voltage (1)

“L” level

Input leak current

VIN (3)

VOH (1)

VOL (1)

VOH (2)

VOL (2)

VOL (3)

VOH (4)

VOL (4)

ILI

Analog input

IOH=–1 mA

IOL=1 mA

IOH=–1 mA

IOL=2 mA

IOL=2 mA

IOH=–0.28 mA

IOL=0.36 mA

VI=0 to 5.25 V

VSS VDD V

VDD–0.5 VDD V

0 0.4 V

VDD–0.5 VDD V

0 0.4 V

0 0.4 V

VDD–0.5 VDD V

0 0.4 V

±5 µA

∗3

∗4

∗5

∗

6

∗

7

∗

1, ∗2, ∗3

Tristate pin output leak

current

ILO

VO=0 to 5.25 V

±5 µA

∗

8

Related pins

∗

1 XTSL, DATA, XLAT, MD2, PSSL

∗

2 CLOK, XRST, EXCK, SQCK, MUTE, FOK, SEIN, CNIN, MIRR, VCKI, ASYE

∗

3 CLTV, FILI, RF

∗

4 MDP, PDO, PCO, VPCO

∗

5 ASYO, DOUT, FSTT, C4M, C16M, SBSO, SQSO, SCOR, EMPH, MON, LOCK, WDCK, DATO, CLKO,

XLTO, SENS, MDS, DA01 to DA16, APTR, APTL, LRCK, WFCK

∗

6 FSW

∗

7 FILO

∗

8 SENS, MDS, MDP, FSW, PDO, PCO, VPCO

—8—

AC Characteristics

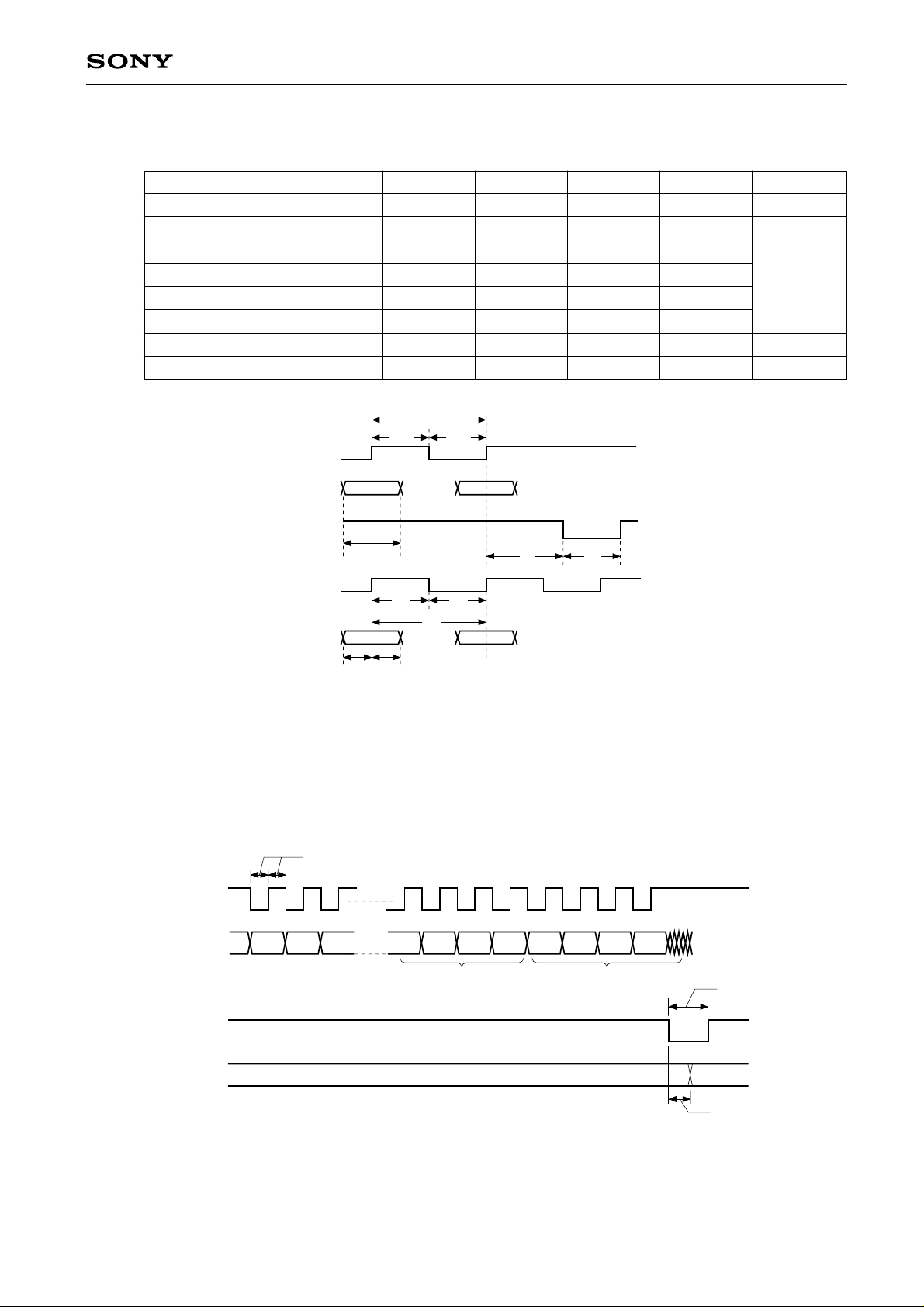

(1) XTAI and VCOI pins

1) During self-oscillation (Topr=–20 to +75 °C, VDD=AVDD=5.0 V±5 %)

CXD2500BQ

Item

Oscillation frequency

Symbol

fMAX

Min.

7

Typ. Max.

34

Unit

MHz

2) With pulses input to XTAI and VCOI pins (Topr=–20 to +75 °C, VDD=AVDD=5.0 V±5 %)

Item

“H” level pulse width

“L” level pulse width

Pulse period

Input “H” level

Symbol

tWHX

tWLX

tCX

VIHX

Min.

13

13

26

VDD–1.0

Typ. Max.

500

500

1,000

Unit

ns

V

Input “L” level

Rising time

Falling time

VILX

tR, tF

0.8

10

ns

tCX

tWHX tWLX

XTAI

t

R

tF

3) With sine waves input to XTAI and VCOI pins via capacitor

Item

Input amplitude

Symbol

V1

Min.

2.0

VIHX

VIHX×0.9

VDD/2

VIHX×0.1

V

ILX

(Topr=–20 to +75 °C, VDD=AVDD=5.0 V±5 %)

Typ. Max.

VDD+0.3

Unit

Vp-p

—9—

(1) CLOK, DATA, XLAT, CNIN, SQCK, and EXCK pins

(VDD=AVDD=5.0 V±5 %, VSS=AVSS=0 V, Topr=–20 to +75 °C

CXD2500BQ

Item

Clock frequency

Clock pulse width

Setup time

Hold time

Delay time

Latch pulse width

EXCK, CNIN, SQCK frequency

EXCK, CNIN, SQCK pulse width

CLOK

DATA

XLAT

EXCK

CNIN

SQCK

SUBQ

SQCK

tSU tH

tSU tH

Symbol

tWCK

tWCK

tWT

fCK

tSU

tH

tD

tWL

fT

tWT

1/fCK

1/fT

tWCK

tWT

Min.

750

300

300

300

750

300

tD tWL

Typ. Max.

0.65

1

Unit

MHz

ns

MHz

ns

Description of Functions

§1 CPU Interface and Commands

• CPU interface

This interface is used to set various modes using DATA, CLOK, and XLAT.

The interface timing chart is shown below.

750ns or more

CLOK

DATA

XLAT

Registers 4 to E

D1 D2 D3 D0 D1 D2 D3

Data Address

750ns or more

Valid

300ns max

• The command addresses of the CXD2500B and the data capable of being set are shown in Table 1-1.

• When XRST is set to 0, the CXD2500B is reset, causing its internal registers to be initialized to the values

listed in Table 1-2.

—10—

Data 4

CXD2500BQ

D3 D2 D1 D0

Data 3

D3 D2 D1 D0

Data 2

D3 D2 D1 D0

————

————

————

————

————

————

8421

————

————

————

128 64 32 16

2,048 1,024 512 256

————

————

————

WSEL

————

————

FLFC —

MAIN SUB

BiliGL BiliGL

8421

————

————

128 64 32 16

2,048 1,024 512 256

PCT1 PCT2 — —

————

————

————

————

————

————

————

————

————

CLVS

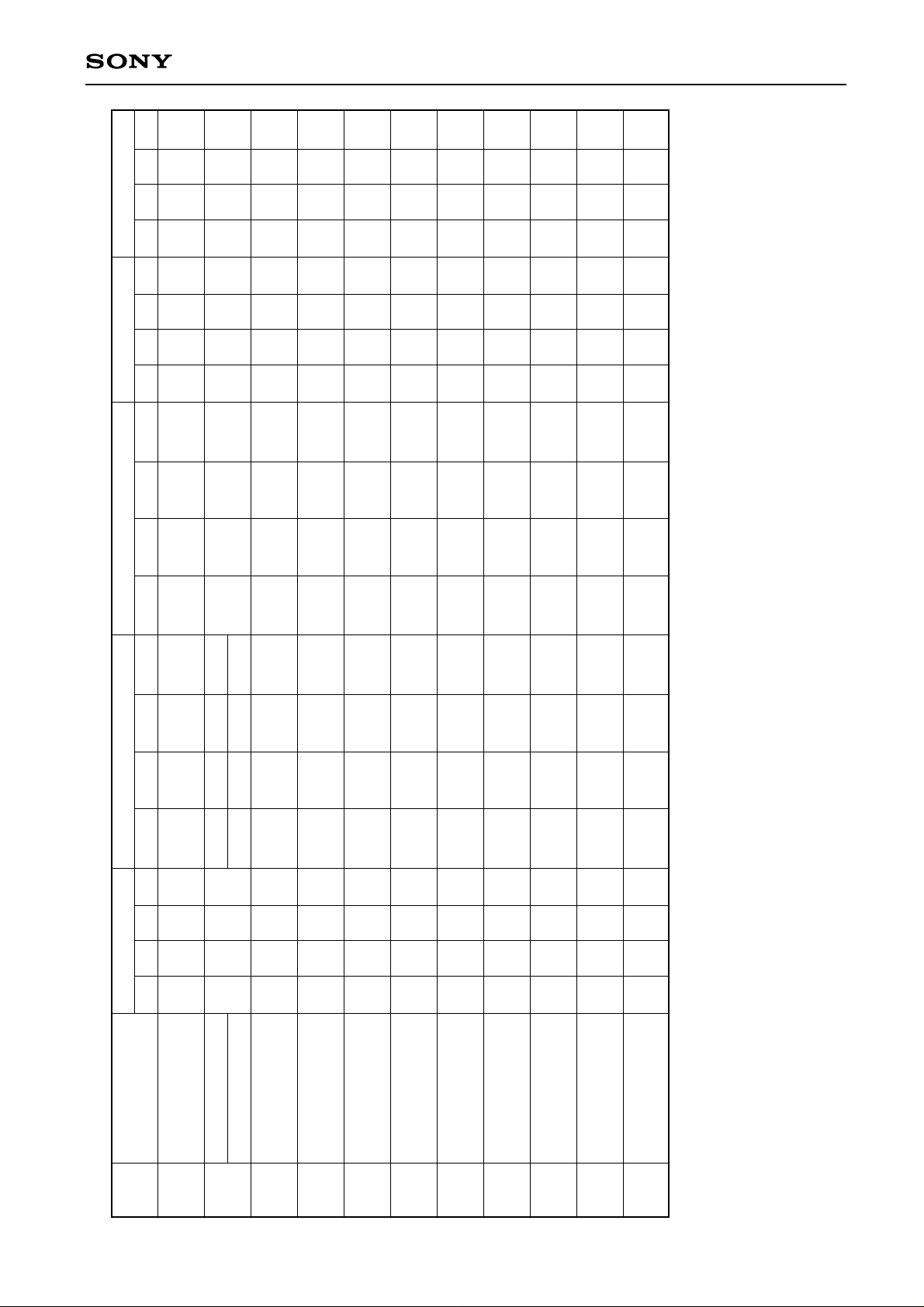

Table 1-1

Data 1

D3 D2 D1 D0

Address

D3 D2 D1 D0

Command

AS3 AS2 AS1 AS0

0.18 ms 0.09 ms 0.045 ms 0.022 ms

0.36 ms 0.18 ms 0.09 ms 0.045 ms

11.6 ms 5.8 ms 2.9 ms 1.45 ms

0100

Auto sequence

0101

0110

Blind (A, E), Overflow (C)

Brake (B)

KICK (D)

D OUT

Mute-F

32,768 16,384 8,192 4,096

0111

Auto sequencer track

jump (N) setting

D CLV DSPB A SEQ D PLL

CDROM 0

1000

MODE specification

ON-OFF ON-OFF ON-OFF ON-OFF

1001

Func specification

Mute ATT

UP Down

Vari Vari

1010

Audio CTRL

Traverse monitor

Gain Gain Gain Gain

32,768 16,384 8,192 4,096

1011

counter setting

MDP1 MDP0 MDS1 MDS0

1100

Servo factor setting

TB TP

DCLV

CM3 CM2 CM1 CM0

PWM MD Gain

1101

1110

CLV CRTL

CLV mode

name

Register

Commands

4

5

6

7

8

9

A

B

C

E

D

—11—

Data 3

CXD2500BQ

D3 D2 D1 D0

Data 3

D3 D2 D1 D0

Data 2

D3 D2 D1 D0

————

————

————

————

————

————

0000

————

————

————

————

0000

————

0001

————

————

————

000—

0000

————

0000

————

00——

0001

————

————

————

————

————

————

————

————

————

Data 1

D3 D2 D1 D0

Address

D3 D2 D1 D0

Command

0000

0100

0101

0111

0000

0000

0101

0110

0111

1000

1001

0011

0000

1001

1010

1011

0110

1100

0000

1101

Table 1-2

0000

1110

Auto sequence

Blind (A, E), Overflow (C)

4

name

Register

Reset Initialization

Brake (B)

5

KICK (D)

Auto sequencer

6

track jump setting

MODE specification

7

8

Func specification

Audio CTRL

Traverse monitor

9

A

—12—

counter setting

Servo factor setting

B

C

CLV CRTL

CLV mode

E

D

§1 Meanings of Data Set at Command Addresses

$4X Command

CXD2500BQ

Command

CANCEL

FOCUS-ON

1 TRACK JUMP

10 TRACK JUMP

2N TRACK JUMP

M TRACK MOVE

AS3

0

0

1

1

1

1

AS2

0

1

0

0

1

1

AS1

0

1

0

1

0

1

AS0

0

1

RXF

RXF

RXF

RXF

RXF=0 FORWARD

RXF=1 REVERSE

• If a Focus-ON command ($47) is canceled during execution, $02 is issued and the auto sequence operation

is discontinued.

• If a Track Jump or Track Move command ($48 to $4F) is canceled during execution, the auto sequence

operation is discontinued.

$5X Command

Used to set timers for the auto sequencer.

Timers set: A, E, C, and B

Command

Blind(A, E), Overflow(C)

Brake(B)

D3

0.18 ms

0.36 ms

D2

0.09 ms

0.18 ms

D1

0.045 ms

0.09 ms

D0

0.022 ms

0.045 ms

Example: D2=D0=1, D3=D1=0 (Initial Reset)

A=E=C=0.112 ms

B=0.225 ms

$6X Command

Used to set a timer for the auto sequencer.

Timer set: D

Command

KICK (D)

D3

11.6 ms

D2

5.8 ms

Example: D3=0 D2=D1=D0=1 (Initial Reset)

D=10.15ms

$7X Command

Used to set the number of auto sequencer track jumps/moves.

Command

Auto sequencer track

jump number setting

Data3

D3 D2 D1 D0

2152142132

12

Data 2

D3 D2 D1 D0

211210292

D1

2.9 ms

Data 3

D3 D2 D1 D0

8

2726252

D0

1.45 ms

Data 4

D3 D2 D1 D0

4

2322212

0

This command sets the value of “N” for 2N track jump and M track move execution using the auto sequencer.

—13—

CXD2500BQ

• The maximum number of tracks that can be counted is 65,535. However, in the case of 2N track jumps, it is

subject to mechanical restrictions due to the optical system.

• When the number of tracks to be jumped is smaller that 15, the signals input from CNIN are counted. When

it is 16 or larger, the signals input from the MIRR pin are counted. This count signal selection contributes

toward improving the accuracy of high-speed track jumping.

Command

MODE specification

$8X Command

Command

CDROM=1

CDROM=0

Command bit

D. out Mute F=1

D. out Mute F=0

D3

CDROM

C2PO timing

1-3

1-3

CDROM mode is entered. In this mode, average value

interpolation and preceding value holding are not performed.

Audio mode is entered. In this mode, average value

interpolation and preceding value holding are performed.

D2

0

D1

D. OUT

Mute-F

Processing

Processing

When Digital Out is ON (pin MD2=1), DA output is muted.

Da output muting is unaffected by the setting of Digital Out.

D/A Out D.out Mute with F=1

Mute-ON

Mute-OFF

MD2=1

(D. out-ON)

– ∞dB

– ∞dB

MD2=0

(D. out-OFF)

– ∞dB

0dB

AS0

WSEL

Command bit

WSEL=1

WSEL=0

$9X Command

Command

Func specification

Sync protection window width

±26 channel clock pulses

±6 channel clock pulses

∗

In normal-speed playback, the channel clock frequency is 4.3218 MHz.

∗

Anti-rolling is enhanced.

Sync window protection is enhanced.

Data 1

D3 D2 D1 D0

DCLV DSPB A. SEQ D. PLL

ON-OFF ON-OFF ON-OFF ON-OFF

Application

Data 2

D3 D2 D1

BiliGL BiliGL FLFC

MAIN Sub

—14—

CXD2500BQ

Command bit

DCLV ON-OFF=0

CLV mode

In CLVS mode

In CLVP mode

FSW=L, MON-H, MDS-Z, MDP=servo control signal, with carrier

frequency of 230 Hz at TB=0 and 460 Hz at TB=1

FSW=Z, MON=H, MDS=speed control signal with carrier frequency of

7.35 kHz, MDP=phase control signal with carrier frequency of 1.84 kHz

Contents

MDS= PWM polarity signal. Carrier

DCLV when frequency=132 kHz

DCLV ON-OFF=1

(FSW and MON are

unnecessary)

In CLVS or

CLVP mode

PWM, MD=1 MDS= PWM absolute value output (binary).

Carrier frequency=132 kHz

DCLV when

PWM, MD=0

MDS= Z

MDP= ternay PWM output.

Carrier frequency=132 kHz

In the Digital CLV servo mode with DCLV ON-OFF set to 1, the sampling frequency of the internal digital filter

is switched at the same time as the switching between CLVP and CLVS.

Therefore, for CLVS, the cut-off frequency fC is 70 Hz when TB is set to 0, and 140Hz when TB is set to 1.

Command bit

DSPB=0

DSPB=1

Normal-speed playback. ECC quadruple error correction is made. Vari-pitch

control is enabled.

Double-speed playback. ECC double error correction is made. Vari-pitch control

is disabled.

Processing

Set FLFC at 1 when in double-speed playback mode (exclude the low power consumption special playback

mode). However, FLFC can be set to 0 during PLL pull-in (lock). Set to 0 for all other modes.

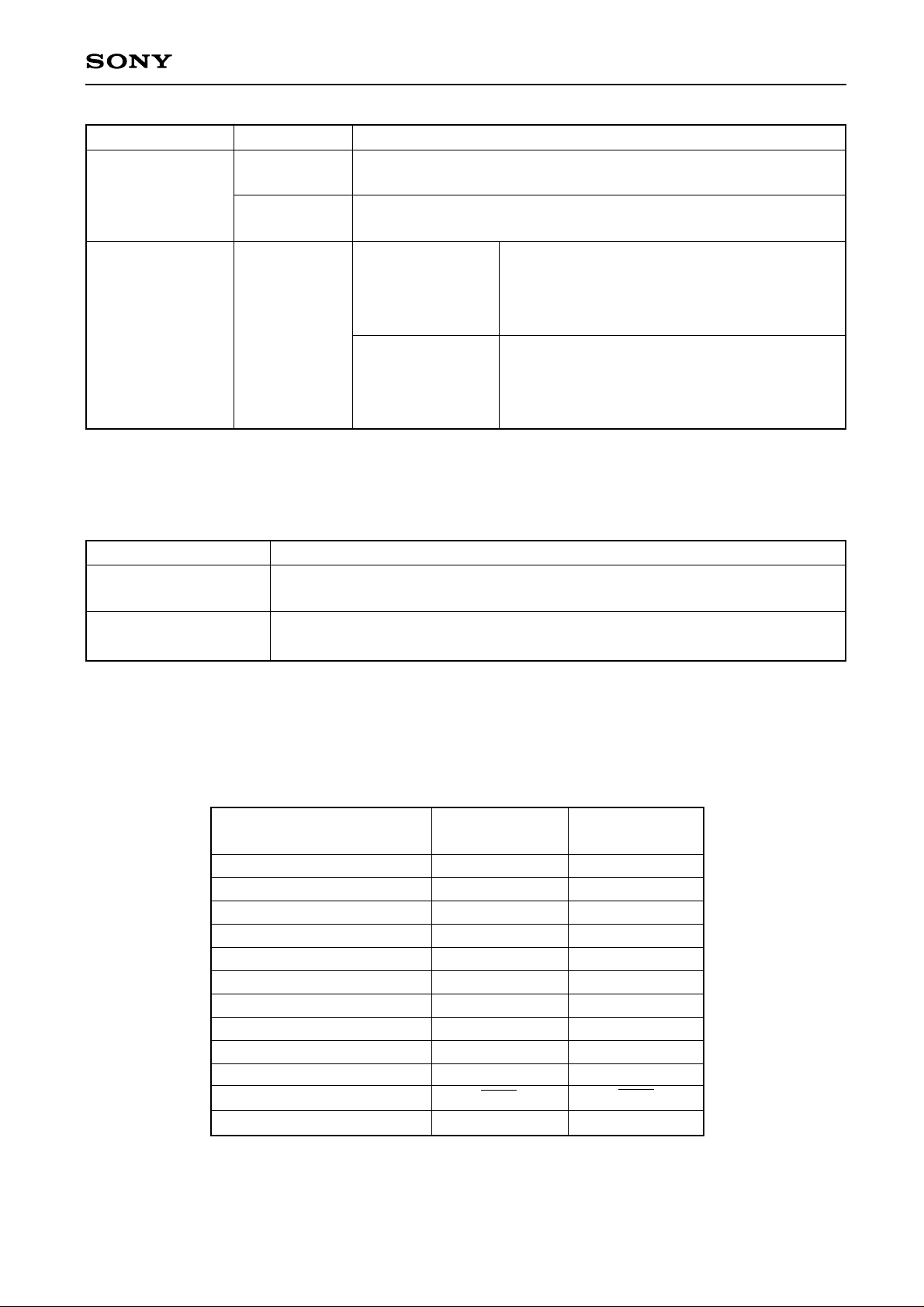

SENS Output

Microcomputer serial register

values (Latching unnecessary)

$0X

$1X

$2X

$3X

$4X

$5X

$6X

$AX

$BX

$CX

$EX

$7X, 8X, 9X, DX, FX

ASEQ=0

Z

Z

Z

Z

Z

Z

Z

GFS

COMP

COUT

OV64

Z

ASEQ=1

SEIN (FZC)

SEIN (A, S)

SEIN (T. Z. C)

SEIN (SSTOP)

XBUSY

FOK

SEIN (Z)

GFS

COMP

COUT

OV64

0

—15—

Loading...

Loading...