Sony CXD2458AR Datasheet

CXD2458AR

Timing Generator for Color LCD Panels

Description

The CXD2458AR is a timing signal generator for

the color LCD panel LCX005BK/BKB, LCX009AK/

AKB, LCX024AK and LCX027AK drivers.

Features

• Generates the color LCD panel LCX005BK/BKB,

LCX009AK/AKB, LCX024AK and LCX027AK drive

pulse

• Supports NTSC/PAL

• Supports 16:9 (WIDE) display (NTSC/PAL)

• Supports composite SYNC and separate SYNC

(XHD, XVD) input

• Standby function (low power consumption function)

• Supports right/left inverse display

• AC drive of LCD panels during no signal

• Generates timing signal of external sample-and-

hold circuit

• Generates line inversion and field inversion signals

• AFC circuit supporting static and dynamic fluctuations

Applications

Color LCD viewfinders, compact LCD projectors, etc.

Structure

Silicon gate CMOS IC

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD VSS – 0.3 to +6.0 V

• Input voltage VI VSS – 0.3 to VDD + 0.3 V

• Output voltage VO VSS – 0.3 to VDD + 0.3V

• Operating temperature Topr –20 to +85 °C

• Storage temperature Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage VDD 2.7 to 3.3 V

• Operating temperature Topr –20 to +85 °C

– 1 –

E98218-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

48 pin LQFP (Plastic)

For the availability of this product, please contact the sales office.

– 2 –

CXD2458AR

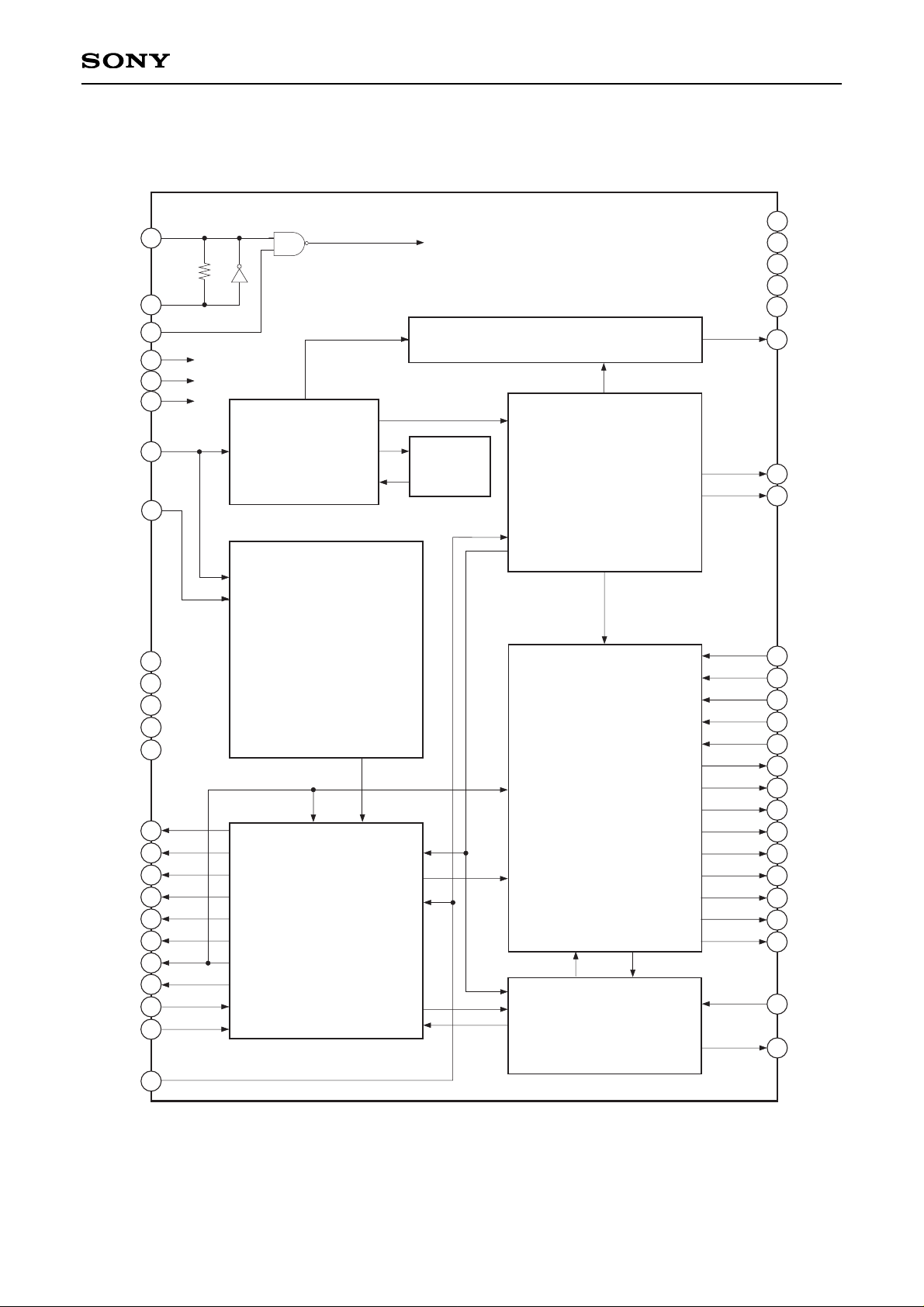

Block Diagram

PLL PHASE COMPARATOR

H-SYNC

DETECTOR

H-SKEW

DETECTOR

V-SYNC

SEPERATOR

(NOISE SHAPE)

PLL-COUNTER

HALF-H

KILLER

H-TIMING

PULSE

GENERATOR

CKO

XCLR

TST3

SLCK

XHD

CKI

PLNT

TST4

EN

VD

VST

VCK1

VCK2

FLDO

SBLK

WIDE

RPD

HD

XCLP

HP1

HST1

HP2

HP3

HP4

RGT

HST2

HCK1

HCK2

SH1

SH2

SH3

SH4

CLR

SLFR

FRP

master ck

FIELD & LINE

CONTROLLER

2

3

4

5

17

18

20

21

25

27

29

41

42

1

PAL PULSE

ELIMINATOR

10

13

14

16

22

23

24

28

30

39

38

36

35

34

32

33

46

47

48

TST0

TST1

TST2

7

8

9

45

XVD

15

STBY

37

44

12

11

26

BLK

V-TIMING

PULSE GENERATOR

SLTM

SLNP

VDD

VDD

VSS

VSS

VSS

19

43

6

31

40

– 3 –

CXD2458AR

Pin Description

Pin

No.

Symbol I/O Description

Input pin for

open status

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

SLCK

PLNT

XCLR

WIDE

SBLK

VSS

TST0

TST1

TST2

RGT

SLTM

BLK

SLFR

HST2

STBY

CLR

EN

VST

VDD

VCK2

VCK1

HST1

HCK2

HCK1

VD

SLNP

XHD

FRP

FLDO

SH4

VSS

SH1

SH2

SH3

I

I

I

I

O

—

I

I

I

I

I

O

I

O

I

O

O

O

—

O

O

O

O

O

O

I

I

O

O

O

—

O

O

O

Switches between LCX005, LCX024 (H) and LCX009, LCX027 (L)

Switches between PAL (H) and NTSC (L)

Cleared at 0V

Switches between 16:9 display (H) and 4:3 display (L)

SBLK pulse output (during WIDE MODE) (positive polarity)

GND

Test (Leave open.)

Test (Leave open.)

Test (Leave open.)

Switches between Normal scan (H) and Reverse scan (L)

Switches between LCX027 (H) and LCX009 (L)

BLK pulse output (during WIDE MODE) (positive polarity)

Switches between field inversion (H) and line inversion (L)

H start pulse 2 (positive polarity)

Standby input (H: Operating mode, L: Standby mode)

CLR pulse output

EN pulse output

V start pulse output

Power supply

V clock pulse 2

V clock pulse 1

H start pulse 1 (positive polarity)

H clock pulse 2

H clock pulse 1

VD pulse output (positive polarity)

Switches between LCX024 (H) and LCX005 (L)

XHD (negative polarity)/Composite SYNC (positive polarity) input

AC drive timing pulse

Field identification signal

Sample-and-hold pulse (positive polarity)

GND

Sample-and-hold pulse (positive polarity)

Sample-and-hold pulse (positive polarity)

Sample-and-hold pulse (positive polarity)

L

L

H

L

—

—

L

L

L

H

L

—

L

—

H

—

—

—

—

—

—

—

—

—

—

L

—

—

—

—

—

—

—

—

– 4 –

CXD2458AR

Pin

No.

Symbol I/O Description

Input pin for

open status

35

36

37

38

39

40

41

42

43

44

45

46

47

48

XCLP

HD

TST3

HP4

RPD

VSS

CKO

CKI

VDD

TST4

XVD

HP1

HP2

HP3

O

O

I

I

O

—

O

I

—

I

I

I

I

I

Burst position clamp pulse (negative polarity)

HD pulse (positive polarity)

Test (Leave open.)

Switches the horizontal display position

Phase comparator output

GND

Oscillation cell (output)

Oscillation cell (input)

Power supply

Test (Leave open.)

XVD (negative polarity) input

Switches the horizontal display position

Switches the horizontal display position

Switches the horizontal display position

—

—

H

H

—

—

—

—

—

H

L

L

L

L

(H: Pull up, L: Pull down)

Note) The CXD2458AR processes the composite SYNC and separate SYNC inputs with the same pins.

Therefore, care should be given to the following points when using the CXD2458AR.

1) During composite SYNC input, the XVD input pin should be set to L or left open.

2) During separate SYNC (XHD, XVD) input, the XVD width specification is from 2H to 10H.

– 5 –

CXD2458AR

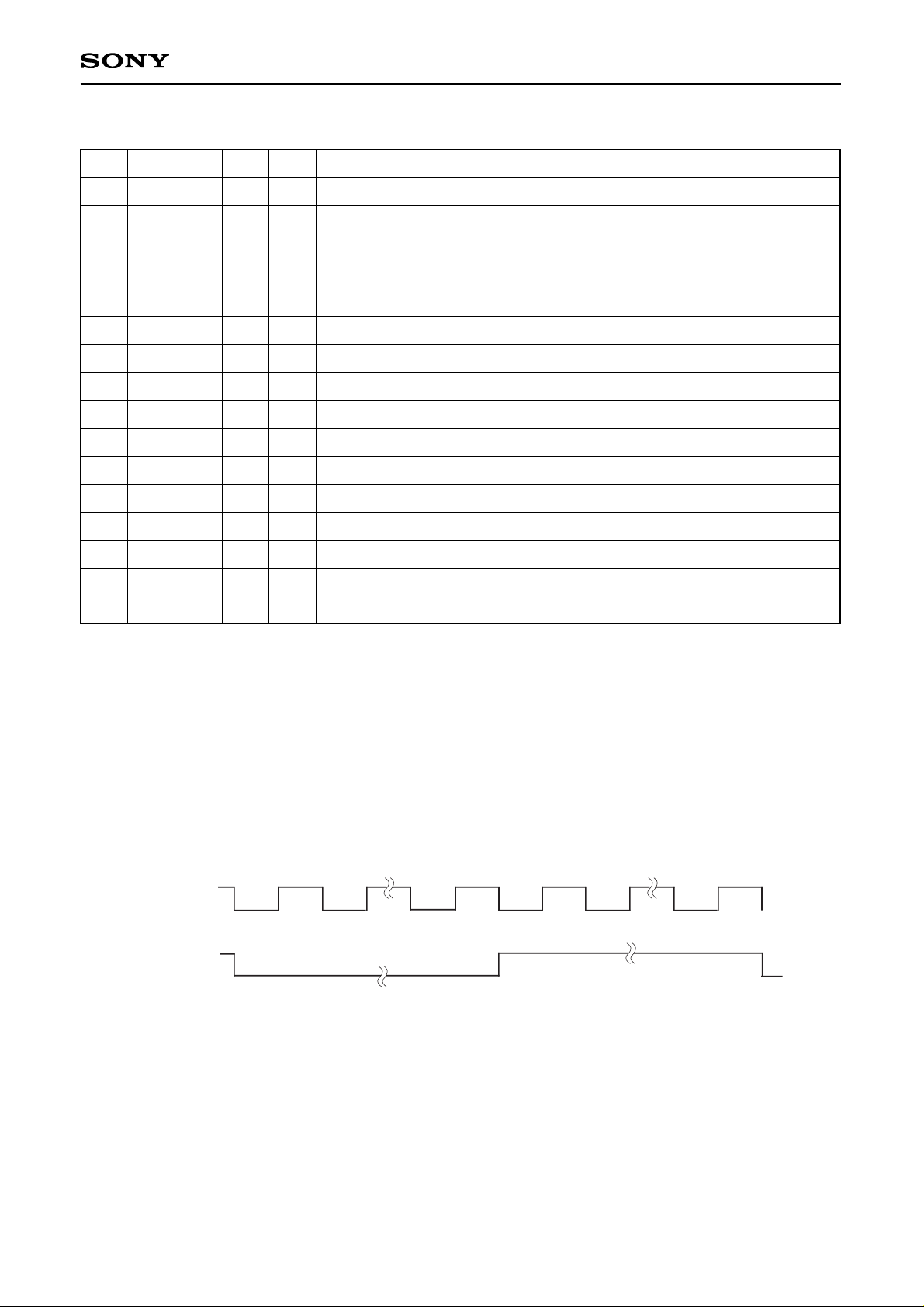

Electrical Characteristics

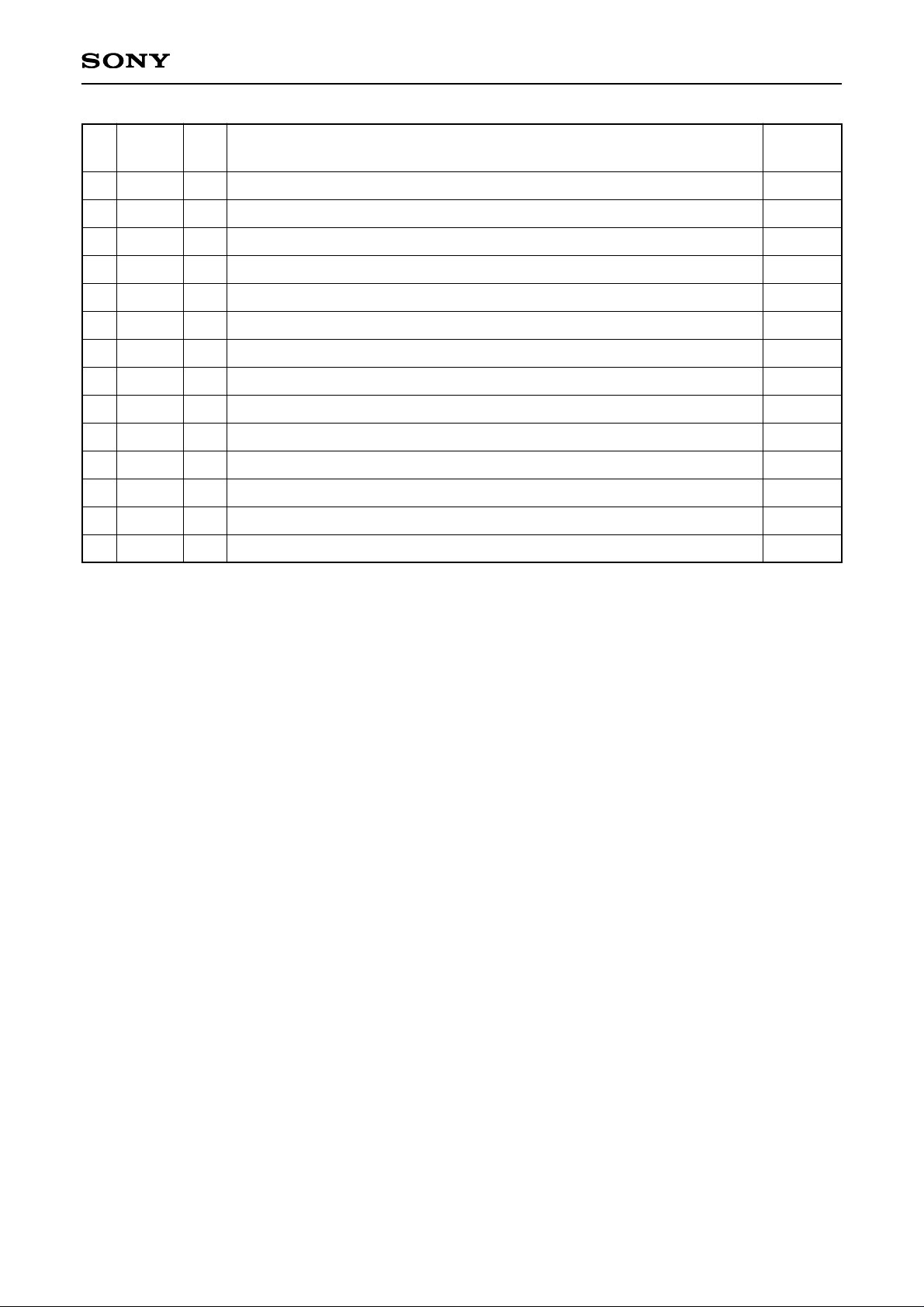

DC Characteristics (VDD = 3.0V ± 10%, Topr = –20 to +85°C)

Item

Symbol

Min. Typ. Max. UnitMeasurement conditions

H level input voltage

L level input voltage

H level input current

L level input current

H level input current

L level input current

H level input current

L level input current

L level output voltage

H level output voltage

L level output voltage

H level output voltage

L level output voltage

H level output voltage

Output leak current

Current consumption

VIH

VIL

IIH1

IIL1

IIH2

IIL2

IIH3

IIL3

VOL1

VOH1

VOL2

VOH2

VOL3

VOH3

IOZ

IDD

VI = VDD

VI = 0V

VI = VDD

VI = 0V

VI = VDD

VI = 0V

IOL = 1mA

IOH = –250µA

IOL = 500µA

IOH = –125µA

IOL = 500µA

IOH = –250µA

At high impedance state

VDD = 3.0V, STBY = H

VDD = 3.0V, STBY = L

0.7VDD

10

–10

2.6

2.6

2.6

–1.0

12

3

0.3VDD

1.0

–1.0

180

–3.0

3.0

–180

0.2

0.2

0.2

1.0

V

V

µA

µA

µA

µA

µA

µA

V

V

V

V

V

V

µA

mA

mA

Remarks

∗1

∗2

∗3

∗4

∗5

∗6

∗7

∗8

Item Applicable pins Min. Typ. Max. UnitConditions

Clock input cycle

Cross-point time difference

Output rise delay time

Output fall delay time

HCK1, SH1 delay time difference

HCK2, SH1 delay time difference

HCK Duty

CKI

HCK1, HCK2

VCK1, VCK2

VCKn, HCKn

Other than HCKn and VCKn

VCKn, HCKn

Other than HCKn and VCKn

HCK1, SH1

HCK2, SH1

HCK1, HCK2

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

60

1

3

1

1

48

15

20

84

76

71

62

5

5

53

ns

ns

ns

ns

ns

ns

ns

ns

ns

%

Symbol

tck

∆t

tpr

tpf

dt1

dt2

dtyH

∗1

All input pins.

∗2

Input pins XHD and CKI.

∗3

Input pins SLNP and XVD.

∗4

Input pins XCLR, RGT, STBY, HP4, TST3 and TST4.

∗5

Output pins HCK1 and HCK2.

∗6

All output pins other than those listed in ∗5, ∗7and ∗8.

∗7

Output pin CKO. However, set the input level of input pin CKI to 0V or VDD during measurement.

∗8

Output pin RPD.

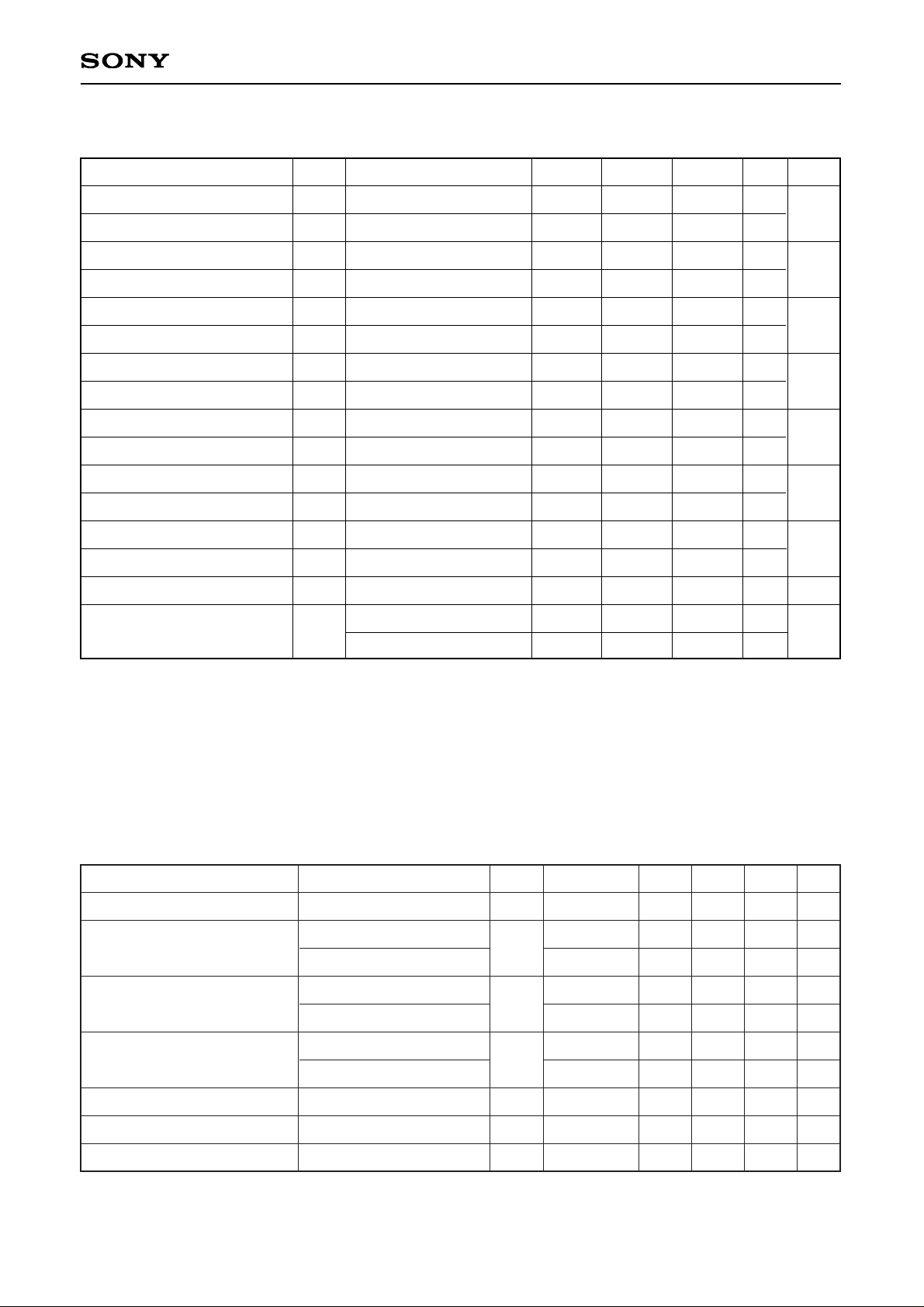

AC Characteristics (VDD = 3.0V ± 10%, Topr = –20 to +85°C)

– 6 –

CXD2458AR

Output

tpr

Output

tpf

100%

CKI

HCK1/VCK1

HCK2/VCK2

V

DD

0V

V

DD

0V

V

DD

0V

VDD

0V

V

DD

0V

50%

50%

50%

50%

∆t∆t

Timing Definition

AC Characteristics

tck

50% 50% 50%

50% 50%

tH tL

dt1 dt2

SH1

HCK1/HCK2

CKI

– 7 –

CXD2458AR

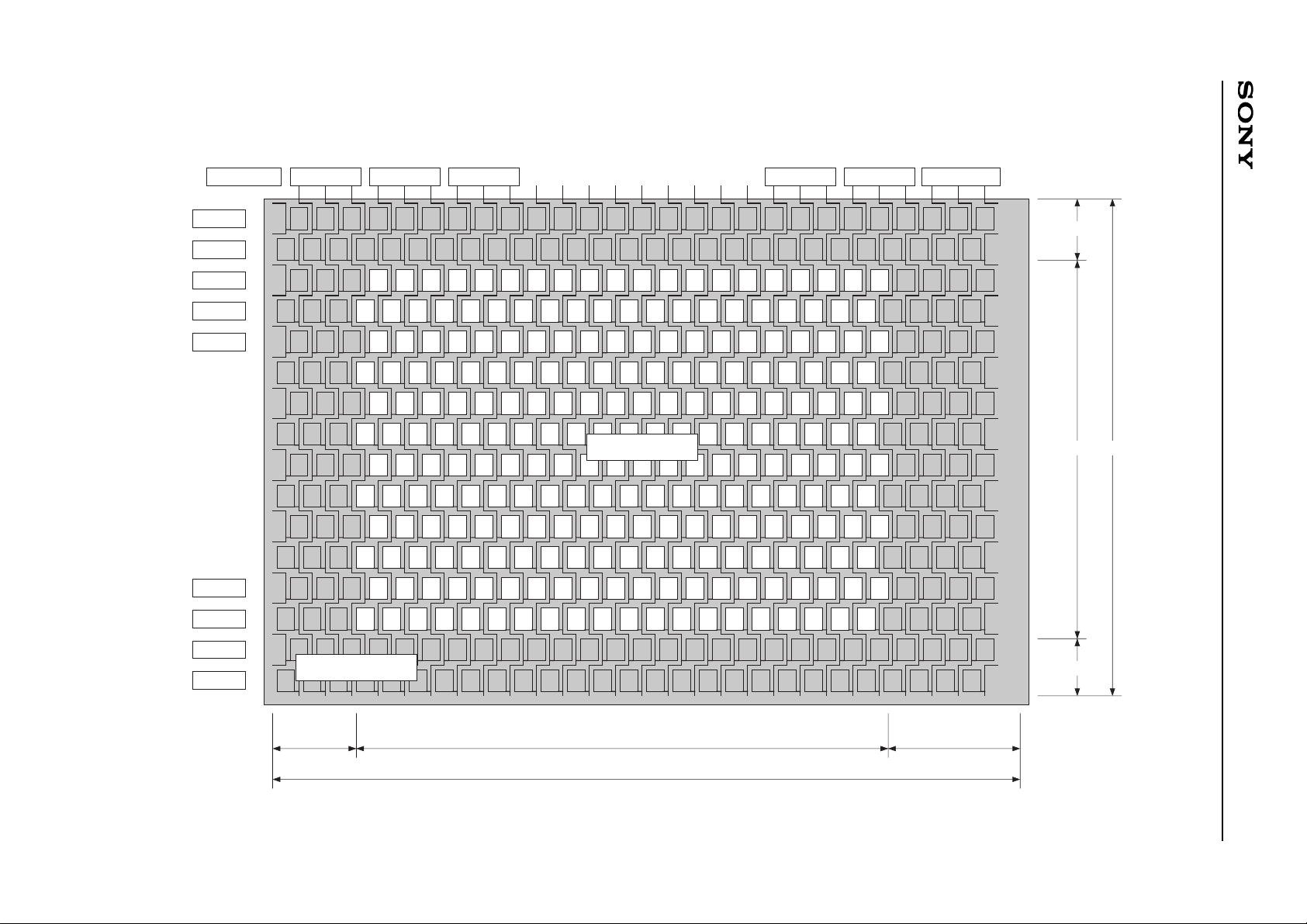

LCX005BK/BKB, LCX024AK Pixel Arrangement

G B R G

B R G B

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R G

B R G B

B R G

R G B

B R G

R G B

G

B

G

B

G

B

G

B

G

B

G

B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B

R

B

R

B

R

B

R

B

R

B

R

B

R

B

R

R

R

R

R

R

R

R

R

G

G

G

G

G

G

G

G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

dummy2 to 5

Hout175Hout174Hout2Hout1 Hout3

dummy1

Drive display area

Photo-shielding area

218 222

521

133

537

2

2

dummy1

Vout1

Vout2

Vout3

Vout218

dummy3

dummy4

dummy2

Vout217

– 8 –

CXD2458AR

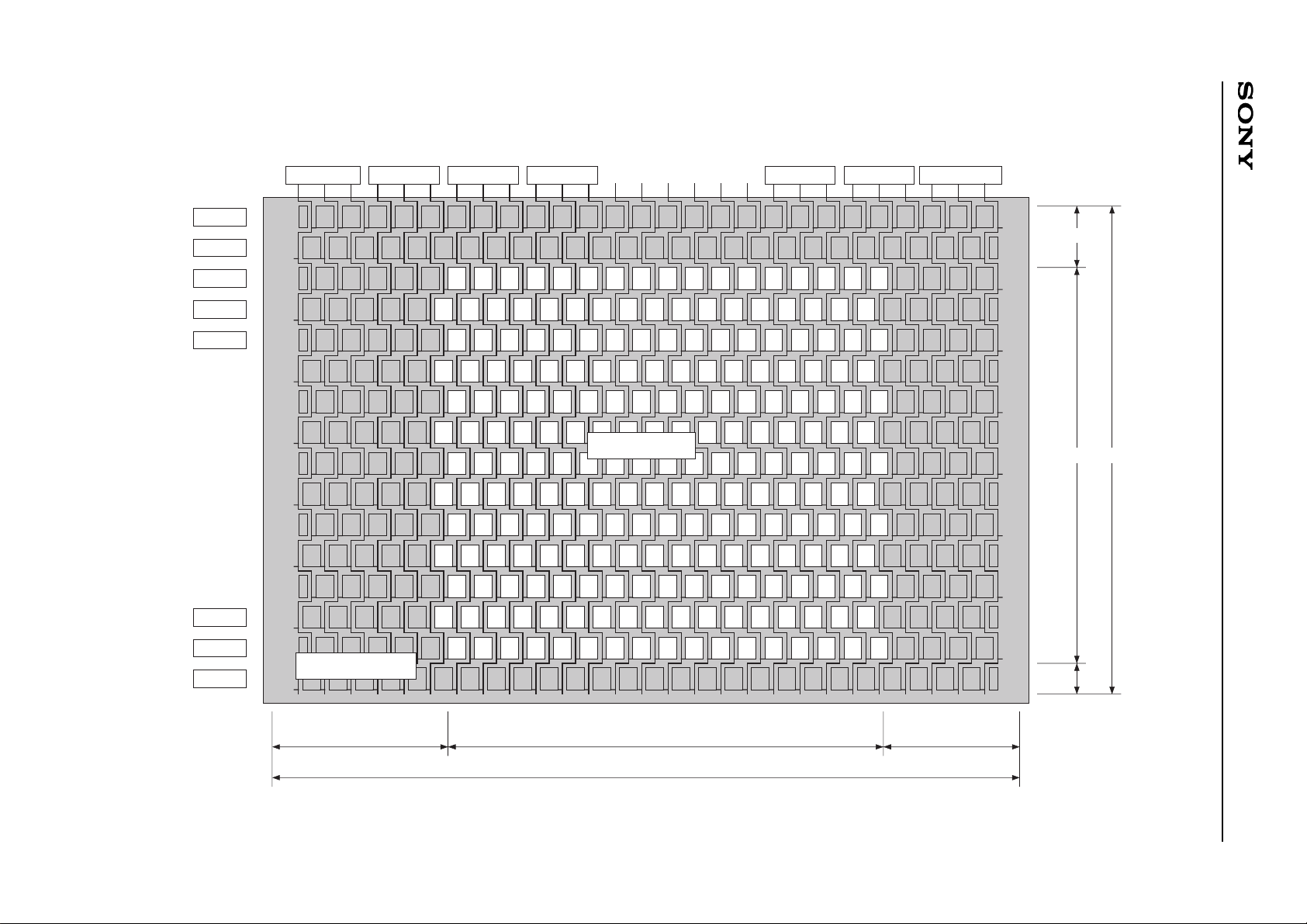

LCX009AK/AKB, LCX027AK Pixel Arrangement

B R G

R G B

B R

R G

B R

R G

B R

R G

B R

R G

B R

R G

B R

R G

B R G

R G B

B R G

R G B

B R G

R G B

G

B

G

B

G

B

G

B

G

B

G

B

B R

R G

B R

R G

B R

R G

B R

R G

B R

R G

B R

R G

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B

R

B

R

G B R G B R G B R G B R G B R G B

B R G B R G B R G B R G B R G B R

G

B

G

B

G

B

G

B

G

B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B R G

R G B

B

R

B

R

B

R

B

R

B

R

R

R

R

R

R

R

R

R

G

G

G

G

G

G

G

G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

G B R

B R G

dummy5 to 8

Hout268Hout267Hout2Hout1 Hout3

dummy1 to 4

dummy1

Vout1

Vout2

Vout3

Vout224

Vout225

dummy3

dummy2

Photo-shielding area

225 228

800 1314

827

1

2

Drive display area

– 9 –

CXD2458AR

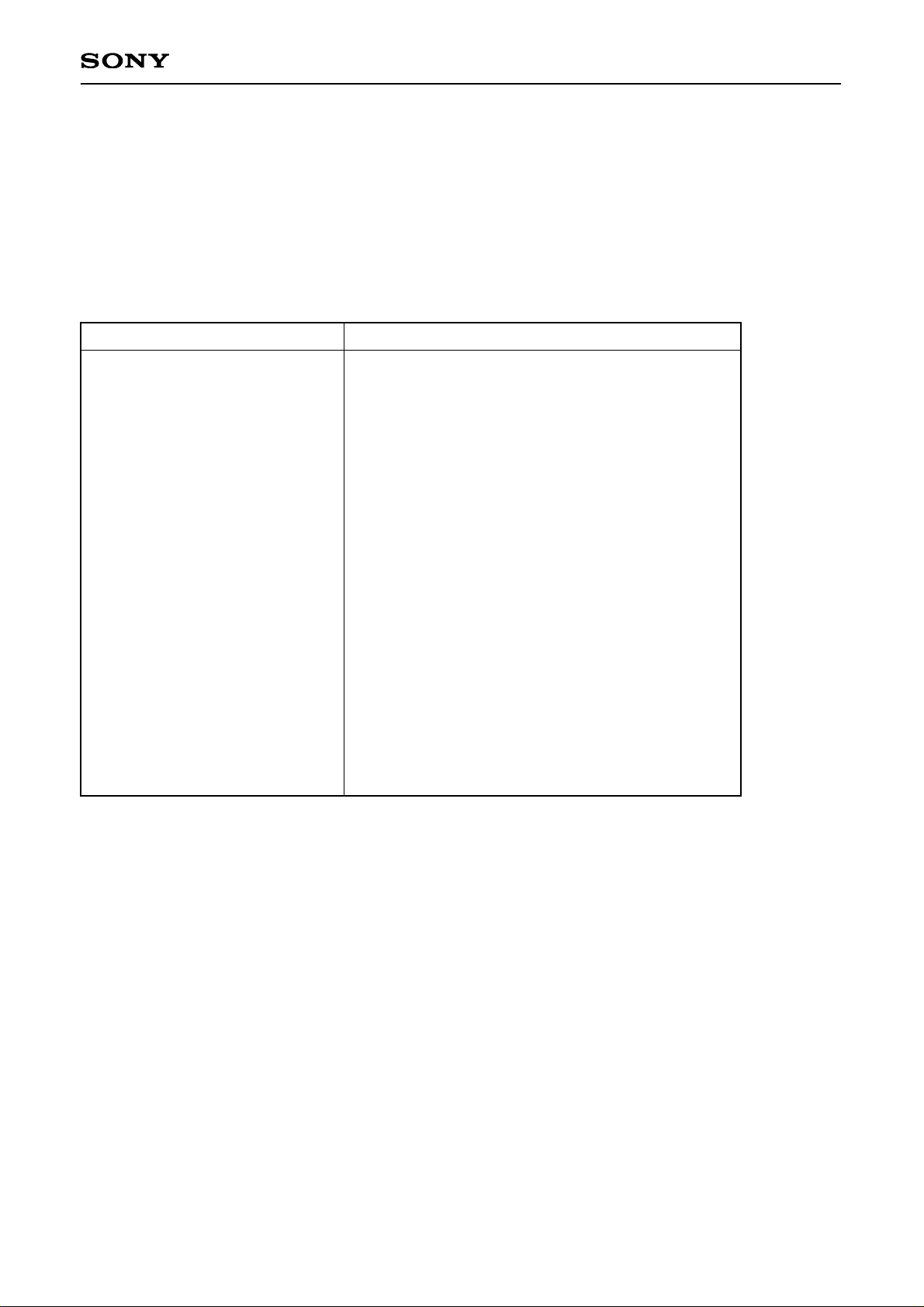

Description of Mode Selection Switch (SLCK, SLTM, SLNP, PLNT, WIDE)

SLCK

H

H

H

H

H

H

H

H

L

L

L

L

L

L

L

L

SLTM

X

X

X

X

X

X

X

X

L

L

L

L

H

H

H

H

SLNP

L

L

L

L

H

H

H

H

X

X

X

X

X

X

X

X

PLNT

L

L

H

H

L

L

H

H

L

L

H

H

L

L

H

H

WIDE

L

H

L

H

L

H

L

H

L

H

L

H

L

H

L

H

MODE

LCX005BK/BKB, NTSC, NORMAL

LCX005BK/BKB, NTSC, WIDE

LCX005BK/BKB, PAL, NORMAL

LCX005BK/BKB, PAL, WIDE

LCX024AK, NTSC, NORMAL

LCX024AK, NTSC, WIDE

LCX024AK, PAL, NORMAL

LCX024AK, PAL, WIDE

LCX009AK/AKB, NTSC, NORMAL

LCX009AK/AKB, NTSC, WIDE

LCX009AK/AKB, PAL, NORMAL

LCX009AK/AKB, PAL, WIDE

LCX027AK, NTSC, NORMAL

LCX027AK, NTSC, WIDE

LCX027AK, PAL, NORMAL

LCX027AK, PAL, WIDE

∗

NORMAL (4:3 display), WIDE (16:9 display)

∗X: Don't Care

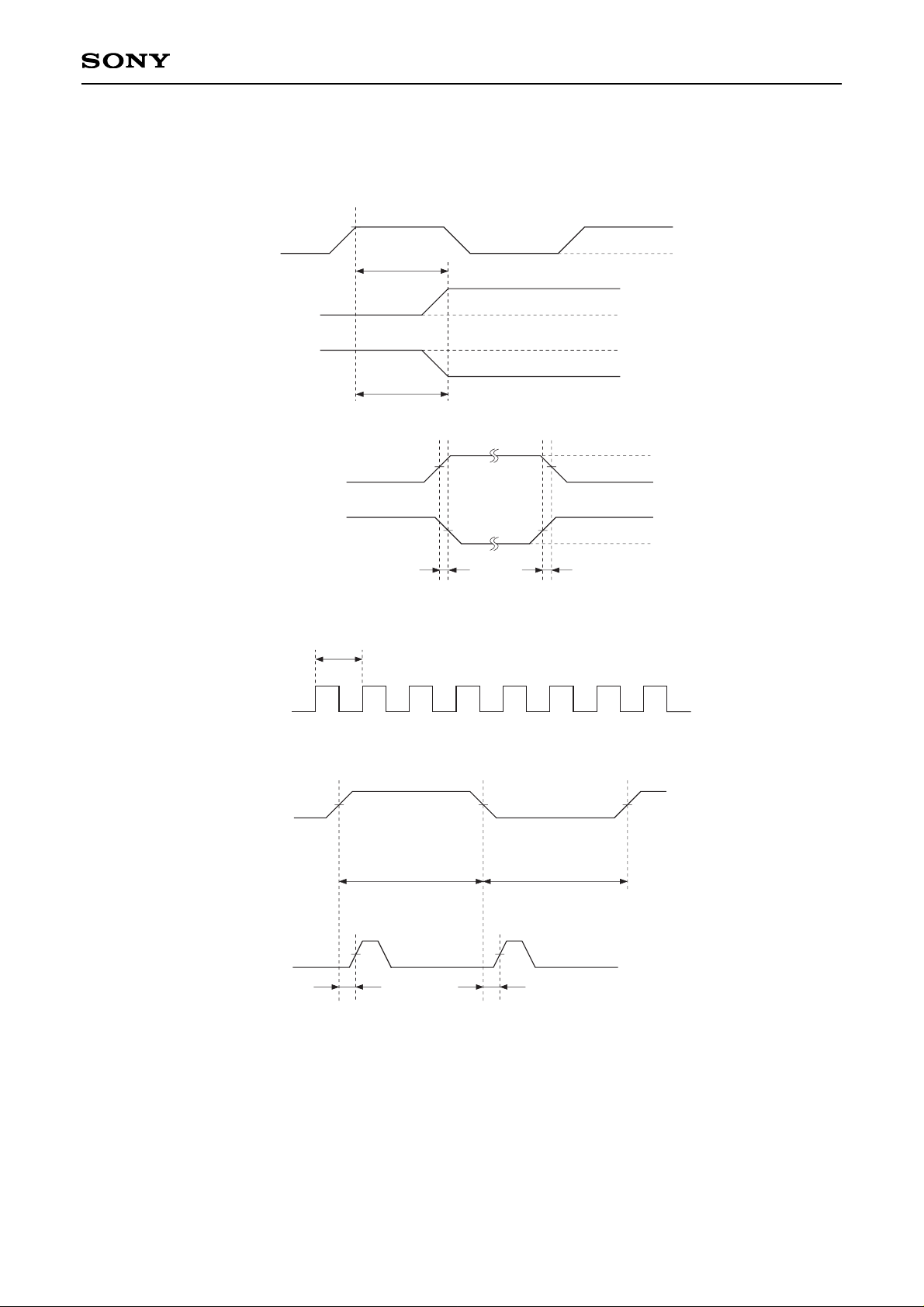

SLFR

SLFR is the selector switch for the AC drive timing pulse (FRP). This switch selects field inversion when H and

line inversion when L. Normally, line inversion (L) is used. The transition point is one clock cycle after the

transition point of the VCK1 and VCK2 pulses.

1H

1Field

1Field

1H

1H inversion

(2H cycle)

1F inversion

(2F cycle)

∗

FRP polarity is not specified.

FRP

1H 1H

– 10 –

CXD2458AR

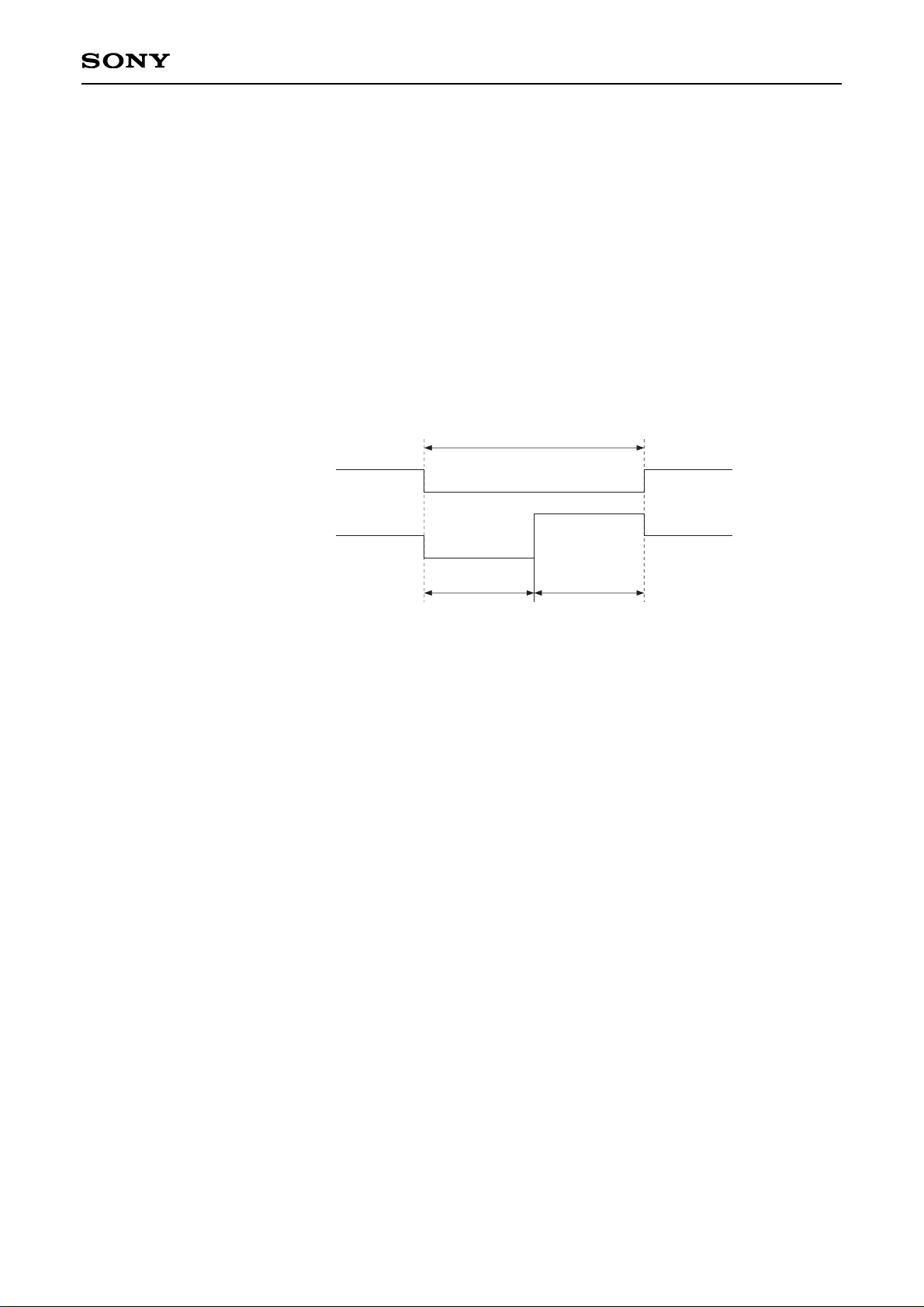

AFC Circuit (PLL Method)

The CXD2458AR employs the PLL method in order to achieve phase synchronization with the input sync

signal.

The PLL circuit phase comparator and frequency division counter are built in, and a fully synchronized AFC

circuit is comprised by connecting an external VCO circuit and LPF.

PLL errors are detected at the following timing.

The phase comparison output of the entire bottom of XHD or the horizontal sync signal of composite SYNC

and the internal H counter becomes RPD. RPD output is converted to DC error with the lag-lead filter (LPF),

and then it changes the varicap capacitance to stabilize the oscillating frequency at 702fh in the

LCX005BK/BKB and LCX024AK, and 1050fh in the LCX009AK/AKB and LCX027AK.

This PLL circuit is adjusted by setting the RPD transition point so that it sets in the center of the window (XHD

or horizontal sync signal of composite SYNC) as shown in the figure below.

XHD or horizontal sync signal of

composite SYNC

4.7µs

RPD

WL WH

WL = WH

AC Driving for No Signal

HST1/2, HCK1/2, FRP, VCK1/2, XCLP, VST, HD, VD, SH1/2/3/4 and EN are made to run freely so that the

LCD panel is AC driven even when there are no input sync signals (XHD/XVD and composite SYNC).

During this time, the horizontal sync separation circuit stops and the PLL internal frequency division counter is

made to run freely. At the same time, the auxiliary V counter is used to create the reference pulse for

generating the free running VD and VST because the vertical sync separation circuit is also stopped.

The cycle of this V counter is set to 269H for NTSC and 321H for PAL. However, when there is no XVD

(VSYNC) input for 301H (NTSC) and 360H (PAL), the no signal state is assumed and the free running VD and

VST pulses are generated from the next field.

RPD is kept at high impedance when there is no signal in order to prevent the AFC circuit from causing phase

errors due to phase comparison.

System Clear (XCLR)

The entire logic is initialized by setting XCLR = L. Be sure to perform this operation during power-on and after

changing the STBY pin from L to H. When this function is activated the outputs (XCLP, HD, FRP, VST, VD,

CLR, EN, HST1/2, HCK1/2, SH1/2/3/4, VCK1/2, FLDO, SBLK and BLK) go to L.

– 11 –

CXD2458AR

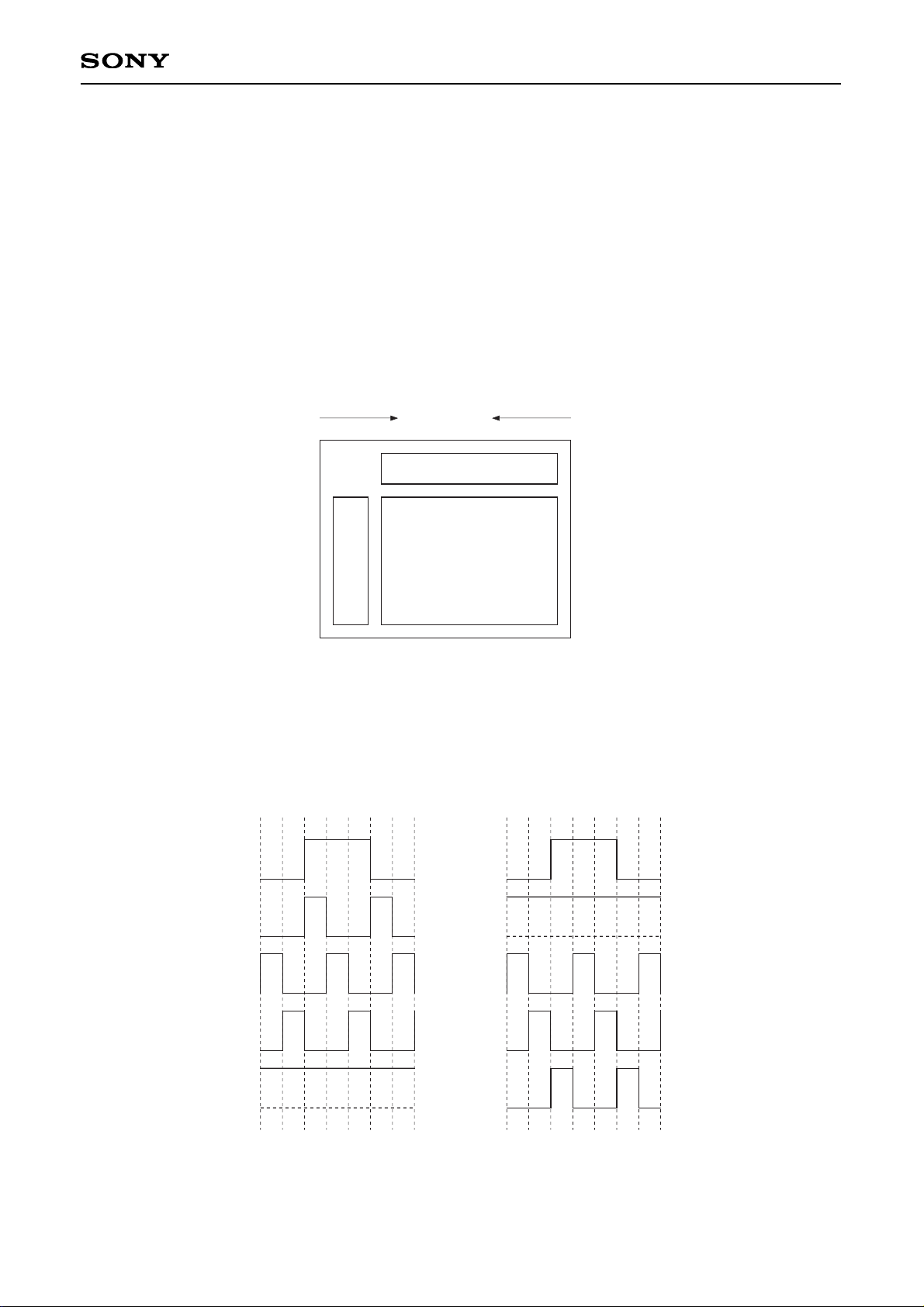

Right/Left Inverse Display

The CXD2458AR outputs a right/left inversion timing pulse that supports the right/left inverse display function

of the LCX005BK/BKB, LCX024AK, LCX009AK/AKB and LCX027AK.

The LCD panel is arranged in a delta pattern, where the same signal line is 1.5-dot offset at adjoining vertical

lines. For this reason, a 1.5-dot offset is attached to the horizontal start pulse (HST) of the LCD between odd

lines and even lines in order to correct this difference. Other H system output pulses are also 1.5-dot offset.

When the panel is driven with left scan (Reverse scan), this offset relationship becomes inverted for even and

odd lines, and the asymmetrical dot arrangement produces an offset.

Therefore, the CXD2458AR internally controls the right/left and interline offset to allow right scan or left scan

display by setting RGT = H or L for right/left inversion.

Left scan

(Reverse scan)

Right scan

(Normal scan)

Display area

H SCANNER

V SCANNER

SH Pulse and HCK Phase Relationship

The phase relationship between the SH pulse and HCK changes according to switching between right scan

(Normal scan) and left scan (Reverse scan). SH3 is the re-sampling pulse.

RGT = H (Normal scan) RGT = L (Reverse scan)

HCK1/2

SH1

SH2

SH3

SH4

– 12 –

CXD2458AR

16:9 (WIDE) Display Mode

Setting the WIDE pin to H shifts the unit to WIDE display mode. In this mode, the aspect ratio is converted

through pulse eliminator processing, allowing 16:9 quasi-WIDE display.

Vertical pulse eliminator scanning of 1/4 (NTSC) and 2/6 (PAL) for the LCX005BK/BKB and LCX009AK/AKB,

and 1/4 (NTSC) and 10/28 (PAL) for the LCX024AK and LCX027AK is performed, and the video signal is

compressed in the display area compared to 4:3 display to achieve 16:9 (WIDE) display. In addition, in areas

outside the display area, vertical high-speed scanning is performed and black signals are written to the black

display area in the upper 28 lines and the lower 27 or 28 lines. During this period, the FRP and HST output

cycles are also changed, and EN and CLR are not output. In addition, the SBLK output, which is the black

signal generation timing pulse, and the LCX024AK/LCX027AK black display area control signal BLK are both

H.

(For example, black display in the panel is permitted by connecting the SBLK output to the external RGB input

pin of the CXA1785AR.)

See the Timing Charts for details.

4:3 display

28 LINES

(28 LINES)

218 LINES

(225 LINES)

Vertical pulse eliminator scanning

Vertical high speed scanning

16:9 display

Display area

163 LINES

(169 LINES)

27 LINES

(28 LINES)

Display area

Black display area

Black display area

∗

Numbers in parentheses are for the LCX009AK/AKB and LCX027AK.

Note) When the no signal status occurs during 16:9 (WIDE) display mode, 4:3 display mode results.

– 13 –

CXD2458AR

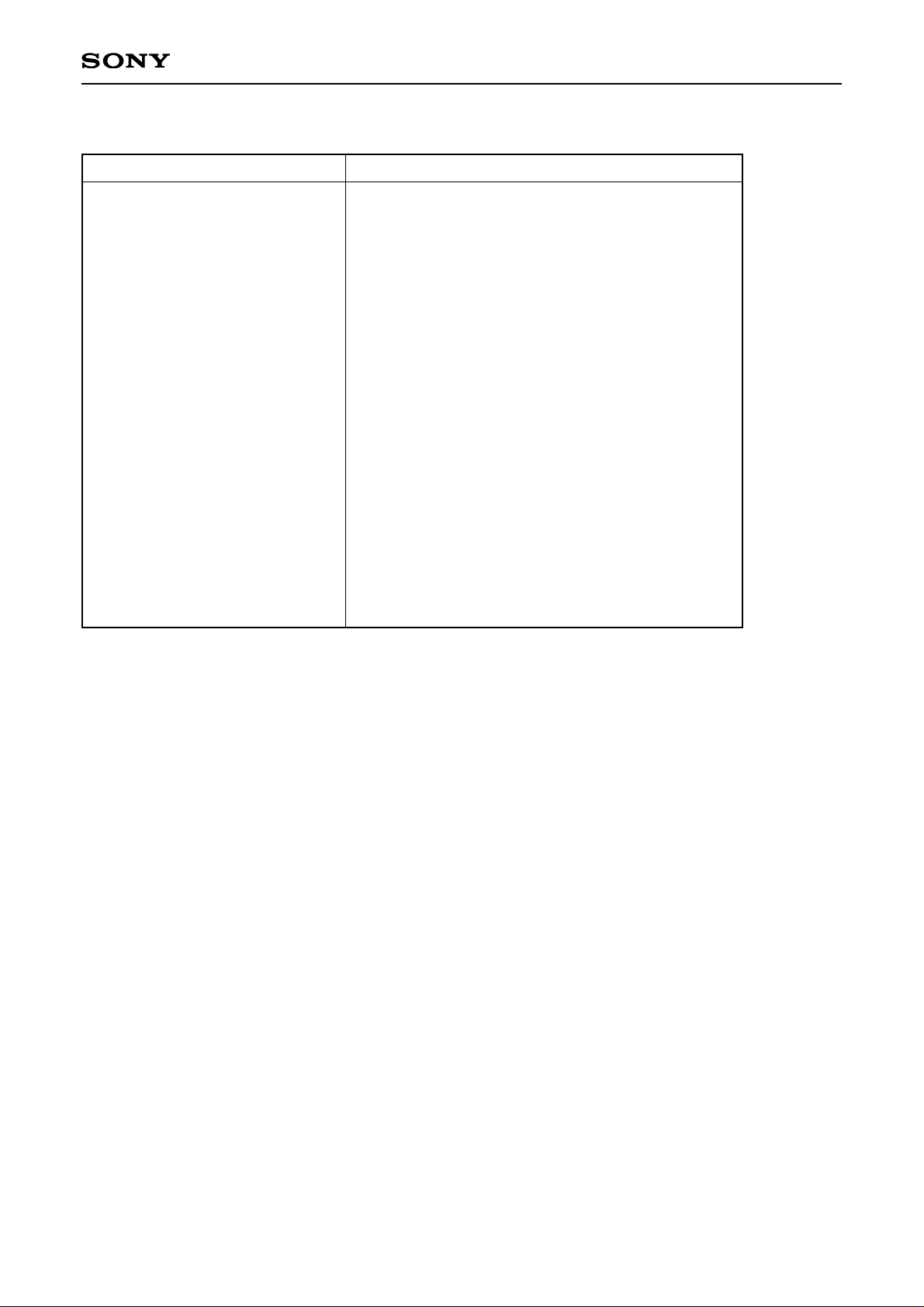

HP1, 2, 3, 4

These are selector switches for the horizontal display position. The HST timing can be set at 2fh intervals in 16

different ways by using the four HP1, 2, 3 and 4 bits. The picture center is set at internal preset value:

HP1/2/3/4: LLLH. However, because there is actually a difference between the RGB signal and the drive pulse

delays, the picture center may not match the design center. In this case, adjust with these switches.

The HST timing (from SYNC termination to the rising edge of HST) for even lines is shown below.

LCX005BK/BKB, LCX024AK (NTSC/PAL)

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

72fh (6.51/6.56µs)

70fh

68fh

66fh

64fh

62fh

60fh

58fh

56fh (5.06/5.11µs)

54fh

52fh

50fh

48fh

46fh

44fh

42fh (3.80/3.83µs)

74.5fh (6.74/6.79µs)

72.5fh

70.5fh

68.5fh

66.5fh

64.5fh

62.5fh

60.5fh

58.5fh (5.29/5.33µs)

56.5fh

54.5fh

52.5fh

50.5fh

48.5fh

46.5fh

44.5fh (4.02/4.06µs)

HP4 HP3 HP2 HP1

HST1 (NTSC/PAL) HST2 (NTSC/PAL)

∗

The HST1 and 2 timing for odd lines is 1.5fh delayed and 1.5fh advanced respectively from the above timings.

(See the Timing Charts for details.)

– 14 –

CXD2458AR

LCX009AK/AKB, LCX027AK (NTSC/PAL)

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

91fh (5.51/5.55µs)

89fh

87fh

85fh

83fh

81fh

79fh

77fh

75fh (4.54/4.57µs)

73fh

71fh

69fh

67fh

65fh

63fh

61fh (3.69/3.72µs)

93.5fh (5.66/5.70µs)

91.5fh

89.5fh

87.5fh

85.5fh

83.5fh

81.5fh

79.5fh

77.5fh (4.69/4.72µs)

75.5fh

73.5fh

71.5fh

69.5fh

67.5fh

65.5fh

63.5fh (3.84/3.87µs)

HP4 HP3 HP2 HP1

HST1 (NTSC/PAL) HST2 (NTSC/PAL)

∗

The HST1 and 2 timing for odd lines is 1.5fh delayed and 1.5fh advanced respectively from the above timings.

(See the Timing Charts for details.)

– 15 –

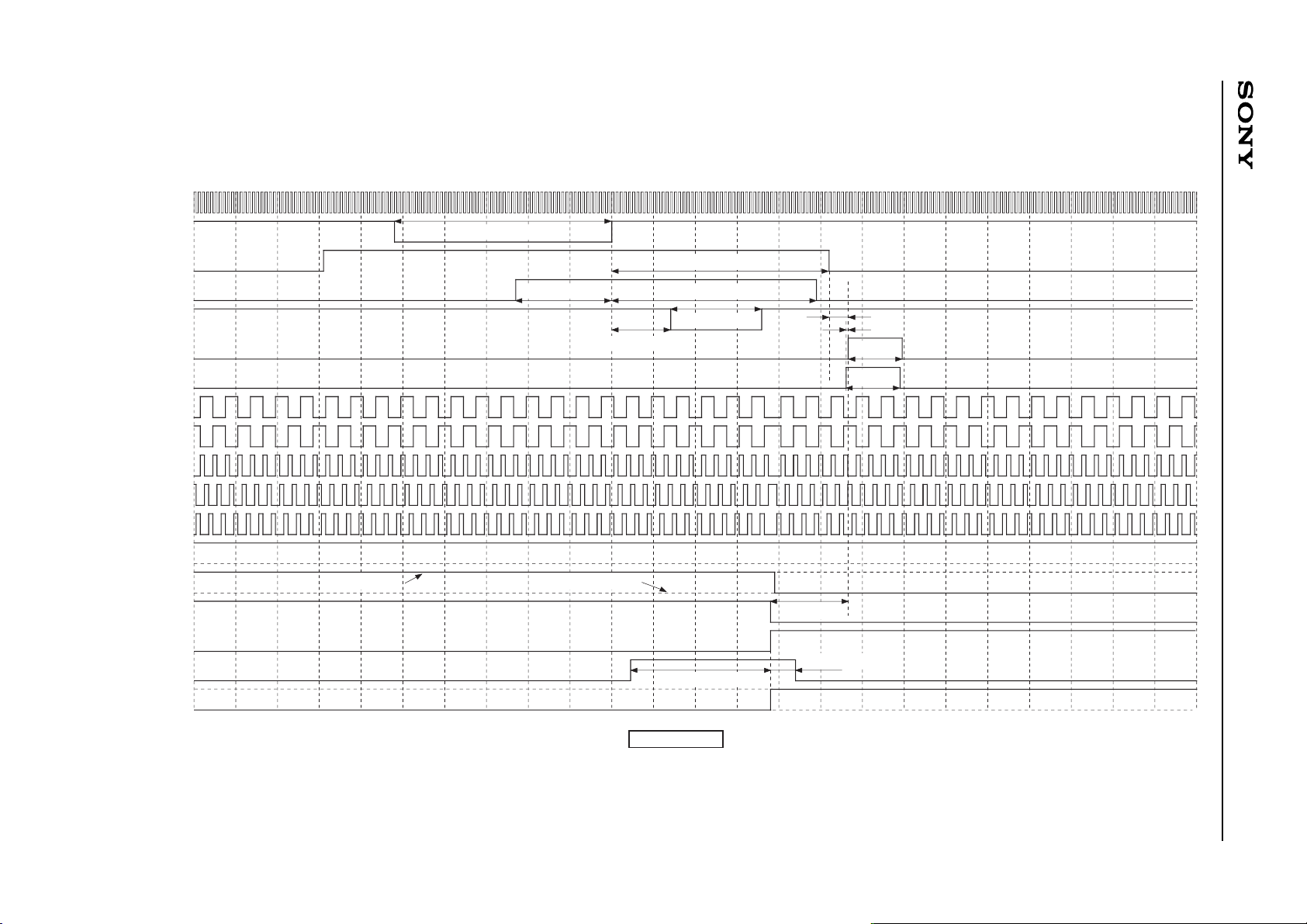

CXD2458AR

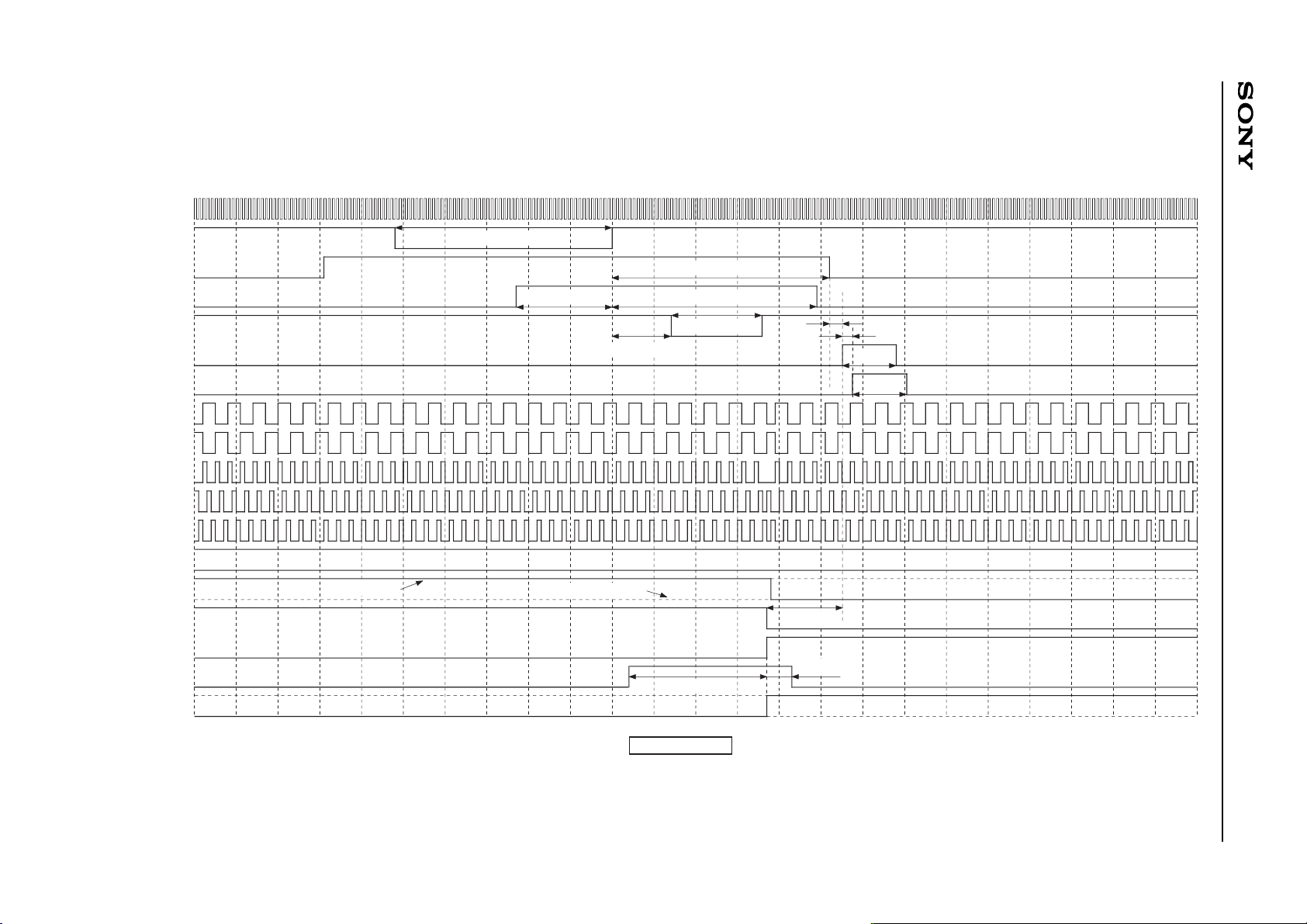

ODD LINE

Note) The third row of the timing chart "BLK" is a pulse indicated as a reference and is not a pulse output from pins.

FRP polarity is not specified for each line and field.

(BLK)

HD

XCLP

HST1

HCK2

SH1

SH3

SH2

SH4

FRP

VCK1

HST2

CLR

MCK

XHD

HCK1

VCK2

EN

HP1/2/3/4: LLLH

RGT: H (Normal scan)

4.7µs (52fh)

4.7µs (52fh)

ODD FIELD

EVEN FIELD

2.1µs (23fh)

4.4µs (49fh)

1.3µs (14fh)

2.0µs (22fh)

4.5fh

0.5fh

13fh

13fh

18.5fh

3.0µs (33fh)

0.5µs (6fh)

LCX005BK/BKB, LCX024AK Horizontal Direction Timing Chart

NTSC/PAL

– 16 –

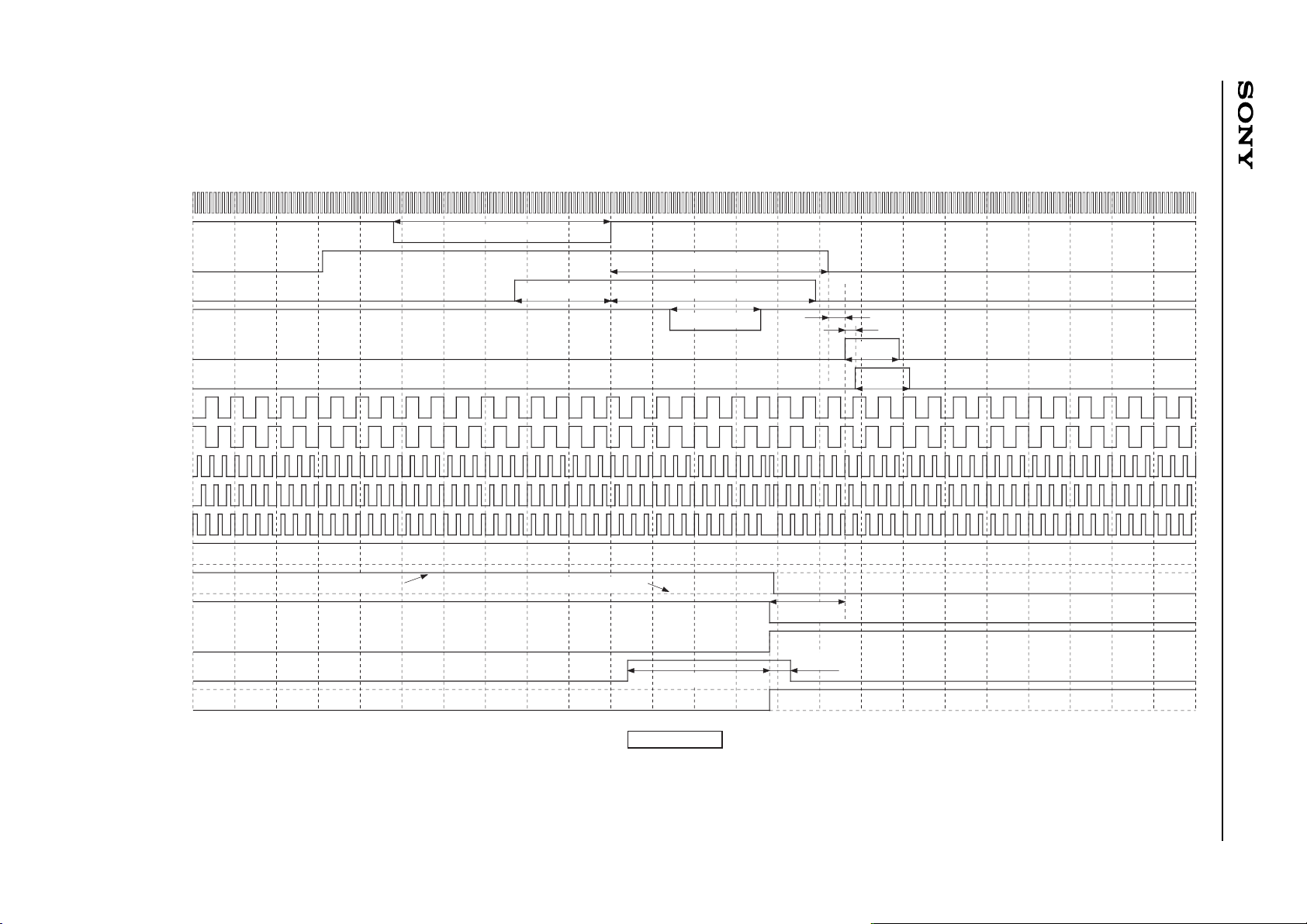

CXD2458AR

EVEN LINE

Note) The third row of the timing chart "BLK" is a pulse indicated as a reference and is not a pulse output from pins.

FRP polarity is not specified for each line and field.

(BLK)

HD

XCLP

HST1

HCK2

SH1

SH3

SH2

SH4

FRP

VCK1

HST2

CLR

MCK

HCK1

VCK2

EN

4.7µs (52fh)

4.7µs (52fh)

ODD FIELD

EVEN FIELD

2.1µs (23fh) 4.4µs (49fh)

1.3µs (14fh)

2.0µs (22fh)

3.0fh

2.5fh

13fh

13fh

18.0fh

0.5µs (6fh)

3.0µs (33fh)

XHD

HP1/2/3/4: LLLH

RGT: H (Normal scan)

LCX005BK/BKB, LCX024AK Horizontal Direction Timing Chart

NTSC/PAL

– 17 –

CXD2458AR

ODD LINE

Note) The third row of the timing chart "BLK" is a pulse indicated as a reference and is not a pulse output from pins.

FRP polarity is not specified for each line and field.

(BLK)

HD

XCLP

HST1

HCK2

SH1

SH3

SH2

SH4

FRP

VCK1

HST2

CLR

MCK

HCK1

VCK2

EN

HP1/2/3/4: LLLH

RGT: L (Reverse scan)

4.7µs (52fh)

4.7µs (52fh)

ODD FIELD

EVEN FIELD

2.1µs (23fh) 4.4µs (49fh)

2.0µs (22fh)

2.5fh

4.0fh

13fh

13fh

18.0fh

0.5µs (5fh)

3.0µs (34fh)

XHD

LCX005BK/BKB, LCX024AK Horizontal Direction Timing Chart

NTSC/PAL

Loading...

Loading...