Sony CXD2436Q Datasheet

Timing Generator for LCD Panels

For the availability of this product, please contact the sales office.

Description

The CXD2436Q is a timing signal generator for the

VGA LCD panel LCX012 driver. This chip has a

built-in serial interface circuit which allows the mode

to be switched with respect to various VGA signals

through direct control from an external

microcomputer, etc.

Features

• Generates the LCX012 drive pulse.

• Supports three-panel projectors.

• Built-in serial interface circuit

• Supports various VGA signals. (non-interlaced

mode)

• Built-in 2-line pair drive circuits

• Supports NTSC and PAL systems.

• Supports up/down and/or right/left inversion.

• Supports line inversion and field inversion.

• Generates timing signal of external sample-and-

hold circuit.

Applications

LCD projectors, etc.

CXD2436Q

100 pin QFP (Plastic)

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VDD VSS–0.5 to +7.0 V

• Input voltage VI VSS–0.5 to VDD+0.5 V

• Output voltage VO VSS–0.5 to VDD+0.5 V

• Operating temperature

Topr –20 to +75 °C

• Storage temperature

Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage VDD +4.5 to +5.5 V

• Supply voltage VCC –20 to +75 °C

Structure

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

—1—

E95810-TE

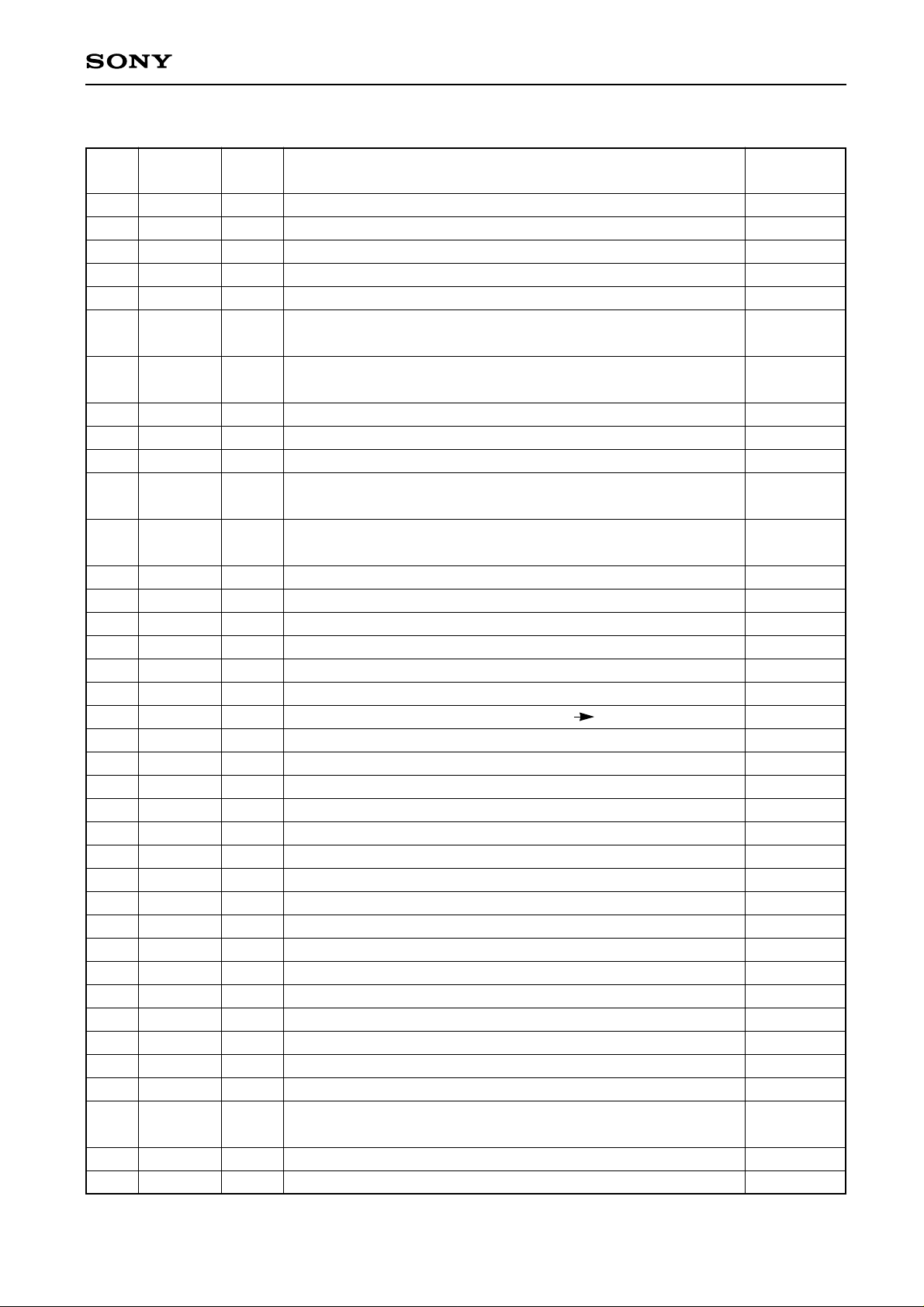

Block Diagram

CXD2436Q

EXT-CKI

CKI

CKO

HPOL

VPOL

CSYNC

HD2IN

VD2IN

HD1IN

VD1IN

TST1

TST2

TST3

TST4

TST5

TST6

TST7

TST8

TST9

TST10

VCK

VST1

VDO

SLDWN

SLMNB

DWN

PRG

XCLP1

XCLP2

HST

HCK1

HCK2

CLR

ENB

INT

PCG

SH1

SH2

SH3

SH4

SH5

SH6

SH7

30

34

33

16

17

14

20

21

23

24

25

26

27

37

50

92

93

72

11

19

71

75

76

77

84

85

86

87

88

89

91

94

95

96

97

98

99

100

283 53 78 4 15 29 40 42 45 46 47 48 49 51 52 54 65 79 90 22

SS

SS

SS

SS

SS

SS

SS

DD

DD

V

DD

V

V

SS

DD

V

V

SS

SS

V

V

SS

SS

V

V

V

V

V

V

V

V

V

MASTER CLOCK

6

7

PLL PHASE COMPARATOR

5

H-SYNC DETECTOR

H-SKEW DETECTOR

1

2

PLL COUNTER

V-SYNC SEPARATOR

V-RESET PULSE GENERATOR

SERIAL INTERFACE

V-RESET PULSE GENERATOR

V-POSITION COUNTER

V-TIMING PULSE

H-POSITION COUNTER

H-TIMING PULSE

GENERATOR

&

PULSE ELIMINATOR

FIELD & LINE CONTROLLER

AUX-VD COUNTER

SS

V

SS

SS

V

V

DIRECT CLEAR

GENERATOR

PWM

SS

NC

V

32

31

8

9

10

18

36

35

38

39

68

69

73

74

41

43

44

55

56

57

58

59

60

61

62

63

64

66

67

12

82

83

80

81

70

13

PEO

XCLR

PLNT

VGAV

SLSY

SLCKI

RPD

FPD

TC

HDN

XHDN

HDO

XHDO

SCK

SI

CS

PO0

PO1

PO2

PO3

PO4

PO5

PO6

PO7

PO8

PO9

PO10

PO11

SLRGT

RGT

XRGT

FRP

XFRP

FLD

SLFR

—2—

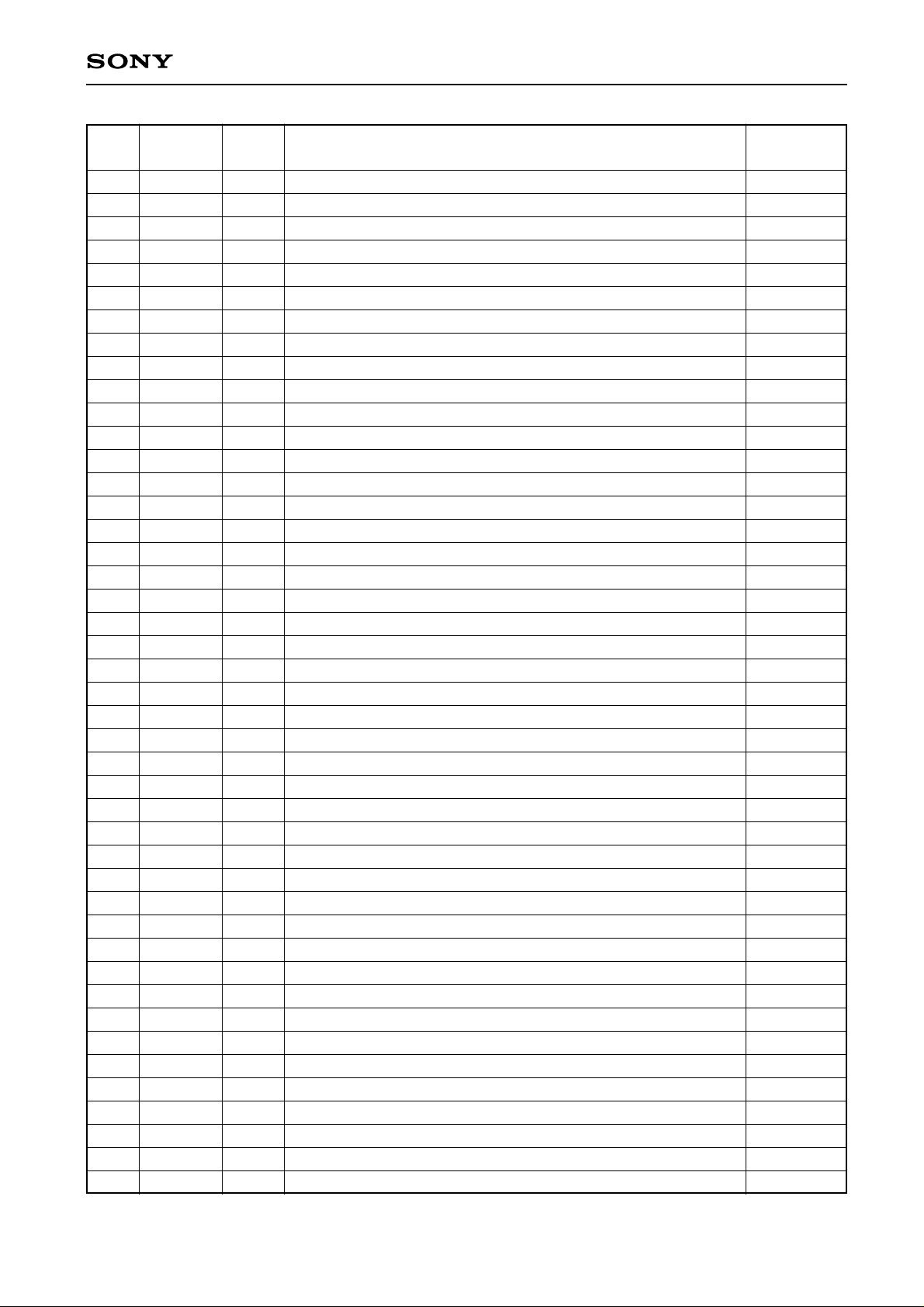

Pin Description

CXD2436Q

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

Symbol

HD1IN

VD1IN

VDD

VSS

CSYNC

HPOL

VPOL

XCLR

PLNT

VGAV

SLDWN

SLRGT

SLFR

TST1

VSS

HD2IN

VD2IN

SLSY

SLMNB

TST2

TST3

N.C.

TST4

TST5

TST6

TST7

TST8

VDD

VSS

EXT-CKI

PEO

PWM

CKO

CKI

RPD

SLCKI

TST9

FPD

I/O

I

I

—

—

I

I

I

I

I

I

I

I

I

I

—

I

I

I

I

I

I

—

—

—

—

—

—

—

—

I

I/O

I

I/O

I

O

I

I

O

Description

Hsync input (VGA)

Vsync input (VGA)

Power supply

GND

Composite sync input (NTSC/PAL)

HD, CSYNC polarity identification input

(High: positive polarity, Low: negative polarity)

VD, CSYNC polarity identification input

(High: positive polarity, Low: negative polarity)

External clear (all clear when Low)

PAL/NTSC switching (High: NTSC, Low: PAL)

VGA (NTSC/PAL) switching (High: VGA, Low: NTSC/PAL)

Up/down inversion discrimination signal input

(High: Down, Low: Up)

Right/left inversion discrimination signal input

(High: Normal, Low: Reverse)

1H/1F inversion switching (High: 1H, Low: 1F)

Test pin (Not connected or High.)

GND

HD2 input (for NTSC/PAL separate-sync)

VD2 input (for NTSC/PAL separate-sync)

SYNC input switching (High: CSYNC, Low: HD2IN and VD2IN)

Switches mode (High: Nothing, Low: 400 480 line conversion)

Test pin (Not connected or High.)

Test pin (Connect to GND.)

N.C.

Test pin (Not connected or High.)

Test pin (Not connected or High.)

Test pin (Not connected or High.)

Test pin (Not connected.)

Test pin (Connect to GND.)

Power supply

GND

External clock input

Loop filter integrator output

Loop filter integrator input

Oscillation cell output (NTSC/PAL)

Oscillation cell input (NTSC/PAL)

Phase comparator output (NTSC/PAL)

Clock input selection (High: CKI, Low: EXT-CKI)

(NTSC/PAL mode only)

Test pin (Not connected or High.)

Phase comparator output (NTSC/PAL)

Input pin for

open status

—

—

—

—

—

H

H

H

H

H

H

H

H

H

—

—

—

H

H

H

H

—

—

—

—

—

—

—

—

—

—

—

—

—

—

H

H

—

—3—

CXD2436Q

Pin

No.

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

Symbol

TC

VSS

SCK

VSS

SI

CS

VSS

VSS

VSS

VSS

VSS

TST10

VSS

VSS

VDD

VSS

PO0

PO1

PO2

PO3

PO4

PO5

PO6

PO7

PO8

PO9

VSS

PO10

PO11

HDN

XHDN

FLD

DWM

VDO

HDO

XHDO

PRG

XCLP1

XCLP2

VDD

VSS

FRP

XFRP

RGT

I/O

I/O

—

I

—

I

I

—

—

—

—

—

I

—

—

—

—

O

O

O

O

O

O

O

O

O

O

—

O

O

O

O

O

O

O

O

O

O

O

O

—

—

O

O

O

Description

FPD pin pulse width adjustment

GND

Serial interface clock input

GND

Serial interface data input

Serial interface chip select

GND

GND

GND

GND

GND

Test pin (Not connected or High.)

GND

GND

Power supply

GND

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

Serial I/O data output

GND

Serial I/O data output

Serial I/O data output

Phase comparator output (positive polarity)

Phase comparator output (negative polarity)

Field discrimination signal output

Up/down inversion discrimination signal output

VD pulse output (positive polarity)

HD pulse output (positive polarity)

HD pulse output (negative polarity)

Precharge signal pulse (positive polarity)

Pedestal clamp pulse 1

Pedestal clamp pulse 2

Power supply

GND

AC drive inversion timing output

AC drive inversion timing output

Right/left inversion discrimination signal output

Input pin for

open status

—

—

H

—

L

H

—

—

—

—

—

H

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—4—

CXD2436Q

Pin

No.

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

Symbol

XRGT

HST

HCK1

HCK2

CLR

ENB

INT

VSS

PCG

VCK

VST1

SH1

SH2

SH3

SH4

SH5

SH6

SH7

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

Description

Right/left inversion discrimination signal output

H start pulse output (positive polarity)

H clock pulse 1 output

H clock pulse 2 output

CLR pin output

ENB pin output

INT pin output

GND

PCG pin output (positive polarity)

V clock pulse output

V start pulse output

Sample-and-hold pulse 1 (positive polarity)

Sample-and-hold pulse 2 (positive polarity)

Sample-and-hold pulse 3 (positive polarity)

Sample-and-hold pulse 4 (positive polarity)

Sample-and-hold pulse 5 (positive polarity)

Sample-and-hold pulse 6 (positive polarity)

Sample-and-hold pulse 7 (positive polarity)

Input pin for

open status

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Electrical Characteristics

1. DC characteristics (Temperature = 25 °C, VSS = 0 V)

Item Symbol Conditions Min. Typ. Max. Unit Applicable pins

Supply voltage

Input voltage 1

Input voltage 2

Output voltage 1

Output voltage 2

Output voltage 3

Output voltage 4

Input leak

current

Output leak

current

Current

consumption

VDD

VIH1

VIL1

VIH2

VIL2

VT+ –VT+

VOH

VOL

VOH

VOL

VOH

VOL

VOH

VOL

IIL

IIH

ILZ

IDD

CMOS input cell

CMOS Schmitt

0.7 VDD

0.8 VDD

trigger input cell

IOH=–2 mA

VDD–0.8

IOL=4 mA

IOH=–4 mA

VDD–0.8

IOL=8 mA

IOH=–6 mA

VDD–0.8

IOL=12 mA

IOH=–3 mA

VDD/2

IOL=3 mA

Pull-up resistor connected

Pull-down resistor connected

High impedance

status

fclk=31 MHz

VDD=5.0 V

4.5

–40

40

–40

5.0

0.6

–100

100

55

5.5

0.3 VDD

0.2 VDD

0.4

0.4

0.4

VDD/2

–240

240

40

V

Input pins other than

V

those noted below

HDnIN, VDnIN, CSYNC,

CKI, PWM, TC, PEO,

V

CKO, SI, SCK, CS

Output pins other than

V

those noted below

VCK

V

HCKn, SHn, HST

V

CKO, PEO

V

∗1

µA

SI

RPD, FPD

µA

At no load

mA

∗1

Input pins with pull-up resistors

HPOL, VPOL, XCLR, PLNT, VGAV, SLDWN, SLRGT, SLFR, TST1, SLSY, TST2, TST3, SLCKI, TST9, SCK, CS

—5—

CXD2436Q

2. AC characteristics (VDD=5.0 V±0.5 V, VSS=0 V)

Item Applicable pins Symbol Conditions Min. Typ. Max. Unit

Clock input cycle

Cross-point time difference

Output rise delay

Output fall delay

Output rise delay

Output fall delay

HCK1, SH1 delay

time difference

HCK2, SH1 delay

time difference

HCK1 duty

HCK2 duty

EXT-CKI, CKI

HCK1, 2

HCKn, SHn

HCKn, SHn

Other than

HCKn and SHn

Other than

HCKn and SHn

HCK1, SH1

HCK2, SH1

HCK1

HCK2

∆t

tpr

tpf

tpr

tpf

dt1

dt2

tH/tH+tL

tH/tH+tL

CL=30 pF

CL=30 pF

CL=30 pF

CL=30 pF

CL=30 pF

CL=30 pF

CL=30 pF

CL=30 pF

CL=30 pF

25

–10

48

48

50

50

10

20

20

30

30

10

10

52

52

ns

ns

ns

ns

ns

ns

ns

ns

%

%

EXT-CKI/CKI

Output

Output

HCK1

50%

tpr

tpf

90%

10%

50%

VDD

0V

V

0V

VDD

0V

VDD

0V

DD

HCK2

V

DD

50%

∆t

50%

0V

∆t

—6—

EXT-CKI

/CKI

CXD2436Q

HCK1

HCK2

SH1

50% 50%

t1

tH

50%

dt1

3. Serial interface block AC characteristics

SCK

50%

tw1

t2

tL

50%

dt2

(SLRGT=H, SHP0/SHP1/SHP2/SHP3=L)

tw1

50%

50%

50%

50%

SI (DATA)

CS

50%

50%

ts0

ts1

th1

50%

50%

th0

(VDD=5.0 V±0.5 V, VSS=0 V, Topr=–20 to +75 °C

Symbol Item Min. Max.

ts1

th1

tw1

ts0

th0

th1

SI setup time with respect to rise of SCK

SI hold time with respect to rise of SCK

SCK pulse width

CS setup time with respect to rise of SCK

CS hold time with respect to rise of SCK

SCK high-level hold time with respect to rise of CS

200 ns

200 ns

200 ns

200 ns

200 ns

200 ns

2tw1

2tw1

th1

—7—

CXD2436Q

A

A

A

A

A

A

A

A

A

A

A

A

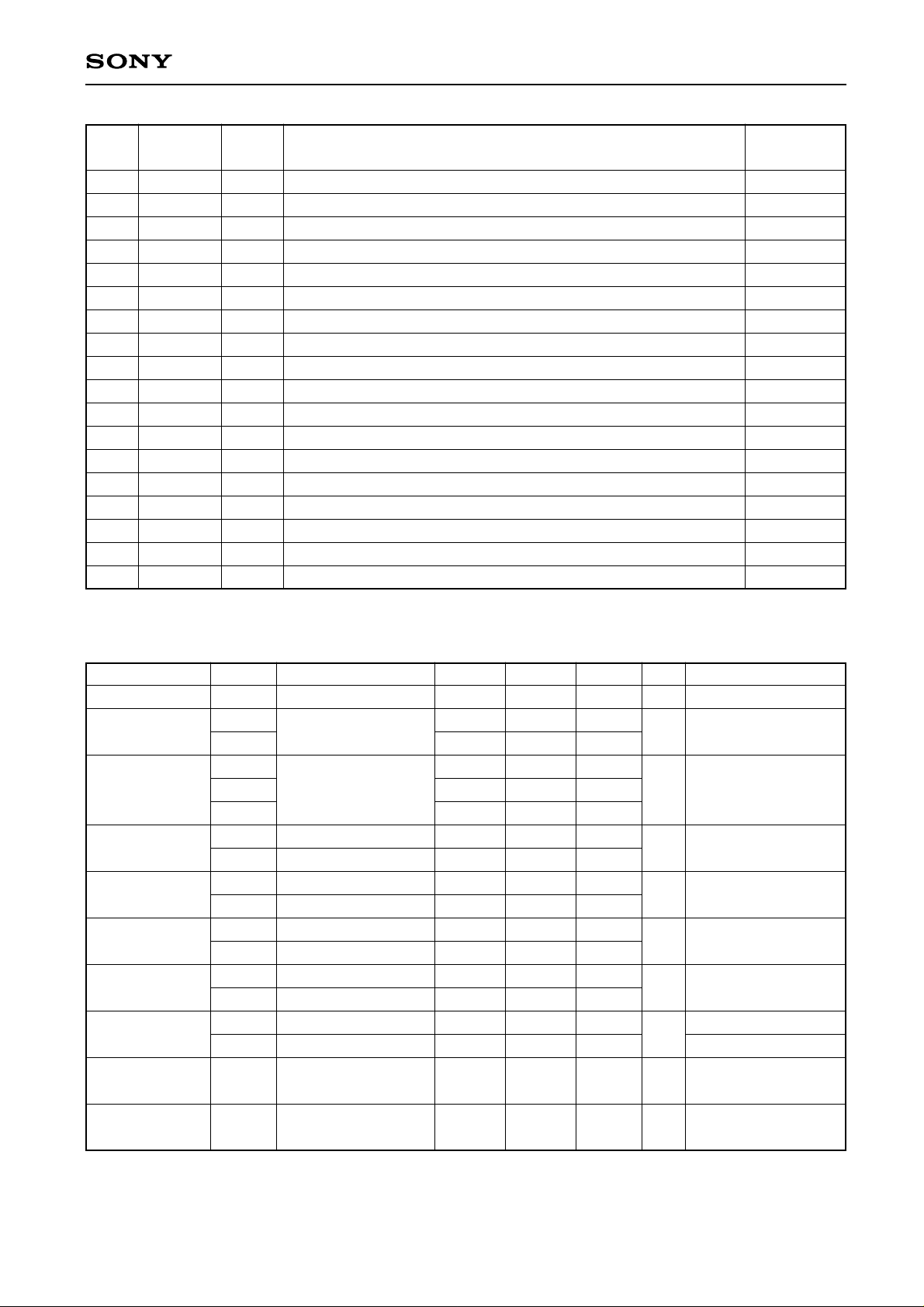

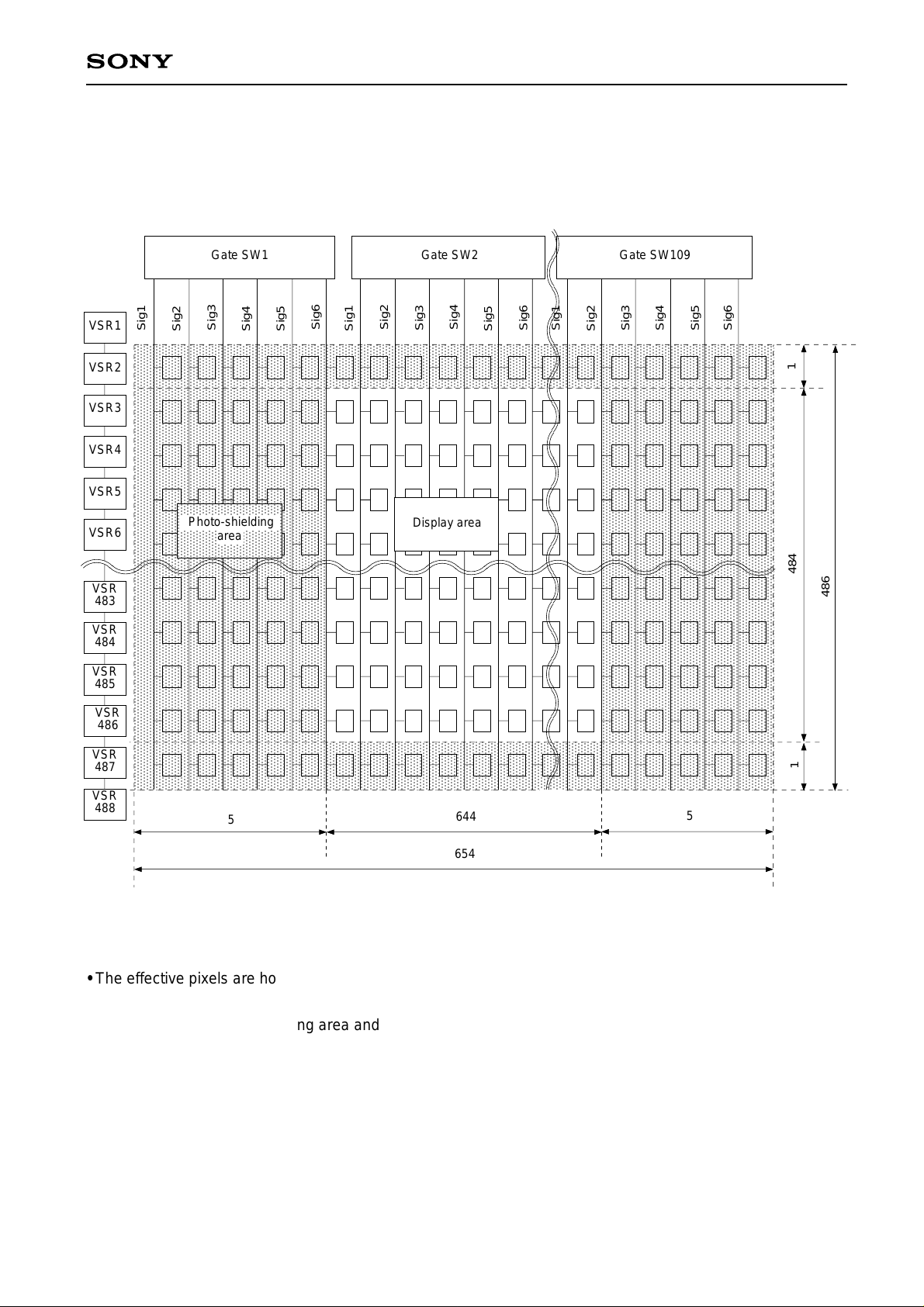

LCD Panel Structure

The structure of LCD panels (LCX012AL) driven by this IC is shown below.

The dot arrangement is a square arrangement, and the shaded region within the diagram is not displayed.

Gate SW1 Gate SW2 Gate SW109

VSR1

VSR2

VSR3

VSR4

VSR5

VSR6

VSR

483

VSR

484

VSR

485

VSR

486

VSR

487

VSR

488

Sig1

Sig2

Sig3

Sig4

Sig5

Sig6

Sig1

Sig2

Sig3

Sig4

Sig5

Sig6

Sig1

Sig2

Sig3

Sig4

Sig5

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

Photo-shielding

area

AAAAAAAAAAAAAAAA

AA

Display area

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

AAAAAAAAAAAAAAAA

5

644

5

Sig6

1

484

486

1

654

• The effective pixels are horizontal: 644 pixels and vertical: 484 pixels.

• The horizontal pixel start position is from Sig6 of the first-stage scanner. (Sig1 to Sig5 of the first-stage

scanner are the photo-shielding area and are not displayed.)

• The vertical pixel start position is from the third-stage scanner.

• These relationships are the same even during up/down and/or right/left inversion. (The entire area within the

panel is inverted.)

—8—

Description of Operation

• Sync input pins

The CXD2436Q has three types of sync input pins.

Pin No. Symbol SLSY setting Application

HD1IN

16

17

1

VD1IN

2

CSYNC

5

HD2IN

VD2IN

—

H

SYNC input pins for VGA

CSYNC input pin for NTSC/PAL

L

Separate SYNC input pins for NTSC/PAL

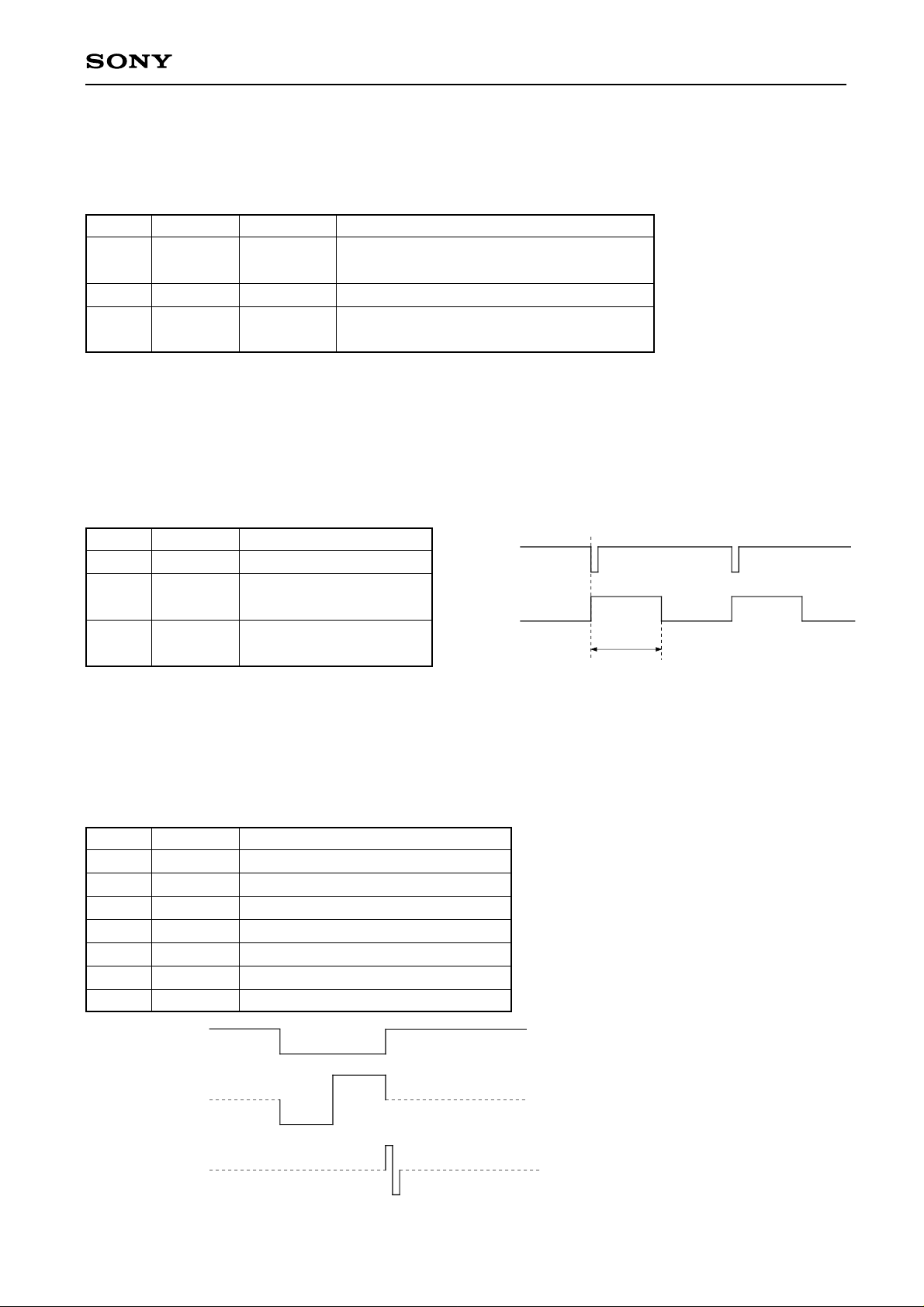

• Clock input pins

The CXD2436Q has two clock input pin systems to support two types of PLL circuits.

1) When using EXT-CKI (using an external PLL IC)

The 1/N frequency divider output is output from the HDN and XHDN pins for the external PLL IC.

The used pins are shown in the following table. (SLCKI = Low)

CXD2436Q

Pin No. Symbol Application

30

68

69

EXT-CKI

HDN

XHDN

Clock input

Phase comparison output

(positive polarity)

Phase comparison output

(negative polarity)

HSYNC

HDN OUTPUT

400 clk

2) When using CKI

This system uses the built-in phase comparator and an externally attached VCO circuit (see the Application

Circuit).

This system is used during AV mode (NTSC/PAL).

The used pins are shown in the following table. (Effective when SLCKI is set to High.)

Pin No. Symbol Application

31

32

33

34

35

38

39

PEO

PWM

CKO

CKI

RPD

FPD

TC

Loop filter integrator output

Loop filter integrator input

Clock output (oscillation cell output)

Clock input (oscillation cell input)

Phase comparator output

Phase comparator output

FPD pin pulse width adjustment

HSYNC

RPD

FPD

An outline of the output waveforms during

PLL lock is shown in the figure to the left.

—9—

CXD2436Q

• Connections supporting up/down and/or right/left inversion

The CXD2436Q is designed for use with three-panel projectors, and has a system configuration which

permits both normal and reverse scan. The RGT and XRGT output to the panel are switched according to

the SLRGT input, and the DWN output is switched according to the SLDWN input in the same manner.

SLRGT

SLDWN

12

11

Example of supporting a three-panel system

82

83

71

RGT

XRGT

DWN

LCX012

RGT

DWN

LCX012

RGT

DWN

LCX012

RGT

DWN

Normal scanning

panel

Normal scanning

panel

Reverse scanning

panel

• AC driving of LCD panels for no signal

The following measures have been adopted to allow AC driving of LCD panels even when there is no

signal.

• Horizontal direction pulse: The PLL is set to free running status. Therefore, the frequency of the

horizontal direction pulse is dependent on the PLL free running frequency.

• Vertical direction pulse: The number of lines is counted by an internal counter and VST and FRP

are output at a specified cycle.

• VST cycle for no signal • Free running detection timing

NTSC 269H

PAL 321H

VGA 526H

NTSC 291H

PAL 339H

VGA 873H

Free running operates at the following cycles.

(No signal is judged if there is no VSYNC input for longer than the following periods.)

• Description of the MODE selector switch

• VGA/AV (NTSC/PAL) switching is performed with two pins.

VGAV PLNT MODE

H H VGA

H L VGA

L H NTSC

L L PAL

• The HD1IN, HD2IN, VD1IN, VD2IN and CSYNC input polarities are supported by two pins.

HPOL VPOL

HD1IN VD1IN

HD2IN VD2IN

CSYNC

H H Positive polarity Positive polarity Positive polarity

H L Positive polarity Negative polarity —

L H Negative polarity Positive polarity —

L L Negative polarity Negative polarity Negative polarity

—10—

CXD2436Q

• XCLR (External clear)

Reset should be performed during startup in order to initialize the serial interface. Performing external

clear sets all serial interface modes to Low.

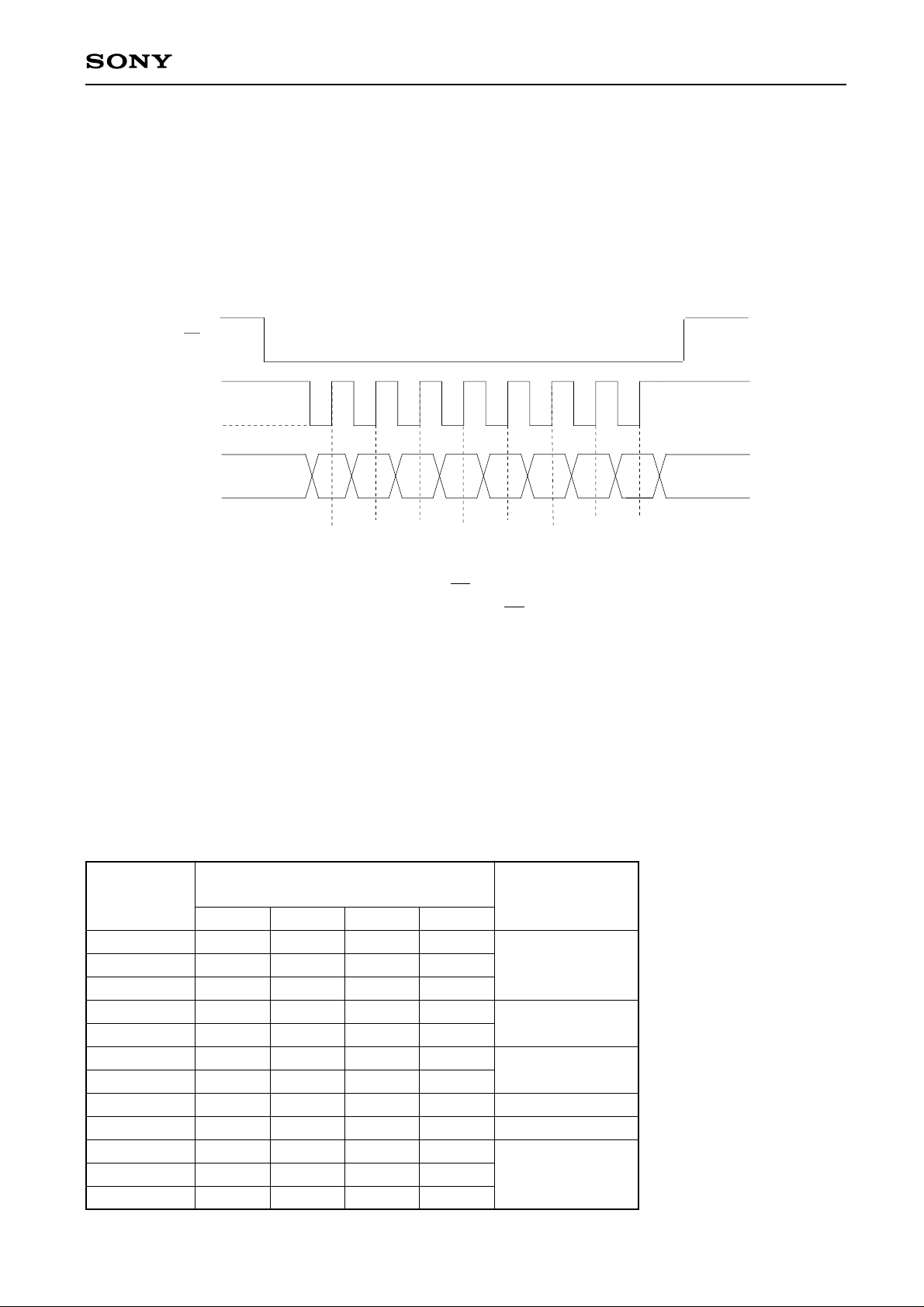

• Serial interface specifications

The CXD2436Q can set and switch the driving mode with the serial interface.

Set the corresponding timing data for each VGA signal according to the format in the diagram below. Be

sure to make the initial mode settings. (See the AC characteristics for detailed timing specifications.)

CS

SCK

SI

D0 D1 D2 D3 D4 D5 D6 D7

Fig. 1. Timing chart for the serial interface input block

Note) D0 to D7 internal transfer is completed by the CS signal switching from a Low to High pulse. Therefore,

the data should be transferred in 1-byte units with the CS signal reset each time.

• Description of mode switching settings using the serial interface

The CXD2436Q can set the following six modes.

(1) Frequency division ratio setting for the 1/N frequency divider of the master clock PLL circuit block.

(2) H screen center adjustment. The center changes by one dot with LSB.

(3) V screen center adjustment. The center changes by one line with LSB.

(4) Sample-and-hold circuit phase adjustment. The phase changes by a half-dot with LSB.

(See the Description of Sample-and-Hold Timing for details.)

(5) Clamp pulse timing adjustment (4-way)

(6) Data output (Serial data is held and output.)

Upper 4-bit

address value

D7 to D4

0H

1H

2H

3H

4H

5H

6H

7H

8H

9H

AH

BH

D3

PHP3

PHP7

—

HP3

—

VP3

—

SHP3

—

PO3

PO7

PO11

Lower 4-bit data

D2

PHP2

PHP6

PHP10

HP2

HP6

VP2

VP6

SHP2

—

PO2

PO6

PO10

D1

PHP1

PHP5

PHP9

HP1

HP5

VP1

VP5

SHP1

CLPP1

PO1

PO5

PO9

D0

PHP0

PHP4

PHP8

HP0

HP4

VP0

VP4

SHP0

CLPP0

PO0

PO4

PO8

Functions

PLL 1/N frequency

divisions

H screen center

adjustment

V screen center

adjustment

S/H timing

Clamp timing

Data output

∗ PHP0, HP0, VP0, SHP0, CLPP0

—11—

Loading...

Loading...