Sony CXD2434ATQ Datasheet

—1—

E97841-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Timing Generator for Progressive Scan CCD Image Sensor

48 pin TQFP (Plastic)

CXD2434ATQ

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VDD VSS –0.5 to +7.0 V

• Input voltage VI VSS –0.5 to VDD +0.5 V

• Output voltage VO VSS –0.5 to VDD +0.5 V

• Operating temperature

Topr –20 to +75 °C

• Storage temperature

Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage VDD 4.75 to 5.25 V

• Operating temperature

Topr –20 to +75 °C

Description

The CXD2434ATQ is an IC developed to generate

the timing pulses required by the Progressive Scan

CCD image sensors as well as signal processing

circuits. The CXD2434ATQ adds EFS operation

when using the high-speed electronic shutter and

other changes to the CXD2434TQ specifications.

Features

• External trigger function

• Electronic shutter function

• Supports non-interlaced operation

• 30 frames/s

• Built-in driver for the horizontal (H) clock

• Base oscillation 1560 fH (24.5454 MHz)

Applications

Progressive Scan CCD cameras

Structure

Silicon gate CMOS IC

Applicable CCD Image Sensors

ICX084AK, ICX084AL

—2—

CXD2434ATQ

TG

PULSE GENERATOR

10

13

14

21

18

22

23

17

16

19

38

39

40

REGISTER

PS

STRB

DCLK

DATA

SMD1

SMD2

XSUB

TEST1

TEST2

RESET

RG

H1

H2

XSHP

XSHD

XRS

XV1

XV2

XV3

XSG

CLD

CL

CKO

BUSY

WEN

ID

PBLK

XCPOB

XCPDM

VD

HD

STDBY

WM

SMDE

FSE

DECODE

COUNTER

GATE

41

48

28

11

9

8

7

5

4

3

252629424647313233343536

1 2

43 44 45

6

12 15 20 24 27 30 37

OSCO

OSCI

TRIG

ESG

EFS

V

SS

V

DD

V

SS

V

DD

V

SS

V

SS

V

DD

V

SS

1/2

1 2 3 4 5 6 7 8 9

10 11 12

13

14

15

16

17

18

19

20

21

22

23

24

35 34 33 32 31 30 29 28 27 252636

46

45

44

43

42

41

40

39

38

37

47

48

CXD2434ATQ

V

SS

CL

CLD

CKO

RESET

STDBY

TRIG

ESG

EFS

HD

VD

TEST2

V

SS

XRS

XSHD

XSHP

V

DD

XSG

XV1

XV2

XV3

V

SS

H2

H1

BUSY

WEN

ID

PBLK

XCPOB

SCPDM

V

DD

WM

TEST1

V

SS

SMDE

FSE

OSCO

OSCI

PS

STRB

DCLK

V

SS

DATA

SMD1

SMD2

RG

XSUB

V

DD

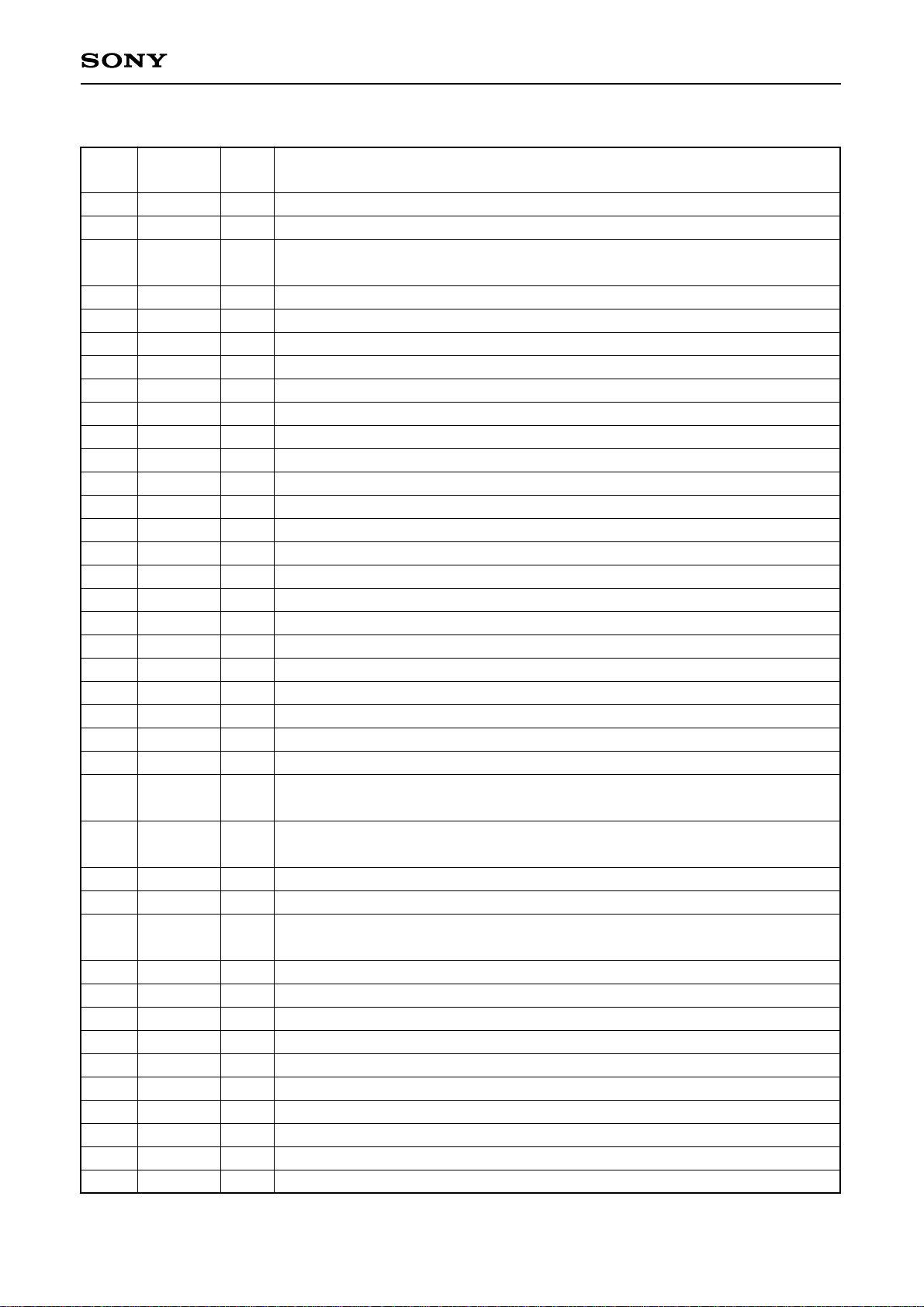

Block Diagram

Pin Configuration (Top View)

—3—

CXD2434ATQ

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

O

I

I

I

I

—

I

I

I

O

O

—

O

O

—

O

O

O

O

—

O

O

O

—

I

I

—

I

I

—

O

O

O

O

O

O

—

O

O

OSCO

OSCI

PS

STRB

DCLK

VSS

DATA

SMD1

SMD2

RG

XSUB

VDD

H1

H2

VSS

XV3

XV2

XV1

XSG

VDD

XSHP

XSHD

XRS

VSS

FSE

SMDE

VSS

TEST1

WM

VDD

XCPDM

XCPOB

PBLK

ID

WEN

BUSY

VSS

CL

CLD

Inverter output for oscillation.

Inverter input for oscillation.

Switching for electronic shutter speed input method. (With pull-up resistor)

Low: Serial input, High: Parallel input

Shutter speed setting. (With pull-up resistor)

Shutter speed setting. (With pull-up resistor)

GND

Shutter speed setting. (With pull-up resistor)

Shutter mode setting. (With pull-up resistor)

Shutter mode setting. (With pull-up resistor)

Reset gate pulse output.

CCD discharge pulse output.

Power supply.

Clock output for horizontal CCD drive.

Clock output for horizontal CCD drive.

GND

Clock output for vertical CCD drive.

Clock output for vertical CCD drive.

Clock output for vertical CCD drive.

Sensor charge readout pulse output.

Power supply.

Sample-and-hold pulse output.

Sample-and-hold pulse output.

Sample-and-hold pulse output.

GND

Switching for external trigger discharge operation. (With pull-up resistor)

Low: No high-speed discharge, High: High-speed discharge

Switching for readout timing. (With pull-up resistor)

Low: ESG input valid, High: ESG input invalid

GND

Test. (With pull-down resistor)

WEN mode setting. (With pull-down resistor)

Low: Effective line, High: XSG synchronization

Power supply.

Clamp pulse output.

Clamp pulse output.

Blanking cleaning pulse output.

Line identification output.

Write enable output.

Trigger mode flag output.

GND

780 fH clock output.

AD conversion pulse output.

Pin Description

Pin No. Symbol I/O Description

—4—

CXD2434ATQ

Pin No. Symbol I/O Description

40

41

42

43

44

45

46

47

48

CKO

RESET

STDBY

TRIG

ESG

EFS

HD

VD

TEST2

O

I

I

I

I

I

I

I

I

1560 fH clock output.

RESET. (With pull-up resistor) Low : Reset, High : Normal

Standby. (With pull-up resistor)

Low: Internal clock supply stopped, High: Normal

External trigger input. (With pull-up resistor)

External readout input. (With pull-up resistor)

Vertical CCD discharge input. (With pull-up resistor)

Horizontal sync signal input.

Vertical sync signal input.

Test. (With pull-up resistor)

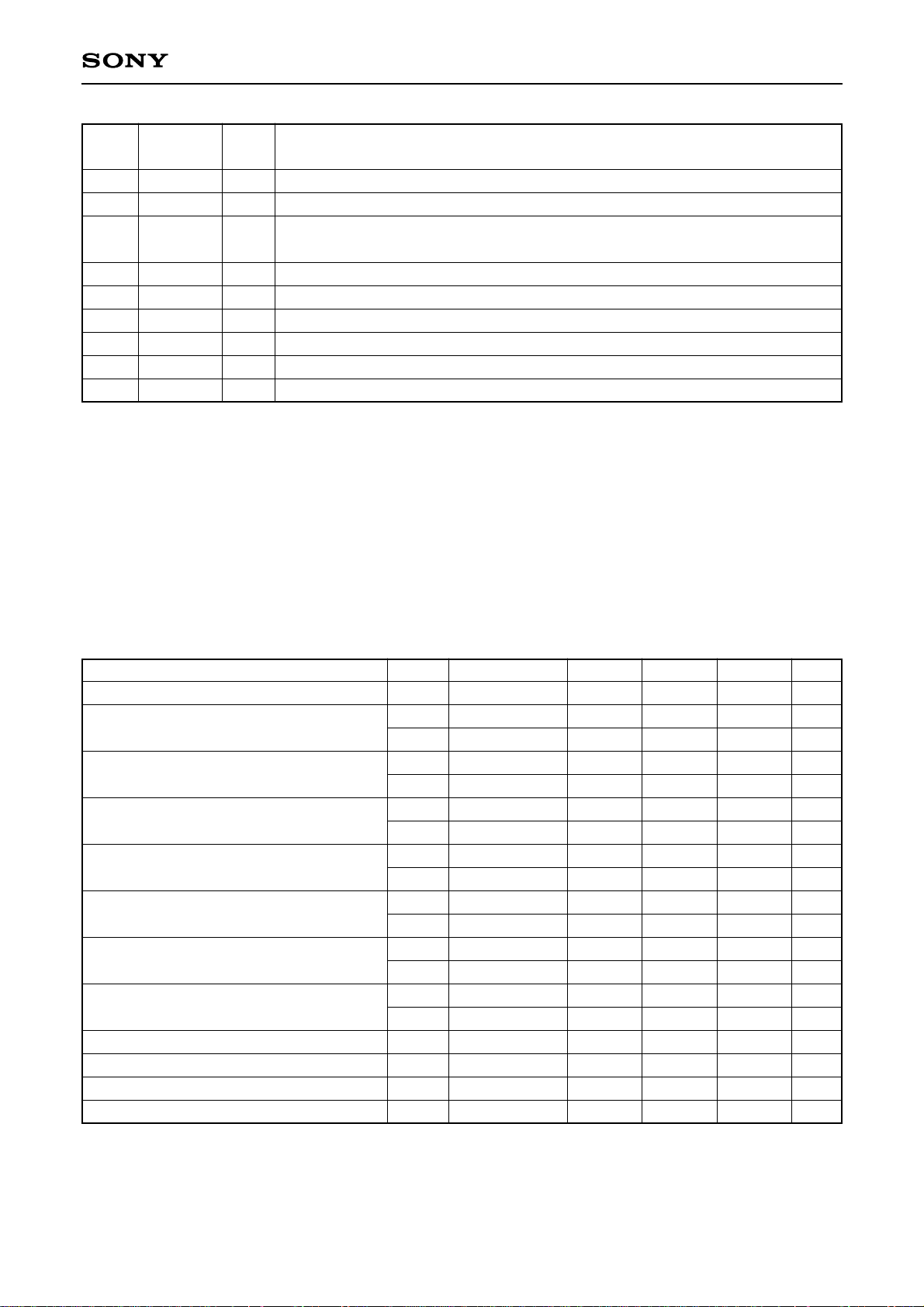

Electrical Characteristics

1. DC Characteristics VDD=4.75 V to 5.25 V Topr= –20 to +75 °C

Item

Supply voltage

Input voltage 1

(Input pins other than those listed below)

Input voltage 2

(Pin 2)

Output voltage 1

(Output pins other than those listed below)

Output voltage 2

(Pins 21, 22, 23, 38, 39 and 40)

Output voltage 3

(Pin 10)

Output voltage 4

(Pins 13 and 14)

Output voltage 5

(Pin 1)

Feedback resistor

Pull-up resistor

Pull-down resistor

Current consumption

Symbol

VDD

VIH1

VIL1

VIH2

VIL2

VOH1

VOL1

VOH2

VOL2

VOH3

VOL3

VOH4

VOL4

VOH5

VOL5

RFB

RPU

RPD

IDD

Conditions

IOH=–2.5 mA

IOL=4.5 mA

IOH=–5.0 mA

IOL=9.0 mA

IOH=–7.5 mA

IOL=13.5 mA

IOH=–14.0 mA

IOL=24.0 mA

VIN=VSS or VDD

VIL=0 V

VIH=VDD

VDD=5 V

Min.

4.75

0.7 VDD

0.7 VDD

VDD–0.4

VDD–0.4

VDD–0.4

VDD–0.4

VDD/2

Typ.

5.0

1 M

50 k

50 k

40

Max.

5.25

0.3 VDD

0.3 VDD

0.4

0.4

0.4

0.4

VDD/2

100 k

100 k

Unit

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

Ω

Ω

Ω

mA

—5—

CXD2434ATQ

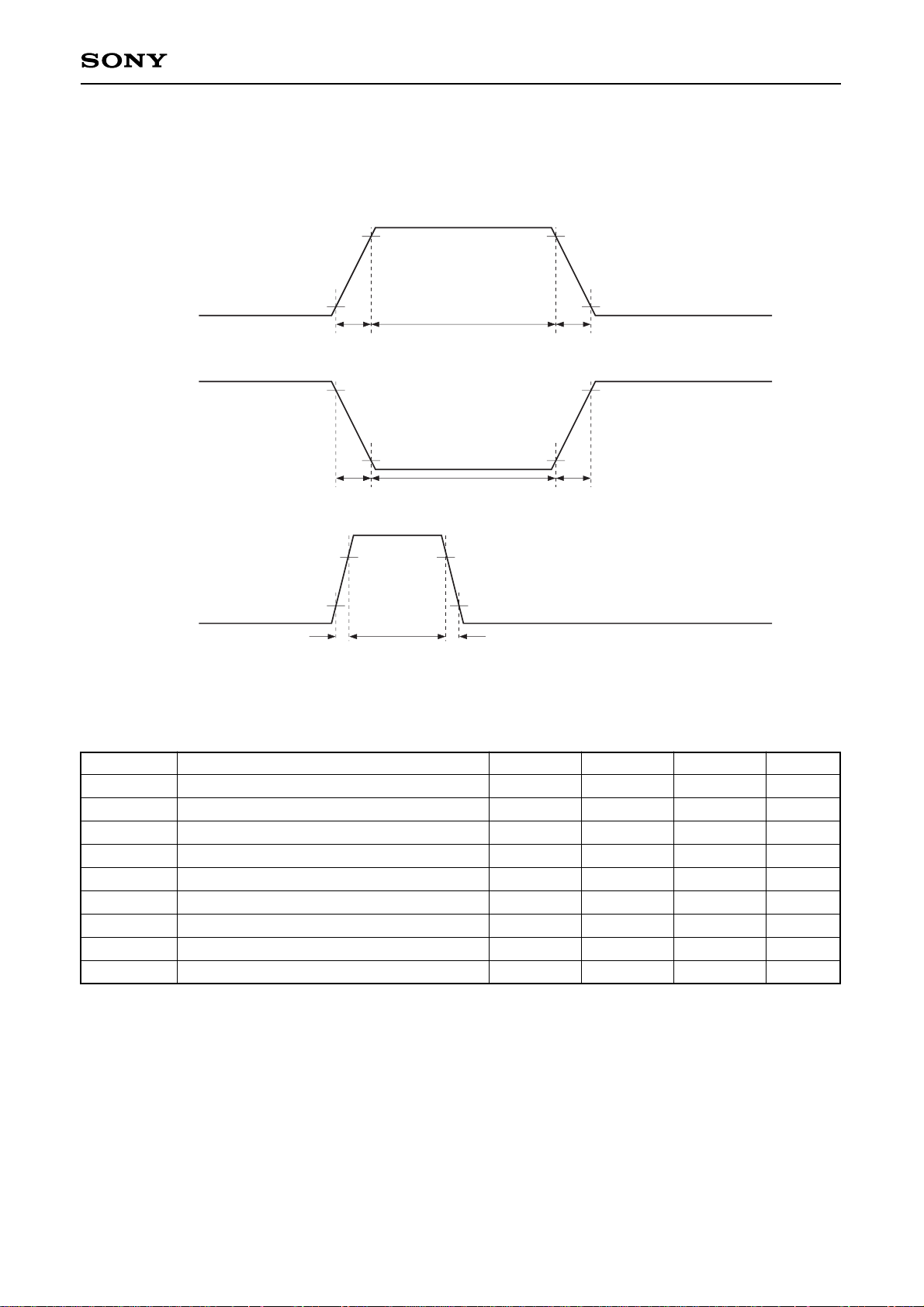

2. AC Characteristics

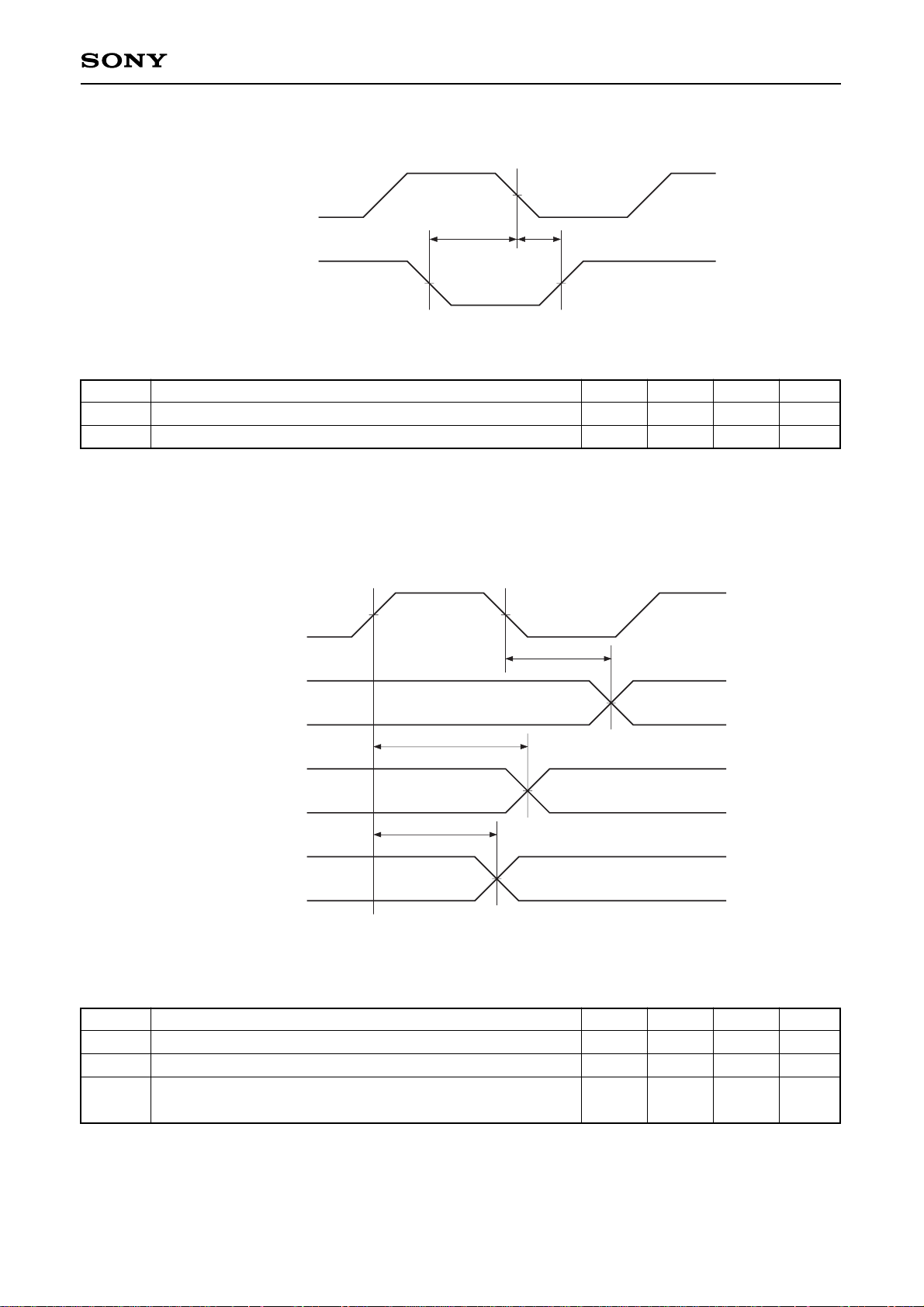

1) Waveform characteristics of H1, H2 and RG

tRH1 tWH1 tFH1

0.9VDD

0.1VDD

0.9VDD

0.1VDD

tFH2 tWH2 tRH2

tRRG tWRG tFRG

H1

H2

RG

0.9V

DD

0.1VDD

VDD=5.0 V, Topr=25 °C, load capacitance of H1 and H2=100 pF, load capacitance of RG=10 pF

Symbol

tRH1

tFH1

tWH1

tRH2

tFH2

tWH2

tRRG

tFRG

tWRG

Definition

H1 rise time

H1 fall time

H1 high level time

H2 rise time

H2 fall time

H2 low level time

RG rise time

RG fall time

RG high level time

Min.

25

25

10

Typ.

6

5

35

6

5

35

2

2

15

Max.

15

15

15

15

5

5

20

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

—6—

CXD2434ATQ

2) Phase characteristics of H1, H2, RG, XSHP, XSHD, XRS, CL, CLD and CKO

tH1

0.5VDD 0.5VDD 0.5VDD

tPD3 tPD1

0.5VDD 0.5VDD

tPD2

0.5VDD 0.5VDD

tPD4 tPD5

tW1

0.5VDD 0.5VDD

tW2 tPD6

0.5VDD 0.5VDD

0.5VDD

tPD7

0.5VDD

tPD8 tPD9

0.5VDD 0.5VDD

tW3tPD10

tW4

0.5VDD 0.5VDD

tW5

tW5

0.5VDD 0.5VDD

0.5VDD

0.5VDD

tPD11 tPD11

H1

H2

RG

XSHP

XSHD

XRS

CLD

CL

CLO

VDD=5.0 V, Topr=25 °C, load capacitance of CL and CKO=30 pF, load capacitance of CLD, XSHP, XSHD, XRS and RG=10 pF

Symbol

tH1

tPD1

tPD2

tPD3

tPD4

tPD5

tPD6

tPD7

tPD8

tPD9

tPD10

tPD11

tW1

tW2

tW3

tW4

tW5

Definition

H1 cycle

H2 rising delay, activated by the falling edge of H1

H2 falling delay, activated by the rising edge of H1

H1 rising delay, activated by the rising edge of RG

XSHP falling delay, activated by the falling edge of RG

H1 falling delay, activated by the rising edge of XSHP

H1 rising delay, activated by the rising edge of XSHD

CLD falling delay, activated by the falling edge of XSHD

CLD falling delay, activated by the rising edge of XRS

XRS falling delay, activated by the falling edge of CLD

CL falling delay, activated by the rising edge of H1

H1 rising (falling) delay, activated by the rising edge of CKO

XSHP pulse width

XSHD pulse width

CLD pulse width

CL pulse width

CKO pulse width

Min.

–5

–5

–5

–2

–7

–5

–5

17

0

–5

–5

13

15

17

38

17

Typ.

82

0

0

0

4

2

2

2

22

8

0

2

18

20

22

41

20

Max.

5

5

5

10

7

7

7

27

15

5

7

23

25

27

45

24

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

—7—

CXD2434ATQ

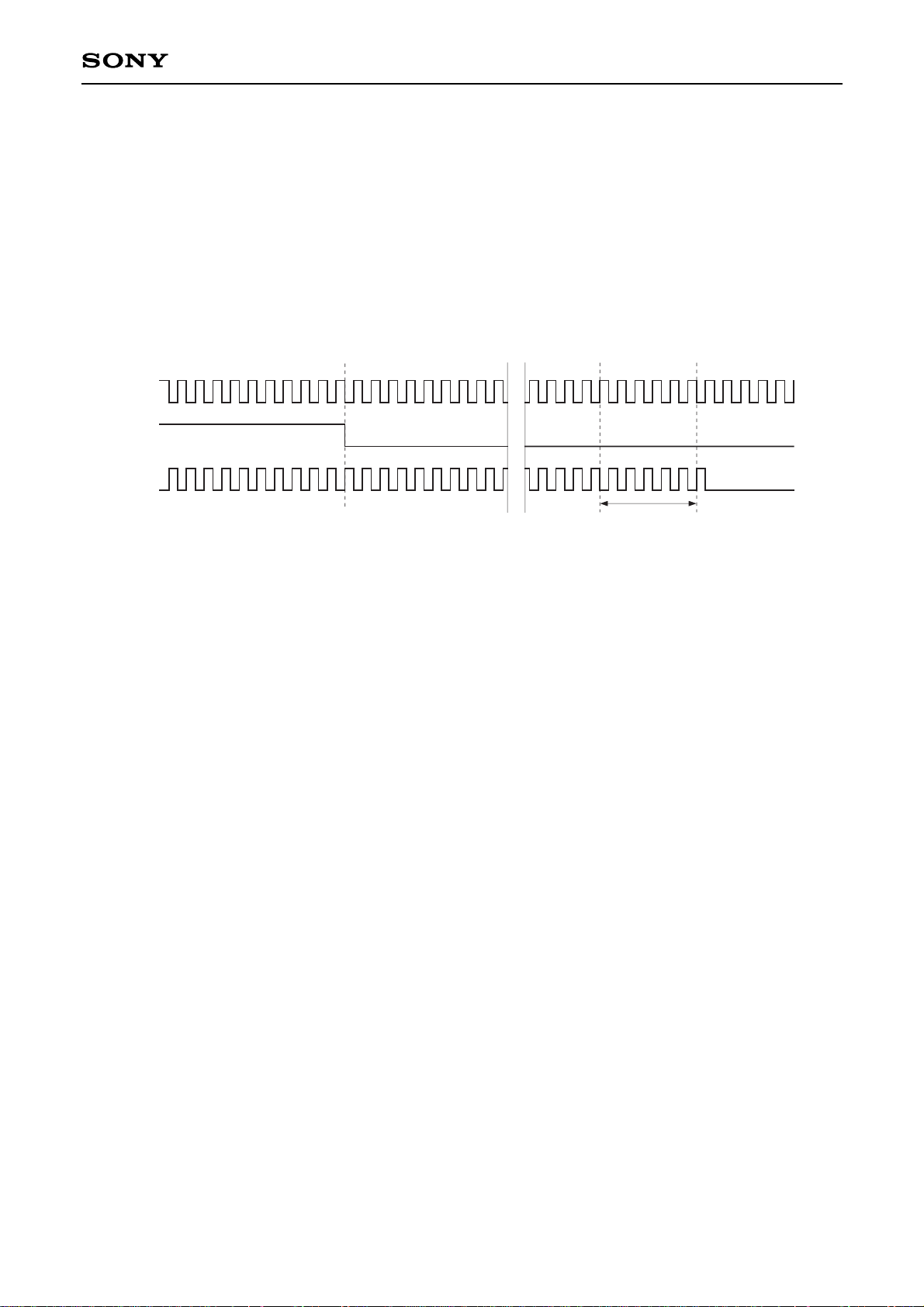

3) Phase conditions of HD, VD, TRIG, EFS and ESG

0.5VDD

tSETUP

tHOLD

0.5VDD 0.5VDD

CL

HD, VD, TRIG

EFS, ESG

VDD=5.0 V, Topr=25 °C, load capacitance of CL=30 pF

Symbol

tSETUP

tHOLD

Definition

HD, VD, TRIG, EFS and ESG setup time, activated by CL

HD, VD, TRIG, EFS and ESG hold time, activated by CL

Min.

20

5

Typ. Max. Unit

ns

ns

4) Phase characteristics of XV1, XV2, XV3, XSG, PBLK, XCPDM, XCPOB, BUSY, WEN and ID

0.5VDD 0.5VDD

tPDCL1

0.5VDD

tPDCL2

0.5VDD

tPDCL3

0.5VDD

CL

XV1, XV2, XV3

BUSY, WEN, ID

XSG, PBLK,

XCPDM, XCPOB

VDD=5.0 V, Topr=25 °C, load capacitance of CL=30 pF,

load capacitance of XV1, XV2, XV3, XSG, PBLK, XCPDM, XCPOB, BUSY, WEN and ID=10 pF

Symbol

tPDCL1

tPDCL2

tPDCL3

Definition

XV1, XV2 and XV3 delay, activated by the falling edge of CL

BUSY, WEN and ID delay, activated by the rising edge of CL

XSG, PBLK, XCPDM and XCPOB delay, activated by the

rising edge of CL

Min.

30

40

40

Typ. Max.

65

60

55

Unit

ns

ns

ns

—8—

CXD2434ATQ

Description of Functions

1. Progressive Scan CCD drive pulse generation

• Combining this IC with a crystal oscillator generates a fundamental frequency of 24.5454 MHz.

• CCD drive pulse generation is synchronized with the HD and VD inputs.

Set fCL to 780 fHD and fHD to 525 fVD.

• The various operations are performed by the TRIG, EFS and ESG inputs. (See the following items.)

<Detection timing for VD, TRIG, EFS and ESG>

35

T1

1

CL

HD

H1

Detection timing for VD,

TRIG, EFS and ESG

After HD input is detected, the status of VD, TRIG, ESG and EFS is detected during T1.

Do not change the status of VD, TRIG, ESG and EFS during T1.

When input is from a non-synchronized system, the low level period for each pulse should be set to 63.5 µs

or longer to prevent misoperation.

2. Reset

The internal register values are undetermined immediately after power-on, so perform one of the following

reset operations.

1. Reset by the RESET pin

Reset is performed by setting the RESET pin low for a period of 80 ns or more. Reset can also be

performed by setting the RESET pin low during power-on and then switching the RESET pin from low to

high when VDD rises to 4.75 V or higher. Note that when reset is performed by the RESET pin, the

electronic shutter settings made by serial input are also reset.

2. Reset by turning off the electronic shutter

Reset is performed by setting the shutter mode to electronic shutter off and inputting VD. Note that in

this case the TRIG, ESG and EFS pins should all be set high.

Loading...

Loading...