Sony CXD2428Q Datasheet

CXD2428Q

Video Scan Converter

Description

The CXD2428Q is an IC which generates control

signals and performs line interpolation calculations

for field memory (CXK1206AM/ATM) in order to

perform video signal scanning line conversion. In

addition, this IC performs the aspect conversion of

the ZOOM mode and WIDE-ZOOM mode in order to

support wide screens.

Features

• Video signal (NTSC/PAL) scanning line conversion function

• ZOOM function

(Function to cut top and bottom areas of 4:3 image and expand it to 16:9)

• WIDE-ZOOM function

(Function to vertically compress 4:3 image and expand it to 16:9)

• Operating frequency: 28.6MHz (typ.)

100 pin QFP (Plastic)

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VDD VSS – 0.5 to +7.0 V

• Input voltage VI VSS – 0.5 to VDD +0.5 V

• Output voltage VO VSS – 0.5 to VDD +0.5 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –55 to +150 °C

Operating Conditions

Supply voltage VDD 4.5 to 5.5 V

Applications

Liquid crystal projectors, etc.

Structure

Silicon gate CMOS IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E95442-ST

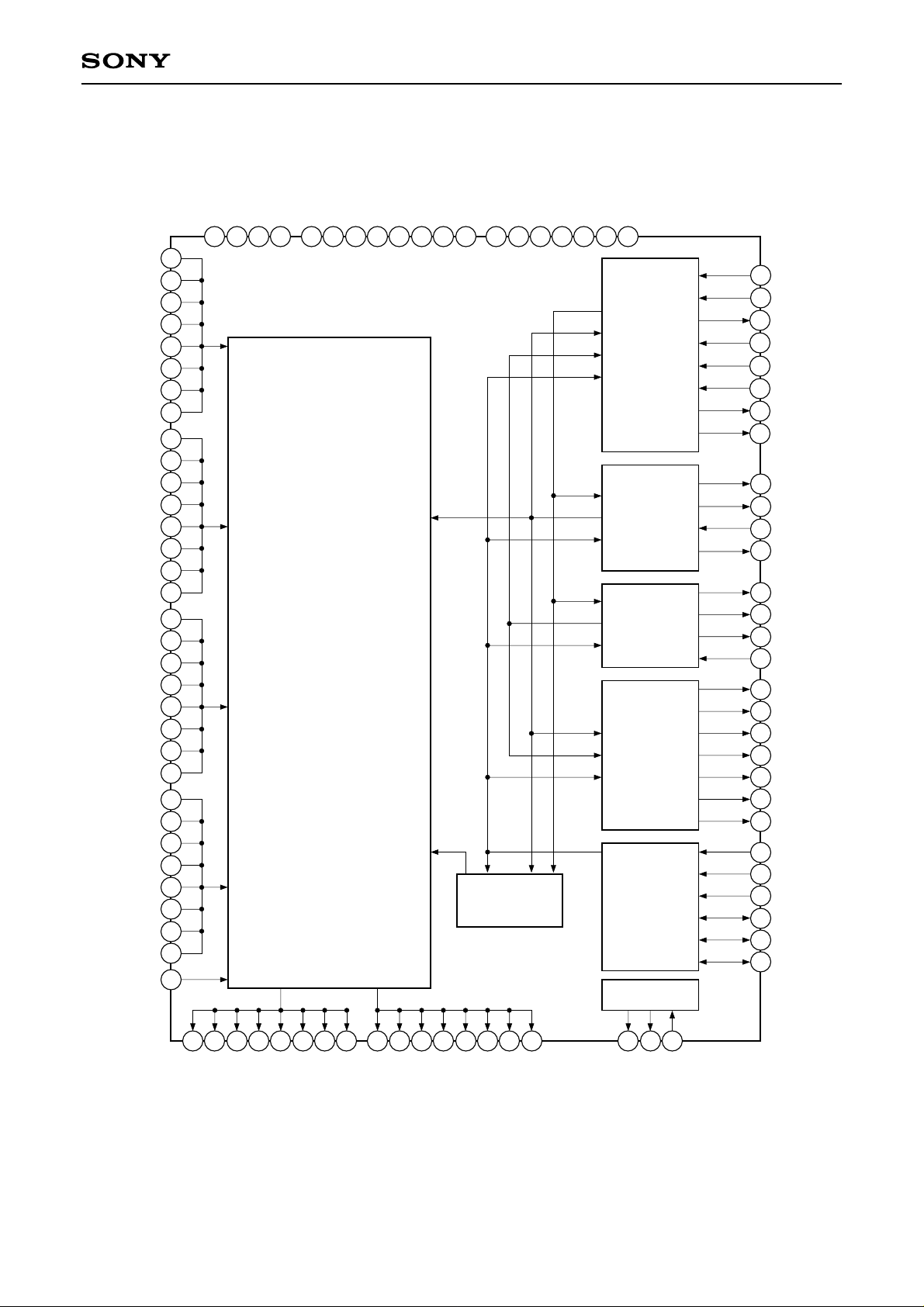

Block Diagram

CXD2428Q

CSD0

CSD1

CSD2

CSD3

CSD4

CSD5

CSD6

CSD7

CFD0

CFD1

CFD2

CFD3

CFD4

CFD5

CFD6

CFD7

YSD0

YSD1

YSD2

YSD3

YSD4

YSD5

YSD6

YSD7

YFD0

YFD1

YFD2

YFD3

YFD4

YFD5

YFD6

YFD7

BLNK

52

55

56

57

58

59

60

61

62

63

64

66

67

68

69

71

74

75

76

77

80

81

82

83

84

85

86

87

88

16

70

72

73

0

DD

V

28

3

3

2

1

DD

DD

DD

V

V

V

53

78

INTERPOLATION

3

2

1

0

SS

SS

V

V

4

15

29

SS

V

40

SS

V

54

4

SS

V

65

5

SS

V

79

6

SS

V

7

SS

V

TST0

6

90

11

COEFFICIENT

TST1

14

TST2

17

TST3

18

TST4

19

TST5

TST6

51

H-WRITE

H-READ

V-WRITE

V-READ

SERIAL-

INTERFACE

12

13

93

94

96

98

99

100

21

22

45

95

89

91

92

97

10

20

46

47

48

50

49

1

2

5

7

8

9

FSL1

FSL2

ADCK

ODEV

HIN

CKI

RYOE

BYOE

HOUT

HBLK

RDCK

HRET

HCR0

VCR0

WEN0

VIN

VBLK

VOUT

REN1

VCR1

HCR1

INC1

INC2

SCLK

SCTR

SDAT

P0

P1

P2

1/2

23

24

CD7

25

CD6

26

CD5

27

CD4

30

CD3

31

CD2

32

CD1

CD0

33

34

YD7

35

YD6

36

YD5

37

YD4

– 2 –

YD3

38

39

YD2

41

YD1

YD0

42

BYCK

43

RYCK

44

YCK

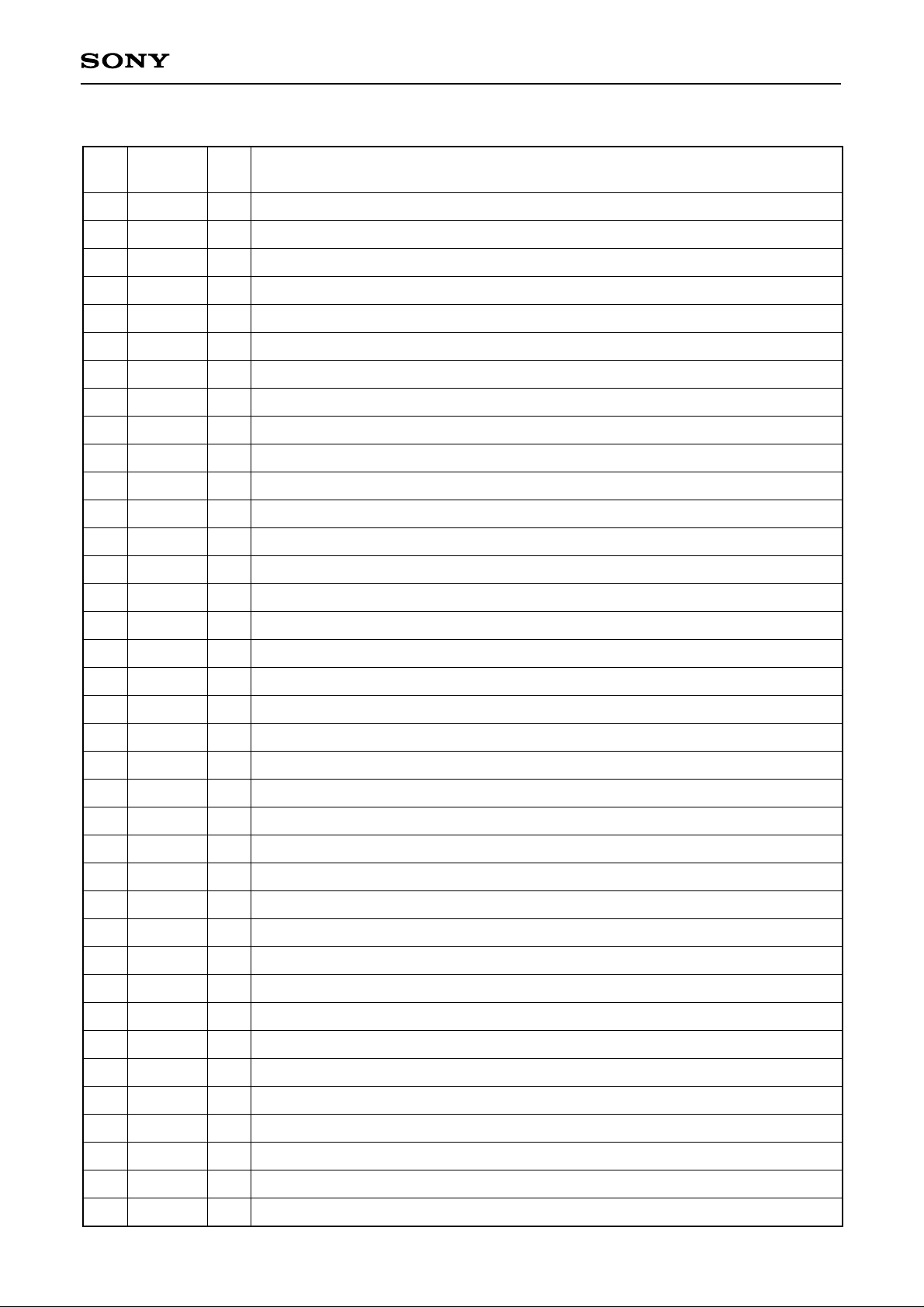

Pin Description

Pin

No.

Symbol I/O Description

1

SCLK

2

SCTR

3

VDD0

4

VSS0

5

SDAT

6

TST0

7

P0

8

P1

9

P2

10

VBLK

11

TST1

I

Serial transfer clock

I

Serial transfer control

—

Power supply

—

GND

I

Serial transfer data

O

Leave open.

I/O

I/O port

I/O

I/O port

I/O

I/O port

O

Vertical blanking output

I

Fixed to high.

CXD2428Q

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

FSL1

FSL2

TST2

VSS1

BLNK

TST3

TST4

TST5

VOUT

HOUT

HBLK

CD7

CD6

CD5

CD4

CD3

VDD1

I

Field identification selection (High: internal, Low: external)

I

Field information polarity switching

I

Fixed to low.

—

GND

I

Output data control (High: black display)

I

Fixed to high.

I

Leave open.

I

Leave open.

O

Vertical sync signal output

O

Horizontal sync signal output

O

Horizontal blanking signal

O

B-Y/R-Y data output (MSB)

O

B-Y/R-Y data output

O

B-Y/R-Y data output

O

B-Y/R-Y data output

O

B-Y/R-Y data output

—

Power supply

29

30

31

32

33

34

35

36

37

VSS2

CD2

CD1

CD0

YD7

YD6

YD5

YD4

YD3

—

GND

O

B-Y/R-Y data output

O

B-Y/R-Y data output

O

B-Y/R-Y data output (LSB)

O

Y data output (MSB)

O

Y data output

O

Y data output

O

Y data output

O

Y data output

– 3 –

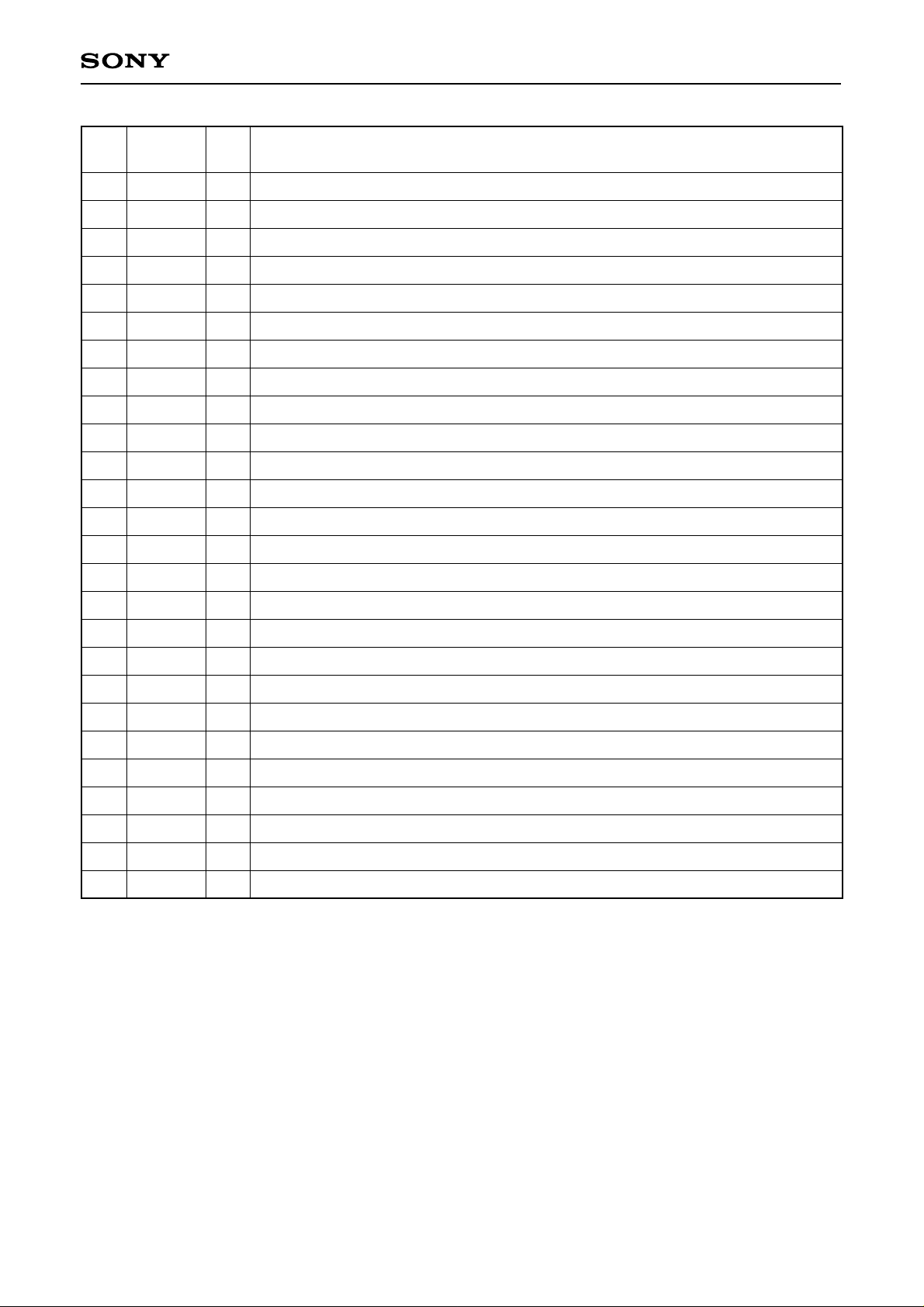

CXD2428Q

Pin

No.

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

Symbol I/O Description

YD2

YD1

VSS3

YD0

BYCK

RYCK

YCK

RDCK

REN1

VCR1

HCR1

INC1

INC2

TST6

CSD0

O

Y data output

O

Y data output

—

GND

O

Y data output (LSB)

O

DA converter (B-Y) clock output

O

DA converter (R-Y) clock output

I

DA converter clock input

I

Readout clock input

O

Readout memory enable

O

Readout memory vertical clear

O

Readout memory horizontal clear

O

Readout memory line increment

O

Readout memory line increment

I

Fixed to high.

I

B-Y/R-Y lower line data input (LSB)

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

VDD2

VSS4

CSD1

CSD2

CSD3

CSD4

CSD5

CSD6

CSD7

CFD0

CFD1

CFD2

VSS5

CFD3

CFD4

CFD5

CFD6

—

Power supply

—

GND

I

B-Y/R-Y lower line data input

I

B-Y/R-Y lower line data input

I

B-Y/R-Y lower line data input

I

B-Y/R-Y lower line data input

I

B-Y/R-Y lower line data input

I

B-Y/R-Y lower line data input

I

B-Y/R-Y lower line data input (MSB)

I

B-Y/R-Y upper line data input (LSB)

I

B-Y/R-Y upper line data input

I

B-Y/R-Y upper line data input

—

GND

I

B-Y/R-Y upper line data input

I

B-Y/R-Y upper line data input

I

B-Y/R-Y upper line data input

I

B-Y/R-Y upper line data input

70

71

72

73

74

CFD7

YSD0

YSD1

YSD2

YSD3

I

B-Y/R-Y upper line data input (MSB)

I

Y lower line data input (LSB)

I

Y lower line data input

I

Y lower line data input

I

Y lower line data input

– 4 –

Pin

No.

75

76

77

78

79

80

81

82

83

84

85

86

Symbol I/O Description

YSD4

YSD5

YSD6

VDD3

VSS6

YSD7

YFD0

YFD1

YFD2

YFD3

YFD4

YFD5

I

Y lower line data input

I

Y lower line data input

I

Y lower line data input

—

Power supply

—

GND

I

Y lower line data input (MSB)

I

Y upper line data input (LSB)

I

Y upper line data input

I

Y upper line data input

I

Y upper line data input

I

Y upper line data input

I

Y upper line data input

CXD2428Q

87

88

89

90

91

92

93

94

95

96

97

98

99

100

YFD6

YFD7

HCR0

VSS7

VCR0

WEN0

ADCK

ODEV

HRET

HIN

VIN

CKI

RYOE

BYOE

I

Y upper line data input

I

Y upper line data input (MSB)

O

Write memory horizontal clear

—

GND

O

Write memory vertical clear

O

Write memory enable

O

AD converter clock

I

Field information input

O

Phase comparison output

I

Horizontal sync signal input

I

Vertical sync signal input

I

Write clock input

O

AD converter (R-Y) enable

O

AD converter (B-Y) enable

– 5 –

Loading...

Loading...