Sony CXD2412AQ Datasheet

Timing Generator for LCD Panels

Description

The CXD2412AQ is a timing signal generator for

LCD panel drivers.

Features

• Generates the LCX007 drive pulse.

• Supports NTSC/PAL.

(With PAL, a video signal on which scanning line

conversion has been performed is used.)

• Supports WIDE.

• Supports HD (20 MHz band).

• Supports Muse-NTSC conversion signal (MNDC).

• Supports up/down and/or right/left inversion.

• Supports three-panel projector.

• Generates timing signal of external sample-andhold circuit.

• Generates line inversion and field inversion

signals.

• AC drive for LCD panel during no signal.

• AFC circuit supporting static and dynamic

fluctuations.

CXD2412AQ

100 pin QFP (Plastic)

Applications

LCD projectors

Structure

Silicon gate CMOS IC

Absolute Maximum Ratings (Ta = 25 °C)

• Supply voltage

• Input voltage

• Output voltage

• Operating temperature

• Storage temperature

Recommended Operating Conditions

•

Supply voltage

•

Operating temperature

VDD VSS–0.5 to +7.0 V

VI VSS – 0.5 to VDD + 0.5V

VO VSS – 0.5 to VDD + 0.5V

Topr –20 to +75 °C

Tstg –55 to +150 °C

VDD 5.0 ± 0.5 V

Topr –20 to +75 °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E94Y04-ST

Block Diagram

CXD2412AQ

RPD1

RPD2

RPD3

FPD1

FPD2

FPD3

TC1

TC2

TC3

HSYNC

N.C.

N.C.

CKI1

CKI2

CKI3

CKO1

CKO2

CKO3

VSYNC

TST6

TST1

TST2

TST3

TST4

TST5

XCLR

VP1

VP2

VST

SLAUX

V

SS0

SS1

V

SS2

V

SS3

V

V

SS4

SS5

V

SS6

V

SS7

V

SS8

V

V

SS10

SS11

V

SS12

V

DD0

V

DD1

V

V

DD2

DD3

V

DD4

V

DD5

V

86

94

83

97

82

98

16

12

89

92

11

88

91

17

14

24

25

26

27

30

31

49

50

46

10

13

15

29

40

65

79

87

90

28

35

53

78

73

54

93

70

9

LOOP

6

FILTER

PHASE

COMPARATOR

5

PLL-COUNTER

2

1

H-SYNC

DETECTOR

H-SKEW

HALF-H

KILLER

DETECTOR

FIELD & LINE

CONTROLLER

V-SYNC

SEPERATER

(NOISE SHAPE)

V-TIMING

PULSE GENERATOR

4

H-TIMING

PULSE

GENERATOR

3

84

95

85

96

48

51

52

55

56

57

58

59

60

75

32

47

33

61

18

19

20

22

23

74

72

81

99

100

36

37

38

39

34

42

43

44

45

62

63

64

67

68

69

76

77

80

7

8

21

71

41

66

PEO1

PEO2

PEO3

PWM1

PWM2

PWM3

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

SLFR

RGT

DWN

XRGT

FRP

HP1

HP2

HP3

HP4

HP5

HP6

PCGW

SLSH1

SLSH2

SLSH3

CP1

CP2

HCK1A

HCK2A

HCK1B

HCK2B

HSTA

HSTB

CLR

ENB

VCK

PCG

XCLP1

XCLP2

PRG

SH1

SH2

SH3

SH4

NTPL

XWD

XHD

– 2 –

Pin Description

CXD2412AQ

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Symbol

N.C.

N.C.

VDD0

VSS0

TC1

FPD1

PEO1

PWM1

RPD1

VSS1

CKO1

CKI1

VSS2

TST6

VSS3

I/O

Not connected

—

Not connected

—

Power supply

—

GND

—

FPD1 pin pulse width adjustment

I

Phase comparator output B-1 (for NTSC/PAL)

O

Loop filter integrator output 1

O

Loop filter integrator input 1

I

Phase comparator output A-1 (for NTSC/PAL)

O

GND

—

NTSC/PAL oscillation cell output

O

NTSC/PAL oscillation cell input

I

GND

—

Test

I

GND

—

Description

Input pin for open

status

L

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

HSYNC

VSYNC

HP1

HP2

HP3

HP4

HP5

HP6

TST1

TST2

TST3

TST4

VDD1

VSS4

TST5

XCLR

RGT

Hsync input (negative polarity)

I

Vsync input (negative polarity)

I

Switches for the horizontal display start position

I

Switches for the horizontal display start position

I

Switches for the horizontal display start position

I

Switches for the horizontal display start position

I

Switches for the horizontal display start position

I

Switches for the horizontal display start position

I

Test

I

Test

I

Test

I

Test

I

Power supply

—

GND

—

Test

I

Cleared at 0 V

I

Right/left inversion identification signal input

I

L

L

L

L

L

H

L

L

L

L

H

H

H

33

34

35

36

37

XRGT

HSTA

VDD2

HCK1A

HCK2A

Right/left inversion identification signal output

O

H start pulse A

O

Power supply

—

H clock pulse 1A

O

H clock pulse 2A

O

– 3 –

CXD2412AQ

Pin No.

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

Symbol

HCK1B

HCK2B

VSS5

HSTB

CLR

ENB

VCK

PCG

VST

DWN

N.C.

VP1

VP2

N.C.

N.C.

I/O

H clock pulse 1B

O

H clock pulse 2B

O

GND

—

H start pulse B

O

Clear pulse

O

Enable pulse

O

V clock pulse

O

Precharge pulse

O

V start pulse

O

Up/down inversion identification signal input

I

Not connected

—

Switches for the vertical display start position

I

Switches for the vertical display start position

I

Not connected

—

Not connected

—

Description

Input pin for open

status

H

L

H

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

VDD3

VSS6

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

FRP

XCLP1

XCLP2

PRG

VSS7

SH1

SH2

SH3

SH4

Power supply

—

GND

—

Not connected

—

Not connected

—

Not connected

—

Not connected

—

Not connected

—

Not connected

—

AC drive inversion timing output

O

Video signal pedestal clamp pulse 1

O

Video signal pedestal clamp pulse 2

O

Precharge signal pulse

O

GND

—

Sample-and-hold pulse 1

O

Sample-and-hold pulse 2

O

Sample-and-hold pulse 3

O

Resample-and-hold pulse

O

70

71

72

73

74

VDD4

SLSH1

SLSH2

SLAUX

PCGW

Power supply

—

Switches SH

I

Switches SH

I

Switches free-running identification line number

I

Switches PCG

I

– 4 –

L

L

H

H

CXD2412AQ

Pin No. Symbol

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

SLFR

NTPL

XWD

VDD5

VSS8

XHD

SLSH3

TC2

FPD2

PEO2

PWM2

RPD2

VSS10

CKO2

CKI2

I/O

Switches between H inversion and F inversion

I

(H: H inversion / L: F inversion)

Switches mode

I

Switches mode

I

Power supply

—

GND

—

Switches mode

I

Switches SH

I

FPD2 pin pulse width adjustment

I

Phase comparator output B-2 (for WIDE)

O

Loop filter integrator output 2

O

Loop filter integrator input 2

I

Phase comparator output A-2 (for WIDE)

O

GND

—

WIDE oscillation cell output

O

WIDE oscillation cell input

I

Description

Input pin for open

status

H

H

H

H

L

90

91

92

93

94

95

96

97

98

99

100

VSS11

CKO3

CKI3

VSS12

RPD3

PEO3

PWM3

FPD3

TC3

CP1

CP2

GND

—

HD/MNDC oscillation cell output

O

HD/MNDC oscillation cell input

I

GND

—

Phase comparator output A-3 (for HD/MNDC)

O

Loop filter integrator output 3

O

Loop filter integrator input 3

I

Phase comparator output B-3 (for HD/MNDC)

O

FPD3 pin pulse width adjustment

I

Switches pedestal clamp position

I

Switches pedestal clamp position

I

H

L

– 5 –

CXD2412AQ

Electrical Characteristics

1. DC characteristics (Temperature = 25°C, Vss = 0V)

Item

Supply voltage

Input voltage

Input voltage

Input voltage

Input voltage

Output voltage

Output voltage

Output voltage

Output voltage

Output voltage

Output voltage

Input leak current

Input leak current

Output leak current

Current consumption

Symbol

VDD

VIH

VIL

VIH

VIL

VOH

VOL

VOH

VOL

VOH

VOL

IIL

IIH

ILZ

IDD

Conditions

TTL input cell

TTL input cell

CMOS input cell

CMOS input cell

IOH = –4mA (HCKl, SHm)

IOL = 8mA (HCKl, SHm)

IOH = –3mA (CKOn, CKIn)

IOL = 3mA (CKOn, CKIn)

IOH = –2mA (other than the above)

IOL = 4mA (other than the above)

Pull-up resistor connected

Pull-down resistor connected

RPDn, FPDn (at high impedance state)

HD mode, VDD = 5.0V (at no load)

Min.

4.5

2.2

0.7VDD

VDD – 0.8

VDD/2

VDD – 0.8

–40

–40

–40

Typ.

–100

100

75

Max.

5.5

0.8

0.3VDD

0.4

VDD/2

0.4

–240

240

40

Unit

V

V

V

V

V

V

V

V

V

V

V

µA

µA

µA

mA

2. AC characteristics (VDD = 5.0 ± 10%)

Typ.

Item

Clock input cycle

Cross point time difference

Cross point time difference

Output rise delay

Output fall delay

Output rise delay

Output fall delay

HCK1, SH1 delay time difference

HCK1, SH1 delay time difference

HCK2, SH1 delay time difference

HCK2, SH1 delay time difference

HCK1 Duty

HCK2 Duty

CKIn

HCK1A, HCK2A

HCK1B, HCK2B

HCKl, SHm

HCKl, SHm

Other than HCK1 and SHm

Other than HCK1 and SHm

HCK1A, HCK1B, SH1

HCK1A, HCK1B, SH1

HCK2A, HCK2B, SH1

HCK2A, HCK2B, SH1

HCK1A, HCK1B

HCK2A, HCK1B

Applicable pins

Symbol

∆t

∆t

tpr

tpf

tpr

tpf

dt1

dt2

dt1

dt2

tH/tH + tL

tH/tH + tL

Conditions

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

CL = 30pF

Min.

22

0.05

1

0.1

1

45

45

Max.

10

10

20

15

25

15

0.25

5

0.5

5

52

52

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

%

%

Note) l = 1A, 1B, 2A, 2B

n = 1, 2, 3

m = 1, 2, 3, 4

– 6 –

Timing Definition

CK1

HCK1A

(HCK2A)

Outpu t

Outpu t

50%

CXD2412AQ

DD

V

0V

VDD

0V

tpr

V

DD

0V

tpf

VDD

50%

0V

HCK1B

(HCK2B)

CK1

HCK1A

1B

2A

2B

SH1

50% 50%

tt

50%

tH tL

50% 50%

t2t1

50% 50%

dt1 dt2

V

DD

0V

∆t∆t

– 7 –

CXD2412AQ

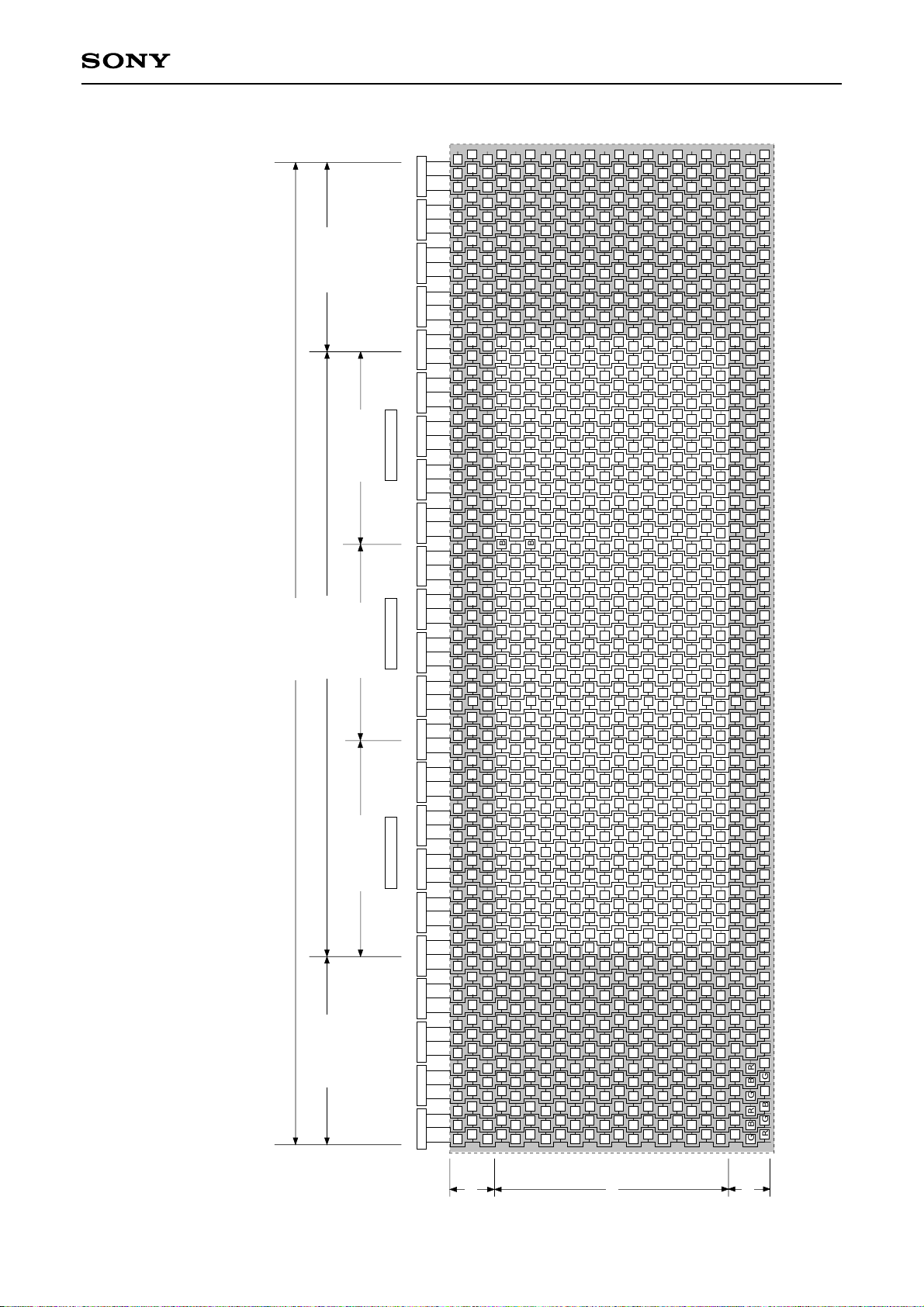

LCD Panel Structure

The structure of LCD panels driven by this IC is shown below.

Dot Arrangement (1) (16 : 9 display)

The dots are arranged in a delta pattern. The shaded area is used for the dark border around the display.

The R corresponds to SIG2, G to SIG1, and B to SIG3, respectively.

ODD = 13

ODD = 1069

ODD = 1094

EVEN = 1095

ODD = 13

EVEN = 13

ODD = 135

EVEN = 134

ODD = 799

EVEN = 800

EVEN = 1068

ODD = 135

EVEN = 134

EVEN = 14

DR4

GATE SW

DR3

GATE SW

DR2

GATE SW

DR1

GATE SW

357

GATE SW

356

GATE SW GATE SW

314

GATE SW

313

GATE SW

312

GATE SW

311

GATE SW

48

GATE SW

47

GATE SW

46

GATE SW

45

GATE SW

44

Side Black 4:3 Area Side Black

GATE SW GATE SW

2

GATE SW

1

GATE SW

DL4

GATE SW

DL3

GATE SW

DL2

GATE SW

DL1

GATE SW

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

G BR

3

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

R R R R R R R R R R R R

GBR

GBR

B

G

R

GBR

GBR

B

G

B

B

GR

GR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

R R R R R R

GBR

GBR

B

G

R

GBR

GBR

B

G

R

GBR

GBR

B

G

R

GBR

GBR

B

G

R

G BR

GBR

123

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

4

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R R R R R R R

B

G

R

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R

B

G

R

B

G

R

B

G

R

B

G

R

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

480

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

479

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

480

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

3

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R R R R R R R

B

G

R

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R

B

G

R

B

G

R

B

G

R

B

G

R

– 8 –

CXD2412AQ

B

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

BR

G

GBR

B

R

G

GBR

GB

B

G

GBR

GBR

B

G

R R R R R R R R R R R R

GBR

GBR

B

G

R

GBR

GBR

B

G

B

B

GR

GR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

GBR

GBR

B

G

R R R R R R

GBR

GBR

B

G

R

GBR

GBR

B

G

R

GBR

GBR

B

G

R

GBR

GBR

B

G

R

G BR

GBR

123

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R R R R R R R

B

G

R

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R

B

G

R

B

G

R

B

G

R

B

G

R

DR4

GATE SW

DR3

GATE SW

DR2

ODD = 13

EVEN = 13

ODD = 135

EVEN = 134

ODD = 799

ODD = 1069

ODD = 1094

EVEN = 1095

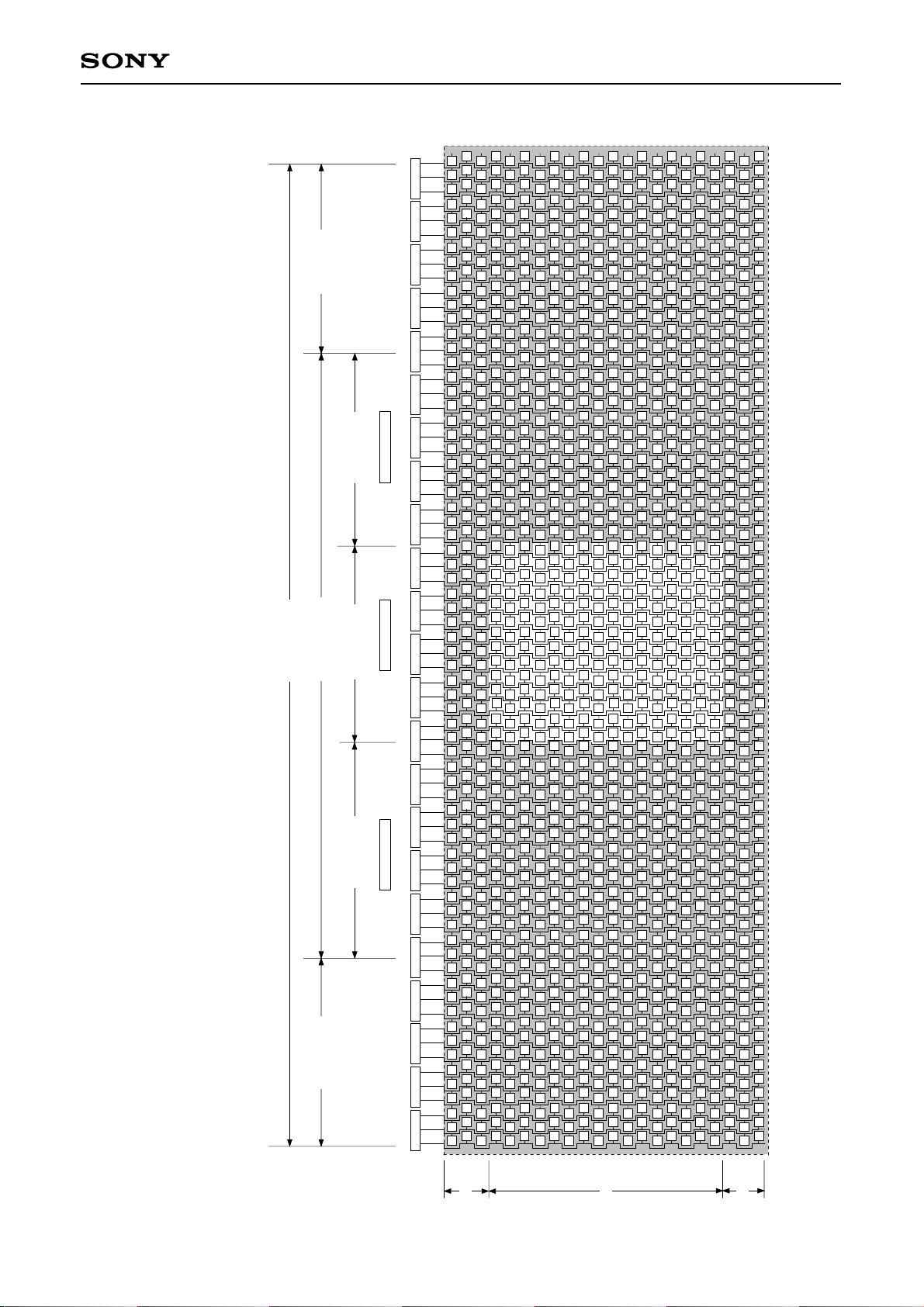

Dot Arrangement (2) (4 : 3 display)

The dots are arranged in a delta pattern. The shaded area is used for the dark border around the display.

The R corresponds to SIG2, G to SIG1, and B to SIG3, respectively.

EVEN = 800

EVEN = 1068

ODD = 135

EVEN = 134

ODD = 13

EVEN = 14

GATE SW

DR1

GATE SW

357

GATE SW

356

GATE SW GATE SW

314

GATE SW

313

GATE SW

312

GATE SW

311

GATE SW

48

GATE SW

47

GATE SW

46

GATE SW

45

GATE SW

44

Side Black 4:3 Area Side Black

GATE SW GATE SW

2

GATE SW

1

GATE SW

DL4

GATE SW

DL3

GATE SW

DL2

GATE SW

DL1

GATE SW

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

G BR

3

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

4

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

480

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

479

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R R R R R R R

GBR

B

G

R

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

GBR

B

G

R R R R R R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

B

G

R

GBR

480

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

GBR

3

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R R R R R R R

B

G

R

B

G

B

G

B

G

B

G

B

G

B

G

R R R R R R

B

G

R

B

G

R

B

G

R

B

G

R

– 9 –

CXD2412AQ

Input Signal Specifications

1. Horizontal sync signal

• With NTSC, NTSC WIDE, PAL, PAL+, and MNDC, the standard signal is doubled in speed, and a 1/2 cycle,

1/2 width horizontal sync signal (H.SYNC) is input.

• With HD, a signal derived by cutting off the lower part of 3-value sync is input.

• Negative polarity input is used.

2. Vertical sync signal

• V.sync separated by synchronizing separation circuit and not doubled in speed is input as the vertical sync

signal.

• Negative polarity input is used.

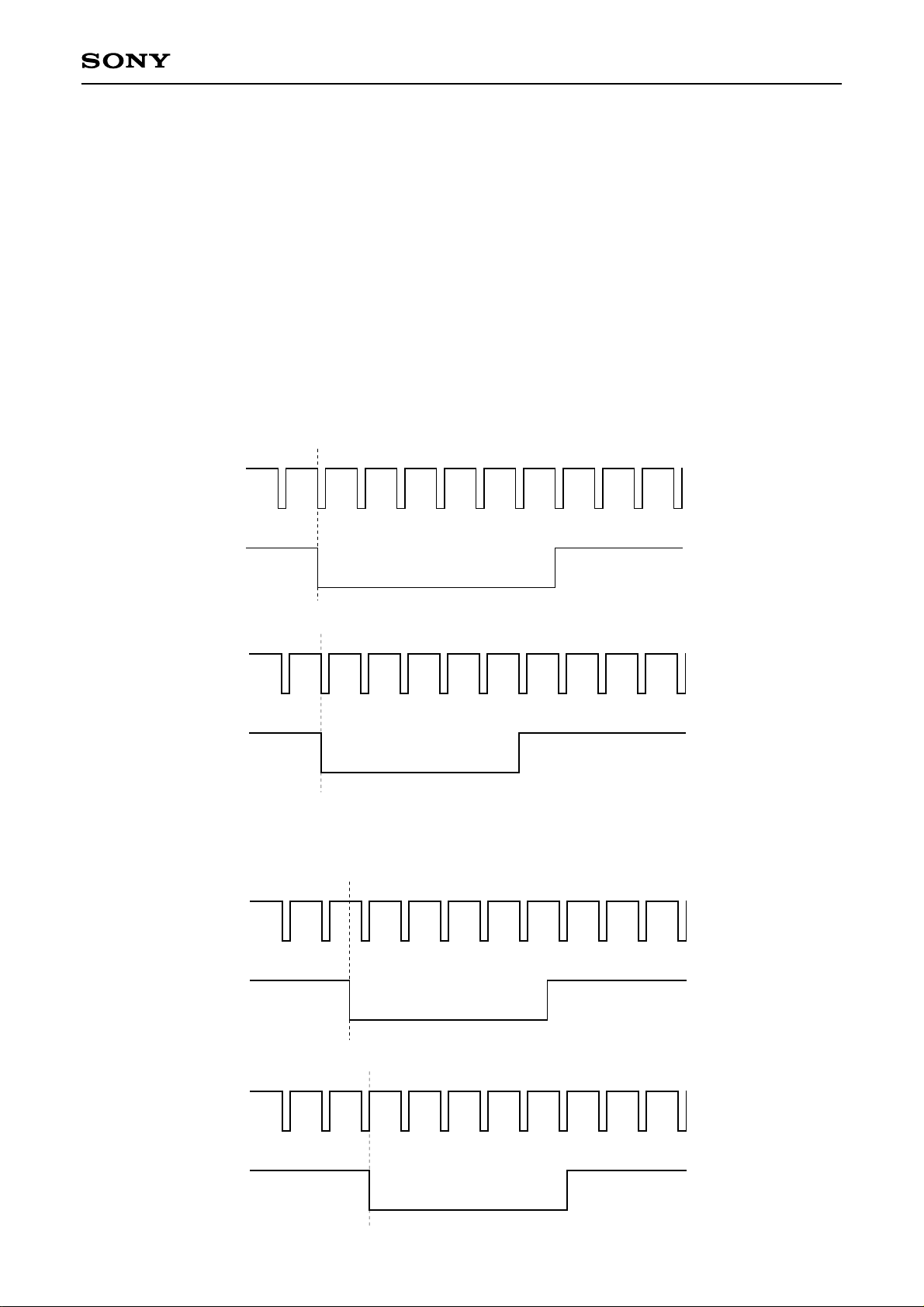

• With this TG, the phase relationship between VSYNC and HSYNC is as follows;

(1) NTSC/NTSC WIDE/MNDC

HSYNC

(Double-speed H.sync)

VSYNC

(2) PAL/PAL+

HSYNC

(Double-speed H.sync )

VSYNC

The video signal has a 487-line effective period due to scanning line conversion.

(3) HD

ODD FIEL D

Phase reference

Phase reference

HSYNC

VSYNC

EVEN FIELD

HSYNC

VSYNC

Phase reference

– 10 –

Mode Selection

Mode selection is performed by means of three pins, as shown in the table.

CXD2412AQ

NTPL

H

L

H

L

L

H

XWD

H

H

L

L

X

X

XHD

H

H

H

H

L

L

Mode

NTSC

PAL

NTSC WIDE

PAL+

HD

MNDC

– 11 –

Loading...

Loading...