Sony CXD2300Q Datasheet

—1—

E91Z06D86-TE

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

Absolute Maximum Ratings (Ta=25 °C)

• Supply voltage VDD 7V

• Reference voltage

VRT, VRB VDD + 0.5 to VSS – 0.5 V

• Input voltage VIN VDD + 0.5 to VSS – 0.5 V

(Analog)

• Input voltage VI VDD + 0.5 to VSS – 0.5 V

(Digital)

• Output voltage VO VDD + 0.5 to VSS – 0.5 V

(Digital)

• Storage temperature

Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage AVDD, AVSS 3.14 to 4.0 V

DVDD, DVSS

| DGND – AGND |

0 to 100 mV

• Reference input voltage

VRB 0 to V

VRT to VDD V

• Analog input VIN 1.3 Vp-p above

• Clock pulse width

Tpw1, Tpw0 25 ns (min) to 1.1 µs (max)

• Operating ambient temperature

Topr –40 to +85 °C

Description

The CXD2300Q is an 8-bit CMOS A/D converter

for video with synchronizing clamp function and can

operate on 3.3 V power supply. The adoption of 2

step-parallel method achieves ultra-low power

consumption and a maximum conversion speed of

18MSPS.

Features

• Resolution: 8-bit ± 1/2LSB (DL)

• Maximum sampling frequency: 18MSPS

• Low power consumption: 18 mW (at 18MSPS typ.)

(reference current excluded)

• Synchronizing clamp function

• Clamp ON/OFF function

• Reference voltage self-bias circuit

• Input CMOS compatible

• 3-state TTL compatible output

• Single 3.3 V power supply

• Low input capacitance: 8 pF

• Reference impedance: 330 Ω (typ.)

Applications

Wide range of applications that require high-speed

A/D conversion such as TV and VCR.

Structure

Silicon gate CMOS IC

8-bit 18MSPS Video A/D Converter with 3.3V Power Supply Operation Function

32 pin QFP (Plastic)

CXD2300Q

—2—

CXD2300Q

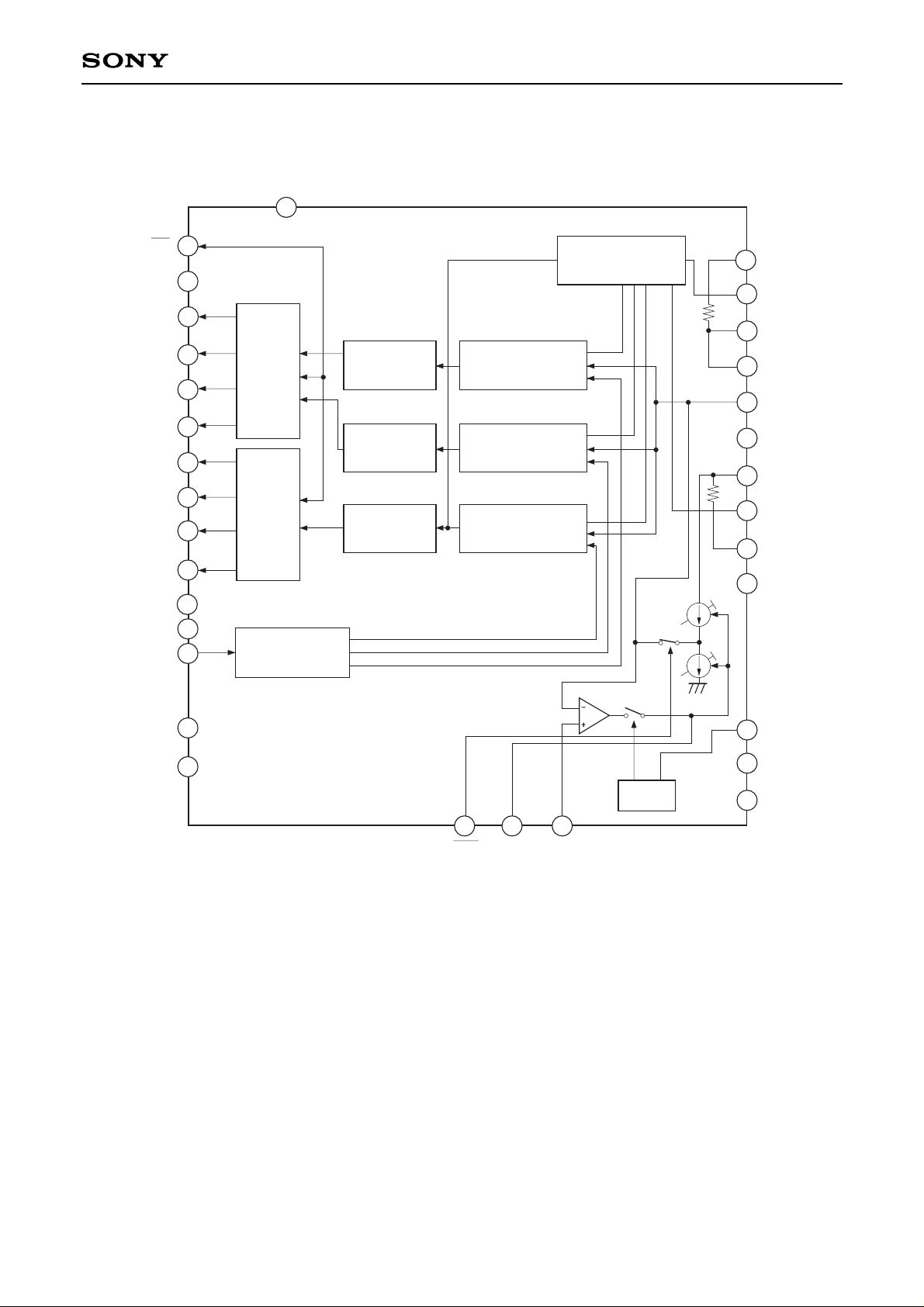

Block Diagram

D5

2

3

4

5

6

7

8

10

11

12

9

30

31

32

1

Clock generator

Upper

data

latch

Lower

data

latch

Lower encoder

(4 BIT)

Lower encoder

(4 BIT)

Upper encoder

(4 BIT)

Lower sampling

comparator (4 BIT)

Lower sampling

comparator (4 BIT)

Upper sampling

comparator (4 BIT)

Reference supply

26

27

29

28

25

24

23

22

21

20

19

18

17

16

15

14

13

DVss

CCP VREFCLE

VRBS

VRB

AVss

AVss

V

IN

AVDD

AVDD

VRT

VRTS

AV

DD

CLP

TEST

(V

DD or Vss)

TEST

(V

DD or Vss)

NC

TEST (OPEN)

CLK

TEST (DV

DD)

DV

DD

D7 (MSB)

D6

D4

D3

D2

D1

D0 (LSB)

DVss

OE

—3—

CXD2300Q

Pin Description

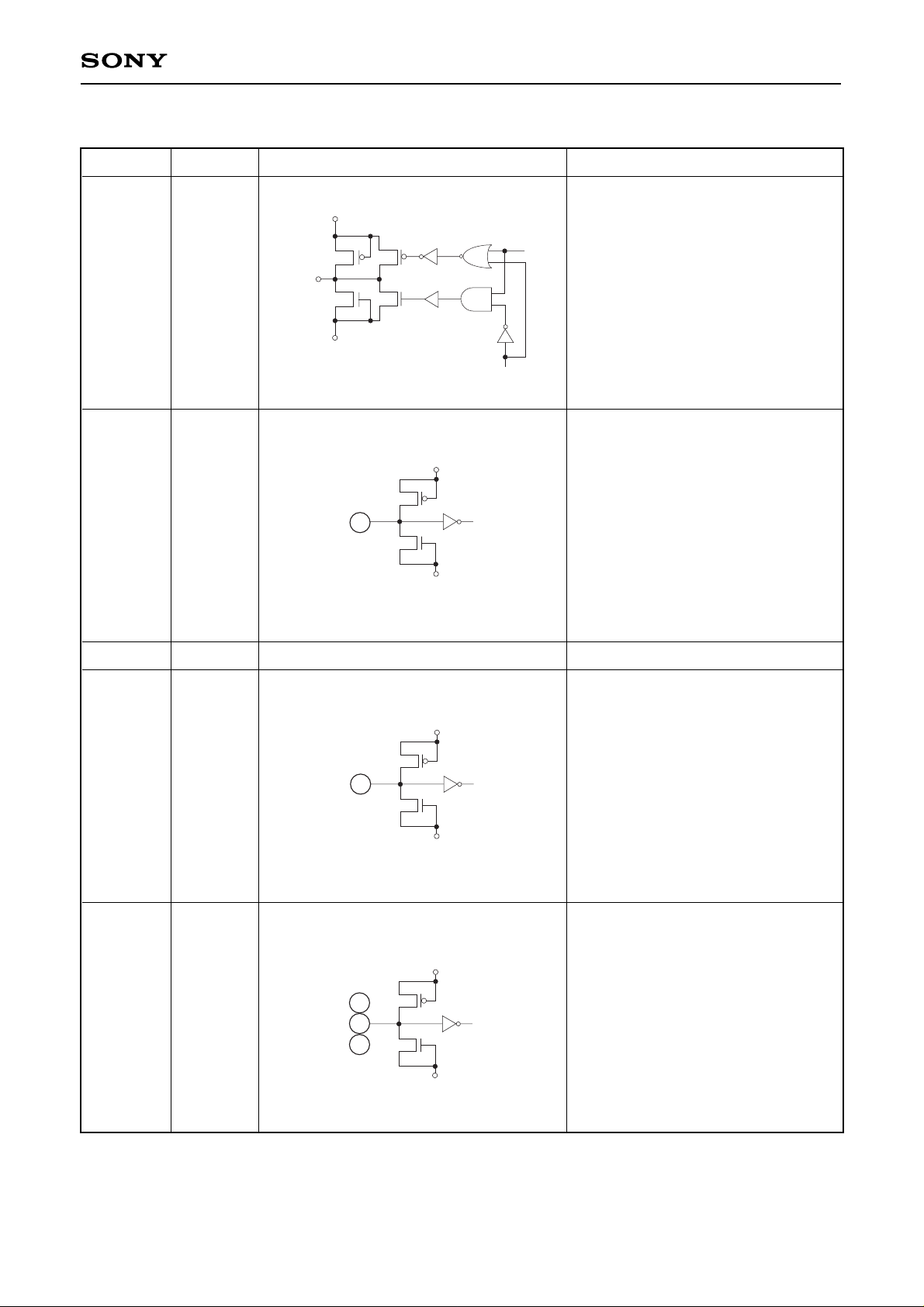

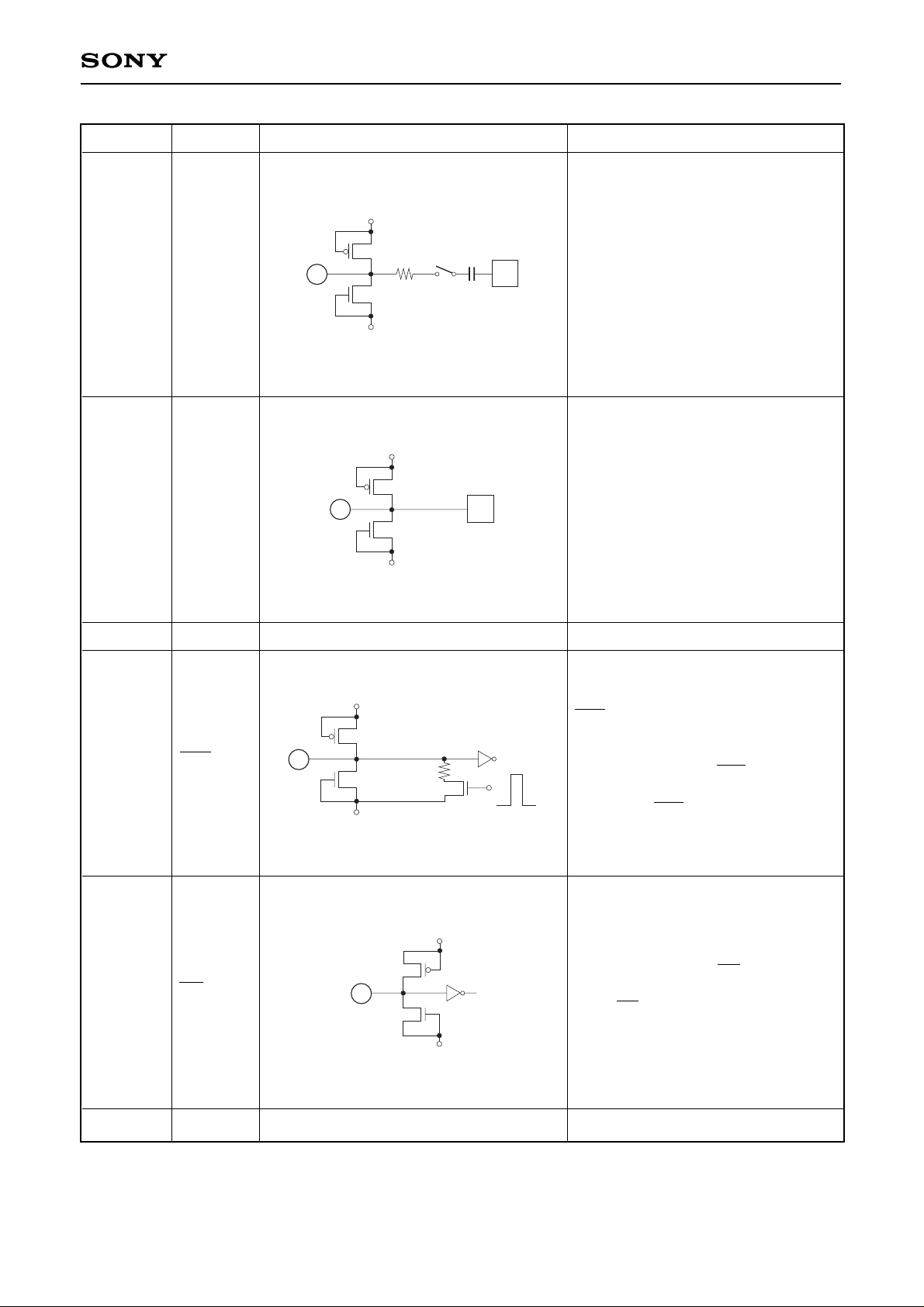

Pin No. Symbol Equivalent circuit Description

1 to 8

D0 to D7

TEST

CLK

TEST

D0(LSB) to D7 (MSB) output

Leave open during normal usage.

Clock input

Fix Pin 11 to VDD, Pins 13 and 14 to

VDD or VSS during normal usage.

9

12

11, 13, 14

Di

9

DV

DD

DVSS

12

DVDD

DVSS

11

13

14

DV

DD

DVSS

10

DVDD

Digital + 3.3 V

—4—

CXD2300Q

15

CLP

18

VRT

24

VRB

21 VIN

25

VRBS

17

VRTS

Inputs clamp pulse to Pin 15 (CLP).

Clamps the signal voltage during Low

interval.

Generates about +1.8 V when shorted

with VRT.

Reference voltage (top)

Reference voltage (bottom)

Analog input

Generates about +0.4 V when shorted

with VRB.

Pin No. Symbol

Equivalent circuit Description

22, 23

AVSS

16, 19, 20 AVDD

15

DV

DD

DVSS

17

AV

DD

18

24

AVDD

AVSS

AVDD

AVSS

21

25

AV

SS

Analog + 3.3 V

Analog ground

—5—

CXD2300Q

Pin No. Symbol Equivalent circuit Description

26 VREF

CCP

CLE

OE

Clamp reference voltage input.

Clamps so that the reference voltage

and the input signal during clamp

interval are equal.

Integrates the clamp control voltage.

The relationship between the changes

in CCP voltage and in VIN voltage is

positive phase.

The clamp function is enabled when

CLE = Low.

The clamp function is set to off and

the converter functions as a normal

A/D converter when CLE = High.

The clamp pulse can be measured by

connecting CLE to DVDD through a

several hundred Ω resistor.

Data is output when OE = Low.

Pins D0 to D7 are at high impedance

when OE = High.

27

29

30

AVDD

AVSS

26

AVDD

AVSS

27

DVDD

DVSS

29

CLAMP

PULSE

DVDD

DVSS

30

28, 31

DVSS

Digital ground

32

NC

NC pin

Loading...

Loading...