Sony CXD2073S Datasheet

Description

The CXD2073S is an adaptive comb filter compatible

with NTSC system, and provide high-precision Y/C

separation with a single chip.

Features

• Y/C separation by adaptive processing

• Horizontal aperture compensation circuit

• 8-bit A/D converter (1 channel)

• 8-bit D/A converter (2 channels)

• One 1H delay line

• Clamp circuit

Absolute Maximum Ratings (Ta = 25°C, VSS = 0V)

• Supply voltage DVDD VSS – 0.5 to +7.0 V

DAVD VSS – 0.5 to +7.0 V

ADVD VSS – 0.5 to +7.0 V

PLVD VSS – 0.5 to +7.0 V

• Input voltage VI VSS – 0.5 to VDD +0.5 V

• Output voltage VO VSS – 0.5 to VDD +0.5 V

• Operating temperature

Topr –20 to +75 °C

• Storage temperature

Tstg –55 to +150 °C

Recommended Operating Conditions

• Supply voltage DVDD 5.0 ± 0.25 V

DAVD 5.0 ±0.25 V

ADVD 5.0 ±0.25 V

PLVD 5.0 ± 0.25 V

• Operating temperature

Topr –20 to +75 °C

Structure

Silicon gate CMOS IC

Applications

Y/C separation for color TVs and VCRs

– 1 –

CXD2073S

E97412B86-PS

Digital Comb Filter (NTSC)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

30 pin SDIP (Plastic)

For the availability of this product, please contact the sales office.

– 2 –

CXD2073S

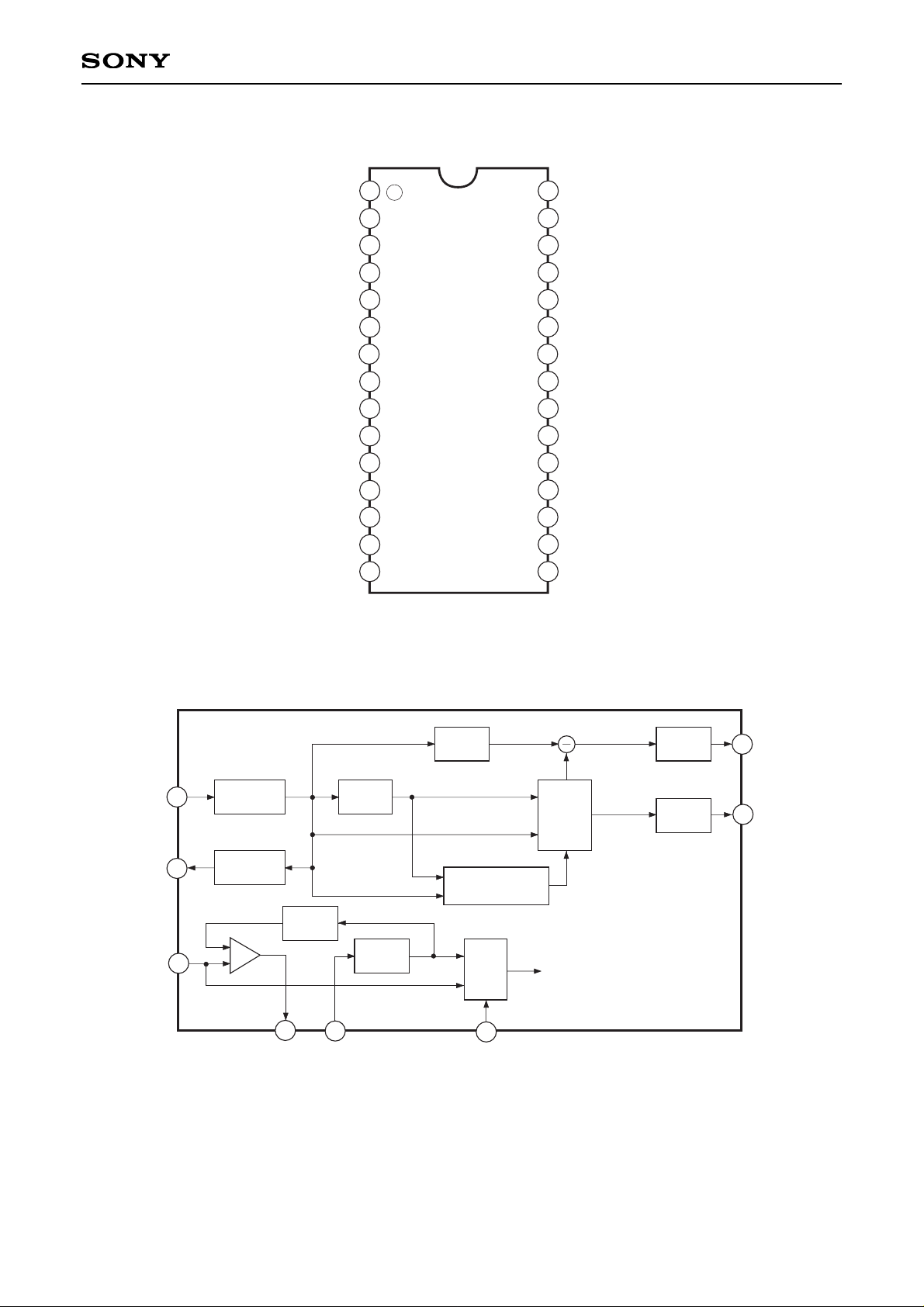

Pin Configuration (Top View)

Block Diagram

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

VCV

CPO

CKSL

FIN

TST1

TST2

DV

SS

DVDD

DVDD

DVSS

TST3

APCN

MOD1

MOD2

INIT

PLVD

PLVS

CLPEN

CLPO

ADIN

ADVS

ADVD

ACO

DAVD

AYO

DAVS

VRF

VG

VB

IRF

AYO

ACO

CKSL

VCV

CPO

FIN

CLPO

ADIN

A/D 1H

Clamp

DL D/A

D/A

1/4

VCO

SEL

Logic Operation

Block

Chroma

Output

Block

Internal clock

4

5

8

10

27

28

29

30

– 3 –

CXD2073S

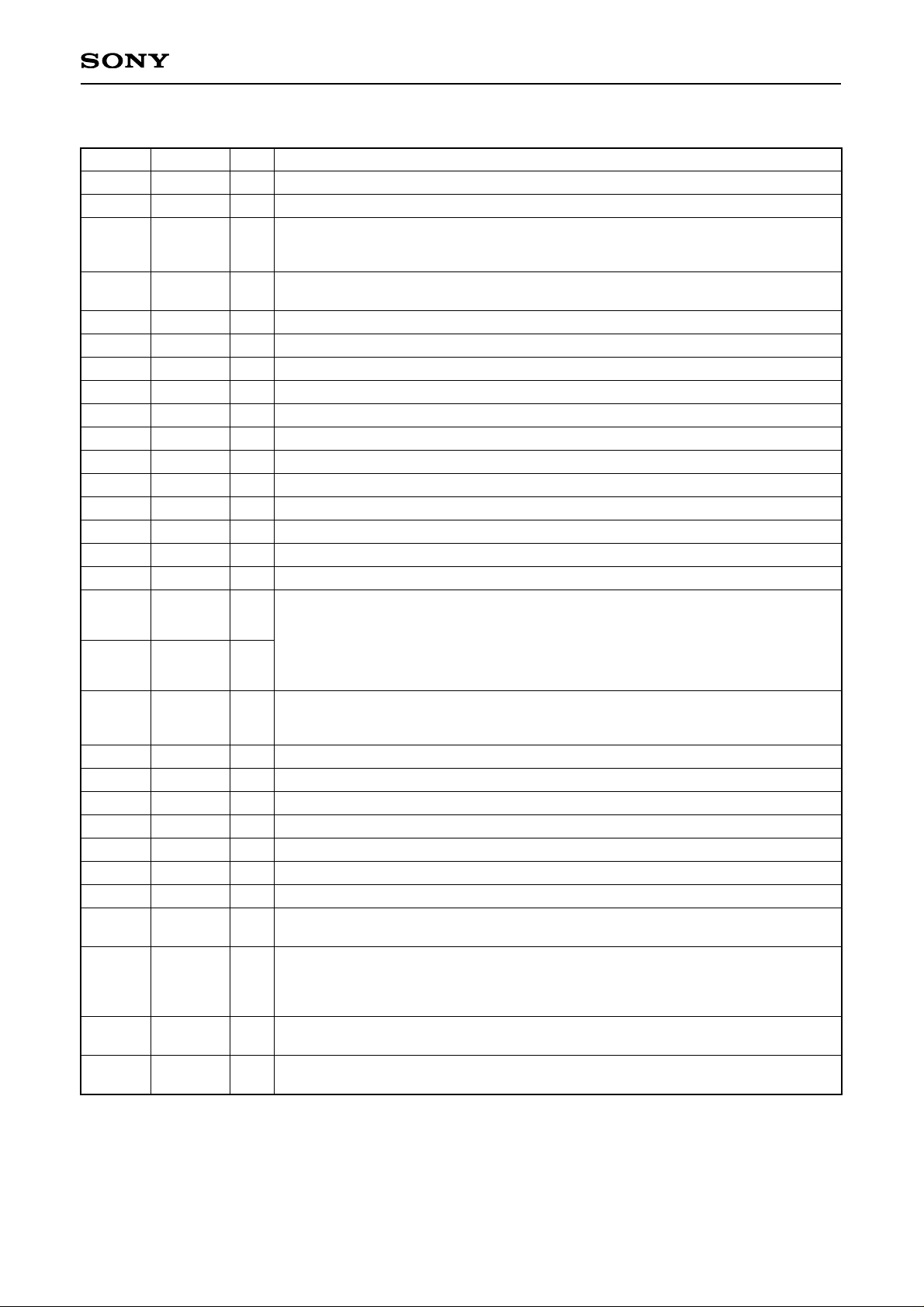

Pin Description

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

19

20

21

22

23

24

25

26

27

28

29

30

PLVD

PLVS

CLPEN

CLPO

ADIN

ADVS

ADVD

ACO

DAVD

AYO

DAVS

VRF

VG

VB

IRF

INIT

APCN

TST3

DVSS

DVDD

DVDD

DVSS

TST2

TST1

FIN

CKSL

CPO

VCV

—

—

I

O

I

—

—

O

—

O

—

I

O

O

O

I

I

O

—

—

—

—

O

I

I

I

O

I

Analog power supply for PLL (+5V)

Analog ground for PLL

Clamp enable

L: Clamp function is enabled. Set to L when the internal clamp is used.

H: Clamp function is disabled. Set to H when the internal clamp is not used.

Connect to ADIN when clamp circuit is used.

Leave this pin open when clamp circuit is not used.

Comb filter analog input (A/D converter input)

Analog ground for A/D converter

Analog power supply for A/D converter (+5V)

Analog chroma signal output

Analog power supply for D/A converter (+5V)

Analog luminance signal output

Analog ground for D/A converter

D/A converter reference voltage setting. Sets the full-scale value for D/A converter.

Connect to DAVD via a capacitor of approximately 0.1µF.

Connect to DAVS via a capacitor of approximately 0.1µF.

Connect a resistor of 16 times (16R) that of the output resistor "R" of AYO pin.

Test. Normally, fix to Low.

Y/C separation status setting pins

MOD2 MOD1

L L Adaptive processing mode

L H BPF separation fixed mode

H L Y through mode

H H Simple comb mode

Aperture compensation switching

L: Aperture compensation OFF

H: Aperture compensation ON

Test. Normally, leave this pin open.

Digital ground

Digital power supply (+5V)

Digital power supply (+5V)

Digital ground

Test. Normally, leave this pin open.

Test. Normally, fix to Low.

Clock input. Input burst-locked clock. Input fsc when the PLL is used. Input 4fsc

when the PLL is not used.

PLL control.

L: When the PLL is not used. The 4fsc clock input to FIN is supplied internally.

H:When the PLL is used. The 4fsc clock from VCO oscillation output is

supplied internally.

Phase comparison output for the internal PLL. Leave open when the PLL is not

used.

VCO oscillation control voltage input for the internal PLL. Connect to PLVS when

the PLL is not used.

Symbol I/O Description

17 MOD2 I

18 MOD1 I

– 4 –

CXD2073S

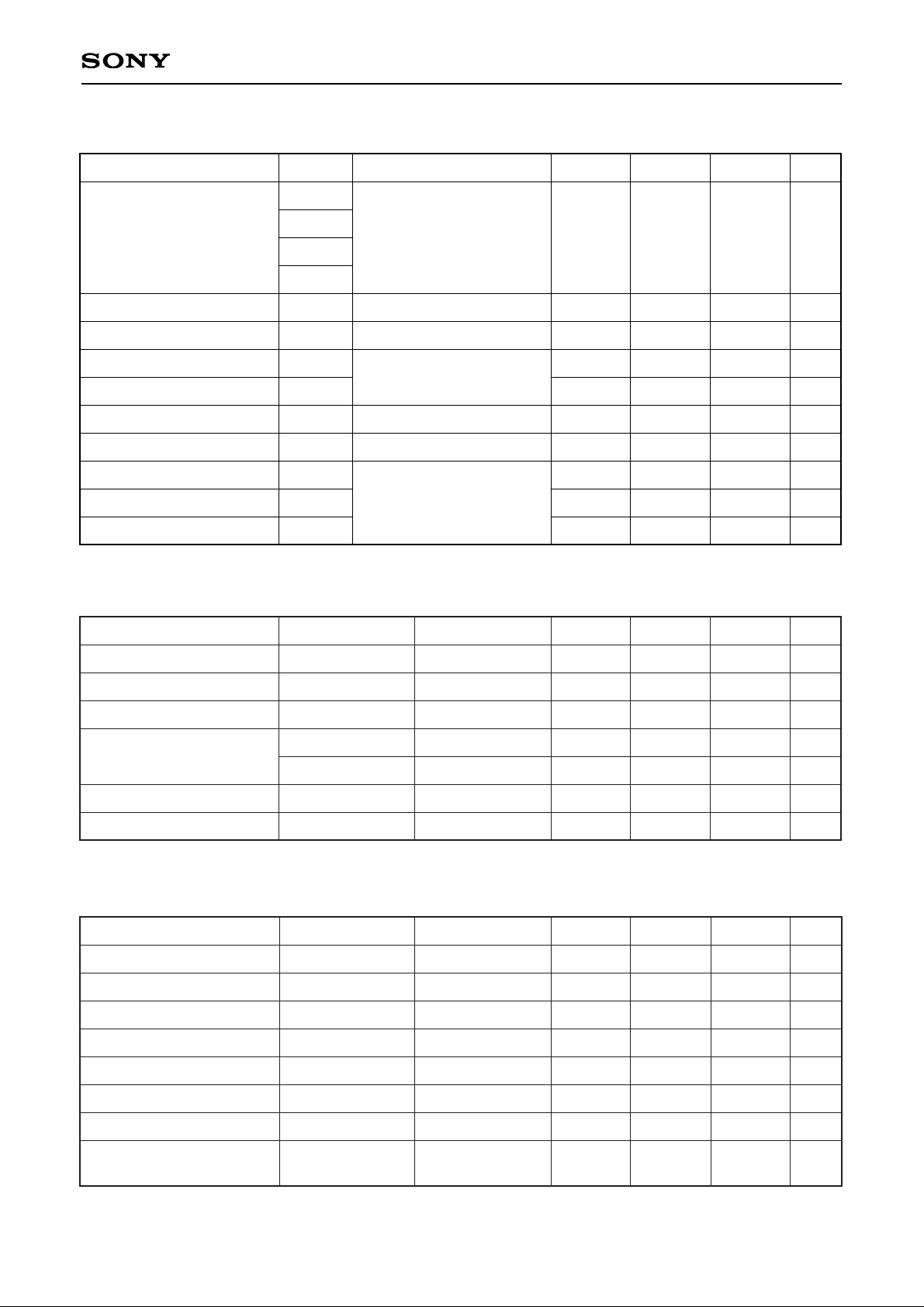

Electrical Characteristics (VDD = 5 ± 0.25V, VSS = 0V, Ta = –20 to +75°C)

Symbol

DVDD

ADVD

DAVD

PLVD

Topr

IDD

VIH

VIL

VOH

VOL

LVth

VIN

RFB

Conditions

—

—

Clock 14MHz

IOH = –2mA (Pin 20 and 25)

IOL = 4mA (Pin 20 and 25)

FIN (Pin 27)

Min.

4.75

–20

—

VDD × 0.7

VSS

VDD – 0.8

VSS

—

0.5

250k

Typ.

5.0

—

55

—

—

—

—

VDD/2

—

1M

Max.

5.25

+75

80

VDD

VDD × 0.3

VDD

0.4

—

VDD

2.5M

Unit

V

°C

mA

V

V

V

V

V

Vp-p

Ω

Item

Supply voltage

Operating temperature

Supply current

High level input voltage

Low level input voltage

High level output voltage

Low level output voltage

Logical Vth

Input voltage

Feedback resistor

A/D Converter Characteristics (VDD = 5V, Ta = 25°C, f = 10MHz)

Symbol

n

fmax

BW

BOTTOM

TOP – BOTTOM

ED

EL

Conditions

–3dB

Min.

—

14.3

—

0.48

1.96

–1.0

–3.0

Typ.

8

—

18

0.52

2.08

—

—

Max.

—

—

—

0.56

2.22

+1.0

+3.0

Unit

bit

MSPS

MHz

V

V

LSB

LSB

Item

Resolution

Max. conversion speed

Analog input band width

Input bias

Differential linearity error

Integral linearity error

D/A Converter Characteristics (VDD = 5V, VRF = 2V, IRF = 3.3kΩ, R = 200Ω, Ta = 25°C, f = 10MHz)

Symbol

n

fmax

ED

EL

VFS

IFS

VOS

VOC

Conditions

—

—

—

—

—

—

—

Min.

—

14.3

–0.8

–2.0

1.805

—

—

1.8

Typ.

8

—

—

—

1.90

9.5

—

—

Max.

—

—

+0.8

+2.0

1.995

15

1.0

2.1

Unit

bit

MSPS

LSB

LSB

V

mA

mV

V

Item

Resolution

Max. conversion speed

Differential linearity error

Integral linearity error

Output full-scale voltage

Output full-scale current

Output offset voltage

Precision guaranteed

output voltage range

CMOS level

(Pin 3, 16 to 19, 26, 28)

Loading...

Loading...