Sony CXA1700AR, CXA1700AQ Datasheet

CXA1700AQ/AR

For the availability of this product, please contact the sales office.

Luminance and Color Signal Processing for 8mm VCR

Description

The CXA1700AQ/AR is an IC designed for 8mm

VCR Y/C main signal processing for consumer use.

Equipped with many built-in filters, the

CXA1700AQ/AR is a one-chip main signal

processing system that greatly reduces the number

of external components.

Features

• Built-in auto-adjusting filters

• Supports simple Hi-8 video.

• Supports camera recording.

• Supports power saving mode.

140mW for composite signal input

250mW for separate signal input

• Supports electronic volume (EVR) control.

• Supports BUS LINE.

• Supports NTSC/PAL.

Function

2-input INPUT SELECT, VIDEO AGC, DDS (Y

signal superimposition), synchronous separation,

75Ω VIDEO OUT DRIVE, Y/C mixing, Y/C

separation comb filter, Y/C cross talk elimination,

playback chroma feedback comb, Y dropout

compensation, Yd playback switching, Y signal H

correlation detection, Y pre-emphasis/de-emphasis,

white/dark clipping, clipping compensation,

MOD/DEMOD, HHS/HHS cancel, ACC, chroma

emphasis/de-emphasis, burst emphasis/deemphasis, XO/VXO, APC, AFC, APC ID, AFC ID,

burst ID, ACK, APC compensation, HHK, PI/PS,

frequency conversion system, PB C BPF, REC C

LPF, PB C LPF, CARRIER BPF, 4.1V regulator

CXA1700AQ CXA1700AR

64 pin QFP (Plastic) 64 pin LQFP (Plastic)

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta=25°C)

• Supply voltage VCC 7V

•Operating temperature Topr –10 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• allowable power dissipation

(when mounted on board)

PD CXA1700AQ 1050 mW

CXA1700AR 1010 mW

Operating Condition

• Supply voltage VCC 4.75

+0.5

–0.25

V

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

—1—

E94X25-TE

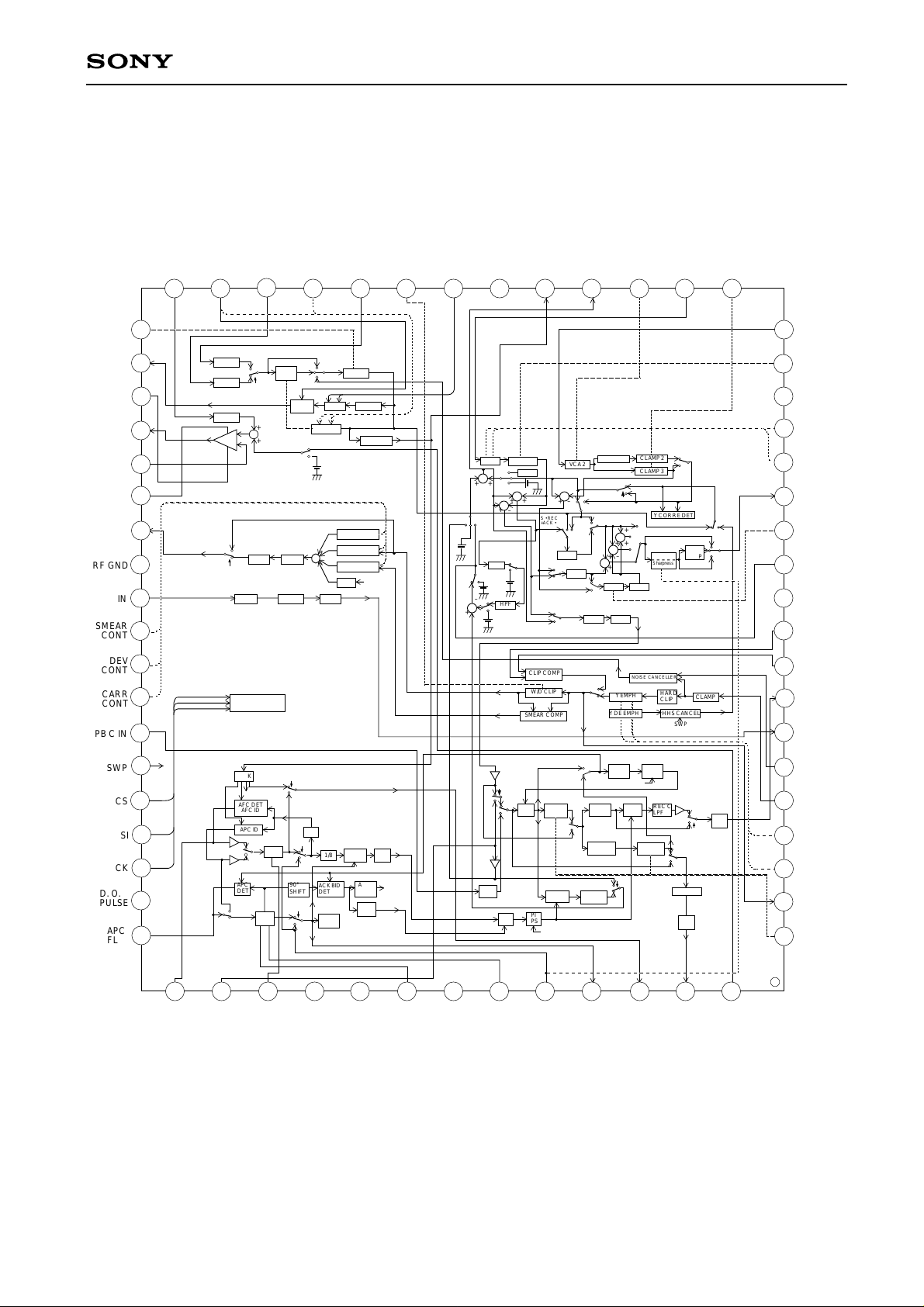

Block Diagram and Pin Configuration

A

A

A

(CXA1700AQ)

CXA1700AQ/AR

CLAMP

TC1

Y OUT

V OUT

GND

VIDEO

OUT

INV IN

RF/V

VCC

Y RF

OUT

RF GND

Y RF IN

SMEAR

CONT

DEV

CONT

CARR

CONT

PB C IN

SWP

CS

CK

D. O.

PULSE

APC

FL

Y IN

32

REC L/

31

V IN1

JVD

30

AGC TC1

29

V IN2

28

WDC

DDS/

27

26

33

34

35

36

37

CLAMP

CLAMP

CLAMP

ON

AGC OFF

VIDEO

AGC

INSEL

VD/H D

INSER T

+

+

+

–

PB

AG C DET

S • REC+PB

REC

DDS

CLAMP

Y MUTE

SYNC SEP

38

39

40

TEST2

LIM MOD

41

SMEAR. CONT

LPFDEMODLIM

CAR. CONT

DEV. CO NT

HHS

SWP

S • R EC

42

43

44

CXA1700AQ

BUS

DECODER

45

46

47

48

SI

49

50

51

HHK

AF C DET

APC

DET

PB

REC

BF

AFC ID

APC ID

TEST2

1/N

REC

PB

TEST1

VCO

90°

SHIFT

CAM REC

VXO

XO

1/8

ACK BID

DET

fo

AUTO

CAR

CONV

ACK

CONT

BID

FF

CAR

BPF

ACK

MASK

25

VCA 1

++

PB

REC

ATT

PB • AC K

–

+

NO CORR

PB C

LPF PB

+

HPF

CAR

INV

W • PB

CC

V

S • R EC

C SEL

REC

PB

CL AMP 1

SYNC

++

–

EDIT

ACC

AMP

SMEAR CO MP

SYNC

COMP

24

+

–

S • R EC

+ACK • REC

EQ

PB

REC

PB+REC • CORR

RE C • (S+443+ED IT+NO COR R)

CLI P COM P

W/ D CLIP

CROMA

EMPH

REC

PB

CONV

PI

PS

SWP

VCA 2

TRAP

TC2

fsc

TRAP

DL OUT1

TEST1

REC

CLAMP

ACK

SW

PB

SHP

THROU

E

CLAMP

20

19

DL OUT2

CLAMP

18

TC3

NC

17

16

AGC TC3

15

COMB

ADJ

14

Y COMB

OUT

13

LIM C

12

C TRAP

11

VG1

DEEMPH

10

IN

COMP TC

9

REC

8

C OUT

7

DEMO D

OUT

NC TC IN

6

EMPH IN

5

SUB

4

EMPH TC

MAIN

3

EMPH TC

MAIN

2

EMPH OUT

C EMPH

1

CONT

DL IN1

23

Yd PB

W •PB

PB

W • PB

ATT

PB

REC

REC

PB

BURST

EMPH

BURST

DEEMPH

PB C

BPF

DOC TRAP

DOP

++

+

–

+

BPF

Y EMPH

Y DE EMPH

ACC

DET

TEST1

22

S •R EC

+ACK • REC

+

Yd PB

PB

REC

ATTLIM

NOISE CANCELLER

SWP

REC

CONV

CROMA

DEEMPH

AGC TC2

CL AMP 2

CL AMP 3

Y CO RRE DE T

Sharpness

ACC

CONT

REC C

LPF

21

W • PB

EQ

HARD

CLIP

HHS CANCE L

SWP

PB

REC

C MUT E

ACK

SW

53

52

EXT

C IN

FL

AFC

I REF

DC FB

GND

IN

X TAL

59

60 61 62 63 6454 55 56 57 58

FSC

V REG

SHP

CAM FSC

OUT

X TAL

OUT

VCO

BF

C IN

C OUT

—2—

Block Diagram and Pin Configuration

(CXA1700AR)

CXA1700AQ/AR

VG1

AGC TC3

COMB ADJ

Y COMB OUT

16

15

14

NC

17

TC3

CLAMP

W • PB

DL OUT2

19 18

TC2

CLAMP

DL OUT1

21 20

AGC TC2

22

DL IN1

SYNC

COMP

V

CC

MASK

DDS/

CL AMP 2

DOC TRAP

VCA 2

CL AMP 1

W • PB

VCA 1

Y CO RRE DE T

CL AMP 3

S • R EC

DOP

Yd PB

SYNC

++ +–

S • R EC

+–

++

WDC

Y MUTE

V IN2

AGC TC1

CLAMP

DDS

AGC OFF

PB

ON

VD/H D

INSER T

VIDEO

AGC

V IN1

JVD

REC L/

Y IN

32 31 30 29 28 27 26 25 24 23

INSEL

CLAMP

CLAMP

CLAMP

C TRAP

LIM C

13

12

PB

E

SHP

THROU

REC

fsc

TRAP

EQ

Sharpness

REC

++

S • REC+PB

+

ATT

PB

+

LIM

+–

TRAP

EQ

PB

REC

EDIT

ATT

PB • AC K

REC

–

Yd PB

+

+ACK • REC

W • PB

PB

S • R EC

+ACK • REC

PB

REC

S • R EC

SYNC SEP

AG C DET

+

+

DEEMPH IN

11

10

BPF

W • PB

ATT

PB+REC • CORR

RE C • (S+443+ED IT+NO COR R)

HPF

NO CORR

–

+

DEV. CO NT

CAR. CONT

REC C O UT

COMP TC

9

8

CLAMP

HHS CANCE L

HARD

CLIP

NOISE CANCELLER

Y EMPH

Y DE EMPH

PB

REC

W/ D CLIP

CLI P COM P

SMEAR CO MP

SWP

HHS

SMEAR. CONT

LPFDEMODLIM

LIM MOD

TEST2

NC TC IN

DEMO D OUT

7

SWP

EMPH IN

SUB EMPH TC

6

5

4

ACK

SW

TEST1

PB

REC C

LPF

ACC

CONT

SWP

ACC

DET

PB

REC

C SEL

CROMA

DEEMPH

REC

CONV

BURST

EMPH

BURST

DEEMPH

PB

REC

CROMA

EMPH

ACC

AMP

PB

REC

MAIN EMPH OUT

MAIN EMPH TC

3

REC

TEST1

PB C

C EMP H CONT

2

1

C IN

64

C OUT

ACK

SW

C MUT E

PB C

BPF

PB

CONV

SWP

PI

PS

CAR

INV

LPF

636261

VCO

BF

OUT

FSC

SHP

60

5958

CAM FSC

OUT

X TAL

V REG

IN

X TAL

5756

GND

I REF

ACK

CAR

BPF

CAR

CONV

CXA1700AR

TEST2

BF

HHK

BUS

DECODER

AF C DET

1/8

1/N

TEST1

VCO

PB

REC

APC ID

AFC ID

BID

FF

ACK

CONT

fo

AUTO

ACK BID

DET

90°

SHIFT

VXO

XO

APC

DET

PB CAM REC

REC

55

DC FB

54

C IN

EXT

53

FL

AFC

525149

FL

APC

PULSE

D. O.

50

CK

33

35

34

36

Y OUT

CLAMP TC1

VIDEO OUT

V OUT GND

38

39

37

INV IN

RF/V VCC

40

RF GND

Y RF OUT

42

41

43

Y RF IN

DEV CONT

SMEAR CONT

45

46

47

CS

48

SI

44

SWP

PB C IN

CARR CO NT

—3—

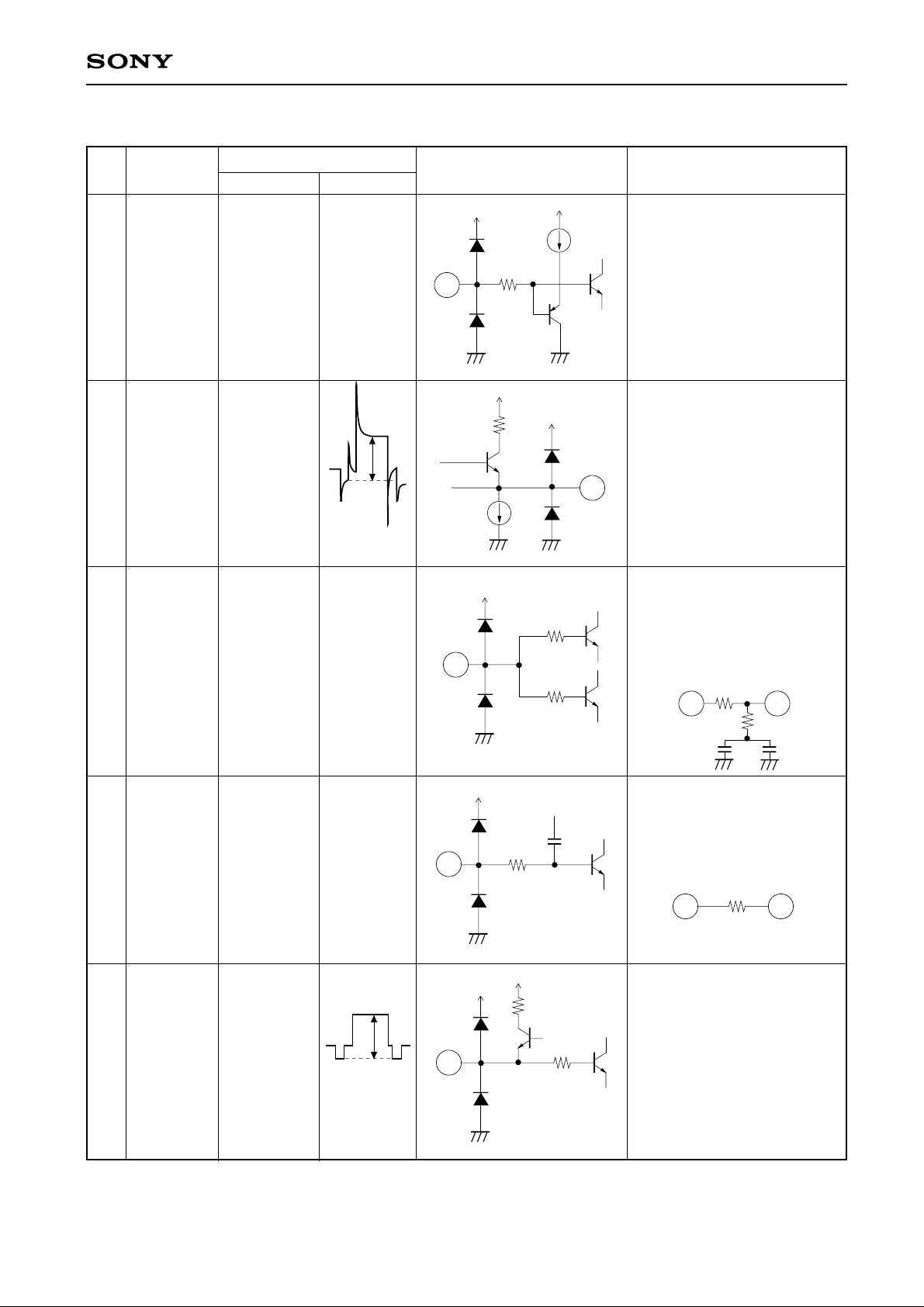

Pin Description

CXA1700AQ/AR

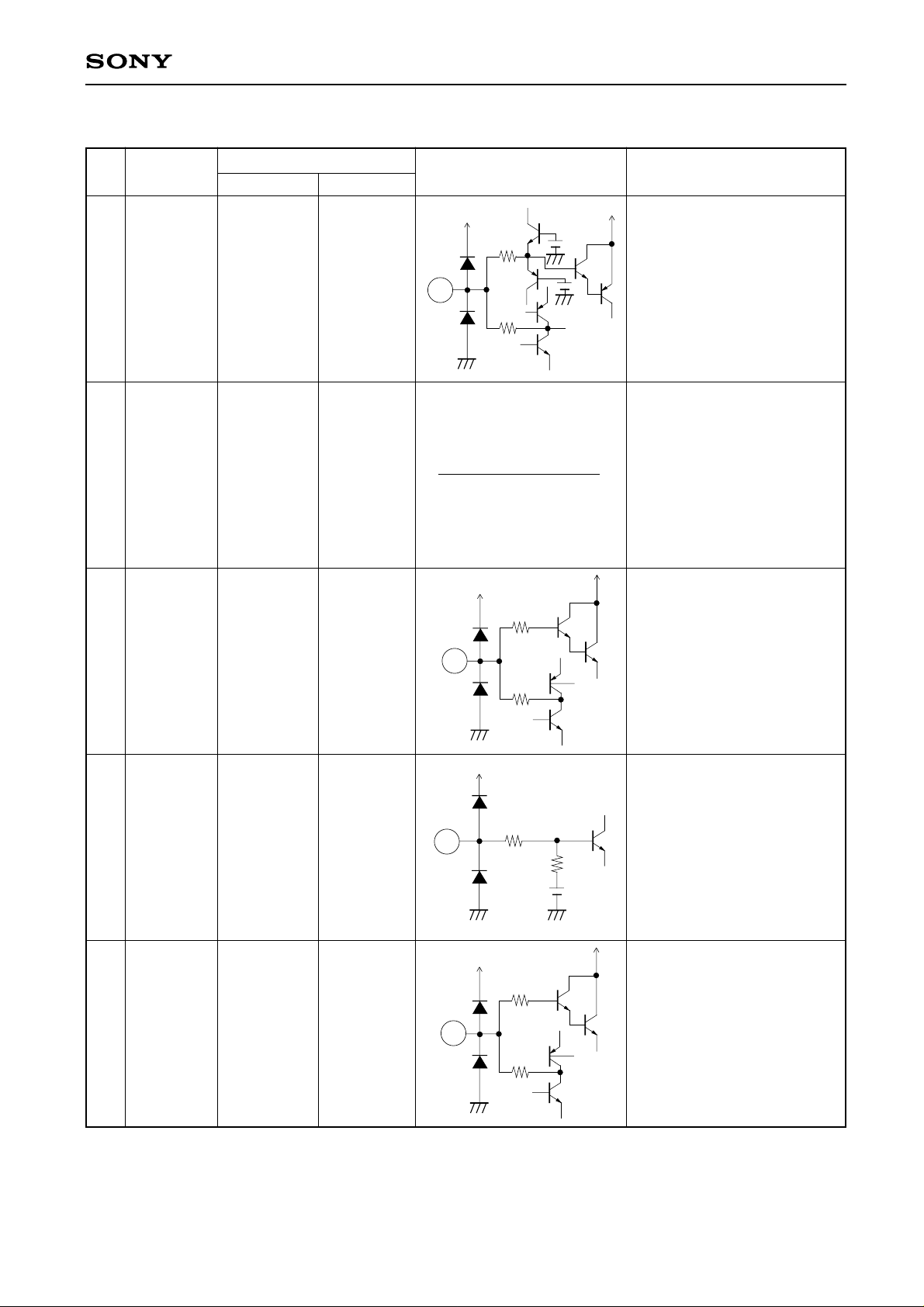

Pin

No. DC AC

Symbol

1 C EMPH

CONT

Control

range:

Pin voltage

—

1.8V to 3.8V

2 MAIN

EMPH

2.05V (sync

tip level)

OUT

250mVp-p

Output

3 MAIN

EMPH

TC

2.05V (when

time constant

connected)

—

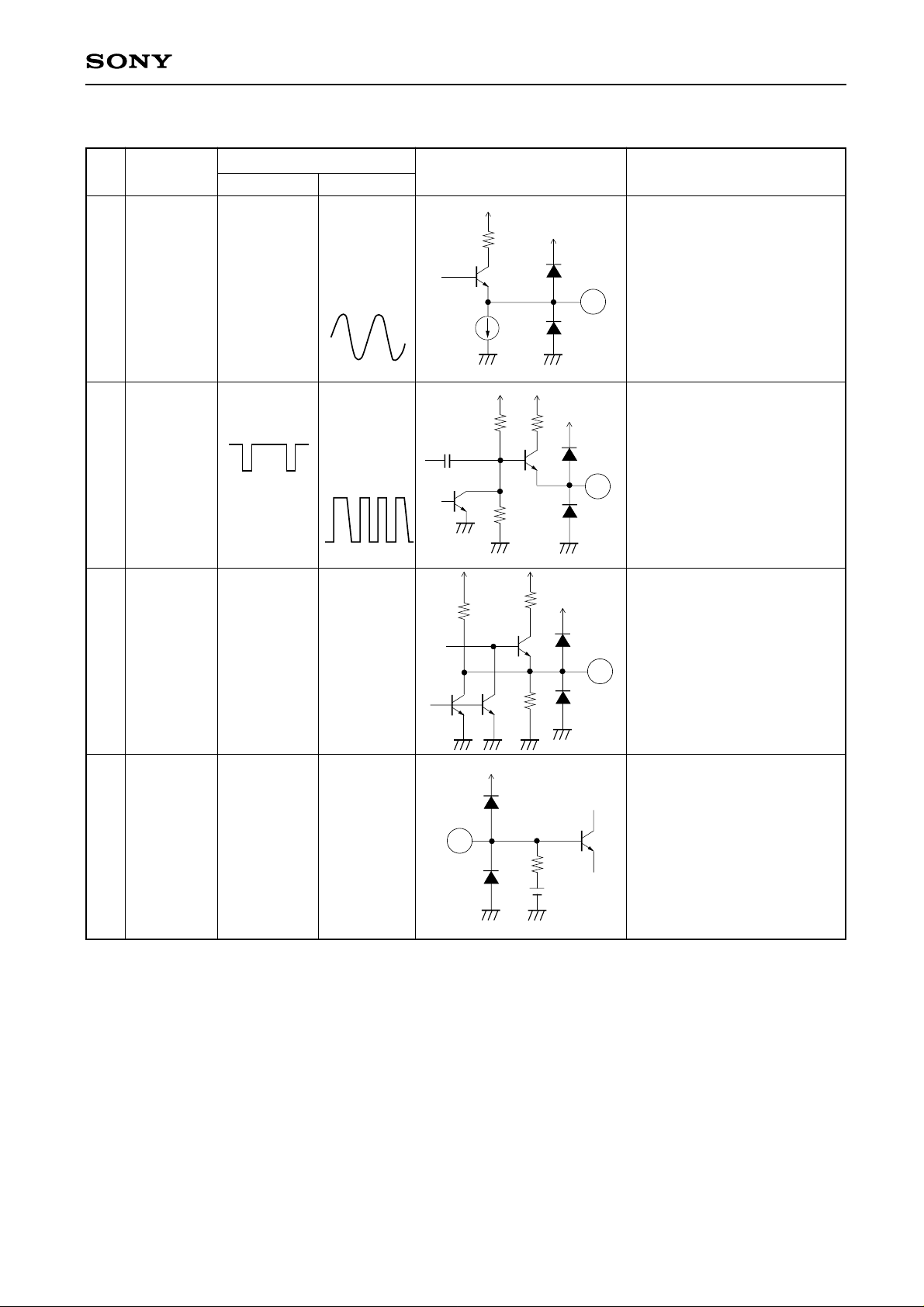

Equivalent circuit Description

Chroma emphasis f0 (center

25µA

frequency) adjustment. (Refer

to item 7 on Description of

1

150

Operation.)

Main emphasis and main de-

150

emphasis time constant.

When recording, the

emphasized Y signal prior to

2

white/dark clipping is output.

1mA

Main emphasis and main deemphasis time constant. Apply

4k

an external constant between

this pin and Pin 2, as shown

3

below.

4 SUB

EMPH

TC

5 EMPH IN

2.05V (when

time constant

connected)

2.05V (sync

tip level)

—

500mVp-p

Input

100

2 3

HPF time constant that forms

sub emphasis and sub de-

100

4

emphasis. Add resistance

between this pin and Pin 11.

411

VG1

During recording, Y emphasis

100

input. During playback, this

signal to the noise canceler is

input. Performs diode

5

150

clamping (sync tip clamping),

with the clamp capacitance

attached externally.

—4—

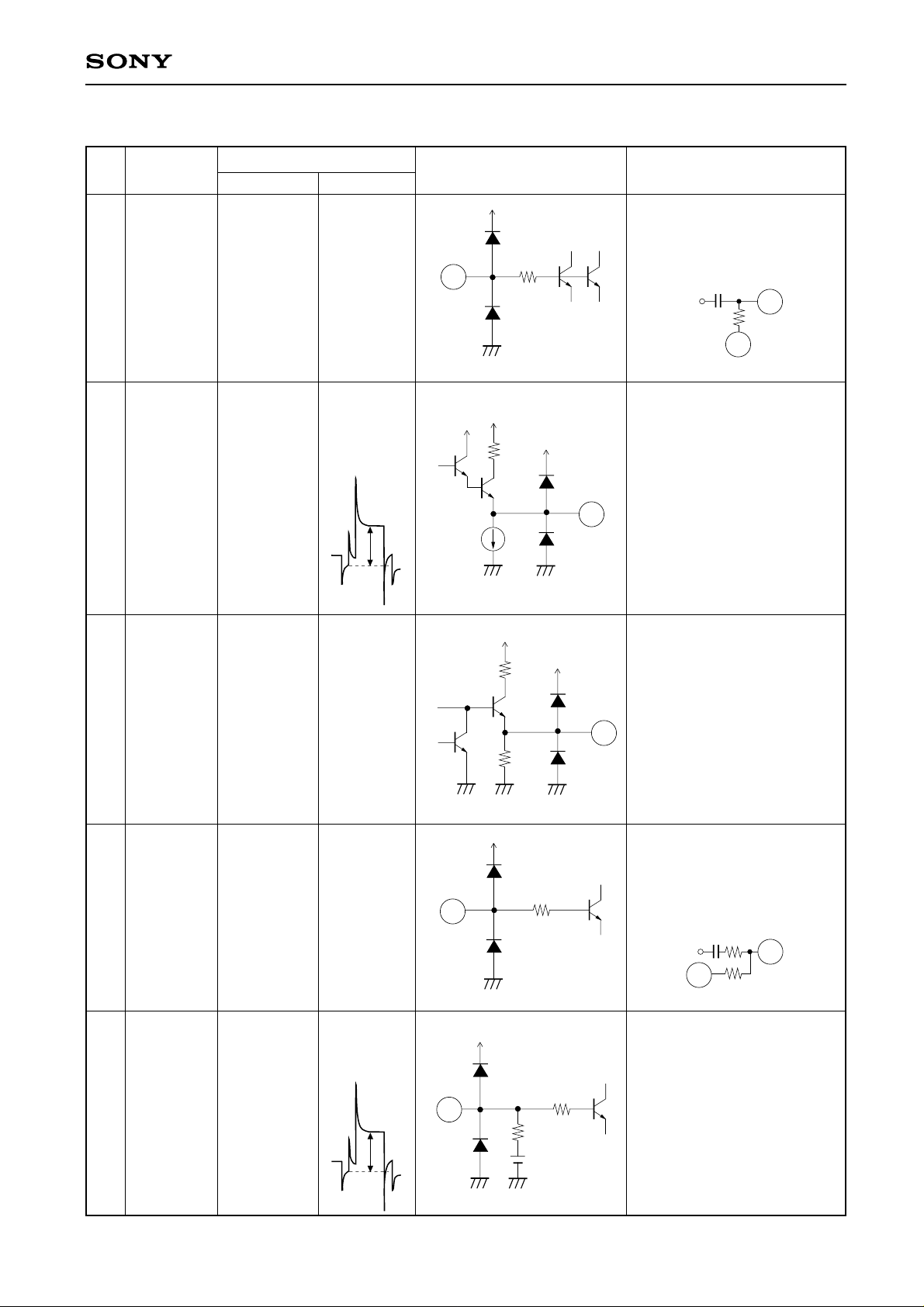

CXA1700AQ/AR

Pin

No. DC AC

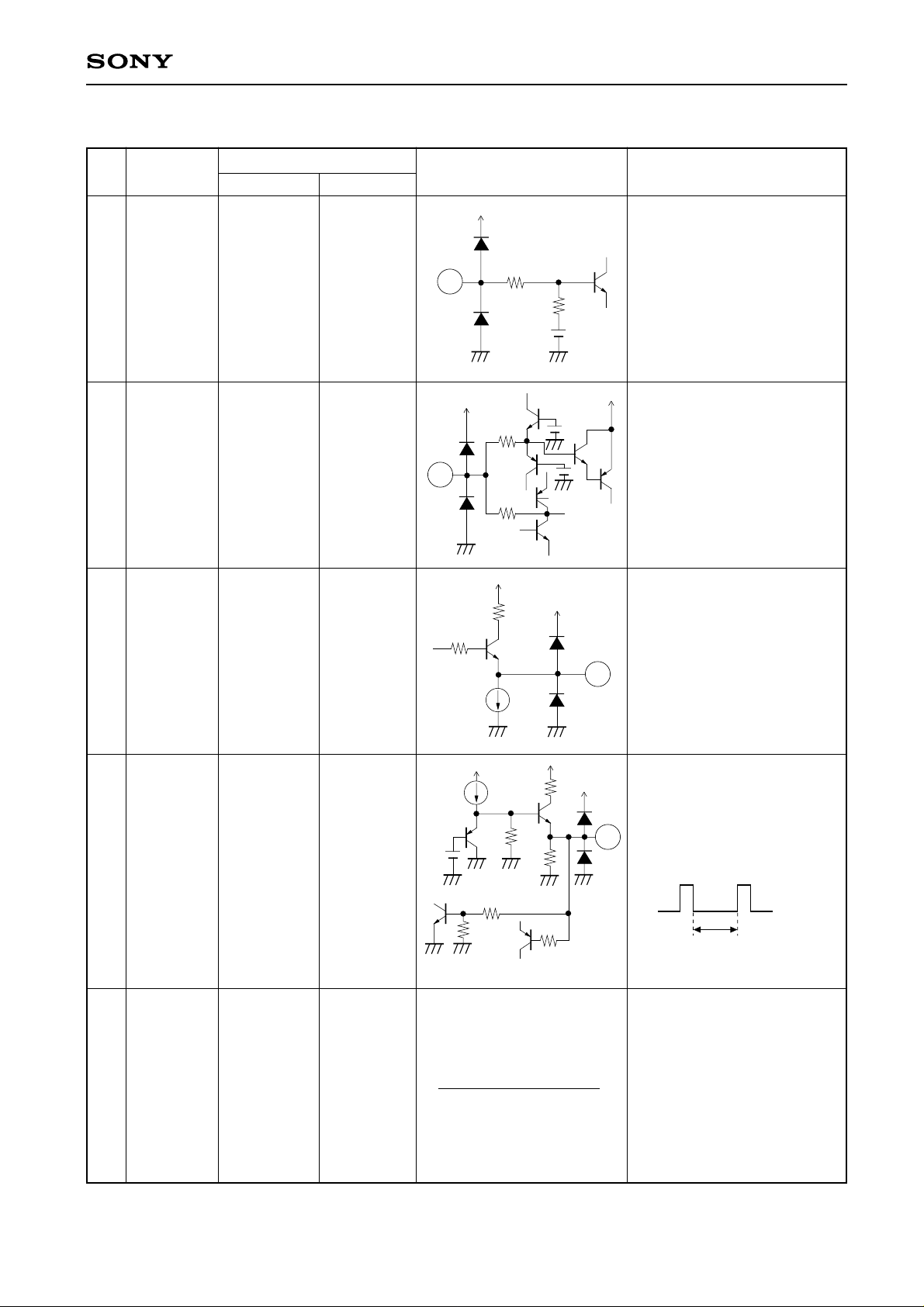

Symbol

6 NCTC IN

2.05V (when

Pin voltage

—

time constant

connected)

7 DEMOD

OUT

1.6V

140mVp-p

output during

standard

playback

Equivalent circuit Description

Connects external time

constant for HPF of noise

canceler. (Refer to item 11 on

6

150

Description of Operation.)

Input

11

VG1

Y signal output that has been

FM demodulated and has

63

passed though the DEMOD

LPF.

7

1mA

6

8 REC C

OUT

9 COMP TC

10 DEEMPH

IN

2.0V

2.05V (when

time constant

connected)

2.05 V

(center DC)

Lowfrequency

conversion

chroma

signal

300mVp-p

output

—

180mVp-p

input during

playback

SAT

10

During recording, a chroma

signal that has been burst

200

emphasized, chroma

emphasized, and frequency

converted is output. During

8

4k

ACK, the output DC goes to

0V. During recording, if

TEST1 is High the burst

emphasized signal is output.

Connects external time

constant for HPF of the

white/dark clipping

9

150

compensation circuit during

playback.

9

11

VG1

Input for de-emphasis circuit

during playback. The signal is

input to the de-emphasis

150

circuit through the clipping

compensation circuit.

5k

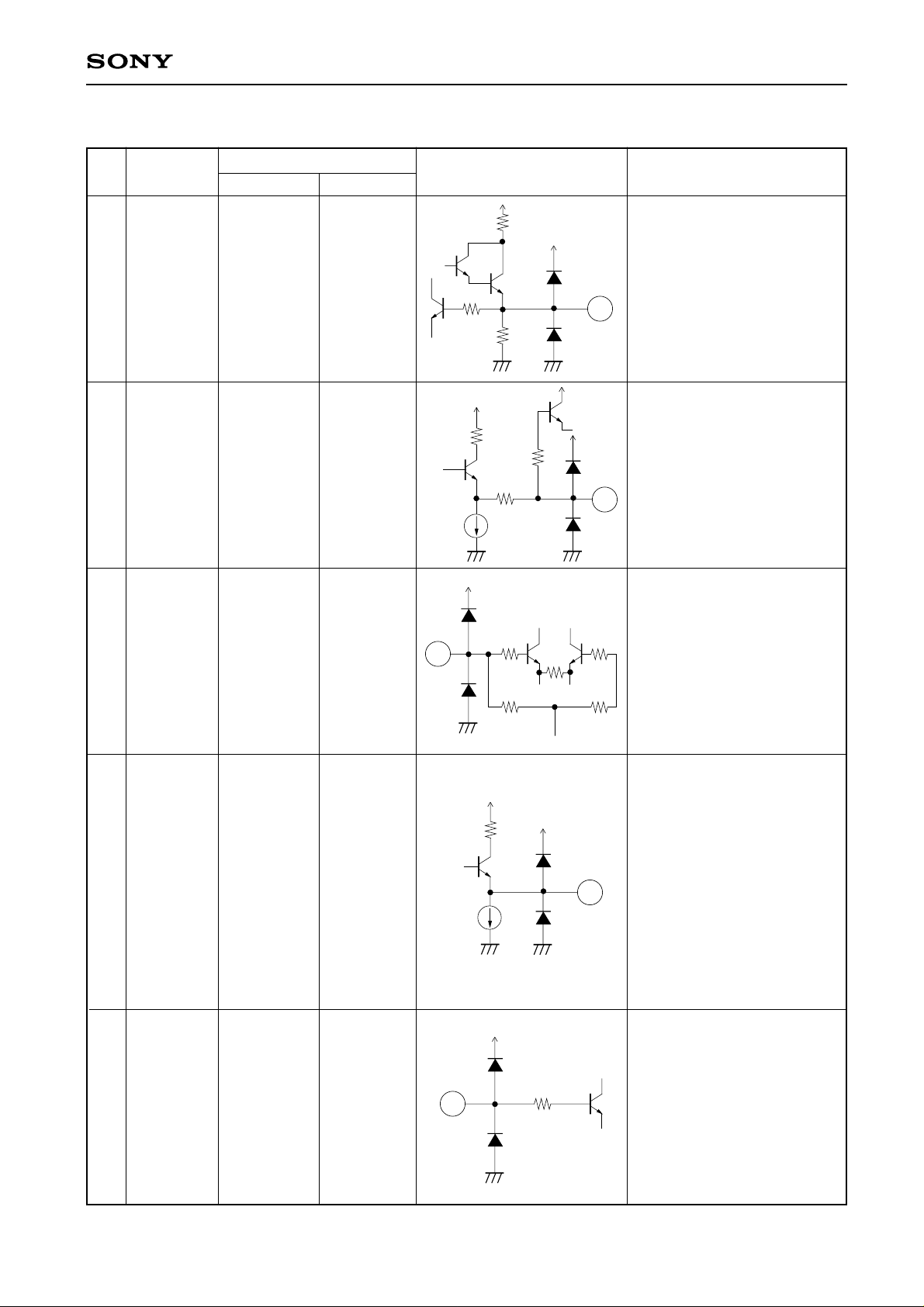

—5—

2.05V

CXA1700AQ/AR

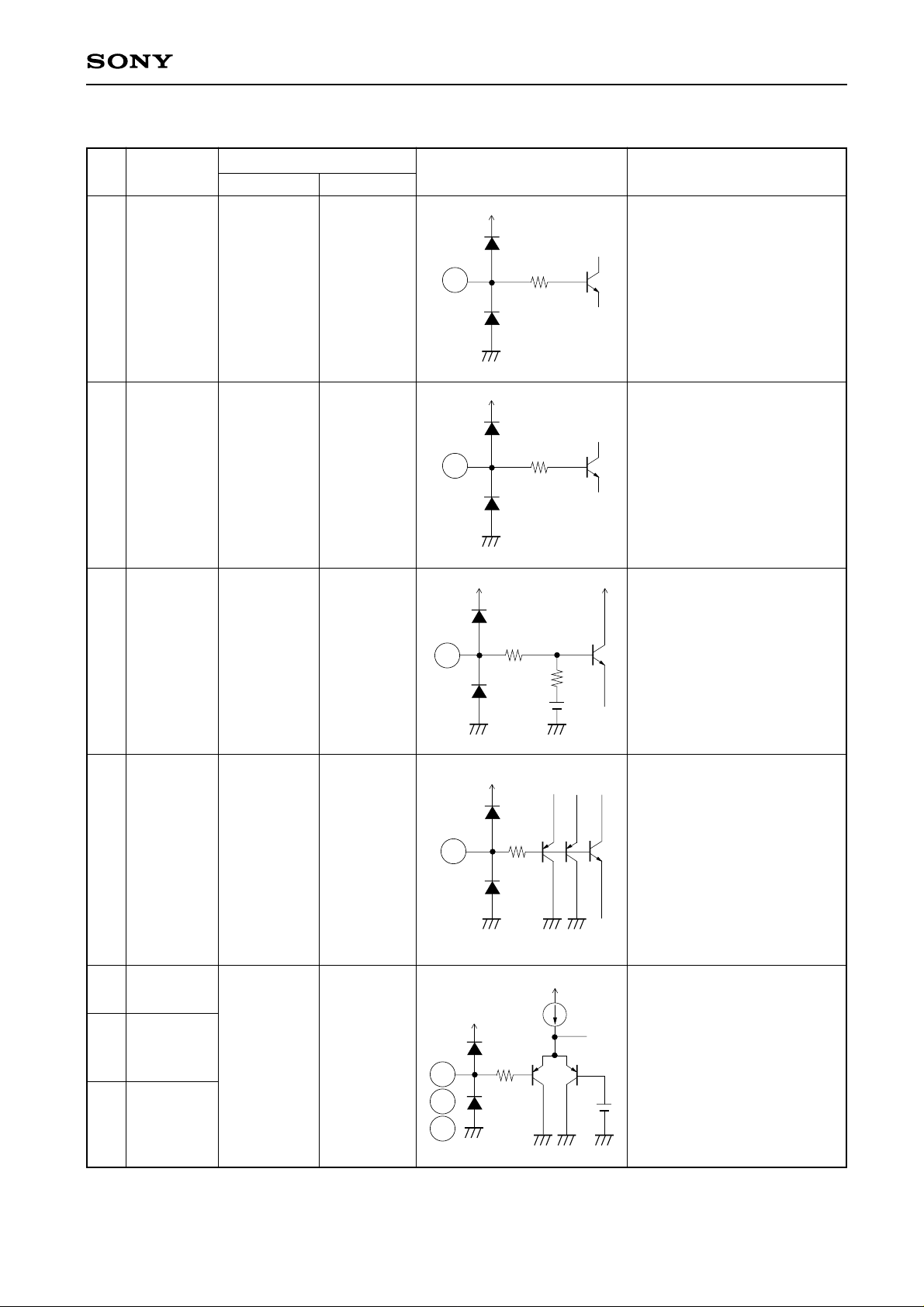

Pin

No. DC AC

Symbol

11 VG1

12 C TRAP

2.05V

2.05V

Pin voltage

—

Chroma

signal

300mVp-p

output during

playback

13 LIM C

2.4V

—

Equivalent circuit Description

150

Internal reference voltage

source. (Can not be used as

external bias for Pins other

than 4, 6, and 9.)

2.5k

3k

11

Outputs chroma signal that

has passed through PB C

0.6mA

270

150

300

BPF and chroma feedback

comb filter subtracter

after frequency conversion

12

during playback.

Connects decoupling

capacitor for limiter of the

playback Y comb block.

13

150

150

14 Y COMB

OUT

15 COMB ADJ

1.2V

(sync tip

level)

Control

range: 1.8V

to Vcc

Y signal

500mVp-p

output

—

1.4mA

15

10k

150

150

14

10k

Outputs Y signal processed by

comb filter. During playback,

the signal is output through

the sharpness circuit. If mode

E is set High, the signal is

output without passing

through the f sc Trap; if mode

SHP THRU is set High, the

signal is output without

passing through the sharp

-ness circuit.

VCA gain adjustment in the

comb filter block. (Refer to

Adjustment Procedure.)

—6—

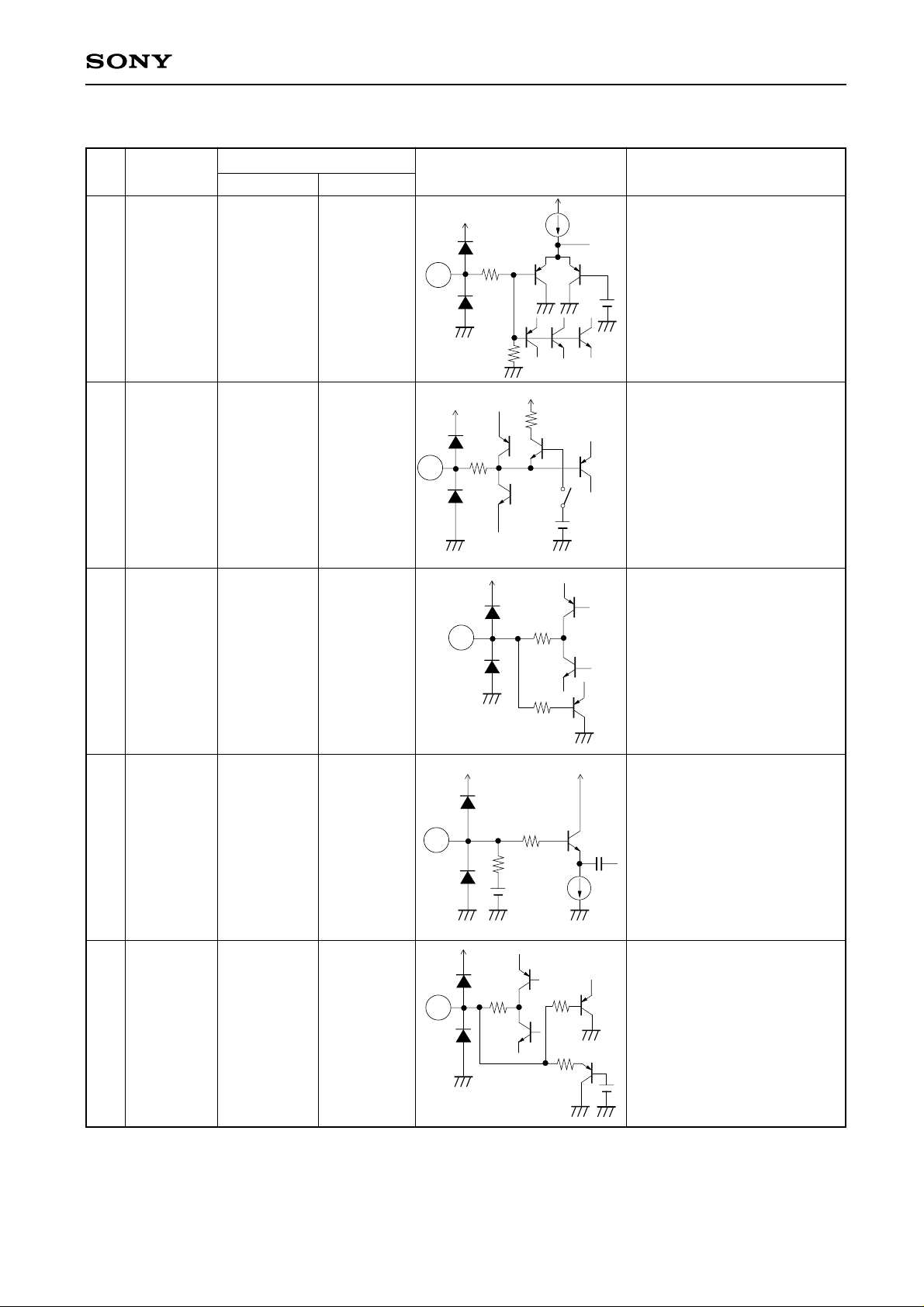

CXA1700AQ/AR

Pin

No. DC AC

16 AGC TC3

Symbol

2.2V to 4.0V

17 NC

18 CLAMP

Pin voltage

—

—

—

—

—

TC3

Equivalent circuit Description

Time constant for VCA circuit

150

in comb filter block. A DC

limiter circuit with an upper

16

150

limit of 4.0V and a lower limit

of 2.2V is built in.

Not connected. Normally,

connect to GND.

Time constant for feedback

150

clamp circuit in the comb filter

block.

19 DL OUT2

20 CLAMP

TC2

2.1V (center

DC)

—

Video

500mVp-p

input

—

19

20

18

150

150

150

Inputs CCD DL (delay line)

output signal to the VCA

circuit.

40k

2.1V

Time constant for feedback

clamp circuit in the comb filter

block.

150

—7—

CXA1700AQ/AR

Pin

No. DC AC

Symbol

21 DL OUT1

2.1V (center

DC)

Pin voltage

Video

500mVp-p

input

22 AGC TC2

23 DL IN1

2.2V to 4.0V

2.2V

—

Video

500mVp-p

output

Equivalent circuit Description

Inputs CCD DL (delay line)

output signal to VCA circuit.

21

150

40k

2.1V

Time constant for VCA circuit

150

in the comb filter block. A DC

limiter circuit with an upper

22

150

limit of 4.0V and a lower limit

of 2.2V is built in.

Output for inputting a signal to

150

150

the CCD DL (delay line).

Normally, Y+C signal is

output.

23

1mA

24 COMP

SYNC

25 VCC

High : 2.5V,

Low : 0V

output

VCC=4.75V

—

—

20k

50k

20k

5k

270

270

Composite sync signal output.

No output if mode SYNC SEP

OFF is set High.

24

1H

Main block power supply.

2.5V

0

—8—

CXA1700AQ/AR

Pin

No. DC AC

26 DDS/MASK

Symbol

2.0V

Pin voltage

—

(when open)

(MASK)

1.5V

(DDS)

2.3 to 3.0V

27 WDC

2.6V

—

(when open)

28 V IN2

2.05V

(sync tip

level)

Video

500mVp-p

input

Equivalent circuit Description

Input for VOW (character

level) signal, VOB (character

background) timing pulse of

DDS (date display system)

2.0V

and masking timing pulse.

MASK : VTH = 1.1V

DDS : VTH = 2.0V

By varying the input DC for

26

150

1.1V

DDS over a range of 2.3V to

45k

16k

15k

3.0V, the character level can

be changed.

(Refer to item 4 on Description

of Operation.)

Determines the white/dark

4.1V

clipping levels. When open,

the standard white clipping

level is 235%, and the dark

clipping level is 95%.

(Mode DC1, 2 = Low, High)

27

150

30k

10k

2.05V

(Refer to item 5 on Description

of Operation.)

270

Video signal input. Performs

diode clamping, with the

clamp capacitance externally

28

connected. If the mode MUTE

is set High, the charge of the

100nA

4µA

MUTE

ON

clamp capacitance is

discharged.

29 AGC TC1

—

—

29

—9—

100

1k

47k

MUTE ON

PB ON

Time constant for the video

AGC circuit in the I/O block.

During mute and playback, the

charge of the external

capacitance is discharged.

CXA1700AQ/AR

Pin

No. DC AC

Symbol

30 V IN1

2.05V

(sync tip

level)

31 REC L/JVD

1.9V

Pin voltage

Video

500mVp-p

input

—

(Typical value

during REC

LEVEL

adjustment)

32 Y IN

1.6V

(sync tip

level)

Video

500mVp-p

input

Equivalent circuit Description

270

Video signal input. Performs

diode clamping, with the

clamp capacitance externally

30

connected. If the mode MUTE

is set High, the charge of the

100nA

4µA

MUTE

ON

clamp capacitance is

discharged.

Level adjustment during

recording. The adjustment

range is 1.3V to 2.6V. During

playback, serves as input for

31

150

JOG (variable speed

playback) VD pulse and HD

pulse.

VTH = 2.7V

(Refer to item 3 on Description

of Operation.)

Video signal input for video

270

out circuit. Performs diode

clamping, with the clamp

32

capacitance externally

connected.

100nA

33 CLAMP TC1

34 Y OUT

—

1.8V

(sync tip

level)

—

Video

500mVp-p

output

33

3.4k

—10—

27k

2.05V

3k

100

100

Time constant for feedback

clamp circuit in I/O block.

I/O block signal output.

150

34

CXA1700AQ/AR

Pin

No. DC AC

35 VOUT GND

36 VIDEO

Symbol

OUT

0V

1.6V

(sync tip

level)

37 INV IN

1.5V

Pin voltage

—

Video

2.0Vp-p

output

Video

1.0Vp-p

input

38 RF/V VCC

39 Y RF OUT

VCC=4.75V

2.1V

—

Y FM output

500mVp-p

Equivalent circuit Description

GND for the video out circuit.

38

Video out 75Ω driver output.

100

37

Inverted input for V sag

compensation for the video

36

out 75Ω driver.

Video out circuit and RF

system block power supply.

35

During recording, FM-

63

63

modulated Y signal output.

If mode TEST2 is set High

during recording, the Y signal

39

2.5mA

after white/dark clipping is

output.

40 RF GND

41 Y RF IN

42 SMEAR

CONT

0V

—

Control

range:

1.8V to Vcc

—

YFM

200mVp-p

input

—

41

42

150

10p

150

RF block GND.

During playback, inputs Y-RF

signal to FM modulation

circuit.

45k

During recording, adjustment

for high Luminance Smear

Compensation.

—11—

CXA1700AQ/AR

Pin

No. DC AC

Symbol

43 DEV CONT

Control

Pin voltage

—

range:

1.8V to Vcc

44 CARR

CONT

Control

range:

—

1.8V to Vcc

45 PB C IN

3.1V

(during

playback)

(PB Y RF)

+

(PB C RF

100mVp-p)

input

Equivalent circuit Description

During recording, adjustment

for deviation of Y-FM

modulation.

43

150

During recording, adjustment

for carrier of Y-FM modulation.

44

150

During playback, chroma RF

signal input.

PB C LPF is built in, so that a

45

150

50k

3.1V

signal with the AFM and ATF

components (Y RF + C RF)

eliminated can be input.

46 SWP

47 CS

48 SI

49 CK

—

High : Vcc,

Low : 0V

input

—

—

47

48

49

46

150

150

2.05V

RF SWP (switching pulse) and

HCHG (head change) pulse

input. Half H shift, HHS

cancel, ACC channel hold,

and PI/PS switching operate

at VTH = 0.7V. Yd playback

during playback operates at

VTH = 2.05V (same as when

mode Yd is High).

Input to BUS DECODER. CS

is used as chip select, and

data is latched at rising edge.

CK is the clock input. Use a

clock frequency fck of less

than 1.3MHz. SI is used as a

serial data input.

—12—

CXA1700AQ/AR

Pin

No. DC AC

50 D.O.PULSE

Symbol

High : 3.1V,

Pin voltage

—

Low : 0V

input

51 APC FL

2.25V (typ.)

—

during lock

52 AFC FL

2.25V (typ.)

—

during lock

Equivalent circuit Description

Drop out pulse input.

VTH = 2.05V

50

150

2.05V

If the drop out pulse is input,

the signal prior to 1H is output

for the Y system and the APC

and ACC system errors are

100k

held for the C system.

Connects an APC external

filter.

200

51

during

playback

Connects an AFC external

filter.

52

200

53 EXT C IN

54 DCFB

2.6V

2.25V (typ.)

during lock

(Chroma

signal

314mVp-p

input

—

53

54

200

150

50k

2.6V

200

200

200

During recording, the chroma

signal is input. When the

typical level is 75% color bar

input, the input signal is

314mVp-p.

Connects a DC feedback

external filter for a nonadjustment VCO.

—13—

CXA1700AQ/AR

Pin

No. DC AC

Symbol

55 I REF

1.8V (when

Pin voltage

—

resistance

connected)

56 GND

57 XTAL IN

0V

2.0V

—

260mVp-p

(NTSC)

during

playback

Equivalent circuit Description

External reference current

source. Connect external

resistance of 18kΩ to GND.

20k

55

Be careful concerning

interference pin.

Main block GND.

Crystal oscillation reference

input. Be careful concerning

57

during

playback

2V

270

270

4k

2V

interference pin and the

floating capacitance.

58 VREG

59 XTAL OUT

60 CAM FSC

SHP

4.1V

3.1V

Sharpness

control range:

1.8V to VCC

—

340mVp-p

(NTSC)

during

playback

—

60

15k

310

540µA

200

100

9p

58

60k

4.1V regulator output.

Crystal oscillation reference

output. Connects the crystal

between this pin and Pin 57.

59

Subcarrier input during

camera recording.

200mVp-p(min). Sharpness

control during playback.

—14—

CXA1700AQ/AR

Pin

No. DC AC

61 FSC OUT

Symbol

2.2V

Pin voltage

NTSC

600mVp-p

PAL

450mVp-p

62 BF VCO

During BF

output

550mVp-p

during VCO

output

High : 1.8V,

Low : 0V

Low during

BF interval

63 C OUT

2.0V

Chroma

signal

314mVp-p

output

(during

recording)

64 C IN

2.05V

Chroma

signal

314mVp-p

input

Equivalent circuit Description

Subcarrier output. This

200

subcarrier is used for the CCD

delay line clock frequency.

61

0.5mA

Burst flag and VCO OUT

20046k

9p

output for testing. When using

this pin, connect 3.3kΩ

resistance to GND. Serves as

62

VCO output when mode

SAT

54k

TEST2 is High.

During recording, outputs

100

200

chroma signal after Y/C

separation or for chroma

signal input from Pin 53.

63

During playback, the playback

2k

chroma signal is output.

During ACK, the output DC

becomes 0V.

Inputs chroma signal to Y/C

MIX circuit in the I/O block.

During component signal

64

28k

2.05V

recording or playback, this

signal is Y/C mixed and is

then output from V OUT.

—15—

CXA1700AQ/AR

mA

113

88

63

1

I

A

mA

100

78

55

I1

C

Unit

Max.

Typ.

Min.

Measurement method

mA

40

30

20

I1

D

mA

70

53

35

I1

E

mA

120

94

68

I1

F

V

4.36

4.13

3.90

CC=4.75V, voltage at Pin 58 :VREG

V

P58

A

mV

–1

–12

VCC=4.5V, voltage at Pin 58 :VREG1

P58

A

VREG–=VREG1–VREG

mV

+12

+1

VCC=5.25V, voltage at Pin 58 :VREG2

P58

A

VREG+=VREG2–VREG

V

µA

106

2.21

100

2.08

94

1.95

Voltage at Pin 11

IREF=(voltage at Pin 55 /18k

P11

P55

A

A

mV

mV

mV

143

143

550

Measures the output SYNC level

P34

B

Measures the output amplitude level

ON tions point

SW Mode Measu-

set to condi- rement

Voltage

∗ Start measurements after adjustments in accordance with the Precautions Concerning Measurements.

Input conditions Control DC Ratings

( )

Signal

Signal

Voltage

source

Frequency

Amplitude

—

source

Symbol

—

—

—

—

—

—

REC1

I

—

—

—

—

—

—

—

IREC2

—

—

—

—

—

—

—

IPS1

—

—

—

—

—

—

—

IPS2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

IPB

VREG

VREG–

VREG+

VG1

IREF

SW30

—

—

—

—

SG30

e

VAGCL

—

—

f

VAGCH

—

—

g

VAGCP

SYNC AGC

input Low level

SYNC AGC

input High level

Measurement item

Composite signal input

Current consumption

during recording

Separate signal input

Current consumption

during recording

Composite signal input

Current consumption in

power saving mode

Separate signal input

Current consumption in

power saving mode

Current consumption

during playback

Internal reference voltage

source 1

<Current consumption, reference bias source>

1

2

3

4

5

Electrical Characteristics VCC = 4.75V, Ta = 25°C, see Electrical Characteristics Test Circuit and BUS DECODER Mode Condition Table.

No.

6

CC–)

CC+)

Internal reference

voltage source 1

Internal reference

voltage source 1

7

(V

(V

8

Internal reference

voltage source 2

Reference current

source

9

10

<Y recording>

11

12

PEAK AGC

Video AGC

13

—16—

Loading...

Loading...