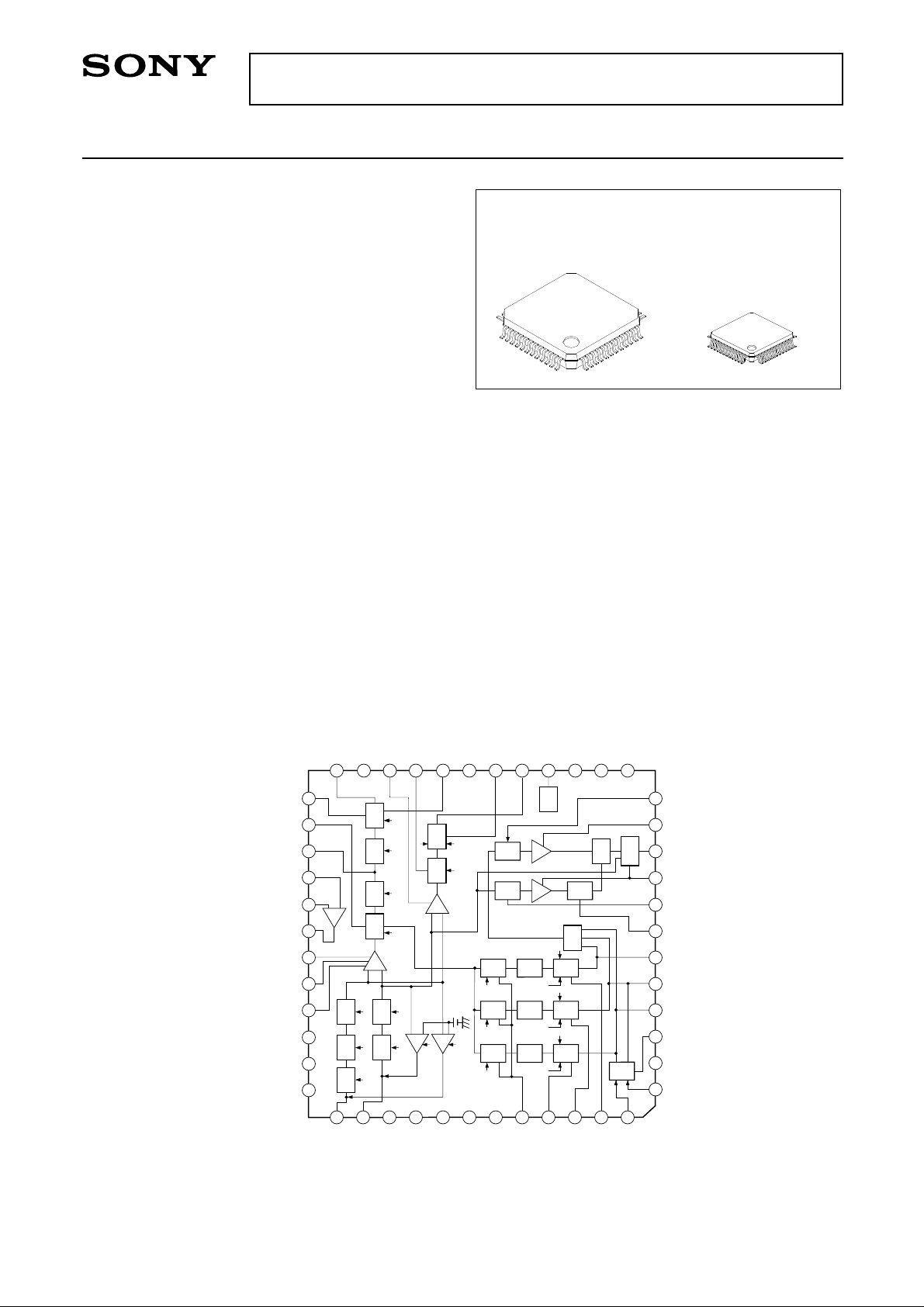

Sony CXA1390AR, CXA1390AQ Datasheet

CXA1390AQ/AR

S/H and AGC for CCD Camera

Description

The CXA1390AQ/AR are CCD camera's signal

processing ICs which extract signals from the CCD

output. These bipolar ICs perform correlated double

sampling. AGC, color separation, high luminance

detection and others. Additionary, these ICs are not

affected by irregular pulses which occure during the

CCD shutter mode.

Featuers

• Pin compatible upgraded version of CXA1390Q/R

which can be swapped out while using same

peripheral chips

• Almost completely corrects irregular pulses and

their negative affects

• Correlated double sampling function alllows for the

suppression of low band noise in the CCD output

• AGC amplifier, which has High S/N ratio and wide

gain control range, enhances the camera sensitivity

• Output for iris adjustment. High luminance

detection output

• Usage of Vg (regulator) output allows for the

formation of IRIS and AGC LOOP which are not

affected by supply voltage functation

Operating Conditions

Supply voltage VCC 4.75 to 5.25 V

CXA1390AQ

48 pin QFP (Plastic)

CXA1390AR

48 pin LQFP (Plastic)

Application

S/H and AGC for CCD camera

Structure

Bipolar silicon monolithic IC

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VCC 12 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 600 (QFP) mW

950 (VQFP) ∗mW

∗

(40mm × 40mm, t = 0.8mm with a mounted glass epoxy

substrate)

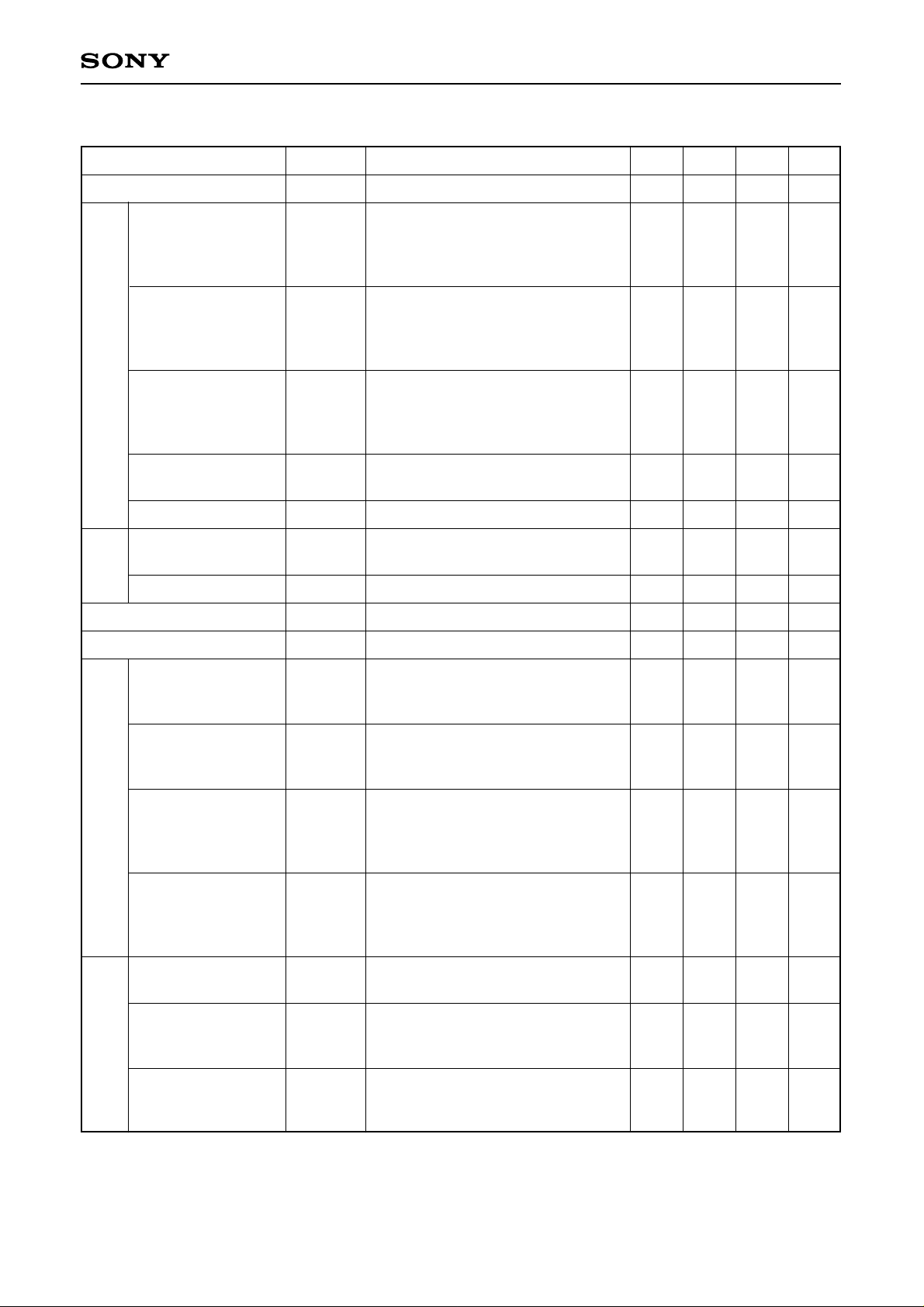

Block Diagram and Pin Configuration (Top View)

CC2

DET OUT

V

IRIS GC

IRIS LEVEL

21

22

CLP

CLP1

CLP1

WND

WND

BLK

PBLK

CLP

CLP1

AGC

SH

XSHP

SH

XSHD

COM

40

39

1

CC

V

XSP3

DET LEVEL

AGC CLP

AGC OUT

OP IN +

OP IN –

OP OUT

AGC CONT

AGC MAX

AGC SEL

XSHP

XSHD

CLP4

23

24

25

26

27

28

29

OP

30

31

32

33

SH

XSHP

34

SHSH

35

36

XSHD

XSHP

37

38

PG IN

DATA IN

DET CLP

GND

IRIS CL P

IRIS OUT

VG OUT

WND

PBLK

CLP1

19

18

17

20

BLK

CLP

WND

GC

CLP4

41

XSP2

COM

SLICE

WND PBLK

SLICE

SH

XSP3

SH

XSP2

CLP4

SH

XSP1

43

42

XSP1

16

VG

GC

CLP

GC

MAX

CLP1

CLP

LPF

BLK

PBLK

CLP1

CLP

LPF

BLK

PBLK

CLP1

CLP

LPF

BLK

PBLK

46

45

44

GND

FSH1

F3 CLP

13

1415

12

CSAGC SL

CSAGC GC

11

CS OUT

F1 CLP

GATE

10

SW

MODE

9

CS CCD GC

CS CCD SL

8

CS CLP

7

F3 OUT

6

5

F2 OUT

4

F1 OUT

GY OUT

3

DC OUT

2

1

XSH1

48

XSH2

OR

47

F2 CLP

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E90941A78

CXA1390AQ/AR

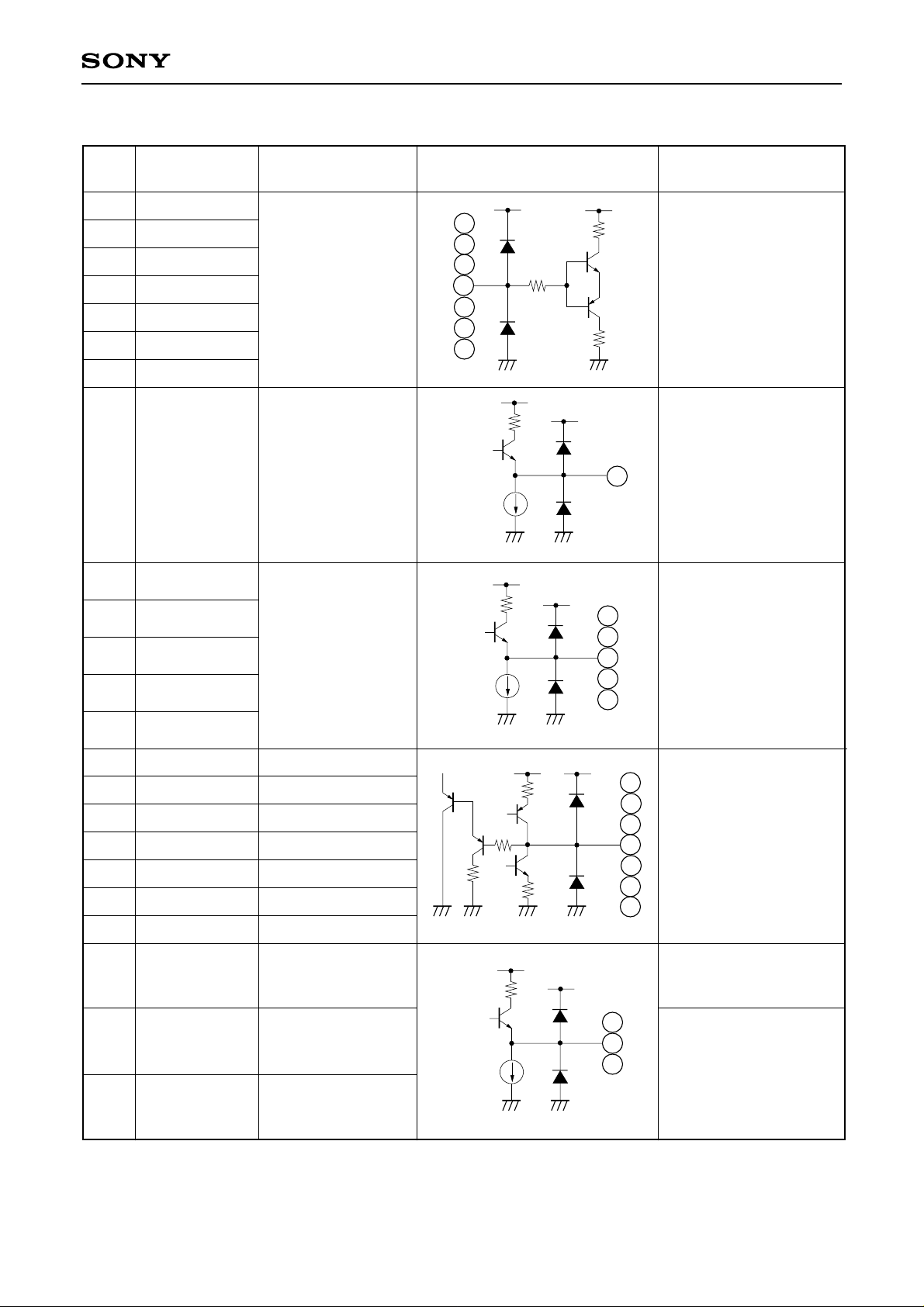

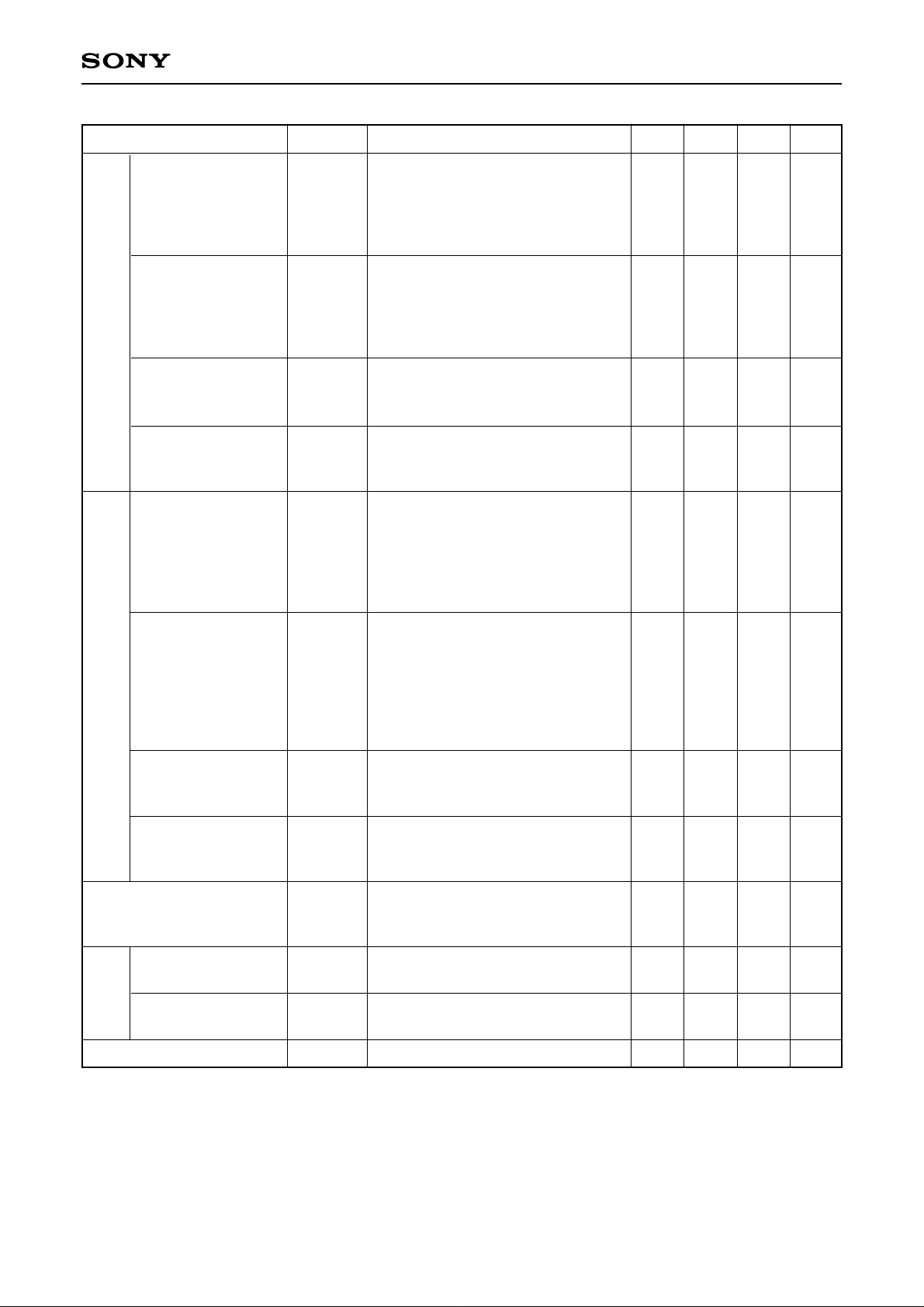

Pin Description and Standard Pin voltage (VCC = 5V)

PIn

No.

1

34

35

40

41

42

48

2

3

4

5

6

Symbol

XSH1

XSHP

XSHD

XSP3

XSP2

XSP1

XSH2

DC OUT

GY OUT

F1 OUT

F2 OUT

F3 OUT

Voltage

H: 4V and above

L: 1V and below

1.8 to 2.1V

Black level

1.8 to 2.1V

Equivalent circuit

1

34

35

40

41

42

48

180µA

360µA

130

1k

300

3

4

6

27

5

200

200

2

Description

High speed pulse input

pin for S/H (active at L)

DC output pin of f1 to f3

output black level

Signal output pin

27

7

18

20

26

45

46

47

10

17

24

AGC OUT

CS CLP

IRIS CLP

DET CLP

AGC CLP

F3 CLP

F2 CLP

F1 CLP

CS OUT

IRIS OUT

DET OUT

2.6 to 3.3V

2.0 to 2.6V

1.9 to 2.6V

2.3 to 2.8V

2.0 to 2.6V

2.0 to 2.6V

2.0 to 2.6V

1.7 to 2.2V

1.7 to 2.0V

1.7 to 2.0V

200µA

130

300

10

17

24

7

18

20

Capacitor connecting

26

45

46

47

pin for clamp

Signal output pin

Signal output pin Vcc

fluctuations effect is

minor on DC level

– 2 –

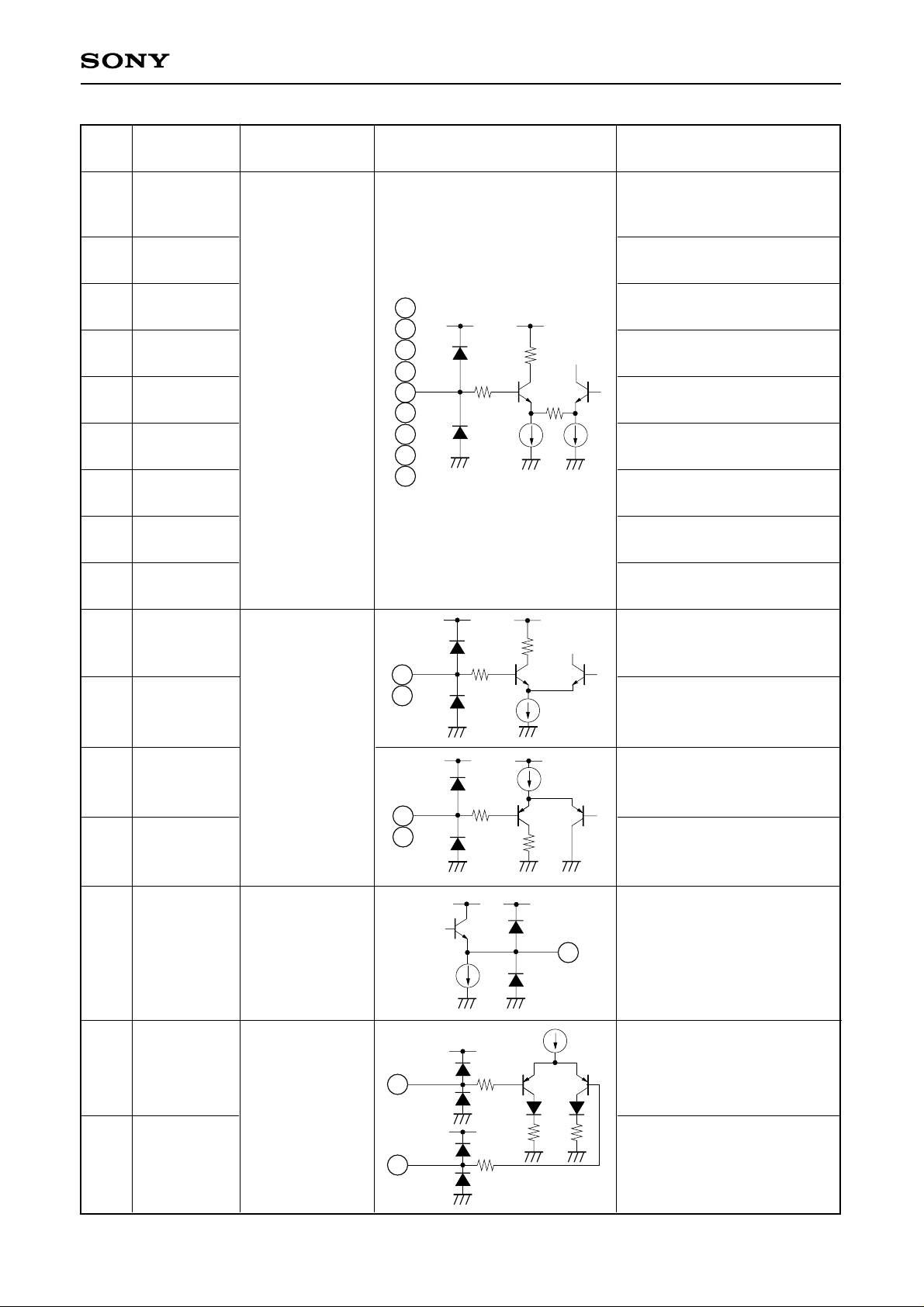

CXA1390AQ/AR

PIn

No.

8

9

11

12

21

22

25

31

32

Symbol

CS CCD SL

CS CCD GC

CSAGC GC

CSAGC SL

IRIS LEVEL

IRIS GC

DET LEVEL

AGC CONT

AGC MAX

Voltage

(Test mode at 0V)

Equivalent circuit

8

9

11

12

21

22

25

31

32

Description

Level adjustment pin of high

luminance detection pin of the

input signal

Gain adjustment pin of input

signal high luminance part

Gain adjustment pin of high

luminance port after AGC

Level adjustment pin of high

luminance detection after AGC

130

Adjustment pin of IRIS output

weighting (Active at WND = L)

Gain adjustment pin of IRIS

output

Adjustment pin of DET output

weighting (Active at WND = L)

AGC amplifier gain

adjustment pin

AGC amplifier MAX gain

adjustment pin

13

14

15

36

16

28

CLP1

P BLK

WND

CLP4

VG OUT

OP IN +

H: 4V and above

L: 1V and below

2.6 to 3.1V

28

13

14

15

36

100µA

130

130

130

16

CLP1 pulse input pin

Active at H (OPB clamp)

Pre BLK pulse input pin

Active at L

Window pulse input pin

Active at L

CLP4 pulse input pin

Active at H

Regulator output pin

(Used for the formation of

AGC and IRIS loop)

Operation amplifier non

inverted input pin

29

OP IN –

1 to 3.3V

29

– 3 –

130

Operation amplifier inverted

input pin

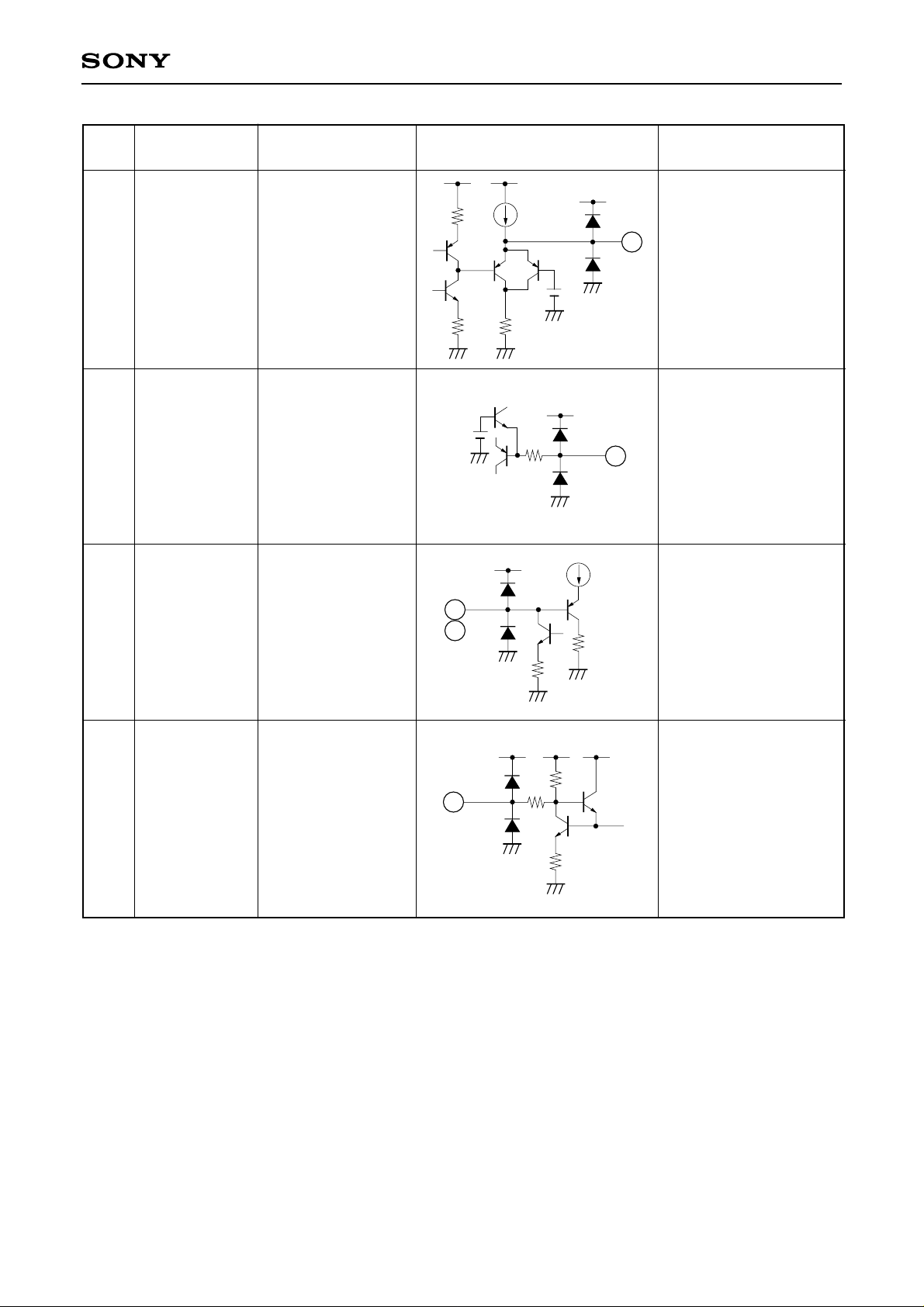

CXA1390AQ/AR

PIn

No.

30

33

Symbol

OP OUT

AGC SEL

Voltage

H: 4.2V and above

L: 1.2V and below

VCC: Low Gain mode

GND: High Gain mode

Equivalent circuit

3.3V

500µA

50k

3.6V

33

100µA

Description

30

Output pin

AGC amplifier gain

selection pin

37

38

44

PG IN

DATA IN

FSHI

Black level

2.7 to 3.2V

1.4 to 1.8V

44

37

38

130

8.5k

CCD signal input pin

Adjustment pin for color

separation S/H follow up

speed

(Normally used OPEN)

– 4 –

CXA1390AQ/AR

Electrical Characteristics

Current consumption

CONT Min.

CONT Max.

AGC

Max. Min.

Gain shift

BLK offset

Color

Gain

separation

BLK offset

(Ta = 25°C, VCC = 5.0V)

SymbolItem Conditions Min. Typ. Max. Unit

ID

32 48 65 mA

AGC OUT/DATA IN

ACON

Min.

AGC CONT = 1.5V

AGC MAX = 5V

68dB

AGC SEL = 0V

AGC OUT/DATA IN

ACON

Max.

AGC CONT = 4.5V

AGC MAX = 5V

30 32 dB

AGC SEL = 0V

AGC OUT/DATA IN

MAX

Min.

AGC CONT = 4.5V

AGC MAX = 1.5V

17 20 dB

AGC SEL = 0V

GSHI

∆BLK

f Gain

f ∆BLK

AGC OUT (SEL = 5V) /AGC OUT

(SEL = 0V)

Note 1)

Color separation output/AGC OUT

(f1, f2, f3)

Note 1)

–5 –4 –3 dB

–10 0 +10 mV

–0.5 0 +0.5 dB

–10 0 +10 mV

DC OUT

Gate Gain

Gain Cont Max.

Gain Cont Min.

IRIS

Window Level Max.

Window Level Min.

Gain

DET

Window Level Max.

DC

GY

IR Max.

IR Min.

IRW

Max.

IRW

Min.

DET G

DET

Max.

GY OUT/AGC OUT

IRIS OUT/DATA IN

IRIS GC = 5V

WND = 5V

IRIS OUT/DATA IN

IRIS GC = 1.5V

WND = 5V

Gain Cont Max. ratio (attenuation)

IRIS GC = 1.5V

IRIS LEVEL = 5V

WND = 0V

Gain Cont Max. ratio (attenuation)

IRIS GC = 1.5V

IRIS LEVEL = 1.5V

WND = 0V

DET OUT/AGC OUT

WND = 5V

DET OUT/AGC OUT

DET LEVEL = 5V

WND = 0V

1.8 1.95 2.1 V

–0.5 0 +0.5 dB

18 22

4

–1

0

8

–14

dB

dB

dB

dB

–2 –1 +0.5 dB

–2

–1

+0.5 dB

Window Level Min.

DET

Min.

Level Max. ratio

DET LEVEL = 1.5V

WND = 0V

– 5 –

–13 dB

CS

CCD

Max. Gain

Min. Gain

CXA1390AQ/AR

SymbolItem Conditions Min. Typ. Max. Unit

CSOUT differential/

CSC

Max.

DATA IN differential

CS CCD SL = 4.1V

CS CCD GC = 5V

13

16

dB

PBLK = 0V

CSOUT differential/

CSC

Min.

DATA IN differential

CS CCD SL = 4.1V

CS CCD GC = 1.5V

–1 1 dB

PBLK = 0V

CS

AGC

Max. SLICE

Min. SLICE

Max. Gain

Min. Gain

Max. SLICE

CSC

Max. SL

CSC

Min. SL

CSA

Max.

CSA

Min.

CSA

Max. SL

Input conversion slice level

CS CCD SL = 1.5V

Note 1)

Input conversion slice level

CS CCD SL = 5V

Note 1)

CS OUT DATA IN = 0.2Vpp

CS AGC GC = 5V

CS AGC SL = 4.2V

CS CCD GC = 1.5V

CS CCD SL = 1.5V

Note 2)

CS OUT differential/

AGC OUTdifferential

CS AGC GC = 1.5V

CS AGC SL = 4.2V

CS CCD GC = 1.5V

CS CCD SL = 1.5V

Note 2)

AGC OUT conversion

CS AGC SL = 1.5V

Note 3)

0.7

0.5

1.2

V

40 100 mV

Vpp

–1 1 dB

V

Min. SLICE

CSA

Min. SL

TEST mode TEST

H level

OPH

OPAmp

L level

Vg OUT

OPL

Vg At no load 2.6 2.85 3.1

AGC OUT conversion

CS AGC SL = 5V

Note 3)

DATA IN = 0.5Vpp

CS CCD GC = 0V

Note 4)

OP IN + = 2.1V

OP IN – = 2.0V

OP IN + = 2.0V

OP IN – = 2.1V

– 6 –

0.06 0.1 V

0.5 Vpp

4.2 V

0.9 1.2 V

V

Loading...

Loading...