SONY CXA1082BS Service Manual

– 1 –

CXA2104S

30 pin SDIP (Plastic)

E97726B96-PS

US Audio Multiplexing Decoder

Description

The CXA2104S is an IC designed as a decoder for

the Zenith TV Multi-channel System and also

corresponds with I2C BUS. Functions include stereo

demodulation, SAP (Separate Audio Program)

demodulation, dbx noise reduction. Various kinds of

filters are built in while adjustment and mode control

are all executed through I2C BUS.

Features

• Adjustment free of VCO and filter.

• Audio multiplexing decoder and dbx noise

reduction decoder are all included in a single chip.

Almost any sort of signal processing is possible

through this IC.

• All adjustments are possible through I2C BUS to

allow for automatic adjustment.

• Various built-in filter circuits greatly reduce external

parts.

• There is an additional SAP output.

Absolute Maximum Ratings (Ta = 25°C)

• Supply voltage VCC 11 V

• Operating temperature Topr –20 to +75 °C

• Storage temperature Tstg –65 to +150 °C

• Allowable power dissipation

PD 1.35 W

Range of Operating Supply Voltage

9 ± 0.5 V

Applications

TV, VCR and other decoding systems for US audio

multiplexing TV broadcasting

Structure

Bipolar silicon monolithic IC

∗ A license of the dbx-TV noise reduction system is

required for the use of this device.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

TVOUT-R

2

3

4

5

6

7

8

9

10

11

12

13

14 15

1

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

TVOUT-L

SDA

SCL

DGND

MAININ

MAINOUT

PCINT1

PCINT2

PLINT

COMPIN

VGR

IREF

GND

SAPTC

SOUT

NC

VCAWGT

VCATC

VCAIN

VEOUT

VETC

VEWGT

VE

SAPIN

SAPOUT

NOISETC

STIN

SUBOUT

V

CC

Standard I/O Level

• Input level

COMPIN (Pin 11) 100mVrms

245mVrms (Selected by INSW)

• Output level

TVOUT-L/R (Pins 2 and 1) 490mVrms

Pin Configuration (Top View)

– 2 –

CXA2104S

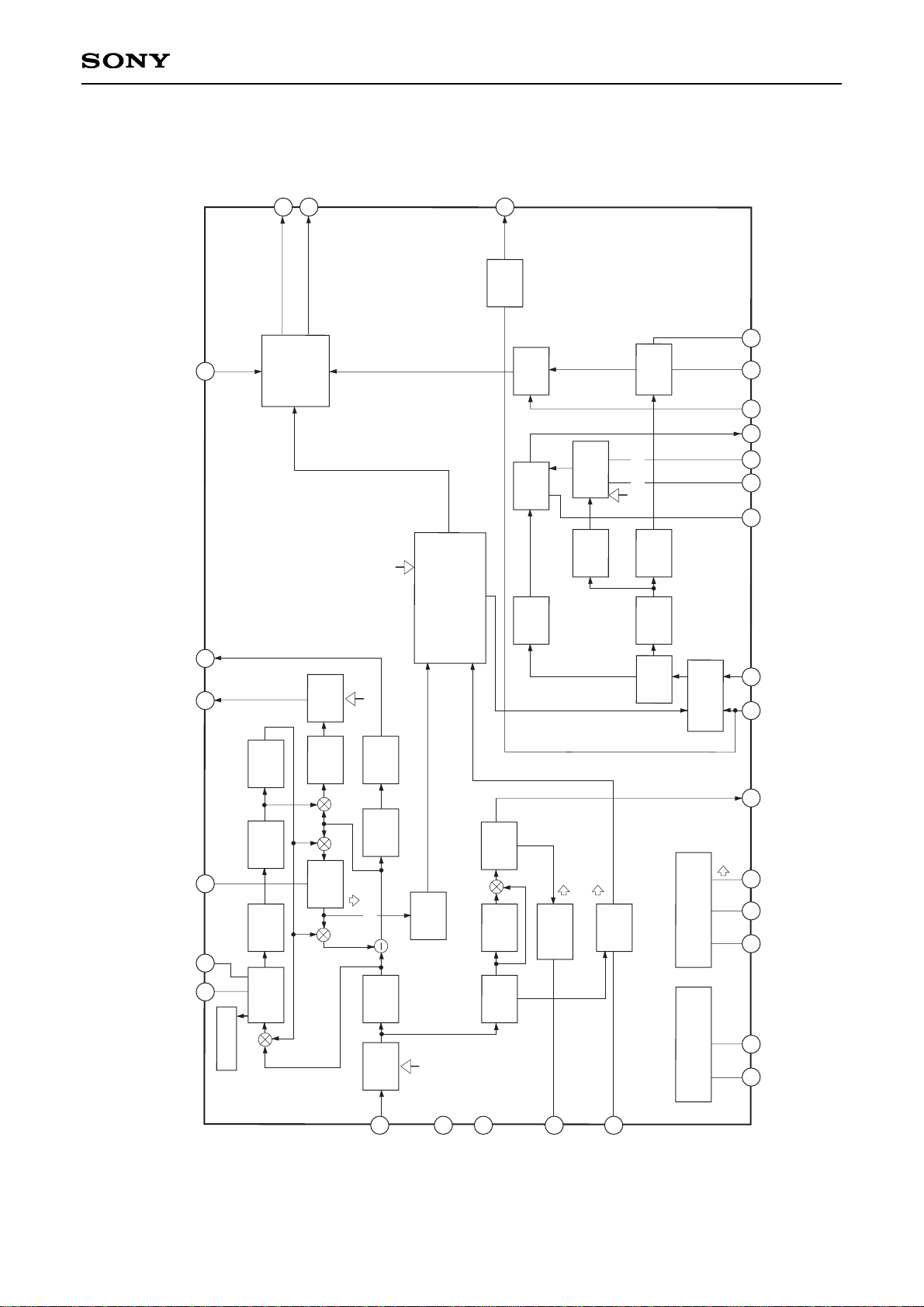

Block Diagram

VGR

IREF

DGND

SCL

SDA

SAPOUT

SAPIN

STIN

VE

VEWGT

VETC

VEOUT

VCAIN

VCAWGT

VCATC

MAININ

MAINOUT

SUBOUT

PLINT

PCINT1

COMPIN

V

CC

GND

NOISETC

SAPTC

TVOUT-L

IREF

SW

LPF LPF

HPF

RMSDET

RMSDET

VCA

VEDeEm

LOGIC

MATRIX

VCA

LPF

LPF

1/21/4VCOLFLT

STLPF

VCA LPF

BPF

SAPVCO

LPF

NOISE

DET

SAPIND

"PONRES"

STIND

"SAP"

"NOISE"

NRSW/FOMO/SAPC

WIDEBAND

SPECTRAL

"STEREO"

DeEm

FLT

AMP

(+4dB)

I

2

C BUS I/F

(+6dB)

TVOUT-R

PCINT2

SOUT

ATT/INSW

LPF

1

2

6

7

17

10

9

8

11

16

14

19

15

12

13

5

4

3

20

21

18

22

23

24

25

26

28

27

30

– 3 –

CXA2104S

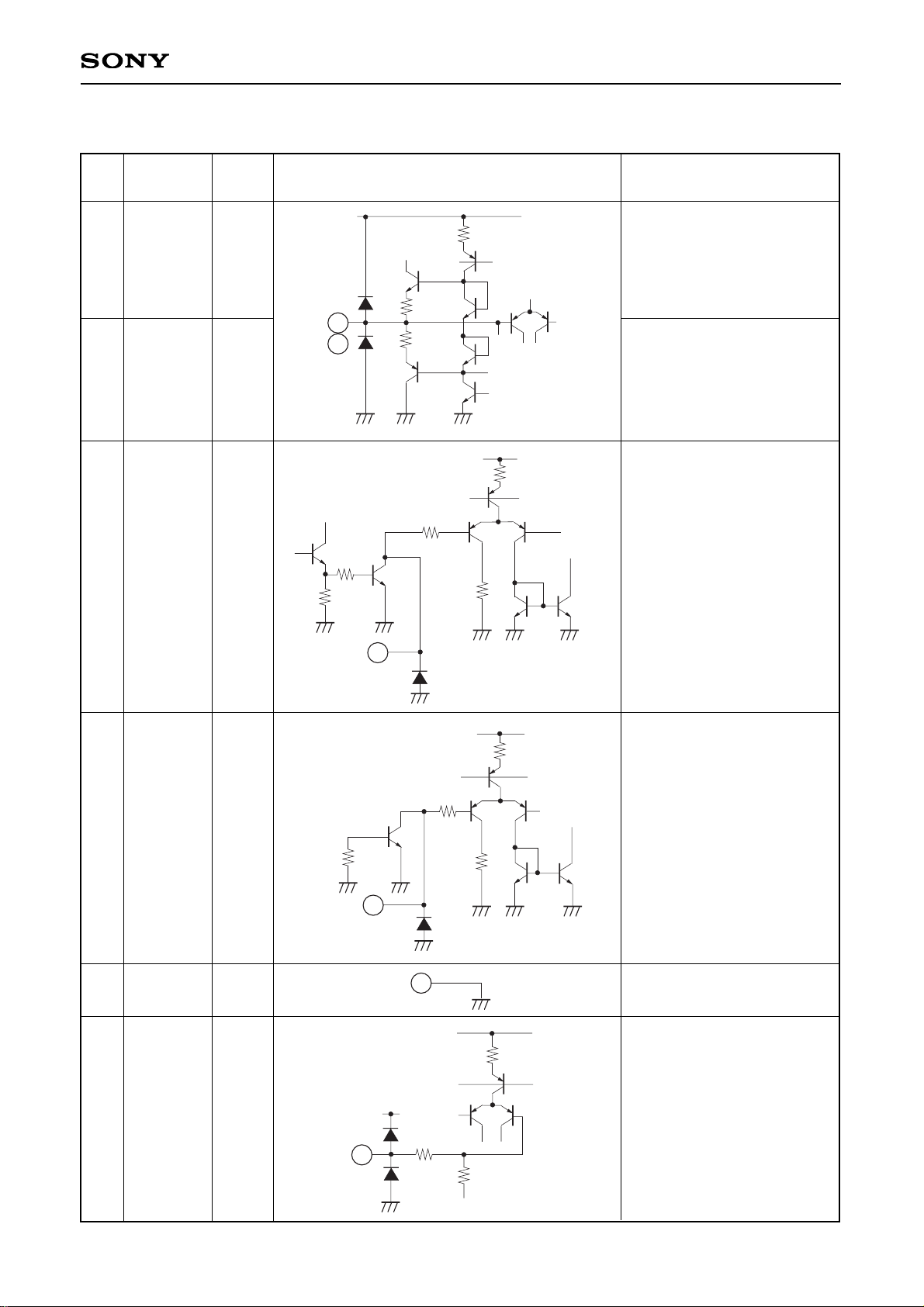

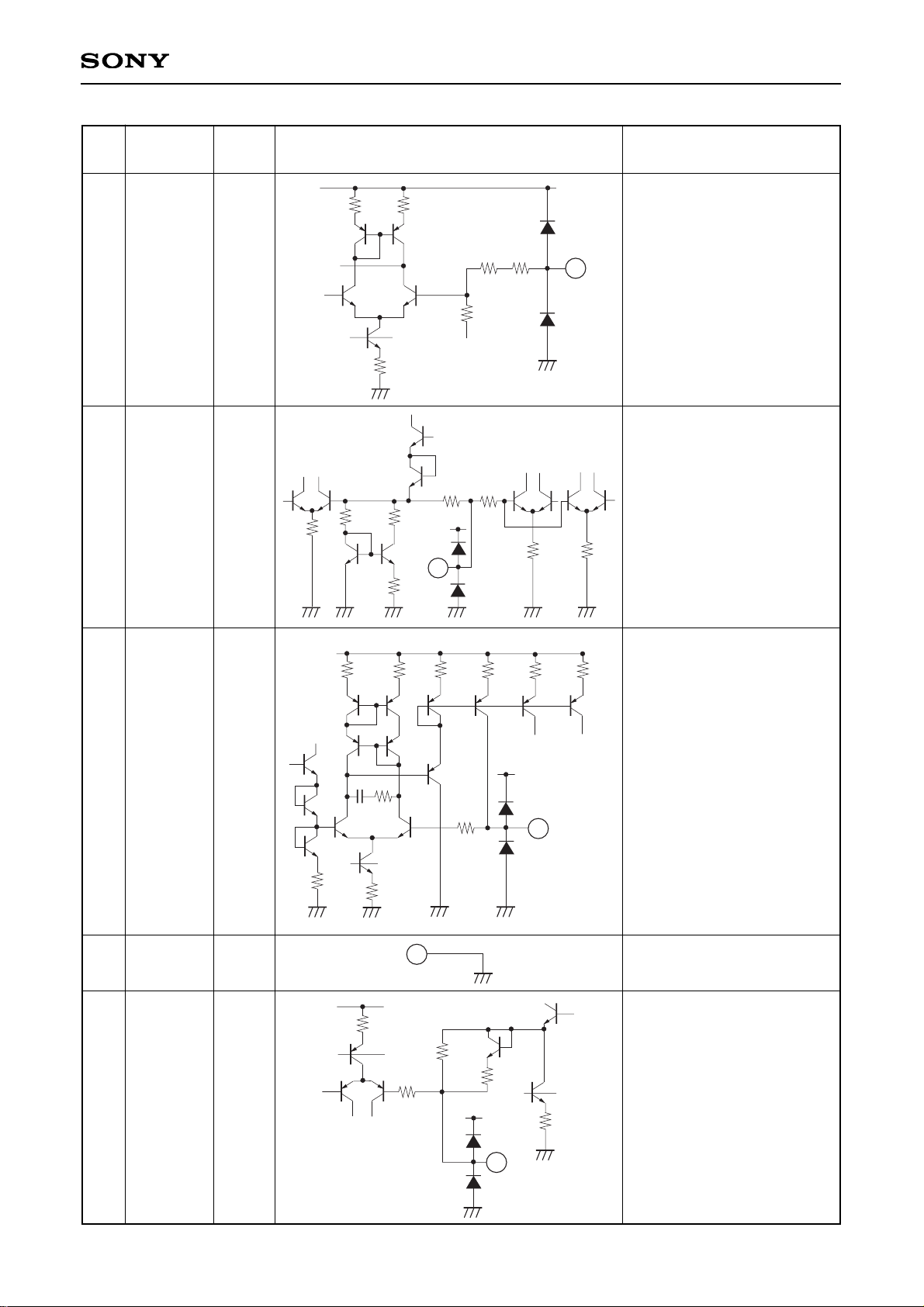

Pin Description (Ta = 25°C, VCC = 9V)

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

SDA

SCL

DGND

MAININ

—

—

—

4.0V

Serial data I/O pin.

VIH > 3.0V

VIL < 1.5V

Serial clock input pin.

VIH > 3.0V

VIL < 1.5V

Digital block GND.

Input the (L + R) signal from

MAINOUT (Pin 7).

3

4

5

6

TVOUT-R

4.0V

TVOUT right channel output

pin.

1

TVOUT-L 4.0V

TVOUT left channel output

pin.

2

3k

580

580

VCC

2

1

7.5k

CC

V

7.5k

↓ 35µ

2.1V

× 2

4.5k

× 5

4k

3k

3

VCC

7.5k

↓ 35µ

4k

10.5k

× 4

3k

2.1V

4

5

VCC

10k

VCC

6

147

53k

4V

– 4 –

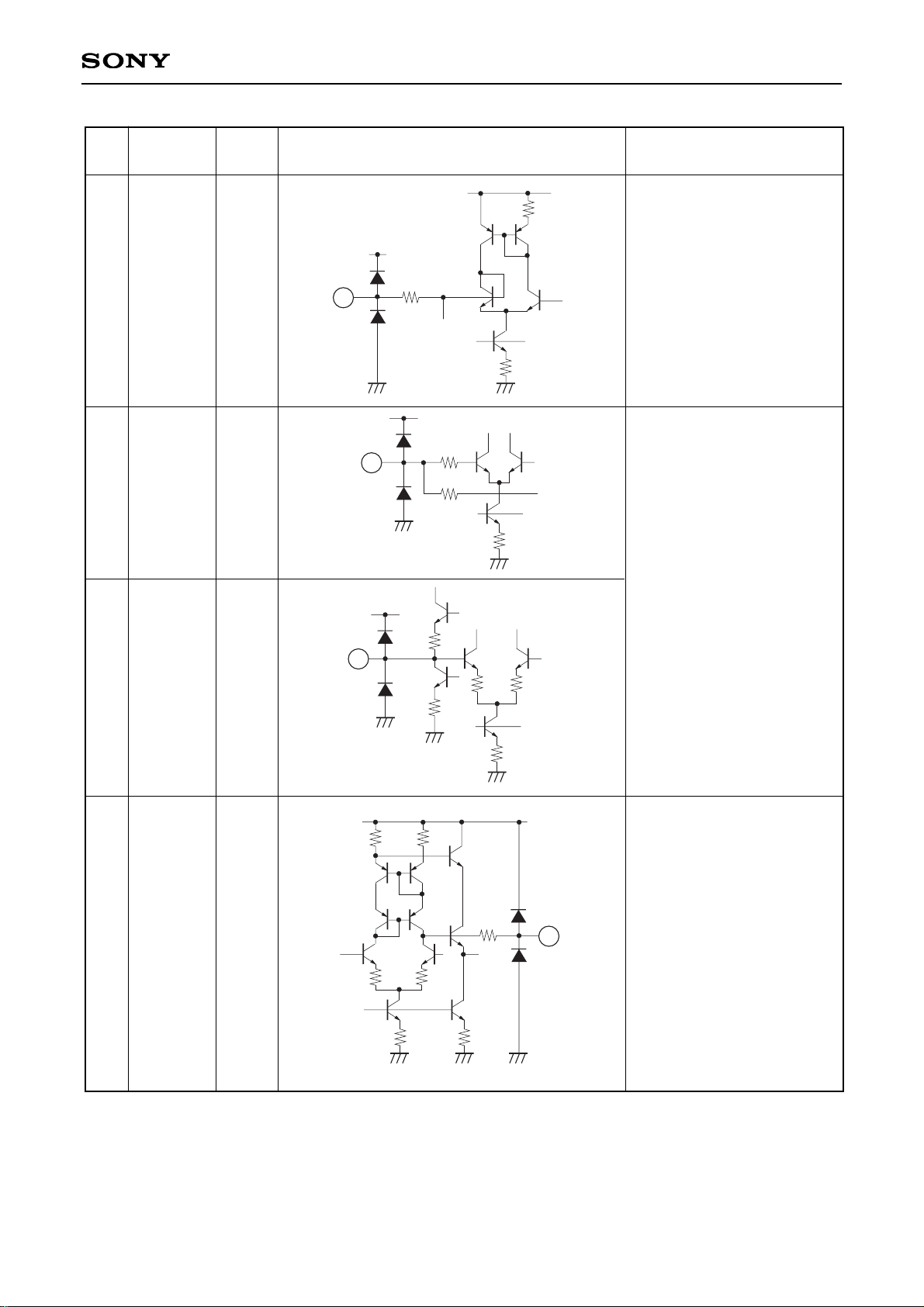

CXA2104S

MAINOUT

PCINT1

PCINT2

PLINT

4.0V

4.0V

4.0V

5.1V

(L + R) signal output pin.

Stereo block PLL loop filter

integrating pin.

Pilot cancel circuit loop filter

integrating pin.

(Connect a 1µF capacitor

between this pin and GND.)

VCC

147

1k

15k

↓

200µ

V

CC

× 4

7

VCC

147

20k

↓

26µ

20k

10k

20k

↓

50µ

20k

20k

10

22k

VCC

30k

147

8

4k

VCC

× 2

10k

10k

2k

147

9

7

8

9

10

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

– 5 –

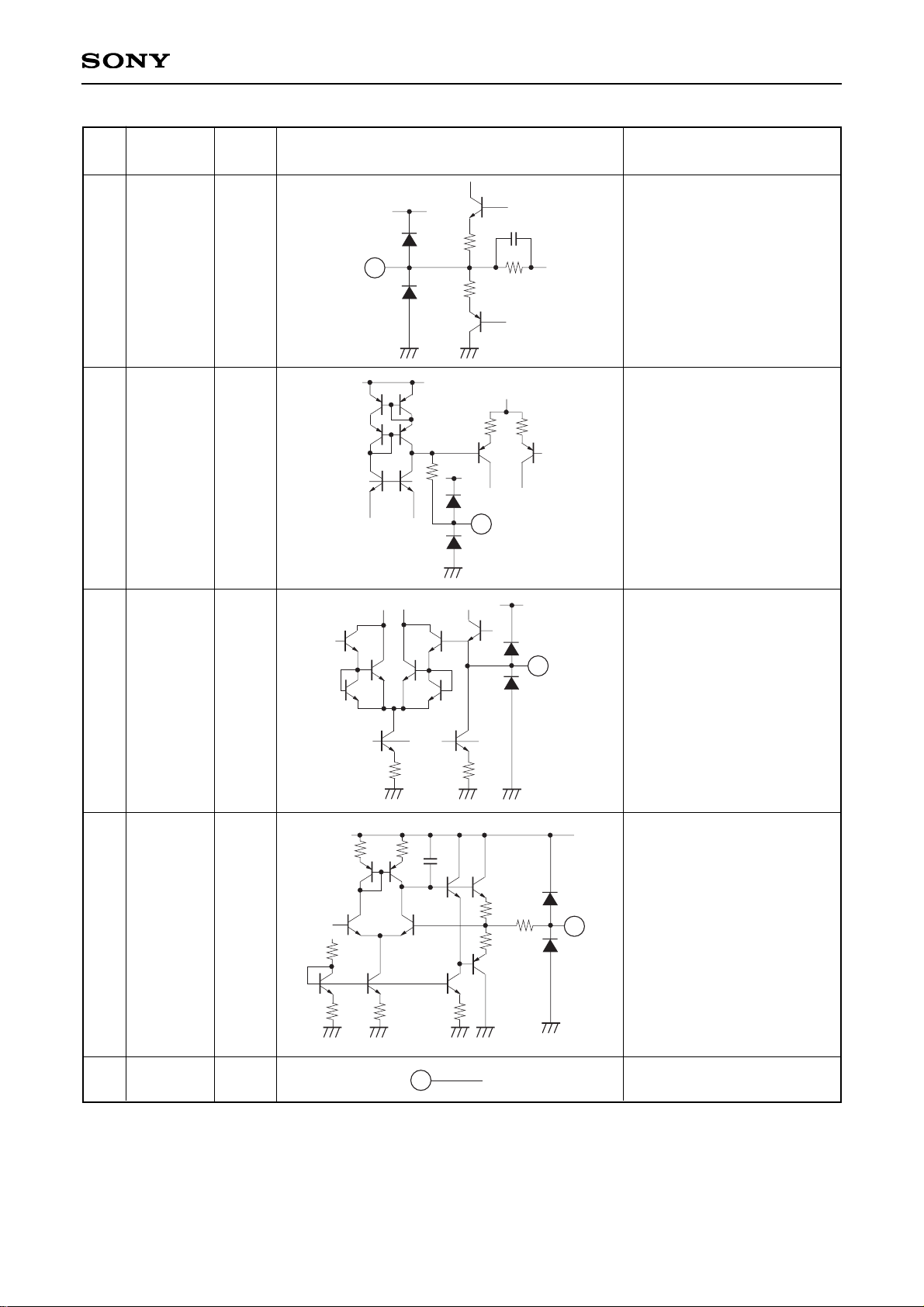

CXA2104S

COMPIN

VGR

IREF

GND

4.0V

1.3V

1.3V

—

Audio multiplexing signal

input pin.

Band gap reference output

pin.

(Connect a 10µF capacitor

between this pin and GND.)

Set the filter and VCO

reference current. The

reference current is adjusted

with the BUS DATA based on

the current which flows to this

pin.

(Connect a 62kΩ (±1%)

resistor between this pin and

GND.)

Analog block GND.

Set the time constant for the

SAP carrier detection circuit.

(Connect a 4.7µF capacitor

between this pin and GND.)

11

12

13

14

SAPTC

4.5V

15

11

VCC

24k

4V

34k

14k 147

24k 24k

8k

4k

3k

10k

V

CC

↓ 50µ

1k

VCC

15

14

40k 40k 30k

30p 1.8k

16k

6.3k

147

30k 15k 30k

VCC

× 2

V

CC

13

× 4

11k

9.7k

19.4k

2.06k

3k

147

VCC

11k

11k

12

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

– 6 –

CXA2104S

VCC

SUBOUT

STIN

NOISETC

—

4.0V

4.0V

3.0V

Supply voltage pin.

(L–R) signal output pin.

Input the (L-R) signal from

SUBOUT (Pin 17).

Set the time constant for the

noise detection circuit.

(Connect a 4.7µF capacitor

between this pin and GND.)

16

17

18

SAPIN

4.0V

Input the (SAP) signal from

SAPOUT (Pin 20).

21

19

16

2k

2k

2k

4k

1k

147

580

14.4k

580

4k

10P

2k2k

Vcc

17

23k

147

18k

20k

11.7k

23k

4V

147

18k

4V

VCC

18

21

3k

3k

3.3k

4k

4V

Vcc

8k

× 2

10k

1k

2k

Vcc

200k

19

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

– 7 –

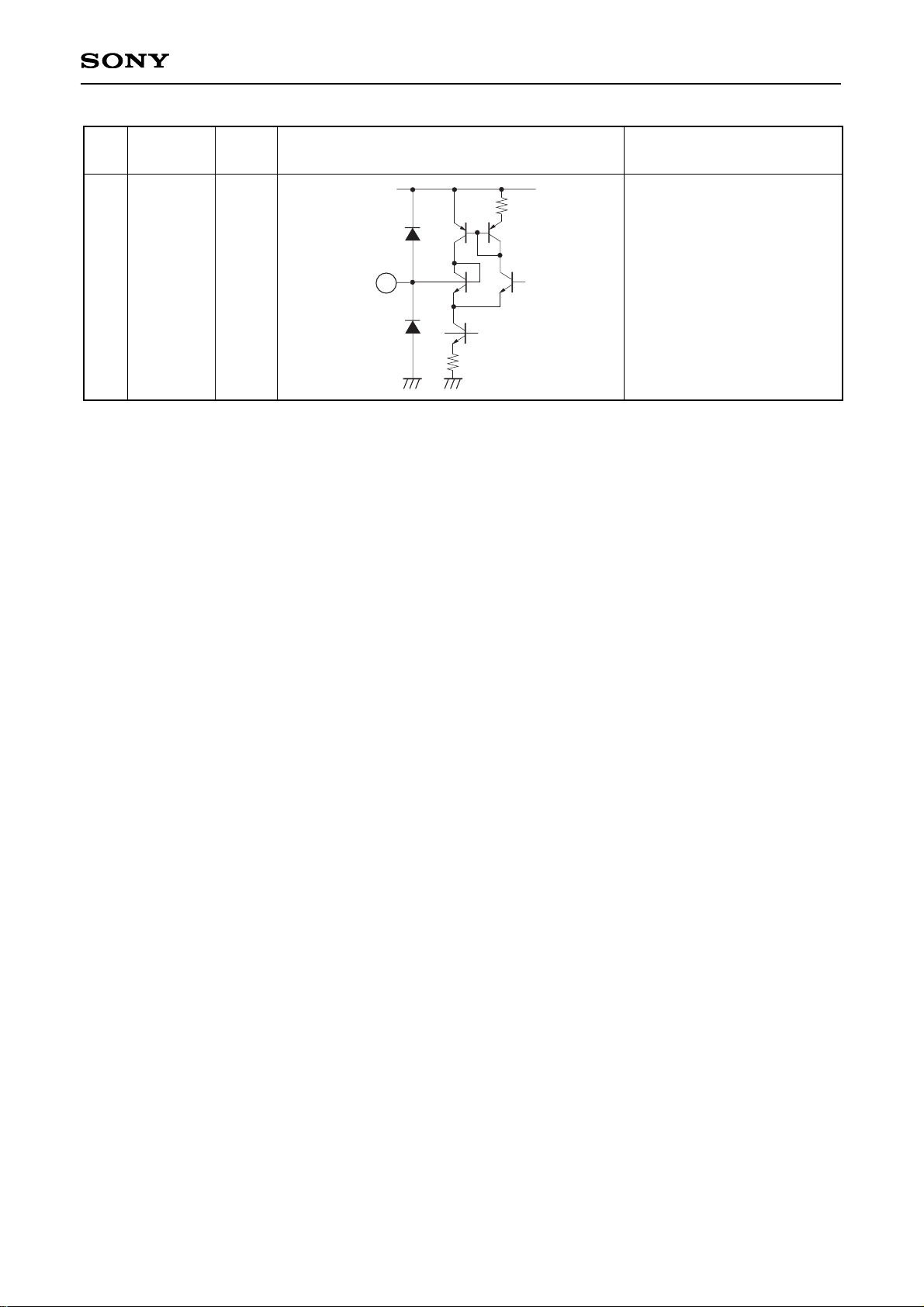

CXA2104S

SAPOUT

VE

VETC

4.0V

4.0V

1.7V

SAP FM detector output pin.

Variable de-emphasis

integrating pin.

(Connect a 2700pF capacitor

and a 3.3kΩ resistor in series

between this pin and GND.)

Determine the restoration

time constant of the variable

de-rmphasis control effective

value detection circuit.

(the specified restoration time

constant can be obtained by

connecting a 3.3µF capacitor

between this pin and GND.)

20

22

VEWGT

4.0V

Weight the variable

de-emphasis control effective

value detection circuit.

(Connect a 0.047µF capacitor

and a 3kΩ resistor in series

between this pin and GND.)

23

24

24k

↓ 10µ

580

Vcc

5P

580

4k

↓ 50µ

10k

147

20

Vcc

4V

36k

2.9V

580

147

580

8k

30k

↓ 8µ

4k

↓ 50µ

23

20k

↓ 7.5µ

4k

↓ 50µ

Vcc

× 4

× 4

24

7.5k

147

VCC

22

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

– 8 –

CXA2104S

VEOUT

VCAIN

VCAWGT

4.0V

4.0V

4.0V

Variable de-emphasis output

pin.

(Connect a 4.7µF non-polar

capacitor between Pins 25

and 26.)

VCA input pin.

Input the variable

de-emphasis output signal

from Pin 25 via a coupling

capacitor.

Weight the VCA control

effective value detection

circuit.

(Connect a 1µF capacitor

and a 3.9kΩ resistor in series

between this pin and GND.)

25

26

VCATC

1.7V

Determine the restoration

time constant of the VCA

control effective value

detection circuit.

(the specified restoration

time constant can be

obtained by connecting a

10µF capacitor between this

pin and GND.)

27

28

Vcc

10k

580

580

5P

25

4k

VCC

30k

8k

36k

2.9V

3p

580

580

147

40k 40k

↓

50µ

↓

8µ

28

↓

50µ

VCC

4k

20k

× 4

× 4

↓

7.5µ

27

VCC

20k

VCC

47k

47k

26

29

NC

—

29

—

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

– 9 –

CXA2104S

SOUT

4.0V

Additional SAP output pin.

30

VCC

1k

15k

× 4

↓

200µ

30

Pin

No.

Symbol

Pin

voltage

Equivalent circuit Description

Loading...

Loading...